Philips TEA1210TS-N1 Datasheet

DATA SH EET

Preliminary specification

File under Integrated Circuits, IC03

1999 Mar 08

INTEGRATED CIRCUITS

TEA1210TS

High efficiency, high current DC/DC

converter

1999 Mar 08 2

Philips Semiconductors Preliminary specification

High efficiency, high current DC/DC converter TEA1210TS

FEATURES

• Fully integrated DC/DC converter circuit, featuring

internal very low R

DSon

power MOSFETs

• Up-or-down conversion

• Start-up from 1.85 V input voltage

• Adjustable output voltage

• High efficiency over large load range

• 600 kHz switching frequency

• Low quiescent power consumption

• Synchronizing with external clock

• Two selectable current limits for efficient battery use in

case of dynamic loads

• Up to 100% duty cycle in down mode

• Undervoltage lockout

• Shut-down function

• 16-pin small body SSOP16 package.

APPLICATIONS

• Cellular phones, Personal Digital Assistants (PDAs) and

others

• Supply voltage source for low-voltage chip sets

• Portable computers

• Battery backup supplies.

GENERAL DESCRIPTION

The TEA1210TS is a fully integrated DC/DC converter.

Efficient, compact and dynamic power conversion is

achieved using a novel digitally controlled concept like

Pulse Width Modulation (PWM) or Pulse Frequency

Modulation (PFM), integrated low R CMOS power

switches with low parasitic capacitances, and fully

synchronous rectification.

The device operates at 600 kHz switching frequency

which enables the use of external components with

minimum size. The switching frequency can be locked to

an external high-frequency clock.

Optionally, the device can be kept in the Pulse Width

Modulation (PWM) mode regardless of the load applied.

Deadlock is prevented by an on-chip undervoltage lockout

circuit.

Two selectable current limits in upconversion mode enable

efficient battery use even at highly dynamic loads such as

cellular phone electronics.

ORDERING INFORMATION

TYPE NUMBER

PACKAGE

NAME DESCRIPTION VERSION

TEA1210TS SSOP16 plastic shrink small outline package; 16 leads; body width 4.4 mm SOT369-1

1999 Mar 08 3

Philips Semiconductors Preliminary specification

High efficiency, high current DC/DC converter TEA1210TS

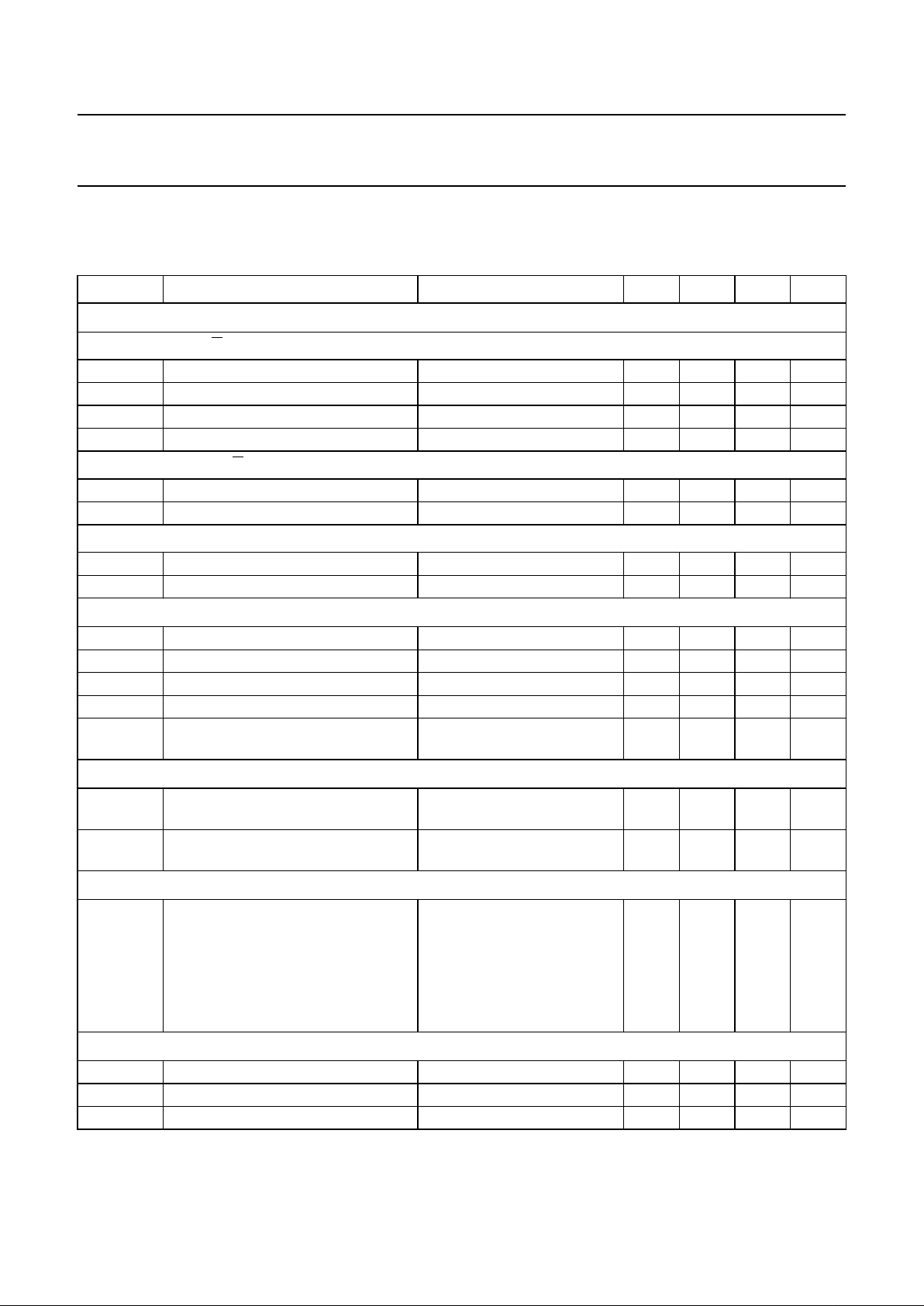

QUICK REFERENCE DATA

T

amb

= −40 to +80 °C; all voltages measured with respect to ground; positive currents flow into the IC; unless otherwise

specified.

SYMBOL P ARAMETER CONDITIONS MIN. TYP. MAX. UNIT

Voltage levels

U

PCONVERSION; pin U/D = LOW

V

I

input voltage V

I(start)

− 5.50 V

V

O

output voltage 2.90 − 5.50 V

V

I(start)

start-up input voltage IL< 200 mA 1.20 1.60 1.85 V

V

I(uvlo)

undervoltage lockout input voltage 1.50 2.10 2.70 V

DOWNCONVERSION; pin U/D = HIGH

V

I

input voltage 2.90 − 5.50 V

V

O

output voltage 1.30 − 5.50 V

GENERAL

V

fb

feedback input voltage 1.20 1.25 1.30 V

∆V

window

output voltage window PWM mode 1.5 2.0 3.0 %

Current levels

I

q

quiescent current on pins LX VI=2.40 V; VO= 3.60 V 100 125 150 µA

I

shdwn

current in shut-down mode − 210µA

∆I

lim(up)

current limit deviation in up mode I

lim(up)

set to 2.0 A −12 − +12 %

I

lim(down)

current limit in down mode 4.8 A

I

LX

maximum continuous current on

pins LX

T

amb

=60°C −−1.8 A

Power MOSFETs

R

DSon(N)

drain-to-source on-state resistance

NFET

Tj=27°C − 56 63 mΩ

R

DSon(P)

drain-to-source on-state resistance

PFET

Tj=27°C − 68 77 mΩ

Efficiency

η efficiency upconversion VI= 2.4 V; VO= 3.6 V;

T

amb

=20°C

I

L

=1mA 83 86 − %

I

L

= 100 mA 90 93 − %

I

L

= 500 mA 92 94 − %

I

L

= 1.5 A; not continual 84 86 − %

Timing

f

sw

switching frequency PWM mode 480 600 720 kHz

f

sync

synchronization clock input frequency 9 13 20 MHz

t

res

response time from standby to P

o(max)

− 25 −µs

1999 Mar 08 4

Philips Semiconductors Preliminary specification

High efficiency, high current DC/DC converter TEA1210TS

This text is here in white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here in

_white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here inThis text is here in

white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader. white to force landscape pages to be ...

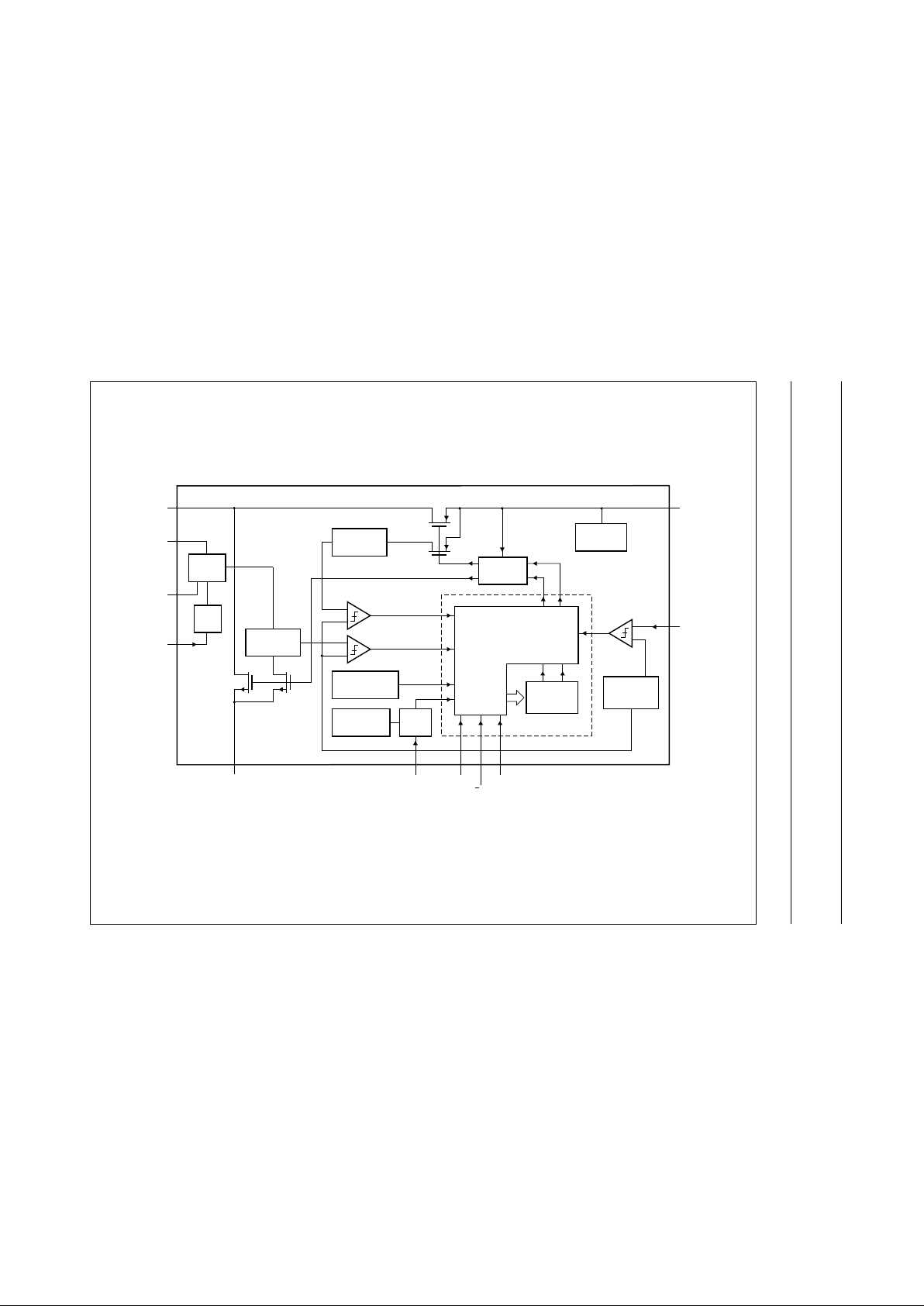

BLOCK DIAGRAM

n

dbook, full pagewidth

MGR725

CONTROL LOGIC

AND

MODE GEARBOX

INTERNAL

SUPPLY

START-UP

CIRCUIT

I/V

CONVERTER

I/V

CONVERTER

TIME

COUNTER

BAND GAP

REFERENCE

13 MHz

OSCILLATOR

SYNC

GATE

SWITCH

LPF

TEMPERATURE

PROTECTION

DIGITAL CONTROLLER

sense FET

P-type POWER FET

sense

FET

SHDWN

GND

SYNC

U/D

N-type

POWER

FET

LX

UPOUT

FB

TEA1210TS

28, 9 3

PWM

146

4, 5, 12, 13

ILIMH

7

ILIML

10

ILIMSEL

11

1, 16

15

CURRENT LIMIT

COMPARATORS

Fig.1 Block diagram.

1999 Mar 08 5

Philips Semiconductors Preliminary specification

High efficiency, high current DC/DC converter TEA1210TS

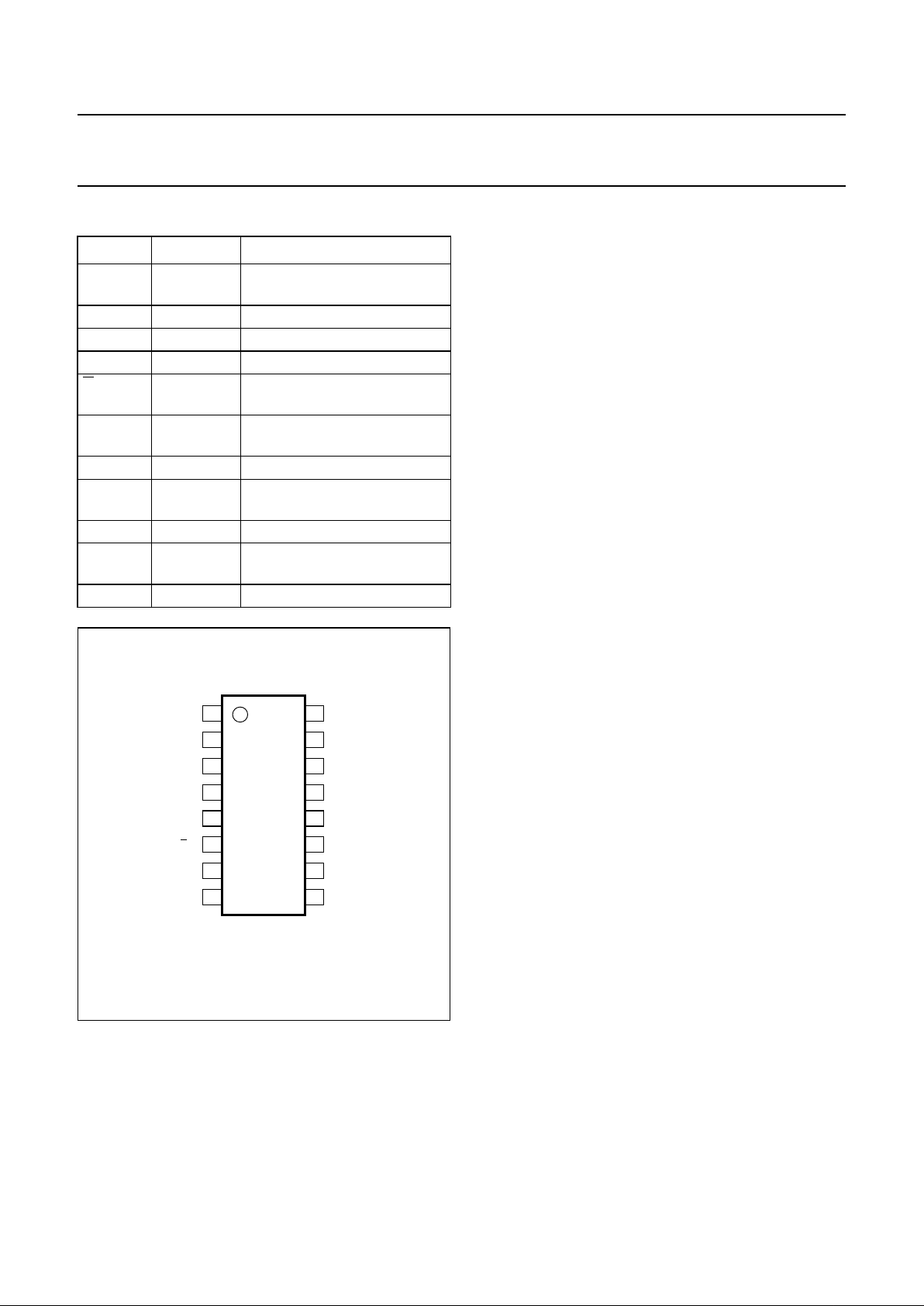

PINNING

For all possible applications, the following groups of pins

must be connected together:

• Pins 4, 5, 12 and 13 (pins LX)

• Pins 1 and 16 (pins UPOUT)

• Pins 8 and 9 (pins GND).

SYMBOL PIN DESCRIPTION

UPOUT 1, 16 output voltage in up mode;

input voltage in down mode

SYNC 2 synchronization clock input

SHDWN 3 shut-down input

LX 4, 5, 12, 13 inductor connection

U/D 6 up-or-down mode selection

input; active LOW for up mode

ILIMH 7 current limiting resistor 1

connection

GND 8,9 ground

ILIML 10 current limiting resistor 2

connection

ILIMSEL 11 current limiting selection input

PWM 14 PWM-only mode selection

input

FB 15 feedback input

Fig.2 Pin configuration.

handbook, halfpage

TEA1210TS

MGR726

1

2

3

4

5

6

7

8

16

15

14

13

12

11

10

9

UPOUT

SYNC

SHDWN

LX

LX

U/D

ILIMH

GND

GND

ILIML

ILIMSEL

LX

LX

PWM

FB

UPOUT

FUNCTIONAL DESCRIPTION

Control mechanism

The TEA1210TS DC/DC converter is able to operate in

PFM (discontinuous conduction) or PWM (continuous

conduction) operating mode. All switching actions are

completely determined by a digital control circuit which

uses the output voltage level as its control input. This novel

digital approach enables the use of a new pulse width and

frequency modulation scheme, which ensures optimum

power efficiency over the complete operating range of the

converter.

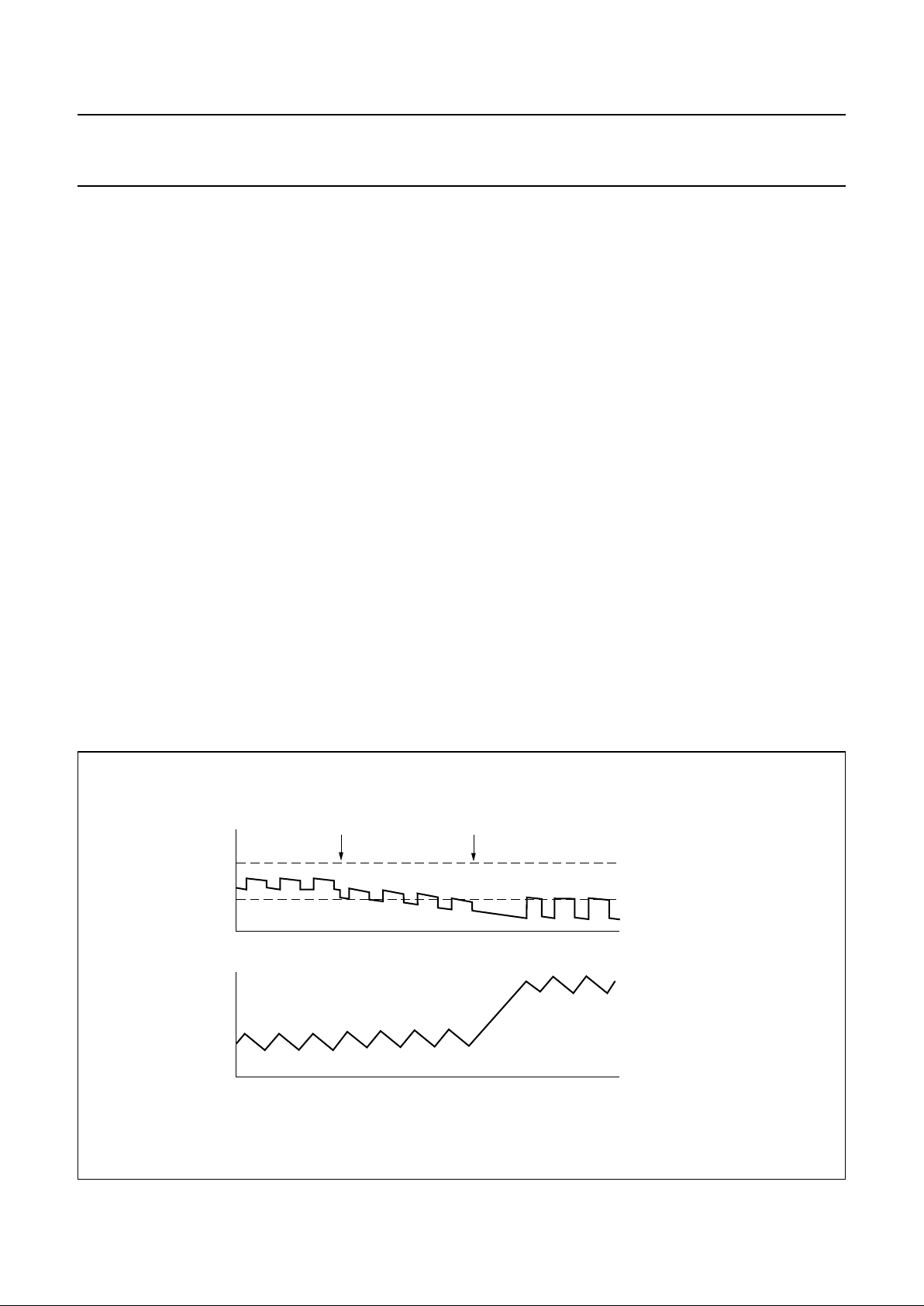

When high output power is requested, the device will

operate in PWM (continuous conduction) operating mode.

This results in minimum AC currents in the circuit

components and hence optimum efficiency, cost and

EMC. In this operating mode, the output voltage is allowed

to vary between two predefined voltage levels. As long as

the output voltage stays within this so-called window,

switching continues in a fixed pattern. When the output

voltage reaches one of the window borders, the digital

controller immediately reacts by adjusting the pulse width

and inserting a current step in such a way that the output

voltage stays within the window with higher or lower

current capability. This approach enables very fast

reaction to load variations. Figure 3 shows the converter’s

response to a sudden load increase. The upper trace

shows the output voltage. The ripple on top of the DC level

is a result of the current in the output capacitor, which

changes in sign twice per cycle, times the capacitor’s

internal Equivalent Series Resistance (ESR). After each

ramp-down of the inductor current, i.e. when the ESR

effect increases the output voltage, the converter

determines what to do in the next cycle. As soon as more

load current is taken from the output the output voltage

starts to decay.

When the output voltage becomes lower than the low limit

of the window, a corrective action is taken by a ramp-up of

the inductor current during a much longer time. As a result,

the DC current level is increased and normal PWM control

can continue. The output voltage (including ESR effect) is

again within the predefined window.

Figure 4 depicts the spread of the output voltage window.

The absolute value is most dependent on spread, while the

actual window size is not affected. For one specific device,

the output voltage will not vary more than 2% typically.

In low output power situations, the TEA1210TS will switch

over to PFM (discontinuous conduction) operating mode in

case the PWM-only mode is not active.

1999 Mar 08 6

Philips Semiconductors Preliminary specification

High efficiency, high current DC/DC converter TEA1210TS

In the PFM mode, regulation information from earlier PWM

operating modes is used. This results in optimum inductor

peak current levels in the PFM mode, which are slightly

larger than the inductor ripple current in the PWM mode.

As a result, the transition between PFM and PWM mode is

optimum under all circumstances. In the PFM mode,

TEA1210TS regulates the output voltage to the high

window limit shown in Fig.3.

Synchronous rectification

For optimum efficiency over the whole load range,

synchronous rectifiers inside the TEA1210TS ensure that

during the whole second switching phase, all inductor

current will flow through the low-ohmic power MOSFETs.

Special circuitry is included which detects that the inductor

current reaches zero. Following this detection, the digital

controller switches off the power MOSFET and proceeds

regulation.

PWM-only mode

When pin PWM is pulled to HIGH-level in the

upconversion mode, the TEA1210TS will use PWM

regulation independent of the load applied. As a result, the

switching frequency does not vary over the whole load

range. Furthermore, the P-type power MOSFET is always

on when the input voltage exceeds the target output

voltage. The internal synchronous rectifier still takes care

that the inductor current does not fall below zero. In this

way, the achieved efficiency is higher than in standard

PWM-controlled converters.

Start-up

Start-up from low input voltage in boost mode is realized

by an independent start-up oscillator, which starts

switching the N-type power MOSFET as soon as the

voltage on pins UPOUT is measured to be sufficiently

high. The switch actions of the start-up oscillator will

increase the output voltage. As soon as the output voltage

is high enough for normal regulation, the digital control

system takes over the control of the power MOSFETs.

Undervoltage lockout

As a result of too high load or disconnection of the input

power source, the output voltage can drop so low that

normal regulation cannot be guaranteed. In that case, the

device switches back to start-up mode. If the output

voltage drops down even further, switching is stopped

completely.

Shut-down

When the shut-down input is made HIGH, the converter

disables both switches and power consumption is reduced

to a few microamperes.

Fig.3 Response to load increase.

handbook, full pagewidth

MGK925

start corrective action

load increase

high window limit

low window limit

V

o

I

L

time

time

Loading...

Loading...