Philips tda8758 DATASHEETS

INTEGRATED CIRCUITS

DATA SH EET

TDA8758

YC 8-bit low-power

analog-to-digital video interface

Product specification

Supersedes data of 1995 Mar 22

File under Integrated Circuits, IC02

1996 Feb 01

Philips Semiconductors Product specification

YC 8-bit low-power analog-to-digital

video interface

FEATURES

• Two 8-bit ADCs:

– one Luminance or CVBS channel

– one Chrominance channel

• Sampling rate up to 32 MHz

• Binary or two's complement 3-state TTL outputs for

each channel

• Internal reference voltage regulator

• TTL-compatible digital inputs and outputs

• Power dissipation of 530 mW (typical)

• Input selector circuit (five selectable video inputs for

CVBS or YC processing)

• Peak white enable input

• Clamp and Automatic Gain Control (AGC) functions for

Y/CVBS channel (clamping on code 64 and Peak White

level control at code 255)

• Clamp function for C channel (code 128)

• No sample-and-hold circuit required.

TDA8758

APPLICATIONS

• Video signal decoding

• Digital picture processing

• Frame grabbing

• Multimedia with the Philips Desktop Video chip set (and

especially SAA7196 multistandard decoder and scaler).

GENERAL DESCRIPTION

The TDA8758 is an 8-bit video high-speed low-power

analog-to-digital conversion (ADC) interface for YC and

CVBS signal processing. It converts 1-of-3 CVBS input

signals or 1-of-2 YC input signals into binary or two’s

complement words at a sampling rate of 32 MHz.

All analog signal inputs are digitally clamped and an ADC

interface is provided on the Y/CVBS channel. A fast

precharge on clamp and AGC is provided for start-up.

All digital inputs and outputs are TTL compatible.

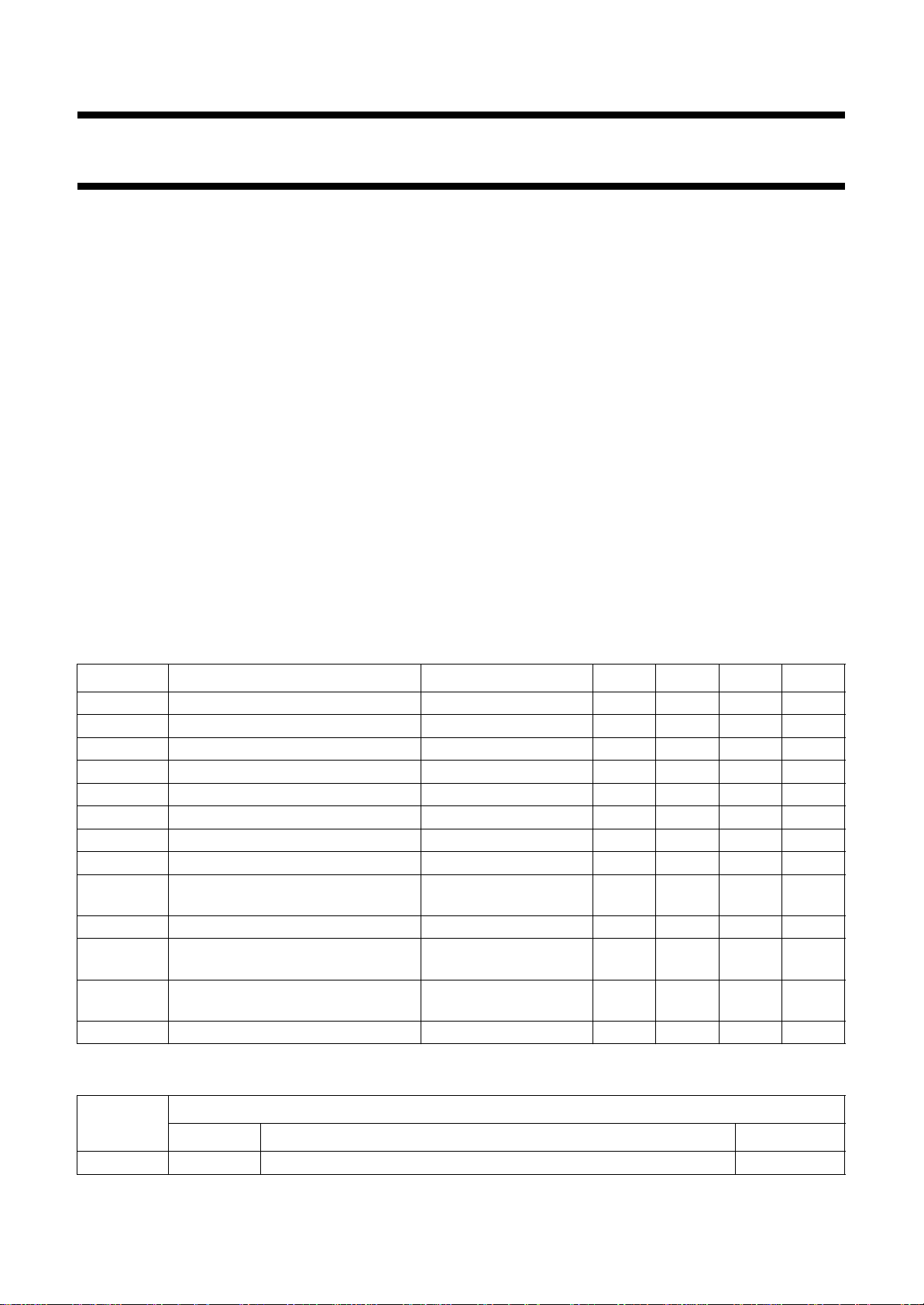

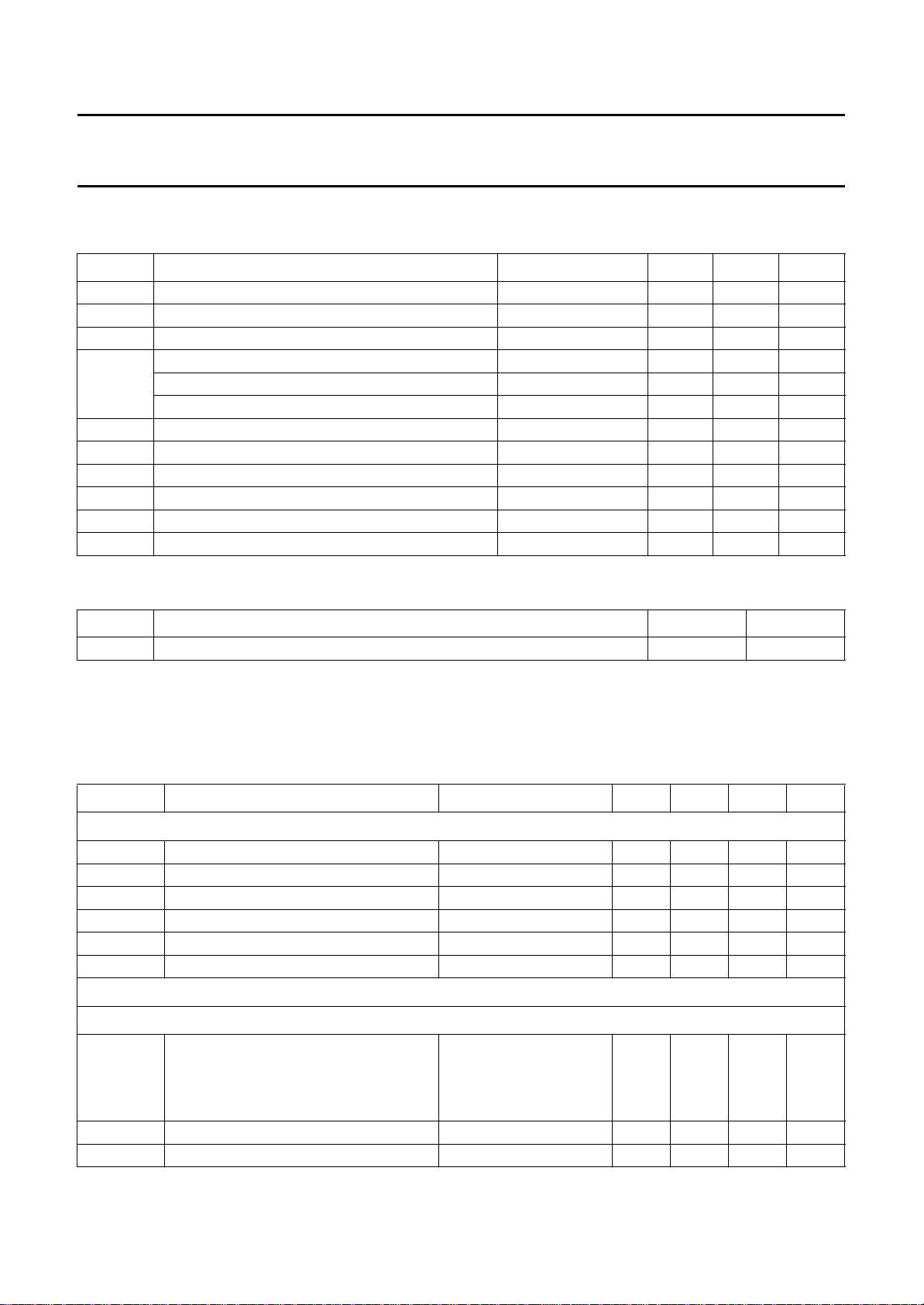

QUICK REFERENCE DATA

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

V

V

V

I

CCA

I

CCD

I

CCO

CCA

CCD

CCO

analog supply voltage 4.75 5.0 5.25 V

digital supply voltage 4.75 5.0 5.25 V

output stages supply voltage 4.75 5.0 5.25 V

analog supply current − 59 70 mA

digital supply current − 28 40 mA

output supply current CL=15pF − 19 28 mA

ILE DC integral linearity error −±0.75 ±1.5 LSB

DLE DC differential linearity error −±0.4 ±1.0 LSB

EB effective bits

(from video input to digital outputs)

f

clk(max)

maximum clock frequency 30 32 − MHz

B maximum −3 dB bandwidth

= 32 MHz;

f

clk

fi= 4.43 MHz

full-scale; 0 dB gain − 15 − MHz

− 7.1 − bits

(input preamplifier)

α

ct

crosstalk between Y and C channels

−−63 −55 dB

and each video input

P

tot

total power dissipation − 530 724 mW

ORDERING INFORMATION

TYPE

NUMBER

NAME DESCRIPTION VERSION

TDA8758G LQFP48 plastic low profile quad flat package; 48 leads; body 7 × 7 × 1.4 mm SOT313-2

1996 Feb 01 2

PACKAGE

Philips Semiconductors Product specification

YC 8-bit low-power analog-to-digital video

interface

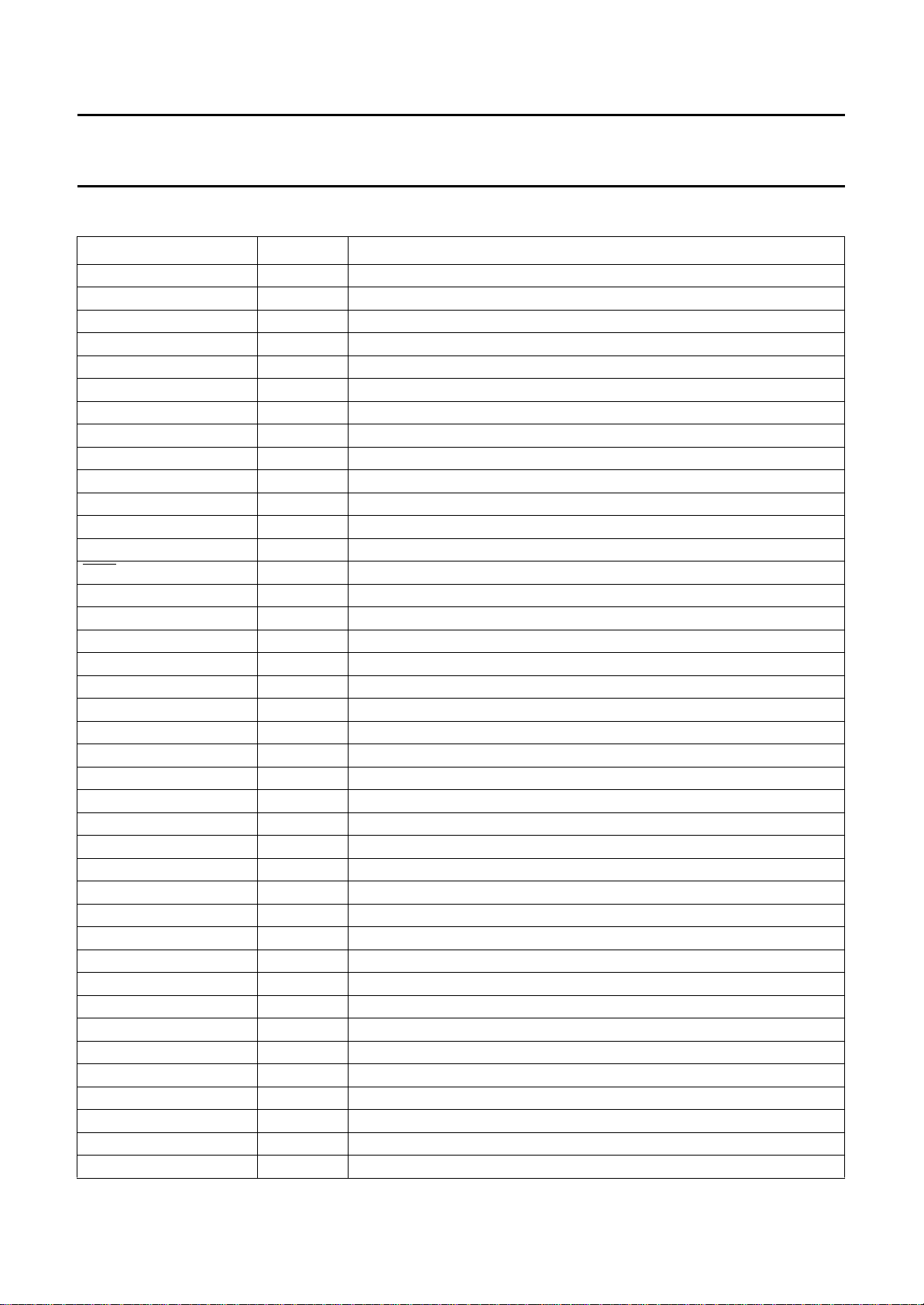

BLOCK DIAGRAM

handbook, full pagewidth

CHROM2

CHROM1

CVBS3

2

4

6

SEL2

5

INPUT

SELECTOR

V

CCD

V

CCA

10 21 41 32

V

V

CCO1

CLAMP

LEVEL 128

CCO2

C

TDA8758

CLPC

V

CCA

REG2

REG1

SDN

ANOUTC

48 45 8 44 17 1 46 15

ADC

COMPARATOR

DEC2

DEC1

TTL

TIMING

GENERATOR

DEC3

TDA8758

8

33

to

40

47

42

C7 to C0

OFC

CLK

Y2/CVBS2

Y1/CVBS1

COMPARATORS

9

11

12 31 43 18 3

SEL1

PWE

AGC &

CLAMP 64

GATE A

GATE B

C

CLPY

713

C

AGC

1614 19 20

ANOUTY

ADC TTL

OGND2

DGND

OGND1

22

23

30

AGND

to

OFY

Y7 to Y0

8

MGB469 - 1

Fig.1 Block diagram.

1996 Feb 01 3

Philips Semiconductors Product specification

YC 8-bit low-power analog-to-digital video

interface

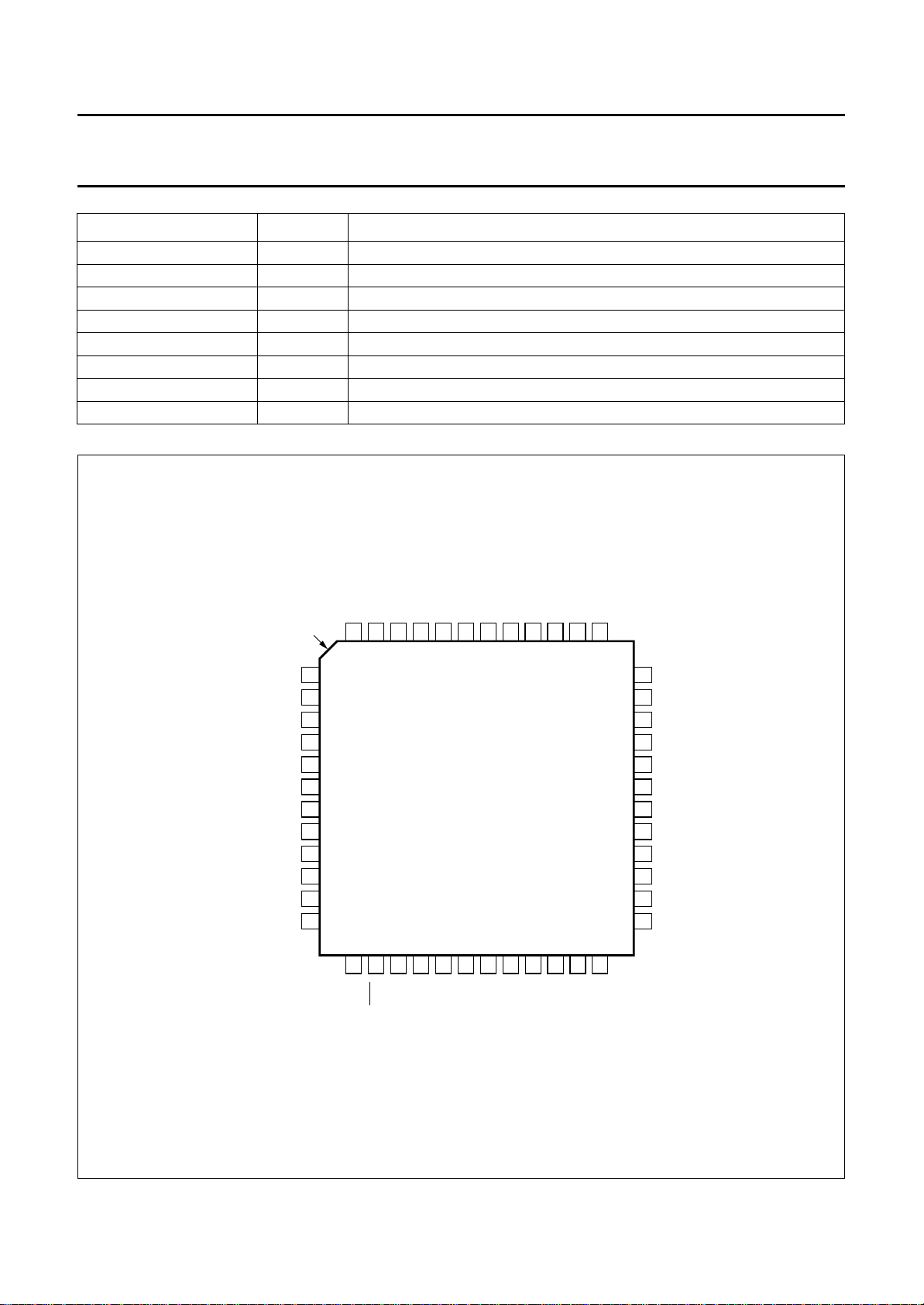

PINNING

SYMBOL PIN DESCRIPTION

DEC1 1 decoupling input 1

CHROM2 2 chrominance analog voltage input 2

AGND 3 analog ground

CHROM1 4 chrominance analog voltage input 1

SEL2 5 selection control input 2

CVBS3 6 luminance analog voltage input 3

C

CLPY

SDN 8 stabilizer decoupling node

Y2/CVBS2 9 luminance analog voltage input 2

V

CCA

Y1/CVBS1 11 luminance analog voltage input 1

SEL1 12 selection control input 1

C

AGC

PWE 14 peak white enable input (active LOW)

DEC3 15 decoupling input 3

ANOUTY 16 analog output for Y channel

REG2 17 decoupling input 2 (internal stabilization loop decoupling)

DGND 18 digital ground

GATE A 19 AGC control input

GATE B 20 clamp control input

V

CCD

OFY 22 Y channel output format/chip enable (3-state input)

Y7 23 Y channel data output; bit 7 (MSB)

Y6 24 Y channel data output; bit 6

Y5 25 Y channel data output; bit 5

Y4 26 Y channel data output; bit 4

Y3 27 Y channel data output; bit 3

Y2 28 Y channel data output; bit 2

Y1 29 Y channel data output; bit 1

Y0 30 Y channel data output; bit 0 (LSB)

OGND2 31 output ground 2

V

CCO2

C7 33 C channel data output; bit 7 (MSB)

C6 34 C channel data output; bit 6

C5 35 C channel data output; bit 5

C4 36 C channel data output; bit 4

C3 37 C channel data output; bit 3

C2 38 C channel data output; bit 2

C1 39 C channel data output; bit 1

C0 40 C channel data output; bit 0 (LSB)

7 Y channel clamping capacitor

10 analog supply voltage (+5 V)

13 AGC capacitor

21 digital supply voltage (+5 V)

32 output supply voltage 2 (+5 V)

TDA8758

1996 Feb 01 4

Philips Semiconductors Product specification

YC 8-bit low-power analog-to-digital video

interface

SYMBOL PIN DESCRIPTION

V

CCO1

CLK 42 clock input

OGND1 43 output ground 1

REG1 44 decoupling input 1 (internal stabilization loop decoupling)

ANOUTC 45 analog output for C channel

DEC2 46 decoupling input 2

OFC 47 C channel output format/chip enable (3-state input)

C

CLPC

41 output supply voltage 1 (+5 V)

48 C channel clamping capacitor

TDA8758

handbook, full pagewidth

pin 1

index

corner

DEC1

CHROM2

AGND

CHROM1

SEL2

CVBS3

C

CLPY

SDN

Y2/CVBS2

V

CCA

Y1/CVBS1

SEL1

CLPC

OFC

DEC2

ANOUTC

REG1

45

44

TDA8758

16

17

REG2

ANOUTY

OGND1

DGND

C

48

47

46

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

AGC

PWE

DEC3

C

43

18

CCO1

CLK

V

42

41

19

20

GATE A

GATE B

C0C1C2

40

39

38

21

22

23

Y7

OFY

CCD

V

C3

24 37

Y6

36

35

34

33

32

31

30

29

28

27

26

25

MGB470

C4

C5

C6

C7

V

CCO2

OGND2

Y0

Y1

Y2

Y3

Y4

Y5

1996 Feb 01 5

Fig.2 Pin configuration.

Philips Semiconductors Product specification

YC 8-bit low-power analog-to-digital video

interface

FUNCTIONAL DESCRIPTION

The TDA8758 provides a simple interface between CVBS

or Y/C analog signals and a digital colour decoder.

Video inputs selection

The input selector allows a choice from different video

sources, and has one of the following configurations:

A: Two Y/C and one CVBS signals

B: One Y/C and two CVBS signals

C: Three CVBS signals (only the Y channel is used).

The wiring of the five video inputs (pins 2, 4, 6, 9 and 11)

and the control of the two selection inputs (pins 5 and 12)

will depend on the available video sources.

• In configuration A, connect as follows:

– Y1 to pin 11

– C1 to pin 4

– Y2 to pin 9

– C2 to pin 2

– CVBS3 to pin 6.

Keep SEL2 (pin 5) LOW and select Y1/C1 or Y2/C2 by

switching SEL1 (pin 12).

CVBS3 is selected with SEL1 and SEL2 HIGH.

• In configuration B, replace Y1 (or Y2) by a CVBS input

(no more C1 or C2). The selection mode is the same.

• In configuration C, connect as follows:

– CVBS1 to pin 11

– CVBS2 to pin 9

– CVBS3 to pin 6.

Use both SEL1 and SEL2 to select inputs.

TDA8758

Synchronization pulses

GATE A and GATE B pulses are synchronization pulses

occurring during the sync period and rear porch

respectively. They should be distinct.

On the Y channel, the digital output of the ADC is

compared to internal digital reference levels. The resultant

outputs control the charge or discharge current of a

capacitor connected to the C

this capacitor controls the gain of the video amplifier.

This is the control loop.

The sync level comparator is active during a positive-going

pulse at the GATE A input. This means that sync pulse of

the composite video signal is used as an amplitude

reference. The bottom of the sync pulse is adjusted to

obtain a digital output of logic 1 at the converter Y output.

As the black level is digital level 64, the sync pulse will

have a digital amplitude of 64 LSBs.

The Peak White control loop is active when the selection

PWE is LOW. Then, if the Y video signal exceeds the

pin

digital code of 255, it will be limited to avoid any over-range

of the converter.

The clamp level control is accomplished by using the same

techniques as used for the gain control. On both Y and C

channels, the black level digital comparators are active

during a positive-going pulse at the GATE B input. On the

Y channel, the clamping capacitor connected to the C

pin will be charged or discharged to adjust the digital

output to code 64. On the C channel, the clamping

capacitor connected to the C

discharged to adjust the digital output to code 128.

pin. The voltage across

AGC

pin will be charged or

CLPC

CLPY

Remark: the video inputs selection is a static selection.

1996 Feb 01 6

Philips Semiconductors Product specification

YC 8-bit low-power analog-to-digital video

TDA8758

interface

LIMITING VALUES

In accordance with the Absolute Maximum Rating System (IEC 134).

SYMBOL PARAMETER CONDITIONS MIN. MAX. UNIT

V

CCA

V

CCD

V

CCO

∆V

V

I

V

clk(p-p)

I

O

T

stg

T

amb

T

j

CC

analog supply voltage −0.3 +7.0 V

digital supply voltage −0.3 +7.0 V

output supply voltage −0.3 +7.0 V

supply voltage difference between V

supply voltage difference between V

supply voltage difference between V

CCA

CCO

CCA

and V

and V

and V

CCD

CCD

CCO

−1.0 +1.0 V

−1.0 +1.0 V

−1.0 +1.0 V

input voltage referenced to AGND − 5.0 V

AC input voltage for switching (peak-to-peak value) referenced to DGND − V

CCO

V

output current − +6 mA

storage temperature −55 +150 °C

operating ambient temperature 0 +70 °C

junction temperature − +150 °C

THERMAL CHARACTERISTICS

SYMBOL PARAMETER VALUE UNIT

R

th j-a

thermal resistance from junction to ambient in free air 72 K/W

CHARACTERISTICS

V

CCA=V10

V

CC02=V32

V

CCO

at V

CCA=VCCD=VCCO

to V3= 4.75 to 5.25 V; V

to V31= 4.75 to 5.25 V; AGND and DGND shorted together; V

to V

CCD

= −0.25 to +0.25 V; V

= 5 V and T

CCD=V21

to V

CCA

=25°C; unless otherwise specified.

amb

to V18= 4.75 to 5.25 V; V

= −0.25 to +0.25 V; T

CCO

CCO1=V41

CCA

= 0 to +70 °C; typical values measured

amb

to V43= 4.75 to 5.25 V;

to V

= −0.25 to +0.25 V;

CCD

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

Supplies

V

CCA

V

CCD

V

CCO

I

CCA

I

CCD

I

CCOtot

analog supply voltage 4.75 5.0 5.25 V

digital supply voltage 4.75 5.0 5.25 V

output stages supply voltage 4.75 5.0 5.25 V

analog supply current − 59 70 mA

digital supply current − 28 40 mA

total output supply current CL=15pF − 19 28 mA

Video amplifier inputs

Y1/CVBS1, Y2/CVBS2, CVBS3, CHROM1

V

I(p-p)

input voltage (peak-to-peak value) AGC load with external

AND CHROM2 INPUTS

capacitor; note 1

Y channel 0.7 − 1.4 V

C channel − 1.0 − V

| input impedance fi= 6 MHz − 25 − kΩ

|Z

i

C

I

input capacitance fi= 6 MHz − 2 − pF

1996 Feb 01 7

Loading...

Loading...