Philips tda8740 DATASHEETS

INTEGRATED CIRCUITS

DATA SH EET

TDA8740; TDA8740H

Satellite sound circuit with noise

reduction

Product specification

Supersedes data of November 1992

File under Integrated Circuits, IC02

Philips Semiconductors

October 1994

Philips Semiconductors Product specification

Satellite sound circuit with noise reduction TDA8740; TDA8740H

FEATURES

• Demodulation of main audio signal using wide band PLL

(lock range selectable)

• Demodulation of secondary audio signals using wide

APPLICATIONS

• Satellite receivers

• TV sets

• Video recorders.

band PLL

• HF input selection: two-out-of-eight secondary audio

signals can be selected

• Noise reduction of the secondary audio signals

• Output selection: stereo, language 1, language 2, main

audio and external

GENERAL DESCRIPTION

The TDA8740; TDA8740H is a multi-function sound IC for

use in satellite receivers, television sets and video

recorders. The pin numbers given in parenthesis

throughout this document refer to the QFP44 package.

• Mute control

• Line outputs (SCART level).

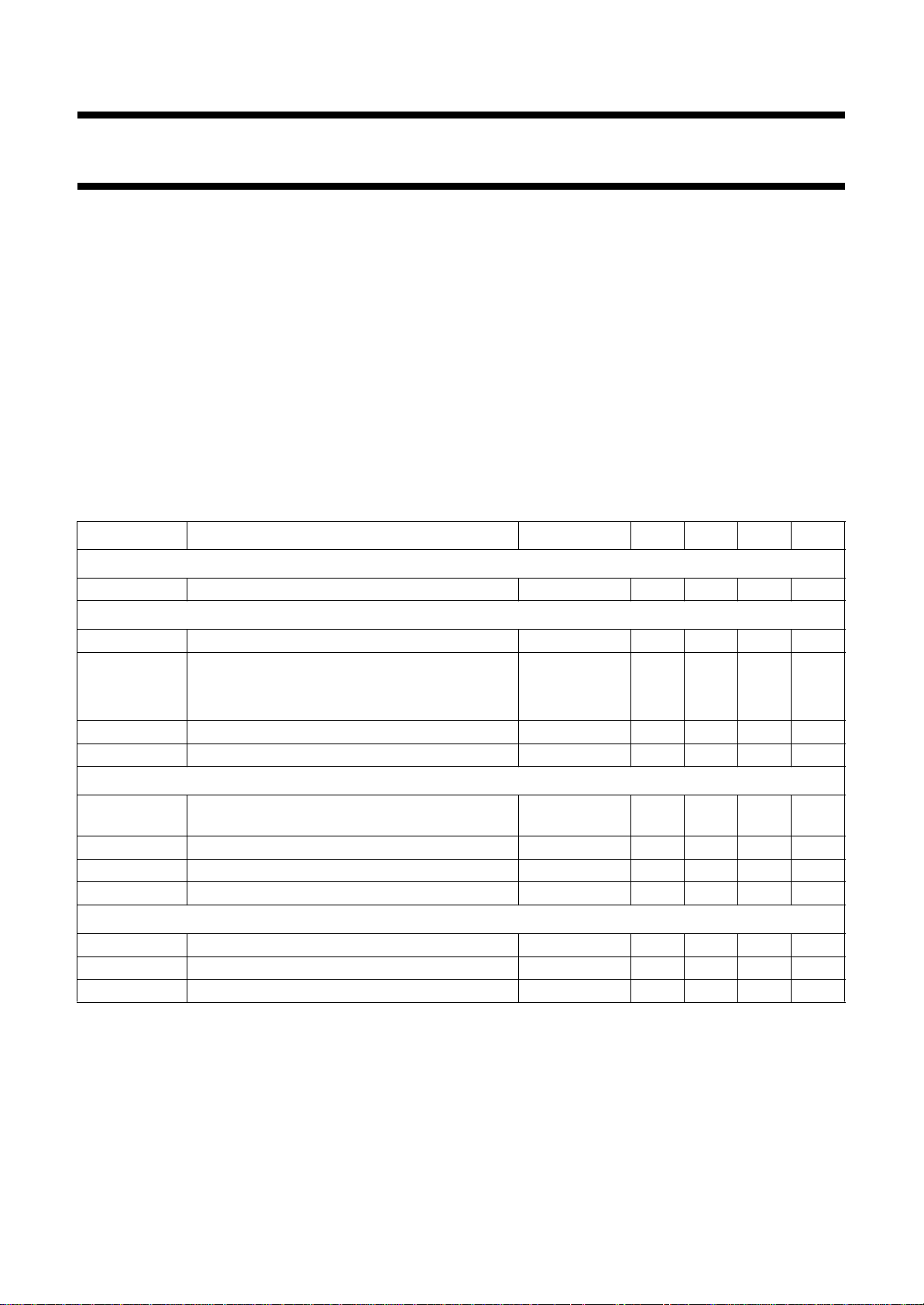

QUICK REFERENCE DATA

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

Supply

V

P

supply voltage 8 12 13.2 V

Main channel

V

IN3(rms)

∆f

OM

input sensitivity pin 18 (14) (RMS value) S/N(A) = 40 dB − 1.0 2.0 mV

lock range PLL demodulator

either 5.5 − 7.5 MHz

or 10.0 − 11.5 MHz

V

OM

output voltage pin 23 (19) −9 −6 −4 dBV

S/N(A) signal-to-noise ratio A-weighted 62 70 − dB

Secondary channels

V

IN1,IN2

input sensitivity pins 2, 4, 6, 8, 10, 12, 14 and 16

S/N(A) = 40 dB − 0.8 1.5 mV

(1, 3, 5, 7, 9, 11, 40 and 42) (RMS value)

∆f

V

OR,OL

OS1,2

lock range PLL demodulators 6.0 − 8.5 MHz

output voltage pins 24 and 25 (20 and 21) −8 −6 −4 dBV

S/N(A) signal-to-noise ratio A-weighted 72 80 − dB

Crosstalk

α

S/M

α

M/S

α

S/S

crosstalk from secondary to main channel − 74 − dB

crosstalk from main to secondary channel − 74 − dB

crosstalk between secondary channels − 74 − dB

October 1994 2

Philips Semiconductors Product specification

Satellite sound circuit with noise reduction TDA8740; TDA8740H

ORDERING INFORMATION

TYPE NUMBER

TDA8740 SDIP42 plastic shrink dual in-line package; 42 leads (600 mil) SOT270-1

TDA8740H QFP44

Note

1. When using IR reflow soldering it is recommended that the Drypack instructions in the

(order number 9398 510 63011) are followed.

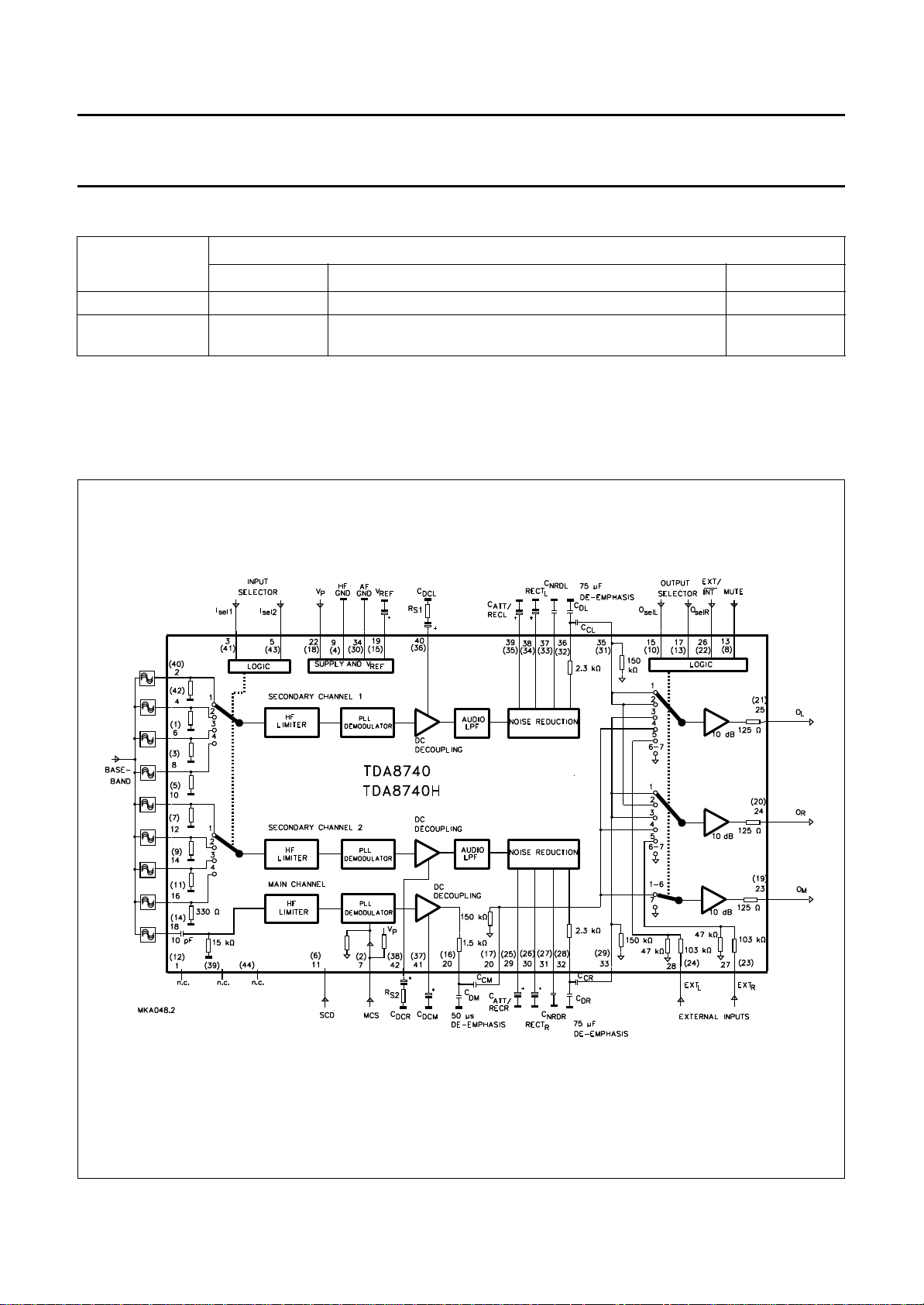

BLOCK DIAGRAM

NAME DESCRIPTION VERSION

(1)

plastic quad flat package; 44 leads (lead length 1.3 mm);

body 10 × 10 × 1.75 mm

PACKAGE

“Quality Reference Handbook”

SOT307-2

The pin numbers in parenthesis refer to the QFP44 package.

October 1994 3

Fig.1 Block diagram.

Philips Semiconductors Product specification

Satellite sound circuit with noise reduction TDA8740; TDA8740H

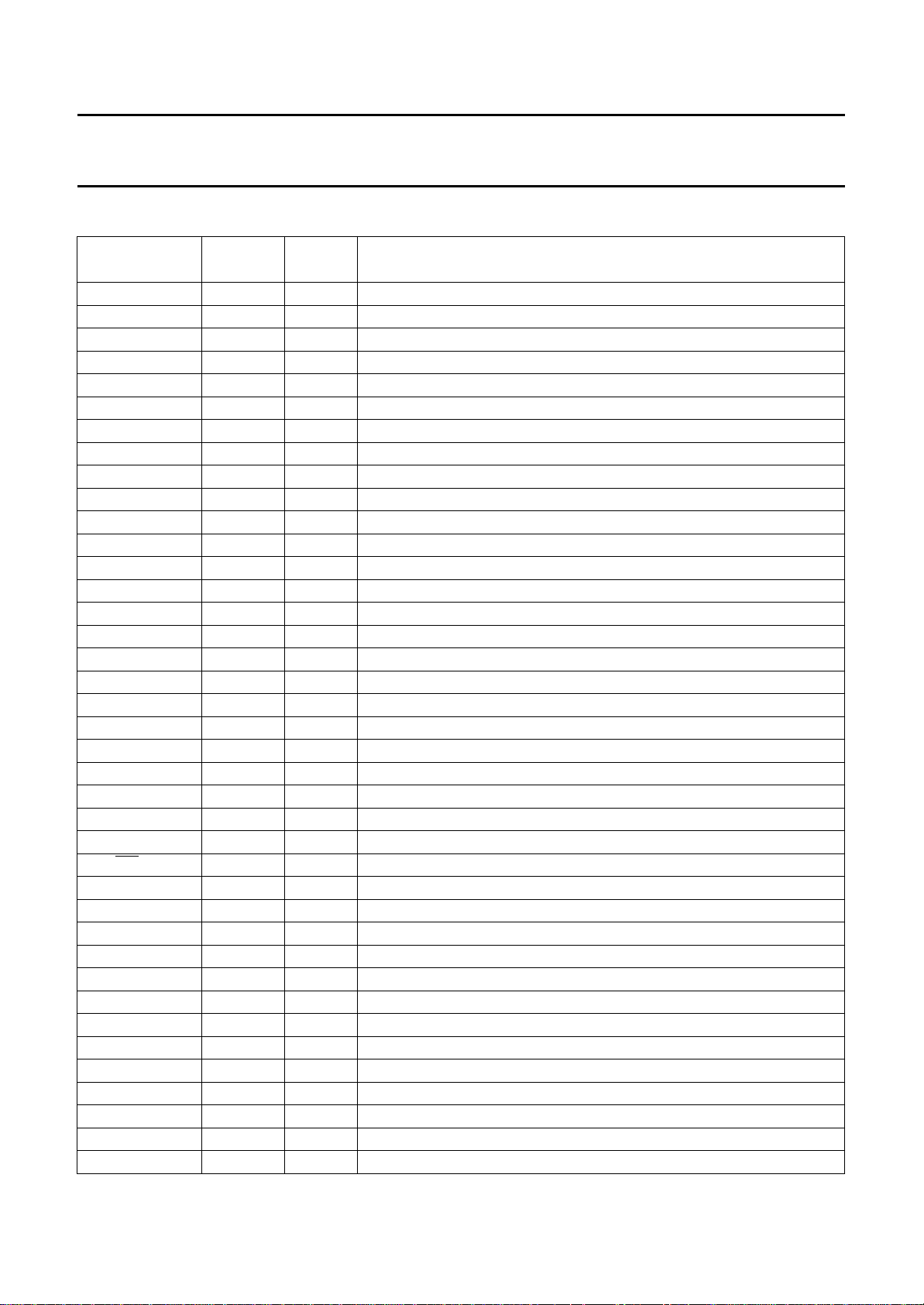

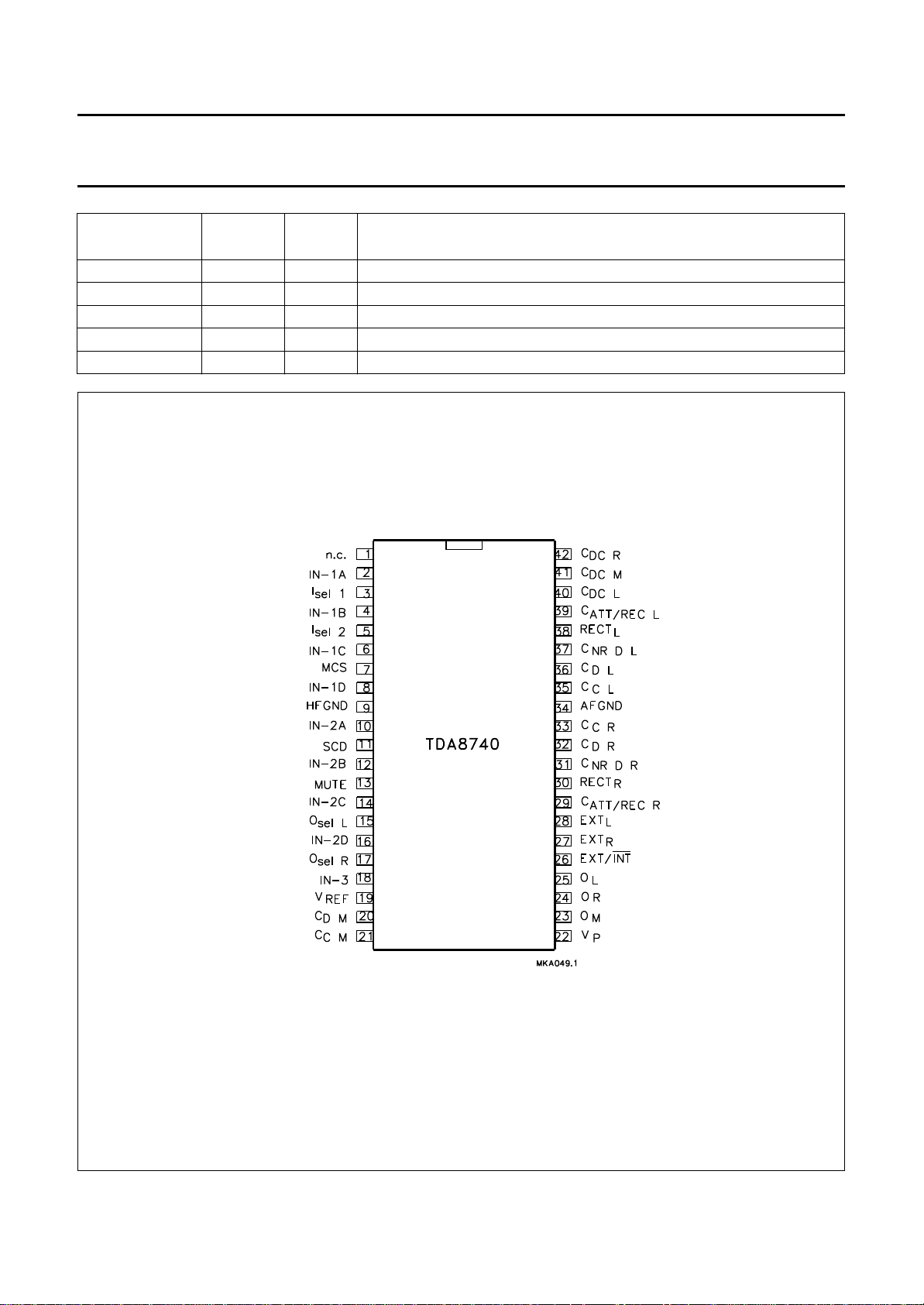

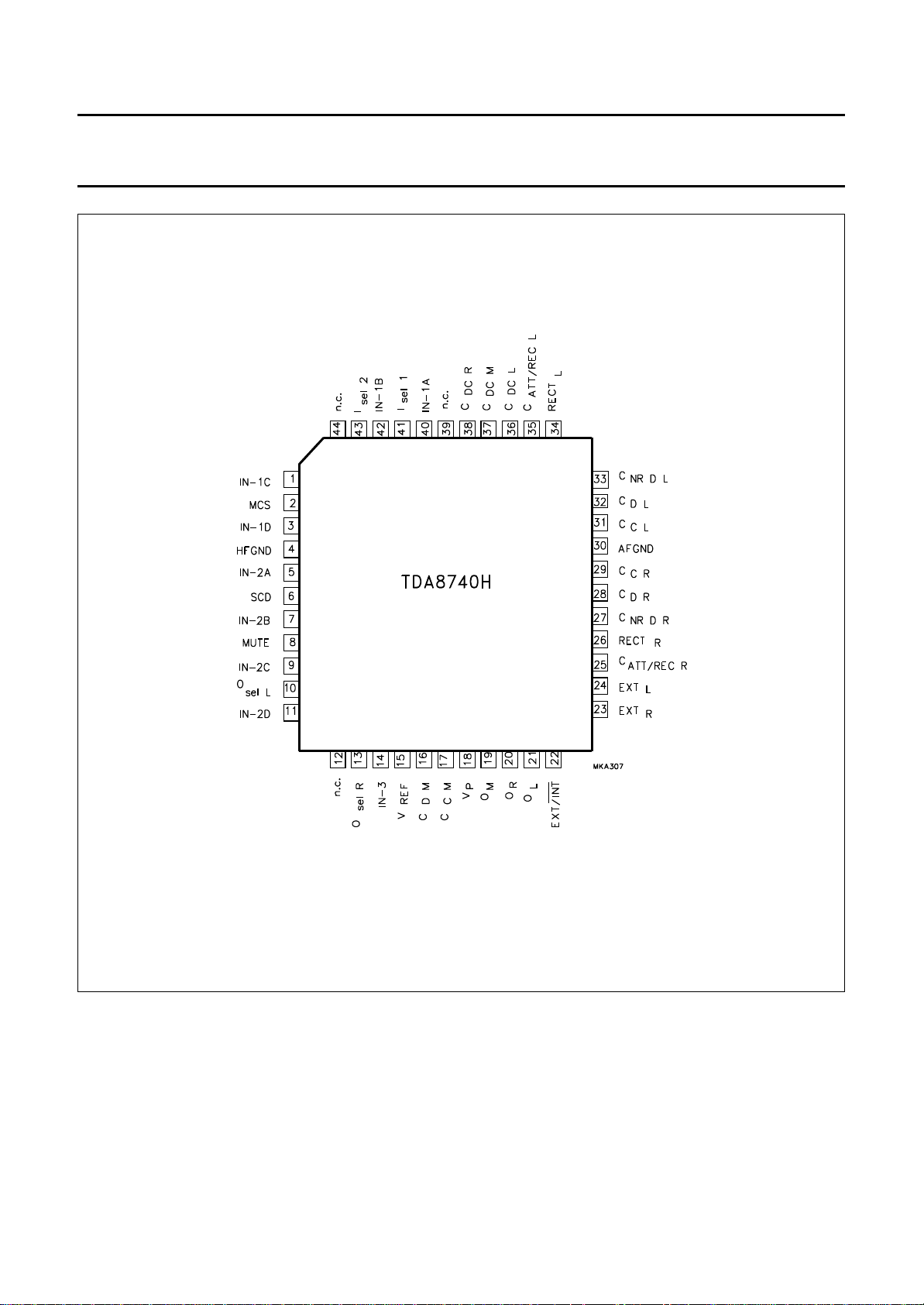

PINNING

SYMBOL

PIN

SDIP42

PIN

QFP44

DESCRIPTION

n.c. 1 39 not connected

IN-1A 2 40 intercarrier input A for Channel 1 (left)

I

sel 1

3 41 input select switch bit 1

IN-1B 4 42 intercarrier input B for Channel 1 (left)

I

sel 2

5 43 input select switch bit 2

IN-1C 6 1 intercarrier input C for Channel 1 (left)

MCS 7 2 main channel PLL lock-in range select/disable

IN-1D 8 3 intercarrier input D for Channel 1 (left)

HFGND 9 4 ground for HF section

IN-2A 10 5 intercarrier input A for Channel 2 (right)

SCD 11 6 secondary channels PLLs disable

IN-2B 12 7 intercarrier input B for Channel 2 (right)

MUTE 13 8 mute switch

IN-2C 14 9 intercarrier input C for Channel 2 (right)

O

sel L

15 10 output select switch bit 1 (left)

IN-2D 16 11 intercarrier input D for Channel 2 (right)

O

sel R

17 13 output select switch bit 2 (right)

IN-3 18 14 intercarrier input for main channel

V

REF

C

D M

C

C M

V

P

O

M

O

R

O

L

INT 26 22 output switch bit 3 (external/internal)

EXT/

EXT

R

EXT

L

C

ATT/REC R

RECT

R

C

NR D R

C

D R

C

C R

19 15 decoupling capacitor for reference voltage

20 16 de-emphasis capacitor for main channel

21 17 audio pass-through capacitor input for main channel

22 18 positive supply voltage

23 19 main channel output

24 20 right channel output

25 21 left channel output

27 23 external audio input (right)

28 24 external audio input (left)

29 25 attack/recovery capacitor (right)

30 26 rectifier DC decoupling (right)

31 27 noise reduction de-emphasis capacitor (right)

32 28 fixed de-emphasis capacitor (right)

33 29 audio pass-through capacitor input for right channel

AFGND 34 30 ground for AF section

C

C L

C

D L

C

NR D L

RECT

C

ATT/REC L

L

35 31 audio pass-through capacitor input for left channel

36 32 fixed de-emphasis capacitor (left)

37 33 noise reduction de-emphasis capacitor (left)

38 34 rectifier DC decoupling (left)

39 35 attack/recovery capacitor (left)

October 1994 4

Philips Semiconductors Product specification

Satellite sound circuit with noise reduction TDA8740; TDA8740H

C

C

C

DC L

DC M

DC R

SYMBOL

PIN

SDIP42

40 36 DC decoupling capacitor (left)

41 37 DC decoupling capacitor (main)

42 38 DC decoupling capacitor (right)

PIN

QFP44

n.c. − 12 not connected

n.c. − 44 not connected

DESCRIPTION

October 1994 5

Fig.2 Pin configuration (SDIP42).

Philips Semiconductors Product specification

Satellite sound circuit with noise reduction TDA8740; TDA8740H

October 1994 6

Fig.3 Pin configuration (QFP44).

Philips Semiconductors Product specification

Satellite sound circuit with noise reduction TDA8740; TDA8740H

FUNCTIONAL DESCRIPTION

Satellite sound

The baseband signal coming from a satellite tuner

contains the demodulated video signal plus a number of

sound carriers to facilitate reception of a

PAL/NTSC/SECAM satellite signal.

Nearest to the video signal is the main sound carrier which

carries the single channel sound related to the video. This

is an FM modulated carrier with a fixed pre-emphasis. The

carrier frequency can be in the range of 5.8 to 6.8 MHz.

Additionally, a number of optional secondary sound

carriers may be present which can be used for stereo or

multi-language sound related to the video, or for unrelated

radio sound. These carriers are also FM modulated, but for

better sound quality (improved signal-to-noise

performance) broadcast satellites (e.g. ‘ASTRA’) use a

noise reduction system (adaptive pre-emphasis circuit,

combined with a fixed pre-emphasis).

These secondary carrier frequencies can be in the range

of 6.30 to 8.28 MHz. The TDA8740; H contains all circuitry

for processing the main channel and for two secondary

channels, from baseband signal to line (SCART) output

drivers. The desired frequencies can be routed to the

TDA8740; H via bandpass filters.

Main channel (see Fig.1)

The lock-in range of the main channel PLL can be

switched between 5.5 to 7.5 MHz, PLL off and 10.0 to

11.5 MHz using the MCS signal at pin 7 (2) [when pin 7 (2)

is at logic 0, being a voltage from 0 to 1.2 V, the lock-in

range = 5.5 to 7.5 MHz; when pin 7 (2) is at logic 1, being

a voltage from 3.5 V until V

11.5 MHz; when pin 7 (2) is in the mid voltage position,

being a voltage from 1.8 to 2.8 V, the main channel PLL is

switched off]. The mid voltage position of the MCS pin can

also be obtained by a floating MCS pin if the circuit supply

voltage Vp is 10.8 to 13.2 V. The voltage on the MCS pin

is then determined by the resistor divider at this pin

between VP and ground.

If only one fixed carrier frequency for the main channel is

to be demodulated (e.g. 6.5 MHz), the lock-in range of the

PLL should be switched to 5.5 to 7.5 MHz. The baseband

signal is applied to the main channel input, pin 18 (14) via

a 6.5 MHz ceramic bandpass filter. Alternatively, if there is

a requirement to demodulate different main channel

frequencies, these frequencies can be transferred to a

fixed intermediate frequency (e.g. 10.7 MHz) using an

external mixer and oscillator-frequency synthesizer. In this

event the lock-in range of the PLL should be switched to

, the lock-in range = 10.0 to

P

10.0 to 11.5 MHz. The IF signal is applied to the main

channel input, pin 18 (14) via a 10.7 MHz ceramic

bandpass filter.

The filtered signal is AC-coupled to a limiter/amplifier and

then to a PLL demodulator. The PLL FM demodulator

ensures that the demodulator is alignment-free. High gain

and DC error signals from the PLL, which are

superimposed on the demodulator output, require DC

decoupling. A buffer amplifier is used to amplify the signal

to the same level as the secondary channels and

decouples DC using an electrolytic capacitor connected to

pin 41 (37). The demodulator output signal is fed to pin 20

(16) via an internal resistor. The output signal can be

de-emphasized by means of this resistor and an external

capacitor connected to ground.

Capacitor value = de-emphasis time constant per 1500

(for 50 µs: 33 nF).

From here the signal is fed to the output selectors. The

signal is amplified to 500 mV(RMS) (i.e. −6 dBV) in the

output amplifiers.

Secondary channels

Up to eight secondary channel inputs are available at pins

2, 4, 6, 8, 10, 12, 14 and 16 (1, 3, 5, 7, 9, 11, 40 and 42).

External ceramic bandpass filters tuned to the required

secondary sound carrier frequencies route these signals to

the inputs.

For stereo applications the TDA8740; TDA8740H contains

two identical secondary sound processing channels. For

each channel it is possible to select from four inputs (IN-A,

IN-B, IN-C and IN-D) using the input selector (see Logic

Table 1). With the input switch several stereo signals or

languages can be selected for demodulation. It should be

noted that the inputs are identical and can be freely

interchanged. Secondary Channel 1 will also be referred

to as ‘LEFT’ or ‘LANGUAGE 1’ and secondary Channel 2

will also be referred to as ‘RIGHT’ or ‘LANGUAGE 2’.

From the input selector switch the signals are coupled to

limiter/amplifiers and then to the PLL demodulators.

Processing is similar to the main channel. The

demodulator output signal is amplified in a buffer amplifier

and DC decoupled using electrolytic capacitors connected

to pins 40 (36) (left) and 42 (38) (right). The output level is

set with a 220 Ω resistor connected in series with the

capacitor.

High frequency components in the amplified PLL output

signal are filtered out in the audio LPF block (4th order

Butterworth low-pass filter) to prevent unwanted influence

on the noise reduction.

October 1994 7

Loading...

Loading...