Philips TDA8376A-N2, TDA8376-N1 Datasheet

DATA SH EET

Objective specification

File under Integrated Circuits, IC02

1996 Jan 26

INTEGRATED CIRCUITS

TDA8376; TDA8376A

I

2

C-bus controlled PAL/NTSC TV

processors

1996 Jan 26 2

Philips Semiconductors Objective specification

I2C-bus controlled PAL/NTSC TV processors

TDA8376; TDA8376A

CONTENTS

1 FEATURES

2 GENERAL DESCRIPTION

3 QUICK REFERENCE DATA

4 ORDERING INFORMATION

5 BLOCK DIAGRAM

6 PINNING

7 FUNCTIONAL DESCRIPTION

7.1 Video switches

7.2 Integrated video filters, peaking and black

stretcher

7.3 Synchronization circuit

7.4 Colour decoder

7.5 RGB output circuit and black-current

stabilization

8I

2

C-BUS SPECIFICATION

8.1 Start-up procedure

8.2 Inputs

8.2.1 Input control bits

8.2.2 Output control bits

9 LIMITING VALUES

10 THERMAL CHARACTERISTICS

11 QUALITY SPECIFICATION

11.1 Latch-up

12 CHARACTERISTICS

13 TEST AND APPLICATION INFORMATION

13.1 East-West output stage

13.2 Adjustment of geometry control parameters

14 PACKAGE OUTLINES

15 SOLDERING

15.1 Introduction

15.2 SDIP

15.2.1 Soldering by dipping or by wave

15.2.2 Repairing soldered joints

15.3 QFP

15.3.1 Reflow soldering

15.3.2 Wave soldering

15.3.3 Repairing soldered joints

16 DEFINITIONS

17 LIFE SUPPORT APPLICATIONS

18 PURCHASE OF PHILIPS I2C COMPONENTS

1996 Jan 26 3

Philips Semiconductors Objective specification

I2C-bus controlled PAL/NTSC TV processors

TDA8376; TDA8376A

1 FEATURES

• Source selection with 2 CVBS inputs and a Y/C (or extra

CVBS) input

• Output signals of the video switch circuit for the teletext

decoder and a Picture-In-Picture (PIP) processor

• Video identification circuit which is independent of the

synchronization for stable On Screen Display (OSD)

under ‘no-signal’ conditions

• Integrated chrominance trap with pre-shoot

compensation and bandpass filters (automatically

calibrated)

• Integrated luminance delay line

• Asymmetrical peaking in the luminance channel with a

(defeatable) noise coring function

• Black stretcher circuit in the luminance channel

• PAL/NTSC colour decoder with automatic search

system

• Easy interfacing with the TDA8395 (SECAM decoder)

for multistandard applications

• RGB control circuit with black-current stabilization and

white point adjustment; to obtain a good grey scale

tracking the black-current ratio of the 3 guns depends on

the white point adjustment

• Two linear RGB inputs and fast blanking

• Horizontal synchronization with two control loops and

alignment-free horizontal oscillator

• Vertical count-down circuit

• Geometry correction by modulation of the vertical and

E-W drive

• Vertical and horizontal zoom possibility for 16 : 9

applications (TDA8376A only)

• I

2

C-bus control of various functions

• Low dissipation (700 mW)

• Small amount of peripheral components compared with

competition ICs

• Y, U and V inputs and outputs.

2 GENERAL DESCRIPTION

The TDA8376 and TDA8376A are alignment-free I

2

C-bus

controlled video processors which contain a PAL/NTSC

colour decoder, luminance processor, sync processor,

RGB-control and deflection processor. The circuits have

been designed for use with the baseband chrominance

delay line TDA4665 and for DC-coupled vertical and

East-West (E-W) output stages. Both ICs are pin

compatible. The TDA8376A has a flexible horizontal and

vertical zoom possibility for 16 : 9 applications.

The supply voltage for the ICs is 8 V. The ICs are available

in an SDIP package with 52 pins and in a QFP package

with 64 pins (see Chapter 4).

The pin numbers indicated in this document are

referenced to the SDIP52; SOT247-1 package; unless

otherwise indicated.

1996 Jan 26 4

Philips Semiconductors Objective specification

I2C-bus controlled PAL/NTSC TV processors

TDA8376; TDA8376A

3 QUICK REFERENCE DATA

4 ORDERING INFORMATION

SYMBOL PARAMETER MIN. TYP. MAX. UNIT

Supply

V

P

supply voltage − 8.0 − V

I

P

supply current − 75 − mA

Input voltages

V

9,13(p-p)

CVBS input voltage (peak-to-peak value) − 1.0 − V

V

27(p-p)

S-VHS luminance input voltage (peak-to-peak value) − 1.0 − V

V

6(p-p)

S-VHS chrominance input voltage (burst amplitude) (peak-to-peak

value)

− 0.3 − V

V

i(p-p)

RGB input voltage (peak-to-peak value) − 0.7 − V

Output voltages

V

38(p-p)

TXT output voltage (peak-to-peak value) − 1.0 − V

V

11(p-p)

PIP output voltage (peak-to-peak value) − 1.0 − V

V

30(p-p)

−(R−Y) output voltage (peak-to-peak value) − 525 − mV

V

29(p-p)

−(B−Y) output voltage (peak-to-peak value) − 675 − mV

V

19,20,21(p-p)

RGB output signal voltage amplitudes (peak-to-peak value) − 2.0 − V

Output currents

I

40

horizontal output current 10 −−mA

I

47,48

vertical output current 1 −−mA

I

46

E-W drive output current 0.5 −−mA

TYPE

NUMBER

PACKAGE

NAME DESCRIPTION VERSION

TDA8376 SDIP52 plastic shrink dual in-line package; 52 leads (600 mil) SOT247-1

TDA8376AH QFP64 plastic quad flat package; 64 leads (lead length 1.95 mm);

body 14 × 20 × 2.8 mm

SOT319-2

1996 Jan 26 5

Philips Semiconductors Objective specification

I

2

C-bus controlled PAL/NTSC TV processors

TDA8376; TDA8376A

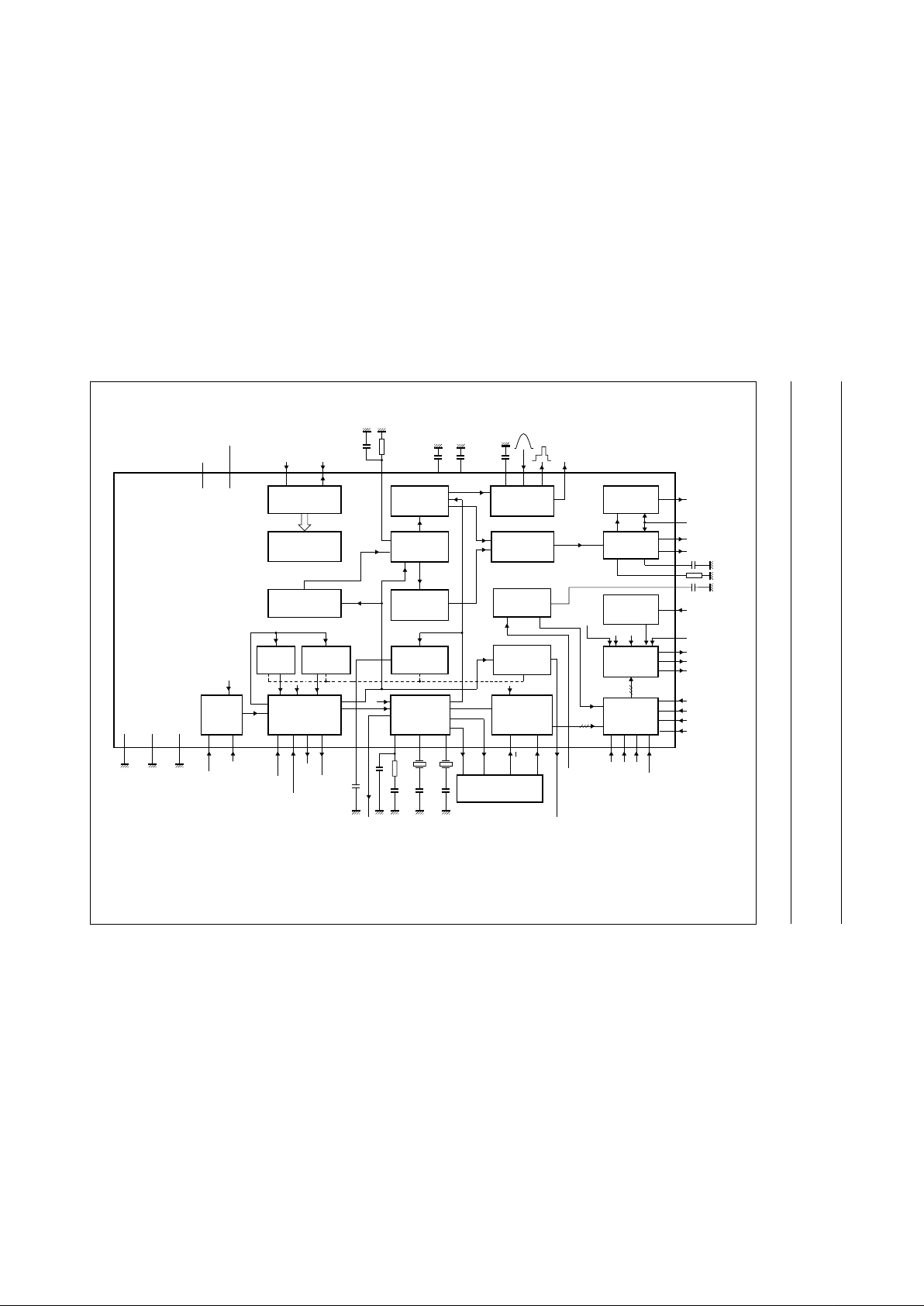

5 BLOCK DIAGRAM

d

book, full pagewidth

MGE078

CVBS

SWITCH

S-VHS SWITCH

BAND PASSTRAP

CONTROL DACs

16 x 6 bits

2 x 4 bits

PAL/NTSC

DECODER

FILTER

TUNING

VERTICAL

SYNC

SEPARATOR

VIDEO

IDENTIFICATION

BLACK

STRETCHER

SYNC

SEPARATOR

AND 1st LOOP

VCO

AND

CONTROL

I

2

C-BUS

TRANSCEIVER

35 34 33

4.4

MHz

3.6

MHz

6 7 11 38 12 36

2nd LOOP AND

HORIZONTAL

OUTPUT

HORIZONTAL/

VERTICAL

DIVIDER

DELAY,

PEAKING AND

CORING

G-Y MATRIX

AND

SAT CONTROL

TDA4665

EW

GEOMETRY

VERTICAL

GEOMETRY

BLACK

CURRENT

STABILIZER

RGB MATRIX

AND

OUTPUT

RGB INPUT

AND

SWITCH

46

BRI CONTR

WHITE

POINT

21

20

19

30 29 32 31 28 27 23 24 25 26

LUMOUT

LUMIN

RI1 GI1 BI1

RGBIN1

CHROMA

CVBS/Y

PIPO

CVBS/TXT

CVBS

EXT

DEC

FT

DET

XTAL2 XTAL1

DEC

DIG

DEC

BG

GND2

GND1

GND3

PH1LF

CVBS

INT

913

SW

SCL

V

P1

(+8 V)

V

P2

(+8 V)

SDA

34 44

454210

51837 43 41 39 40

HOUT

SCO

FBI

PH2LF

ref

ref

HUE

SW

SAT

RO

GO

BO

22

BCLIN

18

BLKIN

51

2

50

48

47

49

EWD

EHTO

VDR

(p)

VSC

C

BLK

VDR

(n)

SEC

ref

14

15

16

17

RGBIN2

RI2

GI2

BI2

RYO BYO BYIRYI

TDA8376(A)

I

ref

Fig.1 Block diagram (SDIP52; SOT247-1).

1996 Jan 26 6

Philips Semiconductors Objective specification

I2C-bus controlled PAL/NTSC TV processors

TDA8376; TDA8376A

6 PINNING

SYMBOL

PIN

DESCRIPTION

SDIP52 QFP64

DEC

DIG

1 11 decoupling digital supply

C

BLK

2 12 black peak hold capacitor

SCL 3 13 I

2

C-bus serial clock input

SDA 4 14 I

2

C-bus serial data input/output

DEC

BG

5 16 band gap decoupling

CHROMA 6 17 chrominance input (S-VHS)

CVBS/Y 7 18 external CVBS/Y input

V

P1

8 20 main supply voltage (+8 V)

CVBS

INT

9 22 internal CVBS input

GND1 10 23 ground 1

PIPO 11 25 picture-in-picture output

DEC

FT

12 26 decoupling filter tuning

CVBS

EXT

13 27 external CVBS input

RGBIN2 14 28 RGB insertion input 2

RI2 15 29 red input 2

GI2 16 30 green input 2

BI2 17 31 blue input 2

BLKIN 18 32 black-current input

BO 19 34 blue output

GO 20 35 green output

RO 21 36 red output

BCLIN 22 37 beam current limiter input

RI1 23 38 red input 1

GI1 24 39 green input 1

BI1 25 40 blue input 1

RGBIN1 26 41 RGB insertion input 1

LUMIN 27 42 luminance input

LUMOUT 28 43 luminance output

BYO 29 44 −(B−Y) signal output

RYO 30 45 −(R−Y) signal output

BYI 31 46 −(B−Y) signal input

RYI 32 47 −(R−Y) signal input

XTAL1 33 49 3.58 MHz crystal connection

XTAL2 34 51 4.43/3.58 MHz crystal connection

DET 35 53 loop filter phase detector

SEC

ref

36 54 SECAM reference output

V

P2

37 55 horizontal oscillator supply voltage (+8 V)

CVBS/TXT 38 56 CVBS/TXT output

1996 Jan 26 7

Philips Semiconductors Objective specification

I2C-bus controlled PAL/NTSC TV processors

TDA8376; TDA8376A

SCO 39 57 sandcastle output

HOUT 40 58 horizontal output

FBI 41 59 flyback input

GND2 42 24 ground 2

PH2LF 43 62 phase-2 filter

PH1LF 44 63 phase-1 filter

GND3 45 60 ground 3

EWD 46 1 east-west drive output

VDR

(p)

47 3 vertical drive 1 positive output

VDR

(n)

48 4 vertical drive 2 negative output

EHTO 49 5 EHT/overvoltage protection input

VSC 50 7 vertical sawtooth capacitor

I

ref

51 8 reference current input

n.c. 52 2 not connected

n.c. − 6 not connected

n.c. − 9 not connected

n.c. − 10 not connected

n.c. − 15 not connected

n.c. − 19 not connected

n.c. − 33 not connected

n.c. − 48 not connected

n.c. − 50 not connected

n.c. − 52 not connected

V

P3

− 21 supply voltage 3 (+8 V)

GND4 − 61 ground 4

GND5 − 64 ground 5

SYMBOL

PIN

DESCRIPTION

SDIP52 QFP64

1996 Jan 26 8

Philips Semiconductors Objective specification

I2C-bus controlled PAL/NTSC TV processors

TDA8376; TDA8376A

Fig.2 Pin configuration (SDIP52).

handbook, halfpage

TDA8376(A)

MGE076

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

DEC

DIG

C

BLK

SCL

SDA

DEC

BG

CHROMA

CVBS/Y

V

P1

CVBS

INT

GND1

PIPO

DEC

FT

CVBS

EXT

RGBIN2

RI2

GI2

BI2

BLKIN

BO

GO

RO

BCLIN

RI1

GI1

BI1

RGBIN1

n.c.

I

ref

VSC

EHTO

VDR

(n)

VDR

(p)

EWD

GND3

PH1LF

PH2LF

GND2

FBI

HOUT

SCO

CVBS/TXT

V

P2

SEC

ref

DET

XTAL2

XTAL1

RYI

BYI

RYO

BYO

LUMOUT

LUMIN

1996 Jan 26 9

Philips Semiconductors Objective specification

I2C-bus controlled PAL/NTSC TV processors

TDA8376; TDA8376A

Fig.3 Pin configuration (QFP64).

handbook, full pagewidth

TDA8376(A)

MGE077

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

EWD

n.c.

VDR

(p)

VDR

(n)

EHTO

n.c.

VSC

I

ref

n.c.

n.c.

DEC

DIG

C

BLK

SCL

SDA

n.c.

DEC

BG

CHROMA

CVBS/Y

n.c.

XTAL2

n.c.

XTAL1

n.c.

RYI

BYI

RYO

BYO

LUMOUT

LUMIN

RGBIN1

BI1

GI1

RI1

BCLIN

RO

GO

BO

n.c.

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

20

21

22

23

24

25

26

27

28

29

30

31

32

64

63

62

61

60

59

58

57

56

55

54

53

52

GND5

PH1LF

PH2LF

GND4

GND3

FBI

HOUT

SCO

CVBS/TXT

V

P2

SEC

ref

DET

n.c.

V

P1

V

P3

CVBS

INT

GND1

GND2

PIPO

DEC

FT

CVBS

EXT

RGBIN2

RI2

GI2

BI2

BLKIN

1996 Jan 26 10

Philips Semiconductors Objective specification

I2C-bus controlled PAL/NTSC TV processors

TDA8376; TDA8376A

7 FUNCTIONAL DESCRIPTION

7.1 Video switches

The circuit has two CVBS inputs and a Super-Video Home

System (S-VHS) input. The input can be chosen by the

I

2

C-bus. The input selector also has a position in which

CVBS

EXT

is processed, unless there is a signal on the

S-VHS input. When the input selector is in this position it

switches to the S-VHS input if the S-VHS detector detects

sync pulses on the S-VHS luminance input. The S-VHS

detector output can be read by the I2C-bus. When the

S-VHS option is not used the luminance input can be used

as a second input for external CVBS signals. The choice is

made via the CVS bit (see Table 1).

The video switch circuit has two outputs which can be

programmed in a different way. The input signal for the

decoder is also available on the TXT output. Therefore this

signal can be used to drive the teletext decoder and the

SECAM add-on decoder. The signal on the PIP output can

be chosen independent of the TXT output. If S-VHS is

selected for one of the outputs the luminance and

chrominance signals are added so that a CVBS signal is

obtained again.

The circuit contains a video identification circuit which

checks whether a video signal is available at the selected

video input. This circuit is independent of the

synchronization circuit. The information of this

identification circuit can also be used to switch the

phase-1 (ϕ1) loop to a low gain when no signal is received

so that a stable OSD display is obtained. The video

identification circuit can be switched on and off via the

I2C-bus.

7.2 Integrated video filters, peaking and black

stretcher

The circuit contains a chrominance bandpass and trap

circuit. The chrominance trap filter in the luminance path is

designed for a symmetrical step response behaviour. The

filters are realized by gyrator circuits and they are

automatically tuned by comparing the tuning frequency

with the crystal frequency of the decoder. The luminance

delay line and the delay for the peaking circuit are also

realized by gyrator circuits. During SECAM reception the

centre frequency of the chrominance trap is set to a value

of approximately 4.2 MHz to obtain a better suppression of

the SECAM carrier frequencies.

The peaking function is achieved by two luminance delay

cells each with a delay of 165 ns. The resulting peaking

frequency is 3 MHz. The peaking is asymmetrical so that

the overshoots in the direction of ‘black’ are approximately

two times higher than those in the direction of ‘white’.

This provides a better picture impression than a

symmetrical peaking. The circuit contains a coring circuit

to prevent the noise content of the video signal being

amplified by the peaking circuit. This coring circuit can be

switched-off when required.

It is possible to connect a Colour Transient Improvement

(CTI) or Picture Signal Improvement (PSI) IC to the

TDA8376. The luminance signal which has passed the

filter and delay line circuit is available externally. The

output signal of the transient improvement circuit must be

applied to the luminance input circuit. When the CTI

function is not required the two pins must be AC-coupled.

The luminance signal below 50 IRE can be stretched in

accordance with the difference between the peak black

level and the blanking level of the back-porch of the video

signal. The black level stretcher can be switched-off by

connecting pin 2 to the positive supply line.

7.3 Synchronization circuit

The sync separator is preceded by a controlled amplifier

which adjusts the sync pulse amplitude to a fixed level.

These pulses are fed to the slicing stage which is operating

at 50% of the amplitude.

The separated sync pulses are fed to the first phase

detector and to the coincidence detector. This coincidence

detector is only used to detect whether the line oscillator is

synchronized and not for transmitter identification. The first

Phase-Locked Loop (PLL) has a very high-statical

steepness so that the phase of the picture is independent

of the line frequency. To prevent the horizontal

synchronization being disturbed by anti-copy signals such

as Macrovision the phase detector is gated during the

vertical retrace period so that pulses during scan have no

effect on the output voltage. The position of this pulse is

asymmetrical and the width is approximately 22 µs.

The horizontal output signal is generated by an oscillator

which operates at twice the line frequency. Its frequency is

divided-by-two to lock the first control loop to the incoming

signal. The time-constant of the loop can be forced by the

I

2

C-bus (fast or slow). If required the IC can select the

time-constant depending on the noise content of the

incoming video signal. The free-running frequency of the

oscillator is determined by a digital control circuit which is

locked to the reference signal of the colour decoder. When

the IC is switched on the horizontal output signal is

suppressed and the oscillator is calibrated as soon as all

subaddress bytes have been sent. When the frequency of

the oscillator is correct the horizontal drive signal is

switched on.

1996 Jan 26 11

Philips Semiconductors Objective specification

I2C-bus controlled PAL/NTSC TV processors

TDA8376; TDA8376A

To obtain a smooth switching-on and switching-off

behaviour of the horizontal output stage the horizontal

output frequency is doubled during switch-on and

switch-off (slow start/stop). During that time the duty factor

of the output pulse has such a value that maximum safety

is obtained for the output stage

To protect the horizontal output transistor the horizontal

drive is switched off when a power-on reset is detected.

The drive signal is switched on again when the normal

switch-on procedure is followed, i.e. all sub-address bytes

must be sent and, after calibration, the horizontal drive

signal will be released again via the slow start procedure.

When the coincidence detector indicates an out-of-lock

situation the calibration procedure is repeated.

The circuit has a second control loop to generate the drive

pulses for the horizontal driver stage. To prevent the

horizontal output transistor being switched on during

flyback the horizontal drive output is gated with the flyback

pulse.

The vertical sawtooth generator drives the vertical output

and E-W correction drive circuits. The geometry

processing circuits provide control of horizontal shift, E-W

width, E-W parabola/width ratio, E-W corner/parabola

ratio, trapezium correction, vertical shift, vertical slope,

vertical amplitude, and the S-correction. All these controls

can be set via the I2C-bus. The geometry processor has a

differential current output for the vertical drive signal and a

single-ended output for the E-W drive. Both the vertical

drive and the E-W drive outputs can be modulated for EHT

compensation. The EHT compensation pin is also used for

overvoltage protection.

The TDA8376A geometry processor also offers the

possibility for a flexible vertical and horizontal zoom mode

for 16 : 9 applications. Because of this feature an

additional control can be added on the remote control so

that the viewer can adjust the picture.

In addition the de-interlace of the vertical output can be set

via the I2C-bus.

To avoid damage of the picture tube when the vertical

deflection fails, the guard output current of the TDA8350

can be supplied to the sandcastle output. When a failure is

detected the RGB-outputs are blanked and a bit is set

(NDF) in the status byte of the I2C-bus. When no vertical

deflection output stage is connected this guard circuit will

also blank the output signals. This can be overruled by the

EVG bit of subaddress 0A (see Table 1).

7.4 Colour decoder

The colour decoder contains an alignment-free crystal

oscillator, a killer circuit and the colour difference

demodulators. The 90° phase shift for the reference signal

is made internally. The demodulation angle and gain ratio

for the colour difference signals for PAL and NTSC are

adapted to the standard.

The colour decoder is very flexible. Together with the

SECAM decoder TDA8395 an automatic multistandard

decoder can be designed. In the automatic mode the

SECAM identification is accepted only when the vertical

frequency is 50 Hz. In the forced mode the system can

also identify signals with a vertical frequency of 60 Hz.

Which standard the IC can decode depends on the

external crystals. If a 4.4 MHz and a 3.5 MHz crystal are

used PAL 4.4, NTSC 4.4, NTSC 3.5 and PAL 3.5 can be

decoded. If two 3.5 MHz crystals are used PAL N and M

can be decoded. If one crystal is connected only

PAL/NTSC 4.4 or PAL/NTSC 3.5 can be decoded. The

crystal frequency of the decoder is used to tune the line

oscillator. Therefore the value of the crystal frequency

must be given to the IC via the I

2

C-bus. For a reliable

calibration of the horizontal oscillator it is very important

that the crystal indication bits (XA and XB) are not

corrupted (see Table 6). For this reason the crystal bits

(SXA and SXB) can be read in the output bytes so that the

software can check the I2C-bus transmissions

(see Table 38).

7.5 RGB output circuit and black-current

stabilization

The colour-difference signals are matrixed with the

luminance signal to obtain the RGB-signals. For the

RGB-inputs linear amplifiers have been chosen so that the

circuit is suited for signals coming from the SCART

connector. The RGB2 inputs (pins 14 to 17) have priority

over the RGB1 inputs (pins 23 to 26). Both fast blanking

inputs can be blocked by I2C-bus controls. The contrast

and brightness controls operate on internal and external

signals.

1996 Jan 26 12

Philips Semiconductors Objective specification

I2C-bus controlled PAL/NTSC TV processors

TDA8376; TDA8376A

The output signal has an amplitude of approximately 2 V

black-to-white at nominal input signals and nominal

settings of the controls.

The black current stabilization is realized by feedback from

the video output amplifiers to the RGB control circuit. The

‘black current’ of the 3 guns of the picture tube is internally

measured and stabilized. The black level control is active

during 4 lines at the end of the vertical blanking. During the

first line the leakage current is measured and the following

3 lines the 3 guns are adjusted to the required level. The

maximum acceptable leakage current is ±100 µA.

The nominal value of the ‘black current’ is 10 µA. The ratio

of the currents for the various guns automatically tracks

with the white point adjustment so that the background

colour is the same as the adjusted white point.

The input impedance of the ‘black-current’ measuring pin

is 15 kΩ. Therefore the beam current during scan will

cause the input voltage to exceed the supply voltage. The

internal protection will start conducting so that the

excessive current is bypassed.

When the TV receiver is switched on the black current

stabilization circuit is not active, the RGB outputs are

blanked and beam current limiting input pin is

short-circuited. Only during the measuring lines will the

outputs supply a voltage of 5 V to the video output stage

so that it can be detected if the picture tube is warming up.

These pulses are switched on after a waiting time of

approximately 0.5 s. This ensures that the vertical

deflection is activated so that the measuring pulses are not

visible on the screen. As soon as the current supplied to

the measuring input exceeds a value of 190 µA the

stabilization circuit is activated. After a waiting time of

approximately 0.8 s the blanking and the beam current

limiting input pin are released. The remaining switch-on

behaviour of the picture is determined by the external time

constant of the beam current limiting network.

8I

2

C-BUS SPECIFICATION

Valid subaddresses: 00 to 13 (TDA8376) or 00 to 16

(TDA8376A); subaddress FE is reserved for test

purposes. Auto-increment mode is available for

subaddresses.

8.1 Start-up procedure

Read the status bytes until POR = 0 and send all

subaddress bytes. The horizontal output signal is switched

on when the oscillator is calibrated.

Each time before the data in the IC is refreshed, the status

bytes must be read. If POR = 1, the procedure previously

mentioned must be carried out to restart the IC.

When this procedure is not followed the horizontal

frequency may be incorrect after power-up or after a

power dip.

handbook, halfpage

MLA743

A6 A5 A4 A3 A2 A1 A0

10001011/0

R/W

Fig.4 Slave address (8A).

1996 Jan 26 13

Philips Semiconductors Objective specification

I2C-bus controlled PAL/NTSC TV processors

TDA8376; TDA8376A

8.2 Inputs

Table 1 Input status bits

Note

1. The bits EXP and CL in subaddress 0C are only valid for the TDA8376. For the TDA8376A these two bits must be

set to logic 0.

Table 2 Output status bits

Note

1. X = don’t care.

FUNCTION

SUBADDRESS

(HEX)

DATA BYTE

D7 D6 D5 D4 D3 D2 D1 D0

Source select 00 INA INB INC IND FOA FOB XA XB

Decoder mode 01 FORF FORS DL STB POC CM2 CM1 CM0

Hue 02 0 0 A5 A4 A3 A2 A1 A0

Horizontal shift (HS) 03 0 0 A5 A4 A3 A2 A1 A0

E-W width (E-W) 04 0 0 A5 A4 A3 A2 A1 A0

E-W parabola/width (PW) 05 0 0 A5 A4 A3 A2 A1 A0

E-W corner parabola (CP) 06 0 0 A5 A4 A3 A2 A1 A0

E-W trapezium (TC) 07 0 0 A5 A4 A3 A2 A1 A0

Vertical slope (VS) 08 NCIN 0 A5 A4 A3 A2 A1 A0

Vertical amplitude (VA) 09 VID LBM A5 A4 A3 A2 A1 A0

S-correction (SC) 0A HCO EVG A5 A4 A3 A2 A1 A0

Vertical shift (VSH) 0B SBL PRD A5 A4 A3 A2 A1 A0

White point R 0C EXP

(1)

CL

(1)

A5 A4 A3 A2 A1 A0

White point G 0D 0 CVS A5 A4 A3 A2 A1 A0

White point B 0E MAT 0 A5 A4 A3 A2 A1 A0

Peaking 0F YD3 YD2 YD1 YD0 A3 A2 A1 A0

Brightness 10 RBL COR A5 A4 A3 A2 A1 A0

Saturation 11 IE1 IE2 A5 A4 A3 A2 A1 A0

Contrast 12 0 0 A5 A4 A3 A2 A1 A0

Spare 13 0 0 000000

Spare 14 0 0 000000

Spare 15 0 0 000000

Vertical zoom (VX, 76A) 16 0 0 A5 A4 A3 A2 A1 A0

FUNCTION

SUBADDRESS

(HEX)

DATA BYTE

D7 D6 D5 D4 D3 D2 D1 D0

Output status bytes 00 POR FSI STS SL XPR CD2 CD1 CD0

01 NDF IN1 IN2 IFI AFA X

(1)

SXA SXB

1996 Jan 26 14

Philips Semiconductors Objective specification

I2C-bus controlled PAL/NTSC TV processors

TDA8376; TDA8376A

8.2.1 INPUT CONTROL BITS

Table 3 Source select 1

Table 4 Source select 2

Table 5 Phase 1 (ϕ1) time constant

Note

1. X = don’t care.

Table 6 Crystal indication XA and XB

INA INB DECODER AND TXT

0 0 CVBS

INT

0 1 CVBS

EXT

1 0 S-VHS

1 1 S-VHS (CVBS

EXT

)

INC IND PIP

0 0 CVBS

INT

0 1 CVBS

EXT

1 0 S-VHS

1 1 S-VHS (CVBS

EXT

)

FOA FOB MODE

0 0 normal

0 1 slow

1X

(1)

fast

XA XB CRYSTAL

0 0 two 3.6 MHz

0 1 one 3.6 MHz (pin 33)

1 0 one 4.4 MHz (pin 34)

1 1 3.6 MHz (pin 33) and

4.4 MHz (pin 34)

Table 7 Forced field frequency

Note

1. When the forced mode is selected the divider will only

switch to that position when the horizontal oscillator is

not synchronized.

Table 8 Interlace

Table 9 Standby

Table 10 Synchronization mode

Table 11 Colour decoder mode

FORF FORS FIELD FREQUENCY

0 0 auto (60 Hz when line not

synchronized)

0 1 60 Hz; note 1

1 0 50 Hz; note 1

1 1 auto

(50 Hz when line not synchronized)

DL STATUS

0 interlace

1 de-interlace

STB MODE

0 standby

1 normal

POC MODE

0 active

1 not active

CM2 CM1 CM0 DECODER MODE

0 0 0 not forced, own intelligence

0 0 1 forced NTSC 3.6 MHz

0 1 0 forced PAL 4.4 MHz

0 1 1 forced SECAM

1 0 0 forced NTSC 4.4 MHz

1 0 1 forced PAL 3.6 MHz (pin 33)

1 1 0 forced PAL 3.6 MHz (pin 34)

1 1 1 no function

Loading...

Loading...