INTEGRATED CIRCUITS

DATA SH EET

TDA8051

QPSK receiver

Product specification

Supersedes data of 1998 Jan 08

File under Integrated Circuits, IC02

1999 Aug 20

Philips Semiconductors Product specification

QPSK receiver TDA8051

FEATURES

• High operating input sensitivity

• Gain controlled amplifier

• PLL controlled carrier frequency

• Low crosstalk between I and Q channel outputs

• 3-wire transmission bus

• 5 V supply voltage.

APPLICATIONS

• BPSK/QPSK demodulation.

GENERAL DESCRIPTION

This TDA8051 is a monolithic bipolar IC intended for

Quadrature Phase Shift Key (QPSK) demodulation. It

includes:

• Low noise RF and gain controlled amplifier

• Two matched mixers

• Symmetrical Voltage Controlled Oscillator (VCO) with

0to90°signal generator whosefrequency is controlled

by an integrated Phase Lock Loop (PLL) circuit.

• Two matched amplifiers for output base-band active

filtering and output buffers

The gain control is produced by output level detection

compared with an external pre-fixed reference. The PLL

consists of:

• Divide by four preamplifier

• 12-bit programmable main divider

• Crystal oscillator with 8-bit programmable reference

divider

• Phase/frequency detector combined with charge pump

to drive tuning amplifier

• 30 V output

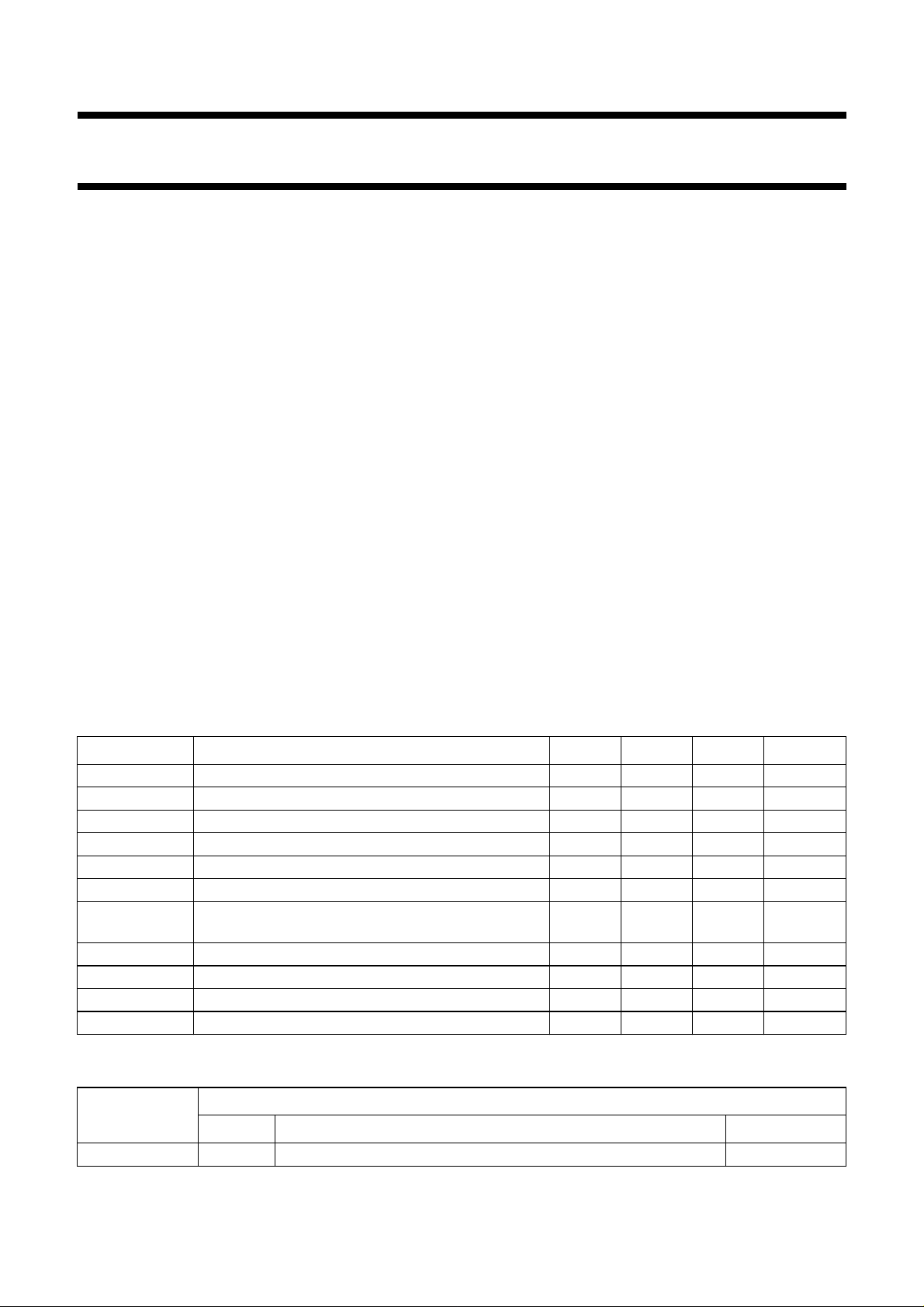

QUICK REFERENCE DATA

All AC units are RMS values unless otherwise specified.

SYMBOL PARAMETER MIN. TYP. MAX. UNIT

V

CC

f

I(LNA)

V

I(LNA)

∆Φ

I-Q

∆G

I-Q

α

CT(I-Q)

IM3 3rd-order intermodulation distortion in

supply voltage range 4.75 5.00 5.25 V

input carrier frequency at LNA input 44 − 130 MHz

input level at LNA input −30 − 0 dBmV

phase error between I and Q channels −±3−deg

gain error between I and Q channels −±1−dB

crosstalk between I and Q channels −−30 − dBc

−−−45 dBc

I and Q channels (0 dBmV at LNA_IN)

V

f

step

f

xtal

T

o

amb

voltage output on pin I_OUT and Q_OUT − 48 − dBmV

step at output 50 − 250 kHz

crystal frequency 1 − 4 MHz

operating ambient temperature 0 − 70 °C

ORDERING INFORMATION

PACKAGE

TYPE NUMBER

NAME DESCRIPTION VERSION

TDA8751T SO32 plastic small outline package; 32 leads; body width 7.5 mm SOT287-1

1999 Aug 20 2

This text is here in white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here in

_white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here inThis text is here in

white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader. white to force landscape pages to be ...

1999 Aug 20 3

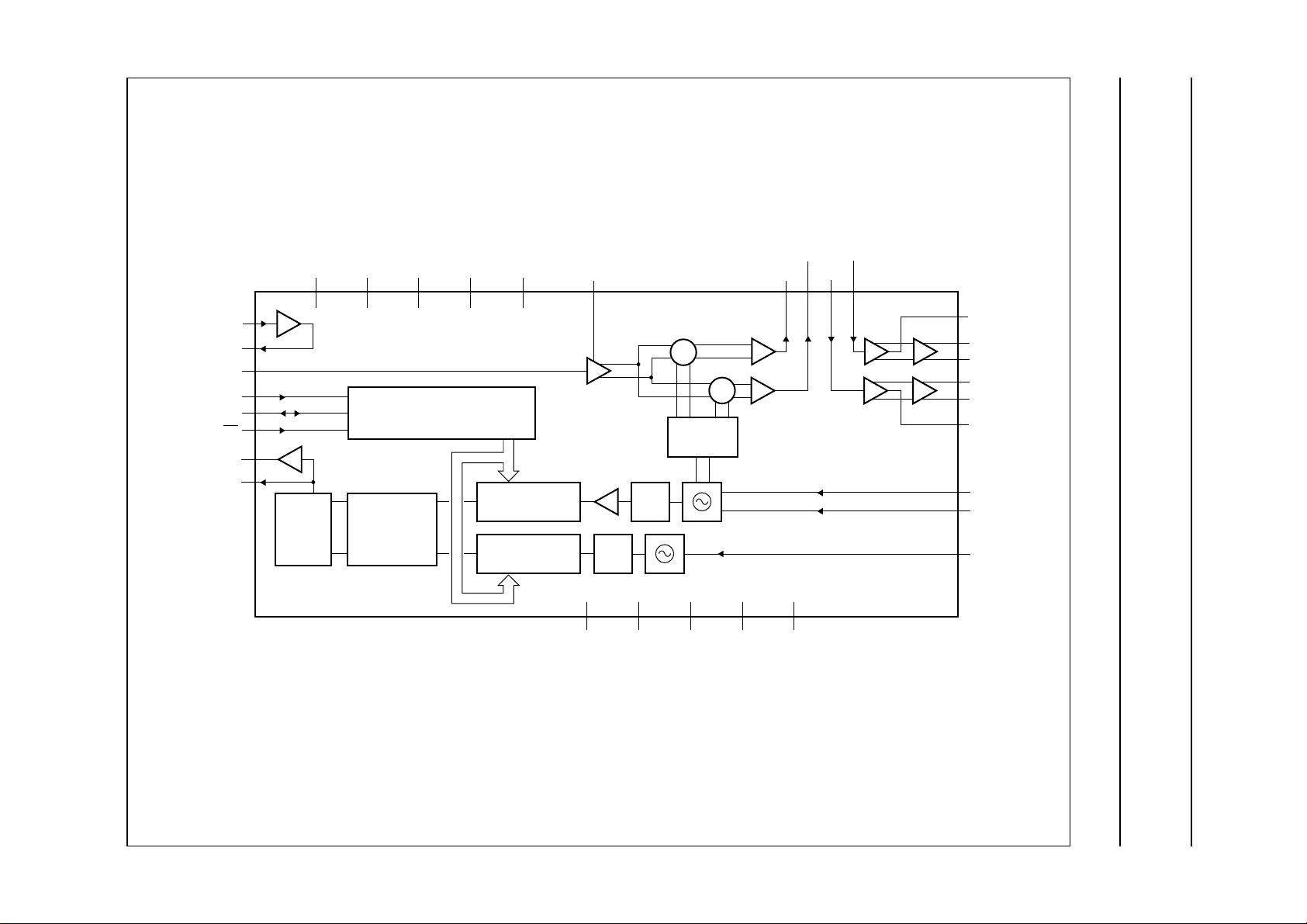

BLOCK DIAGRAM

Philips Semiconductors Product specification

QPSK receiver TDA8051

LNA_IN

LNA_OUT

DEMOD_IN

CLK

DATA

EN

TUNE

CP

9

8

7

14

15

16

19

18

A1VCC

CHARGE

A2VCC

6

A3VCC

23

3-WIRE BUS TRANSCEIVER

DIGITAL

PHASE

COMPARATOR

DVCC

25

OUTVCC

13

27

PROGRAMMABLE

MAIN DIVIDER

PROGRAMMABLE

REF DIVIDER

AGC_IN

11

TDA8051

1/2

17

TEST

n.c.

Q_OUT1

I_OUT1

5

×

×

90¡ 0¡

1/2

1/4

10

A1GND24A2GND26OUTGND20DGND

Q_IN1

28

I_IN1

29 4

32

31

30

21

22

12

FCE112

3

1

2

I_OUT2

I_OUT

I_OUTC

Q_OUT

Q_OUTC

Q_OUT2

TKB

TKA

OSC_IN

Fig.1 Block diagram.

handbook, full pagewidth

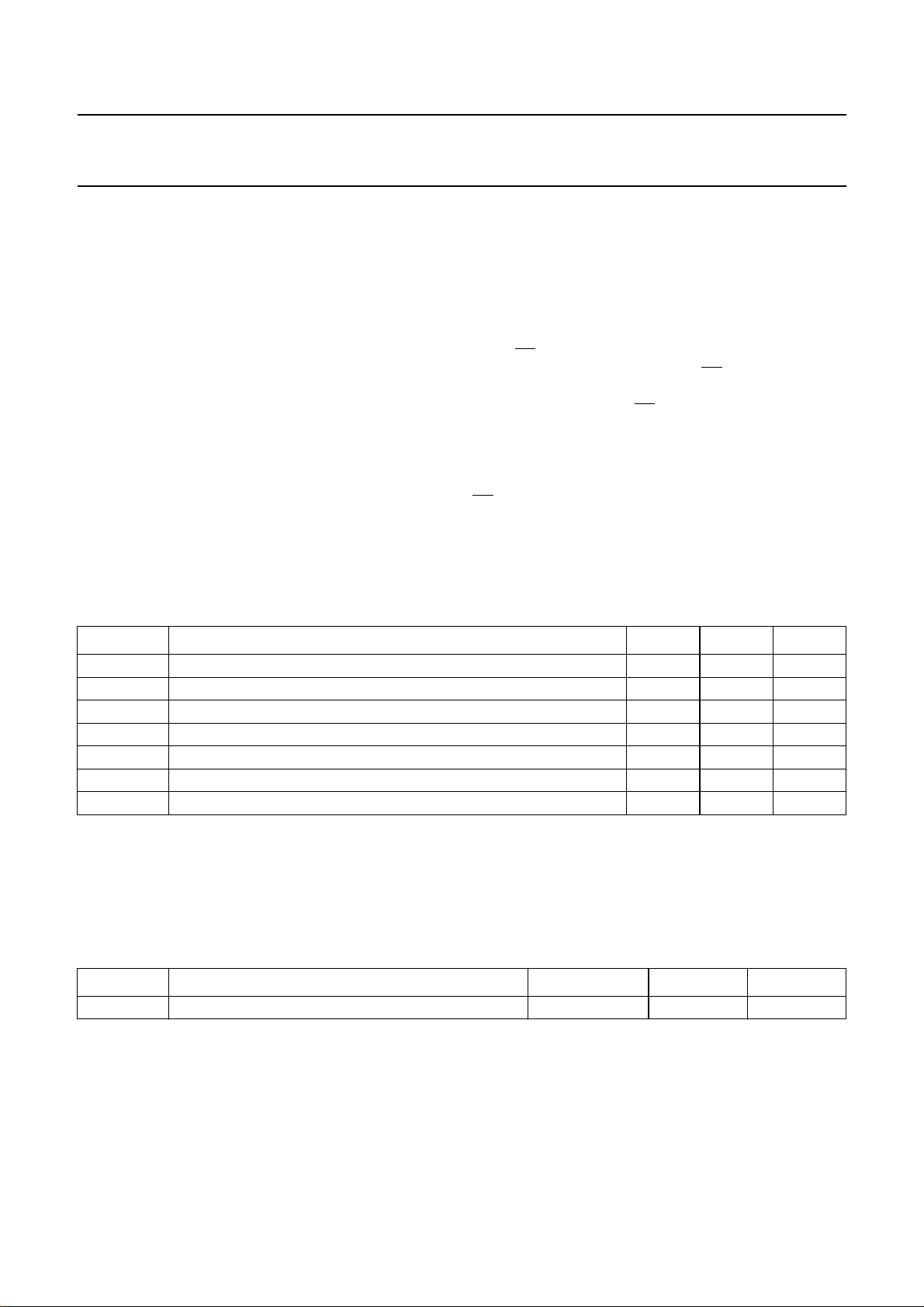

Philips Semiconductors Product specification

QPSK receiver TDA8051

PINNING

SYMBOL PIN DESCRIPTION

I_OUT 1 I data buffered balanced output

I_OUTC 2 I data buffered balanced output

I_OUT2 3 I data filtered output

I_IN1 4 input to active filter amplifier for

I data

I_OUT1 5 I data raw output

A1VCC 6 analog supply voltage 1

DEMOD_IN 7 demodulator RF input

LNA_OUT 8 low noise amplifier RF output

LNA_IN 9 low noise amplifier RF input

A1GND 10 analog ground 1

AGC_IN 11 AGC control voltage input

OSC_IN 12 oscillator input

DVCC 13 digital supply voltage

CLK 14 3-wire bus serial control clock

DATA 15 3-wire bus serial control data

EN 16 3-wire bus serial control enable

(active LOW)

TEST 17 not connected

CP 18 charge pump output for PLL loop

filter

TUNE 19 tuning voltage output

DGND 20 digital ground

TKB 21 VCO tank circuit input

TKA 22 VCO tank circuit input

A2VCC 23 analog supply voltage 2

A2GND 24 analog ground 2

A3VCC 25 analog supply voltage 3

OUTGND 26 output amplifiers ground

OUTVCC 27 output amplifiers supply voltage

Q_OUT1 28 Q data raw output

Q_IN1 29 input to active filter amplifier for

Q data

Q_OUT2 30 Q data filtered output

Q_OUTC 31 Q data buffered balanced output

Q_OUT 32 Q data buffered balanced output

handbook, halfpage

DEMOD_IN

I_OUT

1

I_OUTC

I_OUT2

I_OUT1

A1VCC

LNA_OUT

LNA_IN

A1GND

AGC_IN

OSC_IN

I_IN1

DVCC

CLK

DATA

EN

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

TDA8051

Fig.2 Pin configuration.

FCE171

32

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

Q_OUT

Q_OUTC

Q_OUT2

Q_IN1

Q_OUT1

OUTVCC

OUTGND

A3VCC

A2GND

A2VCC

TKA

TKB

DGND

TUNE

CP

TEST

1999 Aug 20 4

Philips Semiconductors Product specification

QPSK receiver TDA8051

FUNCTIONAL DESCRIPTION

The QPSK modulated signal is applied to the input as an

asymmetrical RF signal in the bandwidth 44 to 130 MHz.

The spectrum extension to this waveform must be limited

by a band-pass filter superseding the IC.

The RF input is either the LNA input, if the level is

−30 to 0 dBmVrms, or the DEMOD input if the level is

−20 to +10 dBmVrms. The amplified RF signal is then

mixed with two clocks in quadrature to provide the

base-band demodulated In-phase (I) and Quad-phase (Q)

signals.

The VCO operates at twice the RF carrier frequency in the

bandwidth 88 - 260 MHz (one octave), therefore the

0to90° clocks are generated by a divider by 2.

The VCO frequency can be programmed by an integrated

PLL that tunes the external LC tank circuit.

The raw I and Q generated signals contain spurious

spikes, therefore each signal is passed through a third

order active low-pass filter (RC cell + Sallen-Key

structure), whose cut-off frequency is set by external

components. The filtered I and Q data signals are then

amplified to provide balanced buffer outputs.

The data sent to the PLL is loaded in bursts, framed by

signal EN. Programming clock edges, together with their

relevant data bits, are ignored until EN becomes active

(LOW). The internal latches are updated with the latest

programming data when EN returns to inactive (HIGH).

The last 14 bits only are retained within the programming

register. No check is made on the number of clock pulses

received while programming is enabled. An active clock

edge causing a shift of the data bits is generated when

EN goesHIGHwhileCLOCKisstillLOW. The main divider

ratio and the reference divider ratio are provided via the

serial bus (see Table 1).

LIMITING VALUES

In accordance with the Absolute Maximum Rating System (IEC 134).

SYMBOL PARAMETER MIN. MAX. UNIT

V

CC

V

(max)

t

sc

T

stg

T

j(max)

T

amb

V

CC(tune)

supply voltage −0.3 6.0 V

maximum voltage on all pins except pin 9 (5 V) −0.3 V

CC

V

maximum short circuit duration on outputs − 10 s

storage temperature −40 +150 °C

maximum junction temperature − 150 °C

operating ambient temperature 0 70 °C

tuning voltage supply −0.3 30 V

HANDLING

HBM ESD: The IC pins withstand 2 kV except pin 26 (1750 V).

MM ESD: The IC pins withstand 100 V except pins 2 and 31 (75 V).

THERMAL CHARACTERISTICS

SYMBOL PARAMETER CONDITIONS VALUE UNIT

R

th(j-a)

thermal resistance from junction to ambient in free air 65 K/W

1999 Aug 20 5

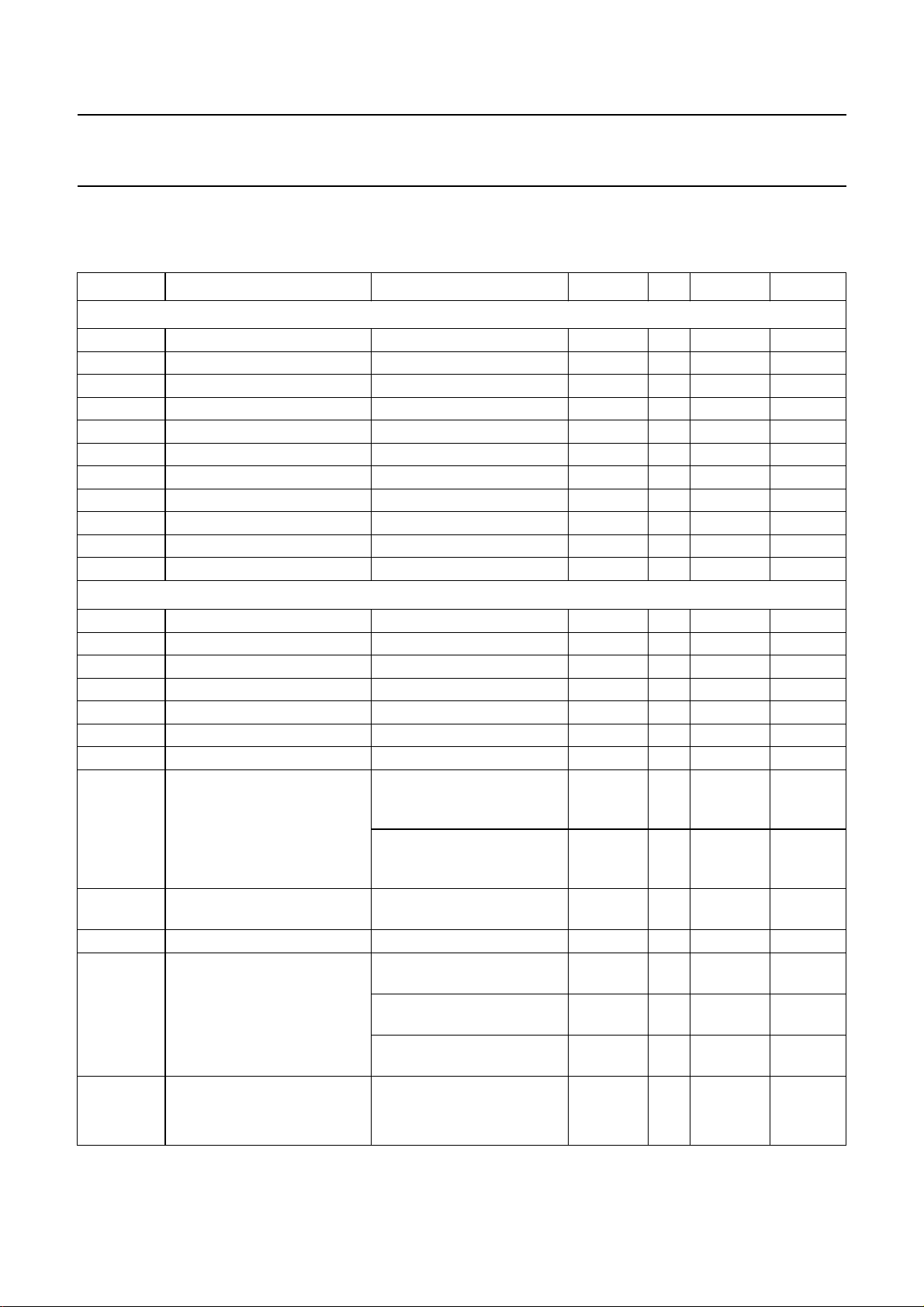

Philips Semiconductors Product specification

QPSK receiver TDA8051

CHARACTERISTICS

Measured in application circuit with the following conditions: VCC=5V; T

unless otherwise specified.

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

Supplies

V

CCA1

I

CCA1

V

CCA2

I

CCA2

V

CCA3

I

CCA3

V

cc(o)

I

cc(o)

V

CCD

I

CCD

V

CC(tune)

analog supply voltage 4.75 5 5.25 V

analog supply current − 23 − mA

analog supply voltage 4.75 5 5.25 V

analog supply current − 18 − mA

analog supply voltage 4.75 5 5.25 V

analog supply current − 29 − mA

output supply voltage 4.75 5 5.25 V

output supply current − 17 − mA

digital supply voltage 4.75 5 5.25 V

digital supply current − 13 − mA

tuning supply voltage −−30 V

Low noise amplifier: Rs=75Ω/Ri=75Ω unless otherwise specified

=25°C. All AC units are RMS values,

amb

V

I(DC)

V

i

f

i

R

i

C

i

R

LLNA

NF

LNA

V

leak(LO)

DC input level internally set − 0.85 − V

input level −30 − 0 dBmV

input carrier frequency 44 − 130 MHz

input resistance − 75 −Ω

input capacitance − 2.5 − pF

input return loss −−15 − dB

noise figure − 711 dB

LO leakage on pin at LNA_IN f

= 140 − 860 MHz;

N × LO

−−−15 dBmV

pin LNA_OUT connected to

DEMOD_IN

=70−130 MHz;

f

LO/2

−−35 −30 dBmV

pin LNA_OUT connected to

DEMOD_IN

G

V

∆V

LNA

o

LNA gain f = 100 MHz;

V

= 0 dBmV

I(LNA)

output level −−20 − +10 dBmV

o

output flatness in 1 MHz bandwidth;

V

= 0 dBmV

I(LNA)

44 to 70 MHz;

V

= 0 dBmV

I(LNA)

70 to 130 MHz;

V

= 0 dBmV

I(LNA)

810−dB

− 0.25 0.5 dB

− 0.50 − dB

− 1.3 1.5 dB

IM3 3rd-order intermodulation 2 carriers at +10 dBmV each −−−60 dBc

at pin LNA_IN

at 103 to 105 MHz

1999 Aug 20 6

Philips Semiconductors Product specification

QPSK receiver TDA8051

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

V

o(DC)

R

o

Quadrature demodulator: Rs=75Ω/Ri=20kΩ unless otherwise specified

DC output level − 1.3 − V

output resistance − 75 −Ω

V

I(DC)

V

i

f

i

R

i

C

i

RL

I

V

o(I-Q)

DC input level internally set − 1 − V

input level −20 − +10 dBmV

input carrier frequency 44 − 130 MHz

input resistance − 75 −Ω

input capacitance − 2.5 − pF

input Return Loss −−12 − dB

output level on pin I_OUT1 or

Q_OUT1

B

o(I-Q)

output 3 dB bandwidth LO = 200 MHz;

C/N carrier to noise ratio at

500 kHz on pin at I_OUT1 or

Q_OUT1

V

leak(LO)

LO leakage on pin

DEMOD_IN

V

AGC(r)

V

AGC(s)

V

AGC

AGC range fLO= 200 MHz;

AGC slope maximum fLO= 200 MHz;

gain control voltage at

AGC_IN

G

G

∆Φ

max

min

I-Q

max. conversion gain fLO= 260 MHz;

min. conversion gain fLO= 140 MHz;

phase error between I and Q

channels

∆G

I-Q

gain error between I and Q

channels

RF = 100 to 130 MHz

V

= −20 dBmV;

I

V

o(I and Q)

V

I

V

o(I and Q)

= 22 dBmV

= 10 dBmV;

= 22 dBmV

fLO= 140 to 260 MHz;

f

= 70 to 130 MHz

LO/2

fRF= 100.25 MHz at

−20 to +10 dBmV;

fBF= 250 kHz at 22 dBmV

fRF= 100.25 MHz at

−20 to +10 dBmV;

fBF= 250 kHz at 22 dBmV

fRF= 130.25 MHz at

−20 dBmV; V

AGC

= 4.5 V

fRF= 70.25 MHz at

10 dBmV V

AGC

= 0.5 V

fLO= 140 to 260 MHz;

fRF= 70.25 to 130.25 MHz;

fBF= 250 kHz at 22 dBmV

over specified input range

fLO= 140 to 260 MHz;

fRF= 70.25 to 130.25 MHz;

fBF= 250 kHz at 22 dBmV

over specified input range

− 22 − dBmV

− 35 38 MHz

− 88 − dBc/Hz

− 93 − dBc/Hz

−−−15 dBmV

30 −− dB

− 30 − dB/V

10% V

CCA

− 90% V

CCA

V

42 −− dB

−−12 dB

−±3−deg

−±1−dB

1999 Aug 20 7

Philips Semiconductors Product specification

QPSK receiver TDA8051

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

∆Φ

I-Q

∆G

I-Q

IM3 3rd-order intermodulation in

IM2 2nd-order intermodulation in

AMREJ AM rejection at I and Q

∆V

o(I/Q)

V

o(DC)

R

o

Output section: Rs= 400 Ω/Ri=4kΩ/R on pin I_OUT2 or Q_OUT2 = 20 kΩ unless otherwise specified

phase error between I and Q

channels

fLO= 88 to 140 MHz;

fRF= 44.25 to 70.25 MHz;

−±3−deg

fBF= 250 kHz at 22 dBmV

over specified input range

gain error between I and Q

channels

fLO= 88 to 140 MHz;

fRF= 44.25 to 70.25 MHz;

−±1−dB

fBF= 250 kHz at 22 dBmV

over specified input range

see Fig.3 −−−45 dBc

I and Q channels

see Fig.3 −−−40 dBc

I and Q channels

channels

output flatness at I and Q

outputs

guaranteed by design;

see Fig.4

in 1 MHz bandwidth − 0.25 − dB

f = 40 to 70 MHz − 3 − dB

−−−38 dBc

f = 70 to 130 MHz − 3 − dB

DC output level − 2.5 − V

output resistance − 400 −Ω

V

V

R

C

G

I(DC)

i

i

i

O

DC input voltage − 3.6 − V

input level − 22 − dBmV

input resistance − 17.5 − kΩ

input capacitance − 0.4 − pF

gain from

I-Q_IN1 to I-Q_OUT2

∆V

o(I-Q_out2)

output flatness on

pins I_OUT2 and Q_OUT2

V

o(flt)

R

o

H

2

H

3

DC output level at filter output − 2.6 − V

output resistance f < 20 MHz − 250 −Ω

2nd harmonic fBF= 1 MHz at 48 dBmV

3rd harmonic

IM3 3rd-order intermodulation at

pins I_OUTand Q_OUT

α

CT(I-Q)

crosstalk between I and Q

channels

N

o

output noise power at

500 kHz from carrier

G

I-Q

gain from

I-Q_IN1 to I-Q_OUT

fBF= 1 MHz at 22 dBmV − 3.8 − dB

fBF= 0 to 1.5 MHz − 0.25 − dB

f

= 0 to 6 MHzat 22 dBmV

BF

− 1 − dB

input

−−40 −35 dBc

output

f

= 1 MHz at 48 dBmV

BF

−−45 −40 dBc

output

see Fig.5 −−50 −45 dBc

f = 5 MHz; see Fig.6 −−40 −30 dBc

see Fig.7 −−56 − dBmv/Hz

fBF= 1 MHz at 22 dBmV

− 27 − dB

input

1999 Aug 20 8

Loading...

Loading...