INTEGRATED CIRCUITS

DATA SH EET

TDA8050A

QPSK transmitter

Product specification

File under Integrated Circuits, IC02

1999 Nov 05

Philips Semiconductors Product specification

QPSK transmitter TDA8050A

FEATURES

• Programmable gain

• PLL controlled carrier frequency

• 3-wire transmission bus

• 5 V supply voltage.

APPLICATIONS

• QPSK modulation.

GENERAL DESCRIPTION

TheQuadraturePhaseShiftKeying(QPSK)transmitter IC

is a monolithic bipolar IC dedicated to quadrature

modulation of the I and Q signals. It includes:

• Two double balanced mixers

• A balanced voltage controlled oscillator (VCO) with

0 to 90 degrees signal generation for modulation

• A phase locked loop (PLL) for IF frequency control

• A conversion mixer

• A PLL for RF frequency control

• A gain controlled output amplifier

• A 3-wire bus and an output buffer.

Two PLLs are incorporated, the first PLL includes:

• A fixed main divider

• A crystal oscillator and its programmable reference

divider

• A phase/frequency detector, combined with a fixed

charge pump.

The second PLL includes:

• A divide-by-four preamplifier

• A 12-bit programmable divider

• A crystal oscillator and its programmable reference

divider

• A phase/frequency detector, combined with a

programmable charge pump which drives the tuning

amplifier, including 30 V output.

QUICK REFERENCE DATA

SYMBOL PARAMETER MIN. TYP. MAX. UNIT

V

CC

f

c

V

o(max)

f

xtal

f

ref(MOD)

f

step

T

amb

supply voltage 4.75 5.00 5.25 V

output centre frequency 5 − 65 MHz

maximum output level − 55 − dBmV

crystal frequency 1 − 4 MHz

reference frequency for modulator synthesizer − 250 − kHz

frequency step size for converter synthesizer 100 − 500 kHz

ambient temperature 0 − 70 °C

ORDERING INFORMATION

TYPE

NUMBER

NAME DESCRIPTION VERSION

PACKAGE

TDA8050A SO32 plastic small outline package; 32 leads; body width 7.5 mm SOT287-1

1999 Nov 05 2

This text is here in white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here in

_white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader.This text is here inThis text is here in

white to force landscape pages to be rotated correctly when browsing through the pdf in the Acrobat reader. white to force landscape pages to be ...

1999 Nov 05 3

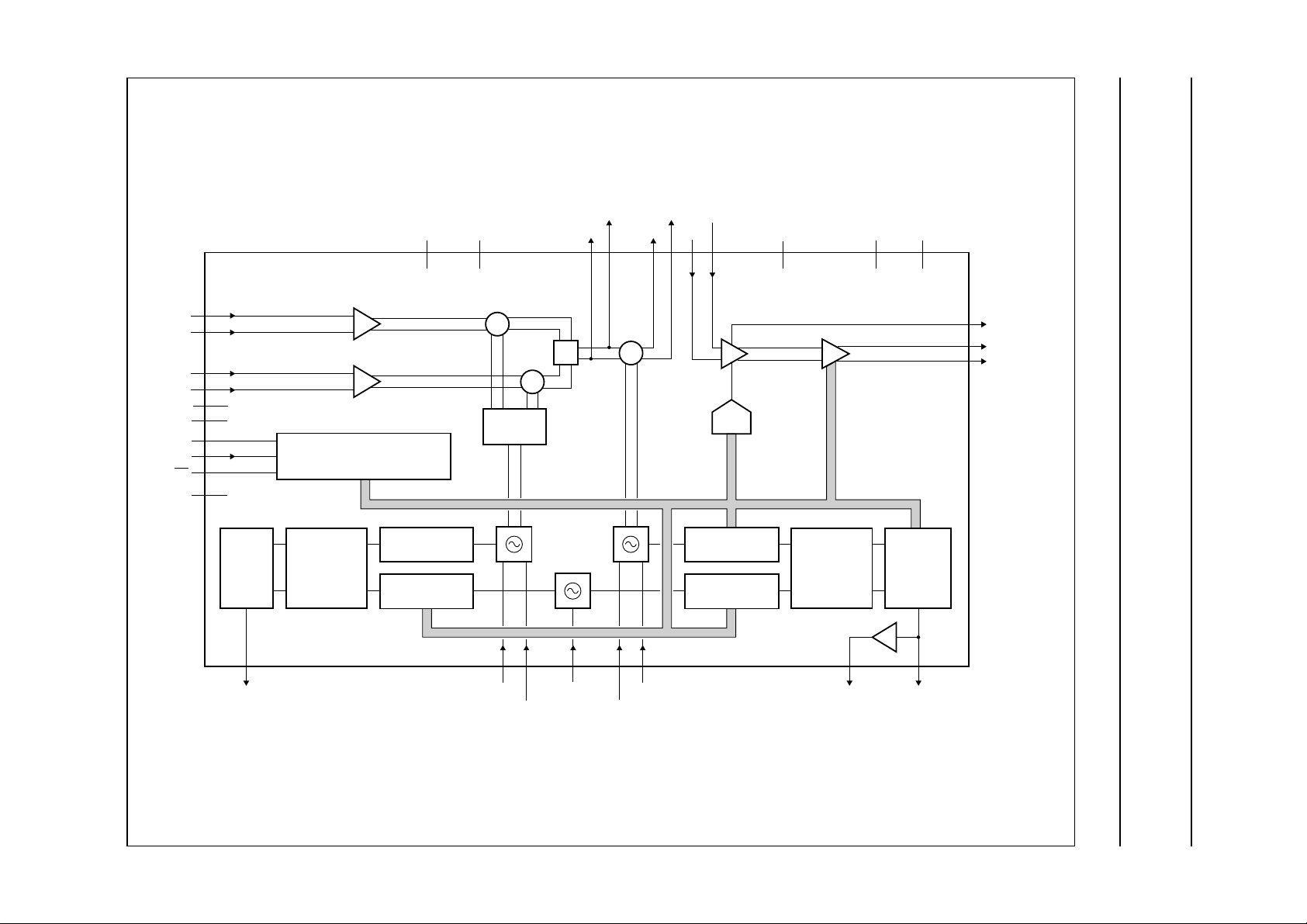

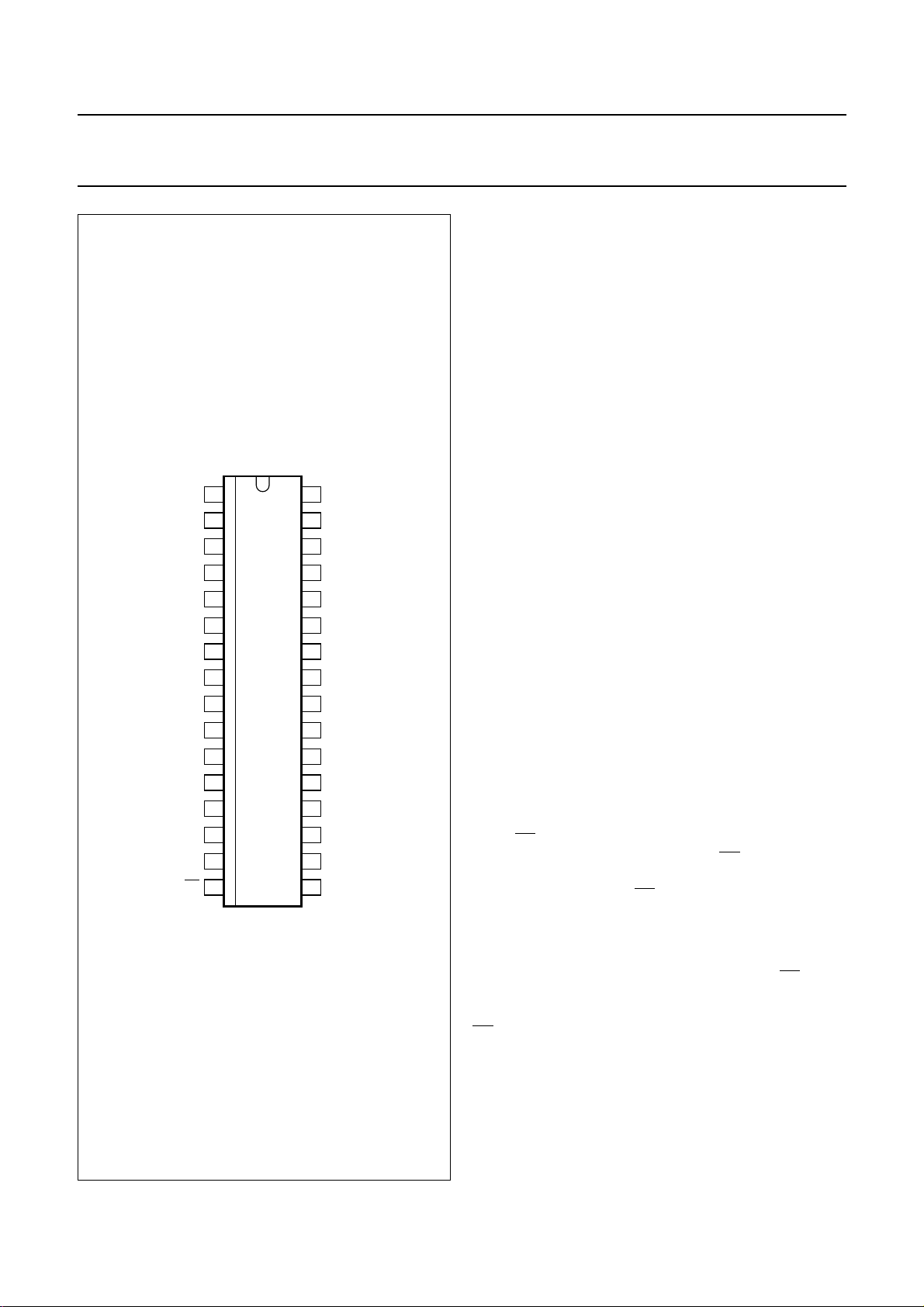

BLOCK DIAGRAM

Philips Semiconductors Product specification

QPSK transmitter TDA8050A

I_IN

I_INC

Q_IN

Q_INC

DVCC

DGND

CLK

DATA

EN

LOCK

5

6

7

8

13

18

14

15

16

23

CHARGE

PUMP

CP_MOD

AVCC1

26

AGND1

9

RF_OUTC

RF_OUT

2524 28

RF_INCIF_FILTC

RF_INIF_FILT

27

30 31

SW_CAP

MODULATOR CONVERTER

×

Σ

×

×

3-WIRE BUS TRANCEIVER

DIGITAL

PHASE

COMPARATOR

PROGRAMMABLE

FIXED

MAIN DIVIDER

REF DIVIDER

90 0

1/2

TDA8050A

101211 17 22 21

TKAMOD

TKBMOD TKACONV

OSC_IN TKBCONV

DAC

PROGRAMMABLE

MAIN DIVIDER

PROGRAMMABLE

REF DIVIDER

AVCC2

32

DIGITAL

PHASE

COMPARATOR

20 19

TUNECONV CP_CONV

AGND2

29

PROGRAM-

MABLE

CHARGE

PUMP

4

1

OUTEN

3

BUF_OUTC

2

BUF_OUT

FCE433

Fig.1 Block diagram.

Philips Semiconductors Product specification

QPSK transmitter TDA8050A

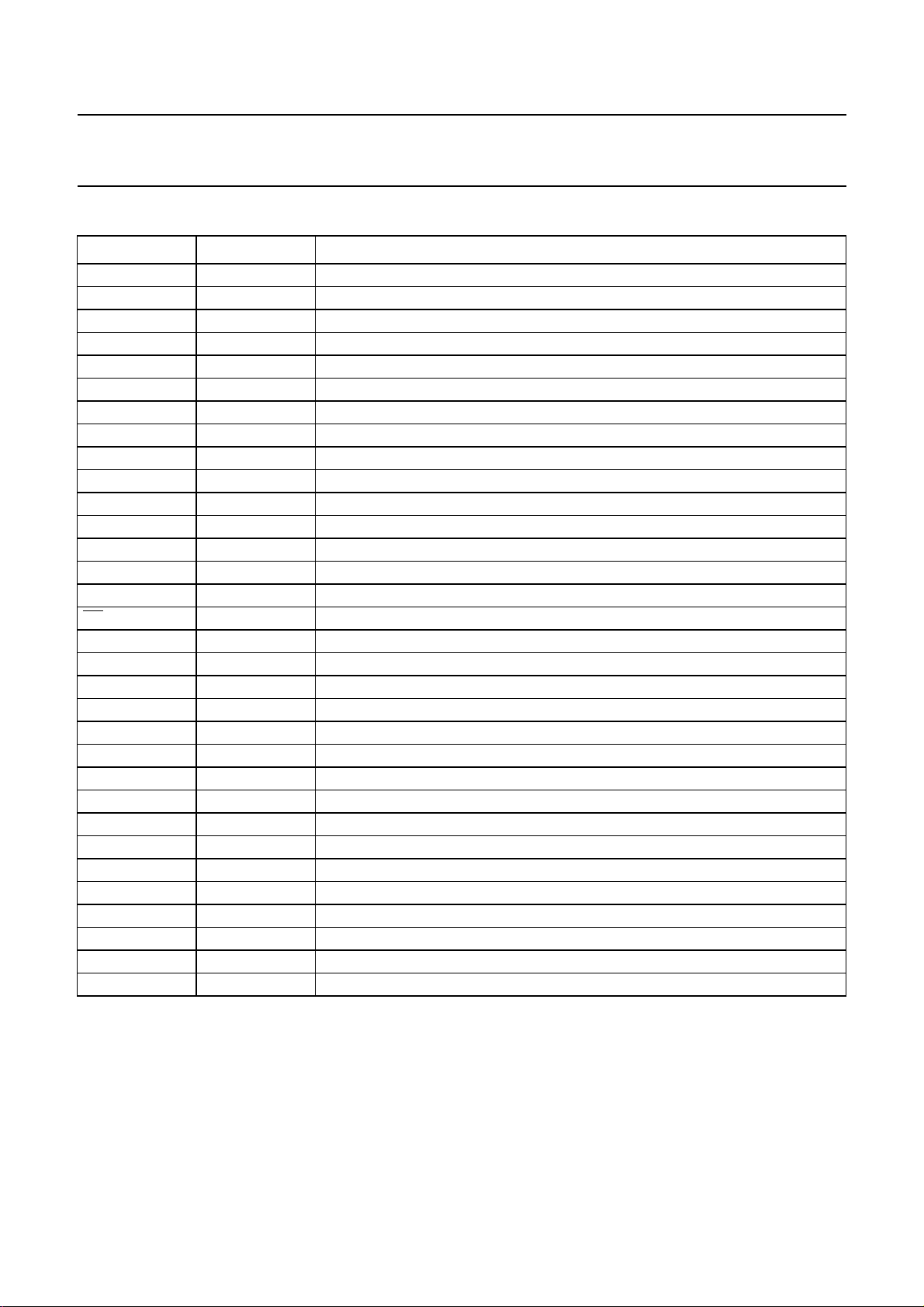

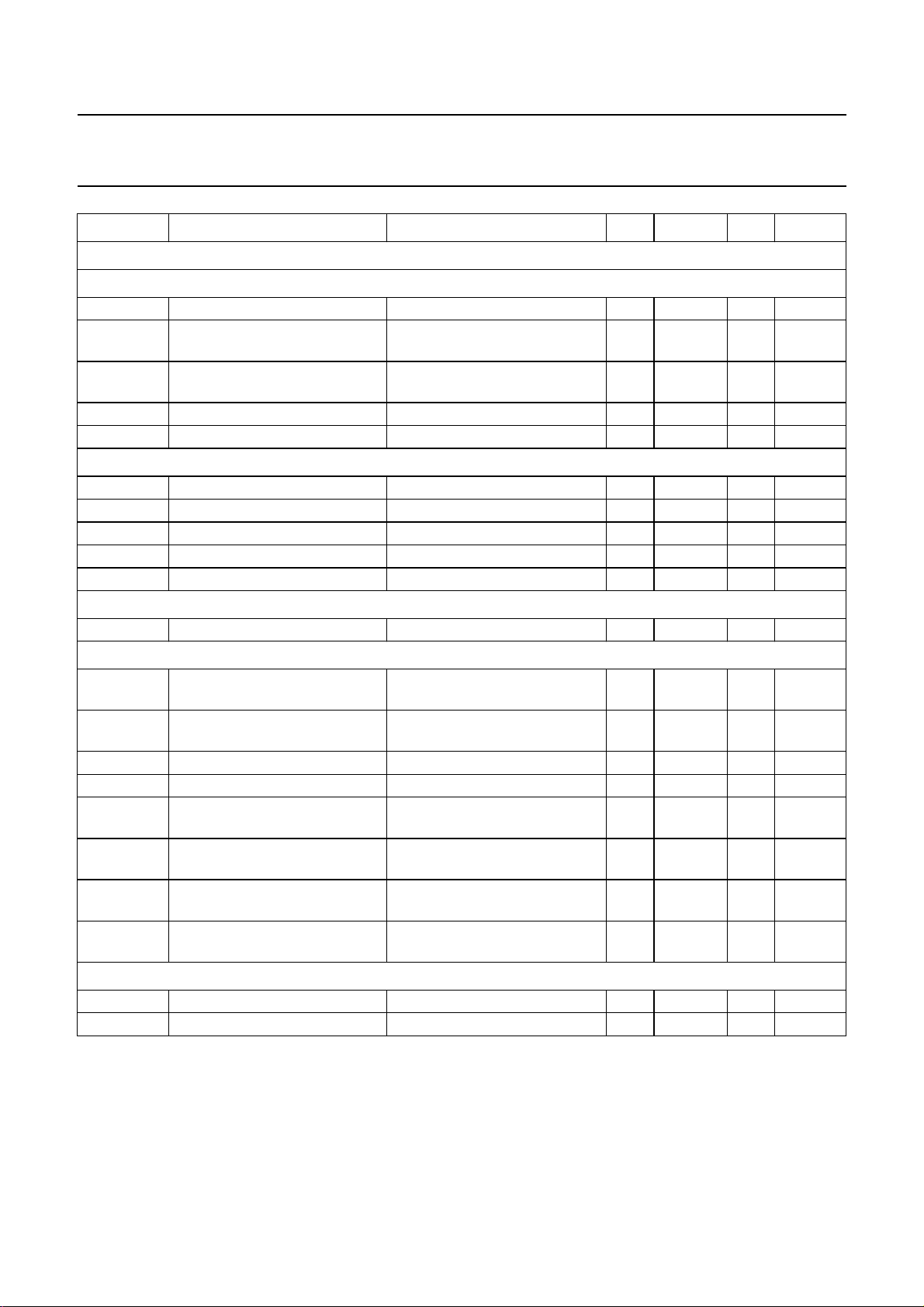

PINNING

SYMBOL PIN DESCRIPTION

OUTEN 1 output enable

BUF_OUT 2 output amplifier balanced output

BUF_OUTC 3 output amplifier balanced output

AGND2 4 converter analog ground 2

I_IN 5 I balanced input

I_INC 6 I balanced input

Q_IN 7 Q balanced input

Q_INC 8 Q balanced input

AGND1 9 modulator analog ground 1

TKA_MOD 10 modulator VCO tank circuit input 2

TKB_MOD 11 modulator VCO tank circuit input 1

CP_MOD 12 modulator charge pump output for PLL loop filter

V

CCD

CLK 14 3-wire bus serial control clock

DATA 15 3-wire bus serial control data

EN 16 3-wire bus serial control enable

OSC_IN 17 crystal oscillator input

DGND 18 digital ground

CP_CONV 19 converter charge pump output for PLL loop filter

TUNE_CONV 20 tuning voltage output for converter VCO

TKB_CONV 21 converter VCO tank circuit input 1

TKA_CONV 22 converter VCO tank circuit input 2

LOCK 23 lock detect signal

IF_FILT 24 IF balanced output to filter

IF_FILTC 25 IF balanced output to filter

V

CCA1

RF_OUTC 27 RF balanced output to filter

RF_OUT 28 RF balanced output to filter

V

CCA2

RF_IN 30 RF balanced input to programmable amplifier

RF_INC 31 RF balanced input to programmable amplifier

SW_CAP 32 switch capacitor

13 digital supply voltage

26 modulator analog supply voltage

29 converter analog supply voltage

1999 Nov 05 4

Philips Semiconductors Product specification

QPSK transmitter TDA8050A

FUNCTIONAL DESCRIPTION

The I and Q signals are balanced analog signals of

400 mV (p-p). These are mixed by two double balanced

mixers with the output signal generated by a first local

oscillator, to provide the modulated signal.

The modulated signal is then filtered by an IF filter. This

filtered signal, together a signal generated by a second

local oscillator, is converted by a balanced mixer to

produce the QPSK signal.

The QPSK signal is amplified by a gain controlled output

amplifier to a level suitable for transmission. The gain of

the amplifier is bus controlled and this amplifier can be

disabled when not transmitting, to provide signal

OUTEN

BUF_OUT

BUF_OUTC

AGND2

I_IN

I_INC

Q_IN

Q_INC

AGND1

TKAMOD

TKBMOD

CP_MOD

DVCC

CLK

DATA

EN

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

TDA8050A

FCE434

32

SW_CAP

31

RF_INC

RF_IN

30

AVCC2

29

RF_OUT

28

RF_OUTC

27

AVCC1

26

25

IF_FILTC

24

IF_FILT

23

LOCK

22

TKACONV

21

TKBCONV

20

TUNECONV

19

CP_CONV

18

DGND

17

OSC_IN

attenuation.

The amplified signal is applied to an on-chip amplifier with

two balanced outputs (open collector) connected to two

off-chip resistors (values 150 Ω), in turn connected to 9 V.

The balanced outputs drive a 2 : 1 transformer (Siemens

V944) loaded with 75 Ω, which gives an output level of

55 dBmV. The output frequency range of the transmitter is

5 to 65 MHz.

The frequency of the first local oscillator operates at twice

the frequency (i.e. 280 MHz), fixed by a PLL implemented

in the circuit.

Thefrequencyofthesecondlocaloscillatoroperatesinthe

145 to 205 MHz bandwidth and can be programmed

through the PLL implemented in the circuit.

The VCOs of both the first and second local oscillators

need an external LC tank circuit with two varicap diodes.

The data sent to the PLL is loaded in bursts framed by

signal EN. Programming rising clock edges and their

appropriate data bits are ignored until EN goes active

(LOW). The internal latches are updated with the latest

programming data when EN returns to inactive (HIGH).

Only the last 14 bits are stored in the programming

register.

Fig.2 Pin configuration.

1999 Nov 05 5

No check is made on the number of clock pulses received

during the time that programming is enabled. If EN goes

high while CLK is still LOW, a wrong active clock edge will

be generated, causing a shift of the data bits. At power up,

EN should be HIGH. The lock detector output LOCK is

HIGH when both PLLs are in lock.

The main divider ratio and the reference divider ratios are

provided via the serial bus. A control register controls the

Digital-to-Analog-Converter (DAC), the output amplifier

and the charge pump currents (see Tables 1, 2 and 3).

Philips Semiconductors Product specification

QPSK transmitter TDA8050A

LIMITING VALUES

In accordance with the Absolute Maximum Rating System (IEC 134).

SYMBOL PARAMETER MIN. MAX. UNIT

V

CC

t

sc

V

MAX

V

o(tune)

V

O(buf)

P

tot

T

amb

T

stg

T

j(max)

HANDLING

supply voltage −0.3 +6.0 V

short-circuit time (every pin to VCC or GND) − 10 s

voltage on all pins except BUF_OUT, BUF_OUTC and TUNE_CONV −0.3 V

CC

V

output tuning voltage −0.3 +30 V

output buffer voltage on pins BUF_OUTand BUF_OUTC − 10 V

maximum power dissipation − 940 mW

ambient temperature 0 70 °C

storage temperature −40 +150 °C

maximum junction temperature − 150 °C

Human Body Model (HBM): The IC pins withstand 2 KV, except pins 27 and 28 (1750 V).

Machine Model (MM): The IC pins withstand 100 V.

THERMAL CHARACTERISTICS

SYMBOL PARAMETER CONDITIONS VALUE UNIT

R

th(j-a)

thermal resistance from junction to ambient in free air 63 K/W

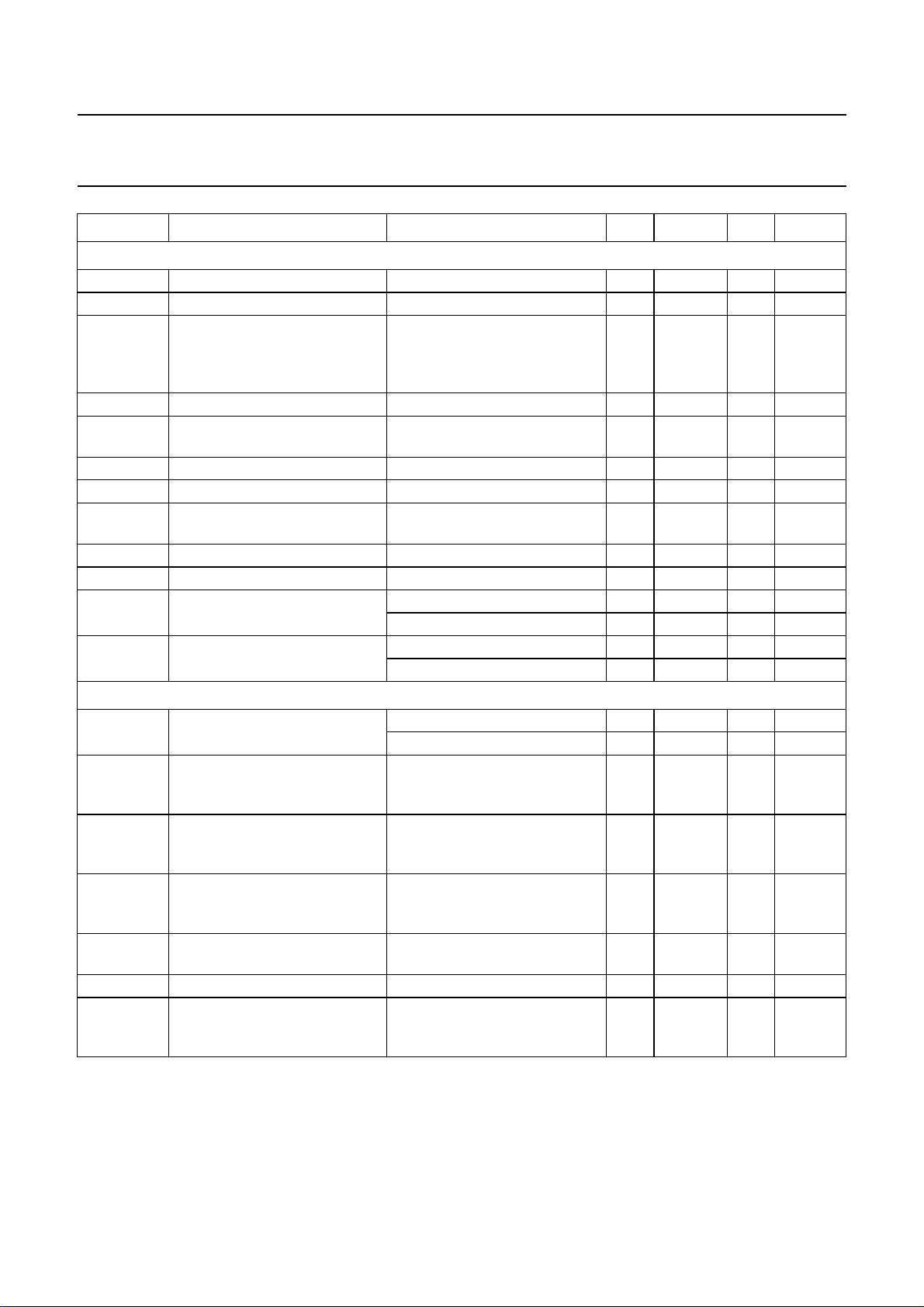

CHARACTERISTICS

Measured in application circuit with the following conditions; V

=5V, T

CC

=25°C; all AC units are RMS values,

amb

unless otherwise specified.

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

Supply

V

CCA1

modulator analog supply

4.75 5 5.25 V

voltage

I

CCA1

modulator analog supply

33 39 45 mA

current

V

CCA2

I

CCA2

I

CC(buf)

V

CCD

I

CCD

V

CC(tune)

converter analog supply voltage 4.75 5 5.25 V

converter analog supply current 39 47 55 mA

buffer output supply current 39 43 47 mA

digital supply voltage 4.75 5 5.25 V

digital supply current 20.5 23.5 26.5 mA

tuning supply voltage −− 30 V

1999 Nov 05 6

Philips Semiconductors Product specification

QPSK transmitter TDA8050A

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

Quadrature modulator

I and Q inputs

V

i(DC)

V

i(p-p)

f

i(max)

Z

i(dif)

B

(1 dB)

Modulator

f

c

∆A amplitude imbalance see Fig.3 −− ±1dB

∆Φ phase imbalance −− ±2 deg

LO

(sup)

Z

o(dif)

Modulator VCO

F

OSC(mod)

Converter output

V

O

∆V

O

f

c

Z

o(dif)

IP

3

H

2

H

3

S

O

Converter VCO

f

osc(min)

f

osc(max)

input DC level − 0.5 × VCC− V

signal input level (balanced)

indicative − 400 500 mV

(peak-to-peak)

I and Q maximum input

indicative − 10 − MHz

frequency

differential input impedance − 4.4 − kΩ

1 dB bandwidth amplifier indicative − 10 − MHz

output centre frequency −− 140 MHz

LO suppression see Fig.3 −−28 − dBc

differential output impedance − 1.8 − kΩ

oscillation frequency −− 280 MHz

output level f = 5 MHz; Vi= 100 mV

at

dif

37.5 40 42.5 dBmV

I and Q inputs

output flatness f = 5 to 65 MHz; Vi= 100 mV

−− 2dB

dif

at I and Q inputs

output centre frequency 5 − 65 MHz

differential output impedance − 150 −Ω

3rd order interception point at

see Fig.4 −− 52 dBmV

I input

2nd order harmonic of

5 to 65 MHz signal

3rd order harmonic of

5 to 65 MHz signal

mixer spurious outputs of

5 to 65 MHz signal

f = 10 to 130 MHz;

Vi= 100 mV

at I and Q inputs

dif

f = 15 to 195 MHz;

Vi= 100 mV

at I and Q inputs

dif

f = 5 to 65 MHz; Vi= 100 mV

at I and Q inputs

−− −40 dBc

−− −40 dBc

−− −45 dBc

dif

minimum oscillation frequency −− 145 MHz

maximum oscillation frequency 205 −−MHz

1999 Nov 05 7

Philips Semiconductors Product specification

QPSK transmitter TDA8050A

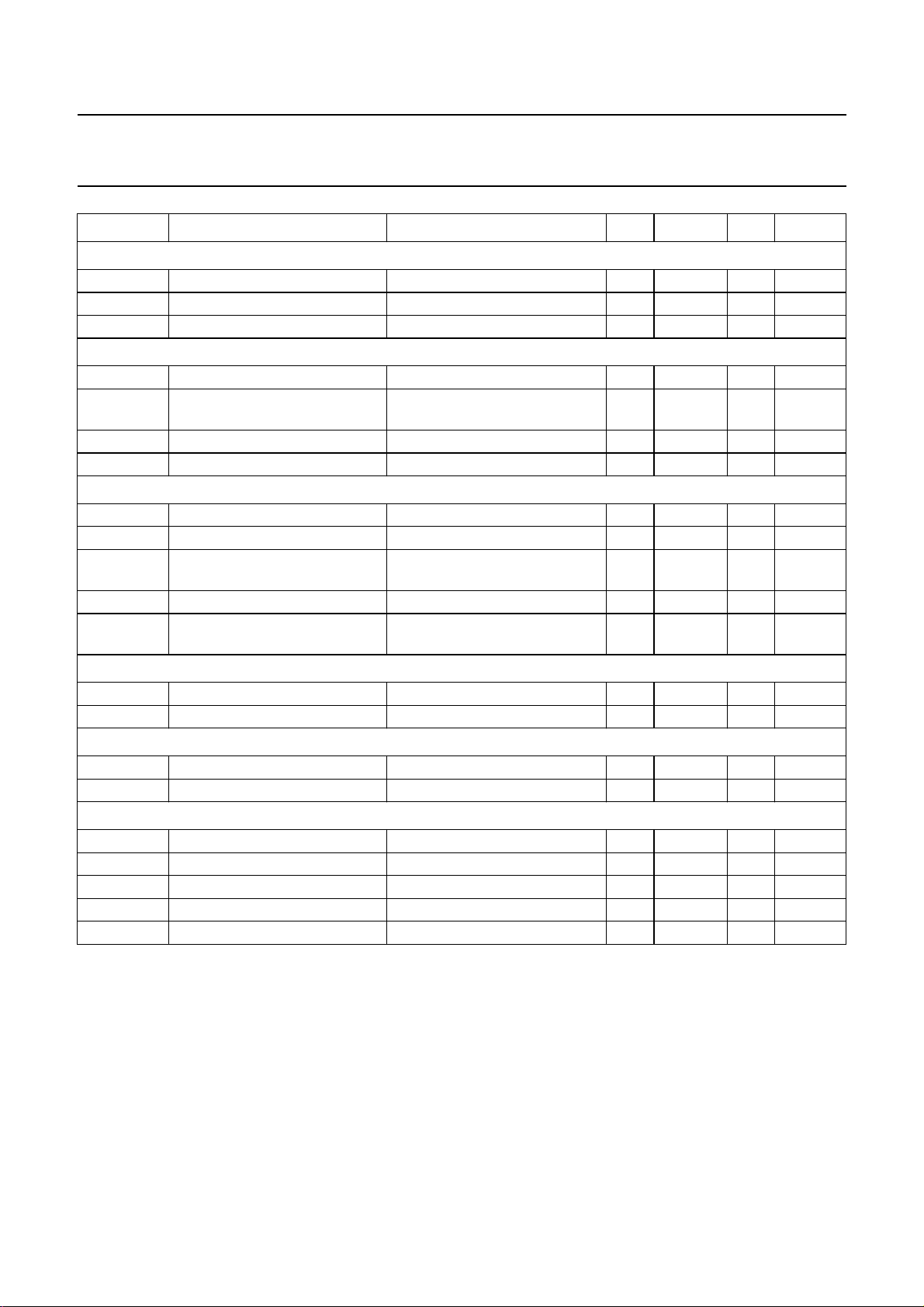

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

Programmable gain and output buffer; note 1

Z

i(dif)

∆G output level step size −− 2dB

∆buf

O

V

o

∆V

o

V

IL(ENL)

V

IH(ENH)

ISO disable isolation V

G

V(max)

V

o(1dB)

H

2

H

3

Overall; note 1

Φ

osc

H

2

H

3

S

o

IP

3

ISO

tot

C/N carrier to noise ratio at final

differential input impedance − 5.6 − kΩ

output level adjust range Vi= 30 dBmV sine wave

32 39 − dB

65 MHz at pins

RF_IN and RF_INC;

DAC = 0 to 31

operational output level − 55 − dBmV

output flatness f = 5 to 65 MHz; Vi= 30 dBmV

− 35dB

sine wave; DAC = 28

output controlled enable low output buffer on −− 0.8 V

output controlled enable high output buffer off 2.4 −−V

= 100 mV

i

; DAC= 28;

dif

−35 −90 − dBc

f = 65 MHz; OE = 0,5 V

maximum gain see Fig.5 17 18.5 − dB

1 dB compression point see Fig.5 58 −−dBmV

2nd order harmonic of

5 to 65 MHz signal

3rd order harmonic

of 5 to 65 MHz signal

f = 10 to 65 MHz; see Fig.6 −− −45 dBc

f = 65 to 120 MHz; see Fig.6 −− −35 dBc

f = 15 to 65 MHz; see Fig.6 −− −45 dBc

f = 65 to 120 MHz; see Fig.6 −− −35 dBc

phase noise at 10 kHz; note 2 −−75 − dBc/Hz

at 100 kHz; note 2 −−95 − dBc/Hz

2nd order harmonic of

5 to 65 MHz signal

3rd order harmonic

of 5 to 65 MHz signal

spurious signals of 5 to 65 MHz

signal

3rd order interception point at

f = 10 to 130 MHz;

Vin= 100 mV

inputs; V

at I and Q

dif

= 55 dBmV

out

f = 15 to 195 MHz;

Vin= 100 mV

inputs; V

at I and Q

dif

= 55 dBmV

out

f = 5 to 65 MHz; Vin= 100 mV

at I and Q inputs;

V

= 55 dBmV

out

−− −40 dBc

−− −40 dBc

−− −45 dBc

dif

−− 49 dBmV

I input

total isolation at I/Q midrange see Fig.7 −−90 −65 dBc

output at 2 MHz from carrier

= 100 mV

V

in

V

= 35 to 55 dBmV;

out

;

dif

− 113 − dBc/Hz

f = 65 MHz

1999 Nov 05 8

Philips Semiconductors Product specification

QPSK transmitter TDA8050A

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

Crystal oscillator

f

xtal

Z

i

V

i(DC)

Modulator synthesizer

f

ref(mod)

RDR1 programmablereferencedivider

ND1 fix main divider ratio − 1120 −

I

(cp)

Converter synthesizer

f

step

RD2 fix reference divider ratio − 2 −

RDR2 programmablereferencedivider

ND2 fix main divider ratio − 4 −

NDR2 programmable main divider

3-wire bus

V

IL

V

IH

Lock detect pin

V

O(lock)

V

O(unlock)

Serial control clock

f

clk

t

su

t

h(CLK)

t

d(strt)

t

d(stp)

Notes

1. All specification points of the output section and the overall circuit are measured after the 2 : 1 transformer (Siemens

V944) loaded with 75 Ω.

2. Overall phase noise:

a) Converter: I

b) I and Q = 100 mV

c) DAC = 28.

d) f = 65 MHz.

3. The crystal oscillator uses a 4, 2 or 1 MHz crystal in series with a capacitor. The crystal is serial resonant with a load

capacitance of 18 to 20 pF. The connection to VCC is preferred but it might also be to GND.

crystal frequency note 3 1 − 4 MHz

input impedance f

= 4 MHz 600 1200 −Ω

xtal

DC input level − 2.9 − V

reference frequency − 250 − kHz

4 − 16

ratio

charge-pump current fixed − 0.30 − mA

step size 100 − 500 kHz

see Tables 4 and 5 4 − 160

ratio

see Tables 4 and 5 290 − 1800

ratio

input LOW level −− 0.8 V

input HIGH level 2.4 −−V

output voltage (LOCK) − 5 − V

output voltage (UNLOCK) − 0.02 − V

clock frequency − 330 − kHz

input data to CLK set-up time see Fig.8 − 2 −µs

input data to CLK hold time see Fig.8 − 1 −µs

delay to rising clock edge see Fig.8 − 3 −µs

delay from last clock edge see Fig.8 − 3 −µs

= 0.36 mA; f

(cp)

dif

.

= 25 kHz.

ref

1999 Nov 05 9

Loading...

Loading...