Philips tda4866 DATASHEETS

INTEGRATED CIRCUITS

DATA SH EET

TDA4866

Full bridge current driven vertical

deflection booster

Product specification

Supersedes data of 1995 Aug 31

File under Integrated Circuits, IC02

1996 Oct 10

Philips Semiconductors Product specification

Full bridge current driven vertical

TDA4866

deflection booster

FEATURES

• Fully integrated, few external components

• No additional components in combination with the

deflection controller TDA4850/51/55

• Pre-amplifier with differential high CMRR current mode

inputs

• Low offsets

• High linear sawtooth signal amplification

• High efficient DC-coupled vertical output bridge circuit

• Powerless vertical shift

• High deflection frequency up to 140 Hz

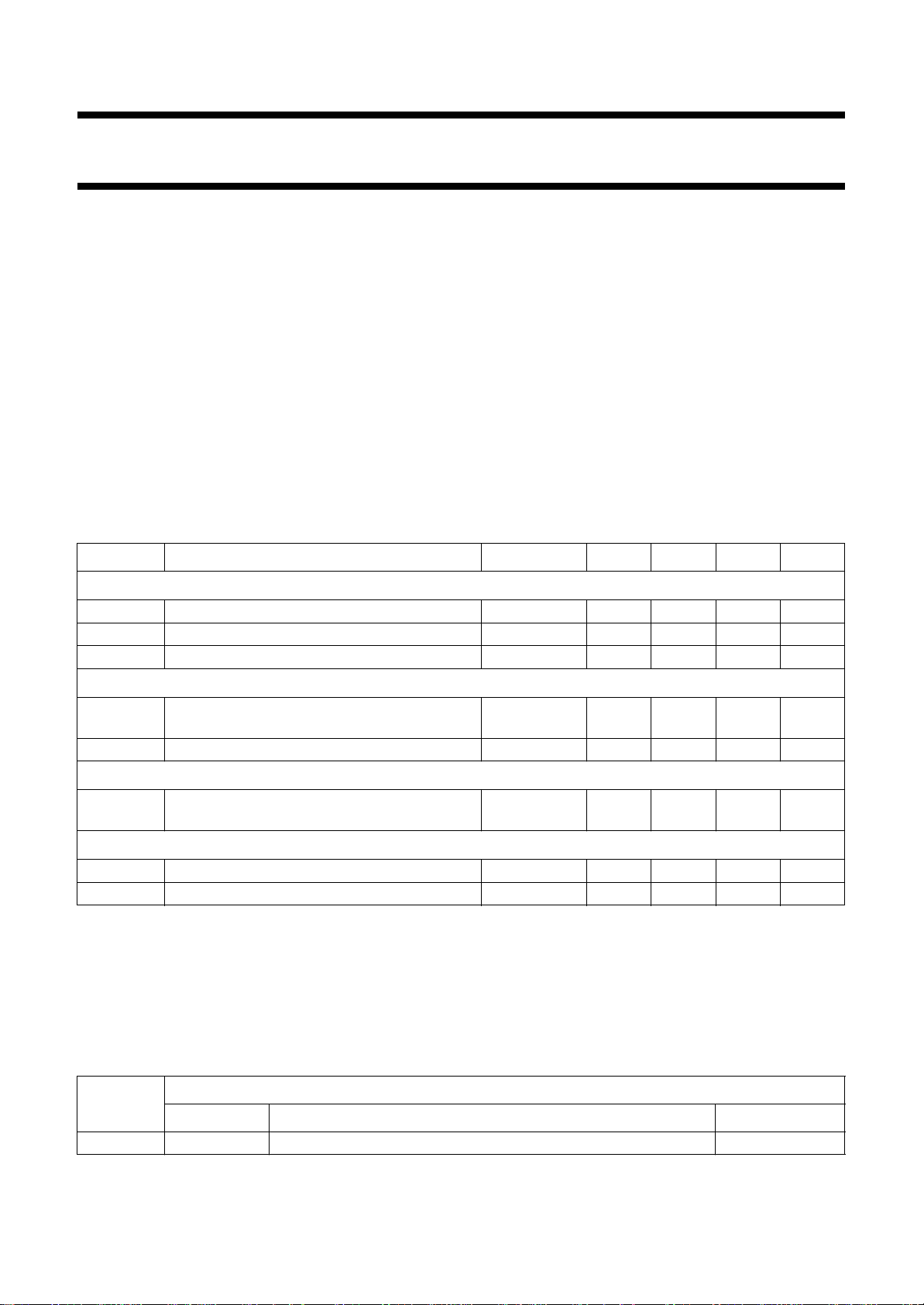

QUICK REFERENCE DATA

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

DC supply; note 1

V

P

V

FB

I

q

supply voltage (pin 3) 8.2 − 25 V

flyback supply voltage (pin 7) note 2 −−60 V

quiescent current (pin 7) − 710mA

Vertical circuit

I

defl

deflection current

(peak-to-peak value; pins 4 and 6)

I

id

differential input current (peak-to-peak value) note 3 −±500 ±600 µA

Flyback generator

I

FB

maximum current during flyback

(peak-to-peak value; pin 7)

• Power supply and flyback supply voltage independent

adjustable to optimize power consumption and flyback

time

• Excellent transition behaviour during flyback

• Guard circuit for screen protection.

GENERAL DESCRIPTION

The TDA4866 is a power amplifier for use in 90 degree

colour vertical deflection systems for frame frequencies of

50 to 140 Hz. The circuit provides a high CMRR current

driven differential input. Due to the bridge configuration of

the two output stages DC-coupling of the deflection coil is

achieved. In conjunction with TDA4850/51/55 the ICs offer

an extremely advanced system solution.

0.6 − 2A

−−2A

Guard circuit; note 1

V

8

I

8

guard voltage guard on 7.5 8.5 10 V

guard current guard on 5 −−mA

Notes

1. Voltages refer to pin 5 (GND).

2. Up to 60 V ≥ V

≥ 40 V a decoupling capacitor CFB=22µF (between pin 7 and pin 5) and a resistor RFB= 100 Ω

FB

(between pin 7 and VFB) are required (see Fig.4).

3. Differential input current Iid=I1−I2.

ORDERING INFORMATION

TYPE

NUMBER

NAME DESCRIPTION VERSION

PACKAGE

TDA4866 SIL9P plastic single in-line power package; 9 leads SOT131-2

1996 Oct 10 2

Philips Semiconductors Product specification

Full bridge current driven vertical

deflection booster

BLOCK DIAGRAM

handbook, full pagewidth

INA 1

INB 2

from e.g.

TDA4850/51/55

TDA4866

INPUT STAGE

GUARD

output

GUARD

CIRCUIT

PROTECTION

TDA4866

V

8

P

GND V

FLYBACK

GENERATOR

AMPLIFIER A

AMPLIFIER B

FB

753

6 OUTA

9

FEEDB

4 OUTB

C

SP

R

SP

R

ref

I

defl

vertical

R

deflection

p

coil

R

m

PINNING

SYMBOL PIN DESCRIPTION

INA 1 input A

INB 2 input B

V

P

3 supply voltage

OUTB 4 output B

GND 5 ground

OUTA 6 output A

V

FB

7 flyback supply voltage

GUARD 8 guard output

FEEDB 9 feedback input

Fig.1 Block diagram.

handbook, halfpage

MED750

INA

1

2

INB

V

3

P

OUTB

4

5

GND

OUTA

V

FB

GUARD

FEEDB

TDA4866

6

7

8

9

MED751

Fig.2 Pin configuration.

1996 Oct 10 3

Philips Semiconductors Product specification

Full bridge current driven vertical

deflection booster

FUNCTIONAL DESCRIPTION

The TDA4866 consists of a differential input stage, two

output stages, a flyback generator, a protection circuit for

the output stages and a guard circuit.

Differential input stage

The differential input stage has a high CMRR differential

current mode input (pins 1 and 2) that results in a high

electro-magnetic immunity and is especially suitable for

driver units with differential (e.g. TDA4850/51/55) and

single ended current signals. Driver units with voltage

outputs are simply applicable as well (e.g. two additional

resistors are required).

The differential input stage delivers the driver signals for

the output stages.

Output stages

The two output stages are current driven in opposite phase

and operate in combination with the deflection coil in a full

bridge configuration. Therefore the TDA4866 requires no

external coupling capacitor (e.g. 2200 µF) and operates

with one supply voltage V

flyback supply voltage V

through the coil (I

defl

which produces a voltage drop (Urm) of: Urm≈ Rm× I

At the feedback input (pin 9) a part of I

input stage. The feedback input has a current input

characteristic which holds the differential voltage between

pin 9 and the output pin 4 on zero. Therefore the feedback

current (I

I

9

R

---------R

ref

m

) through R

9

I

×≈

defl

The input stage directly compares the driver currents into

pins 1 and 2 with the feedback current I

this comparison leads to a more or less driver current for

the output stages. The relation between the deflection

current and the differential input current (I

R

I

idI9

---------R

m

ref

I

×≈=

defl

Due to the feedback loop gain (V

bondwire resistance (R

to determine the accurate value of I

and a separate adjustable

P

only. The deflection current

FB

) is measured with the resistor R

is fed back to the

defl

is:

ref

. Any difference of

9

) is:

id

) and internal

U loop

) correction factors are required

bo

:

defl

m

defl

.

TDA4866

R

I

deflIid

with R

for I

≈ 70 mΩ and

bo

1

–

1

---------------- V

Uloop

= 0.7 A.

defl

ref

× 1

-----------------------RmRbo+

0.98≈

×=

The deflection current can be adjusted up to ±1 A by

varying R

when Rm is fixed to 1 Ω.

ref

High bandwidth and excellent transition behaviour is

achieved due to the transimpedance principle this circuit

works with.

Flyback generator

During flyback the flyback generator supplies the output

stage A with the flyback voltage. This makes it possible to

optimize power consumption (supply voltage V

flyback time (flyback voltage VFB). Due to the absence of a

decoupling capacitor the flyback voltage is fully available.

In parallel with the deflection yoke and the damping

resistor (Rp) an additional RC combination (RSP; CSP) is

necessary to achieve an optimized flyback behaviour.

Protection

The output stages are protected against:

• thermal overshoot

• short-circuit of the coil (pins 4 and 6).

Guard circuit

The internal guard circuit provides a blanking signal for the

CRT. The guard signal is active HIGH:

• at thermal overshoot

• when feedback loop is out of range

• during flyback.

The internal guard circuit will not be activated, if the input

signals on pins 1 and 2 delivered from the driver circuit are

out of range or at short-circuit of the coil (pins 4 and 6).

For this reason an external guard circuit can be applied to

detect failures of the deflection (see Fig.6). This circuit will

be activated when flyback pulses are missing, which is the

indication of any abnormal operation.

–

---------------- V

1

Uloop

) and

P

1996 Oct 10 4

Philips Semiconductors Product specification

Full bridge current driven vertical

TDA4866

deflection booster

LIMITING VALUES

In accordance with the Absolute Maximum Rating System (IEC 134); voltages referenced to pin 5 (GND); unless

otherwise specified.

SYMBOL PARAMETER MIN. MAX. UNIT

V

P

V

FB

I

FB

V

1,V2

I

1,I2

,V

V

4

6

I

4,I6

V

9

I

9

V

8

I

8

T

stg

T

amb

T

j

V

es

supply voltage (pin 3) 0 30 V

flyback supply voltage (pin 7) 0 60 V

flyback supply current 0 ±1.8 A

input voltage 0 V

P

V

input current 0 ±5mA

output voltage 0 V

P

V

output current (note 1) 0 ±1.8 A

feedback voltage 0 V

P

V

feedback current 0 ±5mA

guard voltage (note 2) 0 VP+ 0.4 V

guard current 0 ±5mA

storage temperature −20 +150 °C

operating ambient temperature −20 +75 °C

junction temperature (note 3) −20 +150 °C

electrostatic handling for all pins (note 4) −500 +500 V

Notes

1. Maximum output currents I

and I6 are limited by current protection.

4

2. For VP> 13 V the guard voltage V8 is limited to 13 V.

3. Internally limited by thermal protection; switching point ≥ 150 °C.

4. Equivalent to discharging a 200 pF capacitor through a 0 Ω series resistor.

THERMAL CHARACTERISTICS

SYMBOL PARAMETER VALUE UNIT

R

th j-mb

thermal resistance from junction to mounting base 4 K/W

1996 Oct 10 5

Loading...

Loading...