Philips TDA4821P Datasheet

INTEGRATED CIRCUITS

DATA SH EET

TDA4821P

Autosize IC for colour monitors

Product specification

File under Integrated Circuits, IC02

2000 Feb 09

Philips Semiconductors Product specification

Autosize IC for colour monitors TDA4821P

FEATURES

• Measuring of six horizontal and four vertical timing

parameters as follows:

– Horizontal:syncwidth,sync period, video start, video

end and horizontal flyback pulse start and end

– Vertical: sync width, sync period, first line of video

active and last line of video active.

• Detection of H-sync and V-sync polarity

• I2C-bus interface (maximum clock frequency 400 kHz)

for read-out of data and write data of the internal clock

multiplier using double byte (16-bit format)

• Flexible digital clock input with built-in and (via I2C-bus)

adjustable clock multiplier; internal clock is 48 MHz

(typical value)

• Horizontal measurements are expressed in number of

clock pulses; precision is approximately 20 ns at

48 MHz and can be improved if external averaging

methods are used

• Vertical measurements are expressed in number of

lines

• Internal buffer keep I2C-bus registers stable between

the V-sync pulses, allowing for asynchronous read-out.

The advantages are:

• A more user friendlyadjustment forany undefinedvideo

mode by simply pressing a button

• Factory alignment for a reduced number of modes

• Saving of EEPROM storage space for factory and user

modes.

The activation of the autosizing function can be done on

user command or automatically on any mode change.

Whenautosizing isactivated whilethescreen isonly partly

active or consists of sub-windows, the picture size will

increase, butnot more than therange limits of themonitor

allow.

GENERAL DESCRIPTION

The TDA4821P performs the ‘autosize’ feature for colour

monitors. The IC measures the timing of active H/V video

withrespect tothe H-syncand V-syncpulsesand alsowith

respect tothe horizontal flybackpulse in orderto allow the

microcontrollerto adjustthe displaysettingsautomatically,

in particularparameters HSIZE, VSIZE,HPOS andVPOS.

ORDERING INFORMATION

TYPE

NUMBER

TDA4821P DIP20 plastic dual in-line package; 20 leads (300 mil) SOT146-1

NAME DESCRIPTION VERSION

PACKAGE

2000 Feb 09 2

Philips Semiconductors Product specification

Autosize IC for colour monitors TDA4821P

QUICK REFERENCE DATA

Voltages measured with respect to pins V

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

V

DD(core)

V

DD(I/O)

V

DD(PLL)

V

VIN1

core supply voltage (pin 15) 3 3.3 3.6 V

I/O supply voltage (pin 6) 3 3.3 3.6 V

PLL supply voltage (pin 3) 3 3.3 3.6 V

video channel 1 input voltage

(pin 1)

V

VIN2

video channel 2 input voltage

(pin 2)

V

VIN3

video channel 3 input voltage

(pin 19)

V

clamp(ref)

default clamping level for video

channel inputs (pins 1, 2 and 19)

V

slice

slicing voltage for video

comparators

f

clk(ext)

external input clock frequency

(pin 4)

f

clk(int)

M

clk

t

res(h)

internal clock frequency f

clock multiplying factor adjustable via I2C-bus 1 − 8 −

time resolution for horizontal

measurements

f

SCL

I2C-bus serial clock frequency −−400 kHz

SS(I/O)

and V

SS(core)

.

AC-coupled with 10 nF 0 − VDD− 0.5 V

AC-coupled with 10 nF 0 − VDD− 0.5 V

AC-coupled with 10 nF 0 − VDD− 0.5 V

internal default value 360 400 440 mV

450 500 550 mV

4 − 16 MHz

clk(int)=fclk(ext)

without external

× M

clk

18 48 72 MHz

− 20 − ns

averaging methods;

f

= 48 MHz

clk(int)

2000 Feb 09 3

Philips Semiconductors Product specification

Autosize IC for colour monitors TDA4821P

BLOCK DIAGRAM

handbook, full pagewidth

R, G, B

video

inputs

horizontal

vertical

+3.3 V

+3.3 V

sync

pulse

sync

pulse

V

DD(PLL)

V

SS(I/O)

V

DD(I/O)

VIN1

VIN2

CLK

HS

VS

1

20

LEV

VIDEO COMPARATORS

2

3

4

5

6

7

8

CLOCK PLL

DIGITAL CORE

HORIZONTAL

POLARITY

DETECTION

VERTICAL

POLARITY

DETECTION

VERTICAL

MEASUREMENT

TDA4821P

TEST MODES

HORIZONTAL

MEASUREMENT

19

18

17

16

15

14

VIN3

T1

CLP

V

SS(core)

V

DD(core)

T2

+3.3 V

video

clamping

pulse

+3.3 V

horizontal

flyback

pulse

POR

HFB

9

10

POWER-ON

RESET

Syncpol

Fig.1 Block diagram.

2000 Feb 09 4

VlstVid

VfstVid

Vperiod

VsWidth

I2C-BUS REGISTERS

Rddat

Subaddr

I2C-BUS

INTERFACE

HsWidth

Wren

Hperiod

Wrdat

HlstVid

HfstVid

Hfbstrt

Hfbstop

MHB651

13

SDA

12

SCL

11

TC

Philips Semiconductors Product specification

Autosize IC for colour monitors TDA4821P

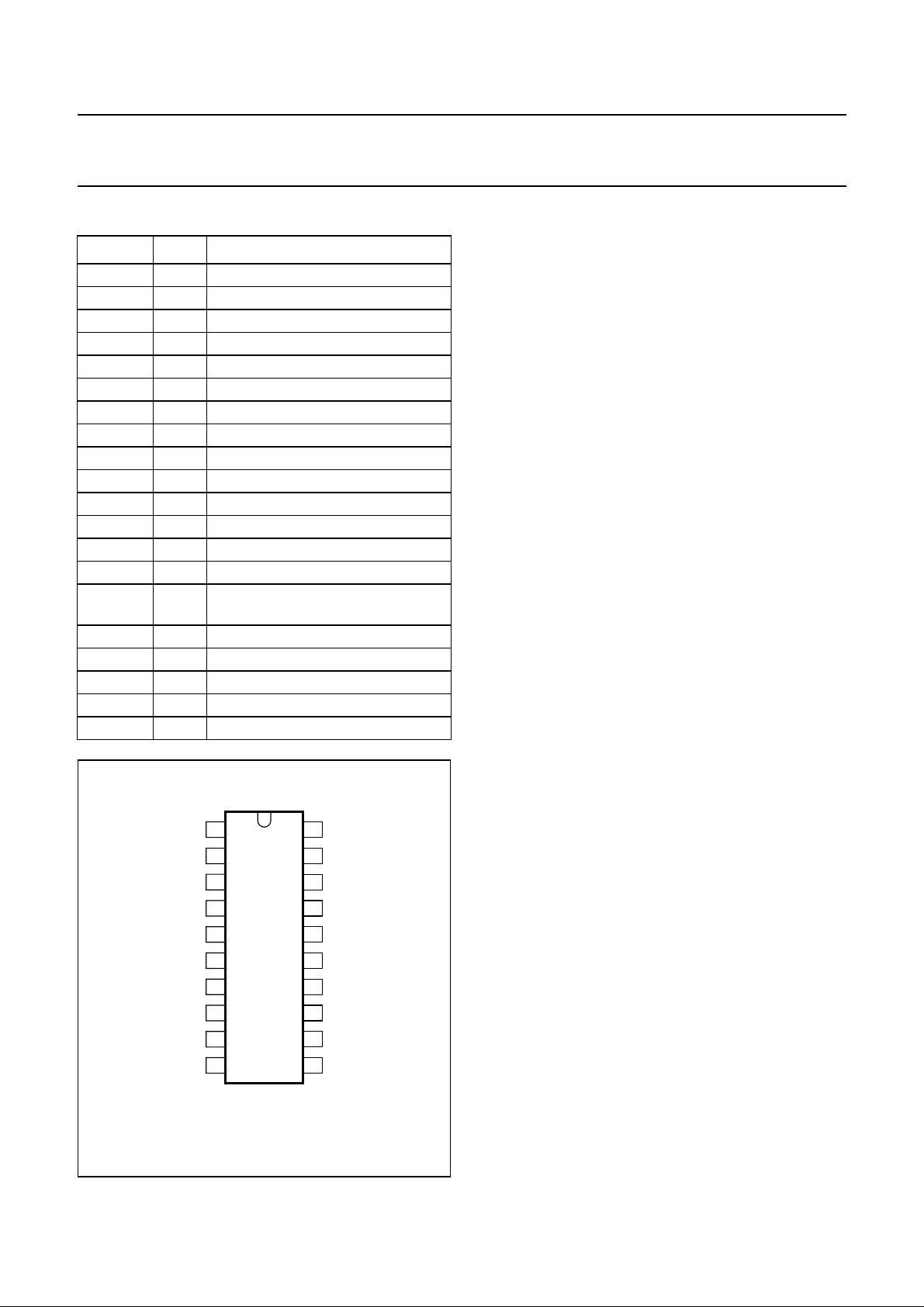

PINNING FUNCTIONAL DESCRIPTION

SYMBOL PIN DESCRIPTION

VIN1 1 video channel 1 input

VIN2 2 video channel 2 input

V

DD(PLL)

3 analog supply voltage of PLL

CLK 4 clock input

V

SS(I/O)

V

DD(I/O)

5 ground of input/output circuit

6 supply voltage of input/output circuit

HS 7 horizontal sync pulse input

VS 8 vertical sync pulse input

POR 9 Power-on reset input

HFB 10 horizontal flyback pulse input

TC 11 test control input

SCL 12 I

SDA 13 I

2

C-bus serial clock input

2

C-bus serial data input/output

T2 14 test mode 2 input

V

DD(core)

15 supply voltage of digital core and

comparator

V

SS(core)

16 ground of digital core

CLP 17 video clamping pulse input

T1 18 test mode 1 input

VIN3 19 video channel 3 input

LEV 20 video clamping level input

The TDA4821P consists of an RGB video comparator

input stage (see Fig.1), a clock PLL for multiplying the

external clock and a digital core which includes the

comparators forH-sync, V-sync and H-flybackpulses, the

polarity detection, the horizontal and vertical time

measurement blocks, the I2C-bus registers and interface

and the Power-on reset circuitry.

RGB video input stage

Three video input comparators are provided, suitable for

AC-coupling with capacitors of approximately 10 nF on

each input. The input pins VIN1, VIN2 and VIN3 are

suitable forthe RGBvideo signals. Thethree input signals

are internally applied to an OR-circuit, so the presence of

one video signal is sufficient to activate the capture

registers.

A positive pulse is needed on pin CLP for black level

clamping. This clamping pulse must not coincide with a

possible Sync-On-Green (SOG) because SOG will not be

detected by this IC.

The black level of the video signal on pins VIN1, VIN2

and VIN3 is clamped internally to 400 mV (typical value).

This clamping level is determined by an internal divider

which is available on pin LEV and can be adjusted by an

additional external resistor divider connected to pin LEV

(see Fig.5).A small HF decoupling capacitor isneeded on

pin LEV.

handbook, halfpage

V

VIN1

VIN2

DD(PLL)

CLK

V

SS(I/O)

V

DD(I/O)

POR

HFB

HS

VS

1

2

3

4

5

TDA4821P

6

7

8

9

10

MHB652

20

19

18

17

16

15

14

13

12

11

LEV

VIN3

T1

CLP

V

SS(core)

V

DD(core)

T2

SDA

SCL

TC

Fig.2 Pin configuration.

2000 Feb 09 5

The video slicing level for the detection of active video is

500 mV(typical value).This level isapproximately 100 mV

above the blacklevel and is fixed byan additional internal

resistor divider fromthe 3.3 V supply voltage; it cannot be

modified. All signals which exceed this level are

recognized as active video. The difference between the

video slicing level andthe clamping level is adjustable via

pin LEV.

Example: changing the voltage on pin LEV from

400 to 200 mV increases the threshold voltage for the

detection of active video from 100 to 300 mV.

Philips Semiconductors Product specification

Autosize IC for colour monitors TDA4821P

Clock PLL

In order to measure the horizontal timing with sufficient

precision, it is recommended to set the frequency of the

internalreference clockto 48 MHz.Thisclock isgenerated

by amultiplying PLL fromthe external clocksignal applied

to pin CLK. The ratio between the internal and external

clock frequency (clock multiply factor is M

clk

) is

programmable from 1 to 8 (viathe I2C-bus). For instance,

for an externalclock frequency of 8 MHz, a multiply factor

M

= 6is neededto achieveaninternal referenceclock of

clk

48 MHz.

After power-on of the IC and with an inactive I2C-bus, the

default value of factor M

is set to 2.

clk

Sync and flyback pulse comparators and polarity

detection

The horizontal and vertical sync pulse input circuits on

pins HS and VS are able to handle both 5 or 3.3 V level

H/V sync pulses. The H-sync and V-sync signals are

internally preprocessed by edge detectors which deliver

positive pulses at the rising and falling edges of the input

signals and are followed by auto-polarity correction

stages. The polarity status of both sync signals will be

detected and corrected and is available as the I2C-bus

status bits Hpol and Vpol. A positive polarity means that

the duty cycle is smaller than 50% (bit Hpol = 0 or

bit Vpol = 0) and for a negative polarity the duty cycle is

larger than 50%.

The horizontal flyback pulse on pin HFB is internally

preprocessed by an edgedetector in the same way asfor

H-sync and V-sync pulses. The measurement of the

position of the horizontal flyback pulse provides further

information for the monitor microcontroller for a correct

auto-adjustment of the picture within the scanned raster

area.

Horizontal and vertical timing measurements

For eachvertical period the IC performs sixhorizontal and

four vertical measurements (see Figs 3 and 4).

The leadingedge of the nextvertical sync pulseis used to

transfer the previous measurement results to the I2C-bus

data read registers and to reset the internal counters for

the next full timing measurement cycle. In this way the

I2C-bus data registers will always contain stable

sample-and-hold data(assuming that thesync signalsare

stable) and they can be read-out via the I2C-bus by an

external microcontroller for automatic adaption of the

display geometry.

Moreover, measuring the width of the sync pulses gives

more advantages such as:

• A better mode discrimination

• In some cases the horizontal PLL of the deflection

controllers operates on the leading edge of the sync

pulse, in other cases in the middle of the sync pulse.

VERTICAL TIMING MEASUREMENTS

The parameters are measuredwith respect to the leading

edgeof theV-sync pulse(see Fig.3).At eachleading edge

of the V-sync pulse on pin VS a 12-bit counter is started.

The four vertical timings (see Table 1) are counted as a

number of H-sync pulses on pin HS and stored in buffer

registers.The contentsof thesebuffer registersare copied

to the I2C-bus registers on every next V-sync pulse with

the additionof LSBs (logic 0) forcompleting the full2-byte

data (see Table 4).

The maximum line count is 4095. With Enhanced

Graphics Adapter (EGA) systems with approximately

400 lines at 31.45 kHz, the lower line count will be 9 bits

long only but the resolution is still better than 0.25%. No

provisions are included for recognizing interlaced sync

signals with or without equal vertical periods.

2000 Feb 09 6

Loading...

Loading...