Philips TDA4680WP-V6, TDA4680-V6 Datasheet

DATA SH EET

Product specification

Supersedes data of April 1993

File under Integrated Circuits, IC02

1996 Oct 25

INTEGRATED CIRCUITS

TDA4680

Video processor with automatic

cut-off and white level control

1996 Oct 25 2

Philips Semiconductors Product specification

Video processor with automatic cut-off

and white level control

TDA4680

FEATURES

• Operates from an 8 V DC supply

• Black level clamping of the colour difference, luminance

and RGB input signals with coupling-capacitor DC level

storage

• Two fully-controlled, analog RGB inputs, selected either

by fast switch signals or via I2C-bus

• Saturation, contrast and brightness adjustment via

I2C-bus

• Same RGB output black levels for Y/CD and RGB input

signals

• Timing pulse generation from either a 2 or 3-level

sandcastle pulse for clamping, horizontal and vertical

synchronization, cut-off and white level timing pulses

• Automatic cut-off control with picture tube leakage

current compensation

• Software-based automatic white level control or fixed

white levels via I

2

C-bus

• Cut-off and white level measurement pulses in the last

4 lines of the vertical blanking interval (I2C-bus selection

for PAL, SECAM, or NTSC, PAL-M)

• Increased RGB signal bandwidths for progressive scan

and 100 Hz operation (selected via I2C-bus)

• Two switch-on delays to prevent discolouration before

steady-state operation

• Average beam current and peak drive limiting

• PAL/SECAM or NTSC matrix selection via I2C-bus

• Three adjustable reference voltage levels (via I2C-bus)

for automatic cut-off and white level control

• Emitter-follower RGB output stages to drive the video

output stages

• Hue control output for the TDA4555, TDA4650/T,

TDA4655/T or TDA4657.

GENERAL DESCRIPTION

The TDA4680 is a monolithic integrated circuit with a

colour difference interface for video processing in TV

receivers. Its primary function is to process the luminance

and colour difference signals from multistandard colour

decoders, TDA4555, TDA4650/T, TDA4655/T or

TDA4657, Colour Transient Improvement (CTI) IC,

TDA4565, Picture Signal Improvement (PSI) IC,

TDA4670, or from a feature module.

The required input signals are:

• Luminance and negative colour difference signals

• 2 or 3-level sandcastle pulse for internal timing pulse

generation

• I2C-bus data and clock signals for microcontroller

control.

Two sets of analog RGB colour signals can also be

inserted, e.g. one from a peritelevision connector and the

other from an on-screen display generator; both inputs are

fully-controlled internally. The TDA4680 includes full

I2C-bus control of all parameters and functions with

automatic cut-off and white level control of the picture tube

cathode currents. It provides RGB output signals for the

video output stages.

There is a very similar IC TDA4681 available. The only

differences are in the NTSC matrix.

ORDERING INFORMATION

TYPE NUMBER

PACKAGE

NAME DESCRIPTION VERSION

TDA4680 DIP28 plastic dual in-line package; 28 leads (600 mil) SOT117-1

TDA4680WP PLCC28 plastic leaded chip carrier; 28 leads SOT261-2

1996 Oct 25 3

Philips Semiconductors Product specification

Video processor with automatic cut-off

and white level control

TDA4680

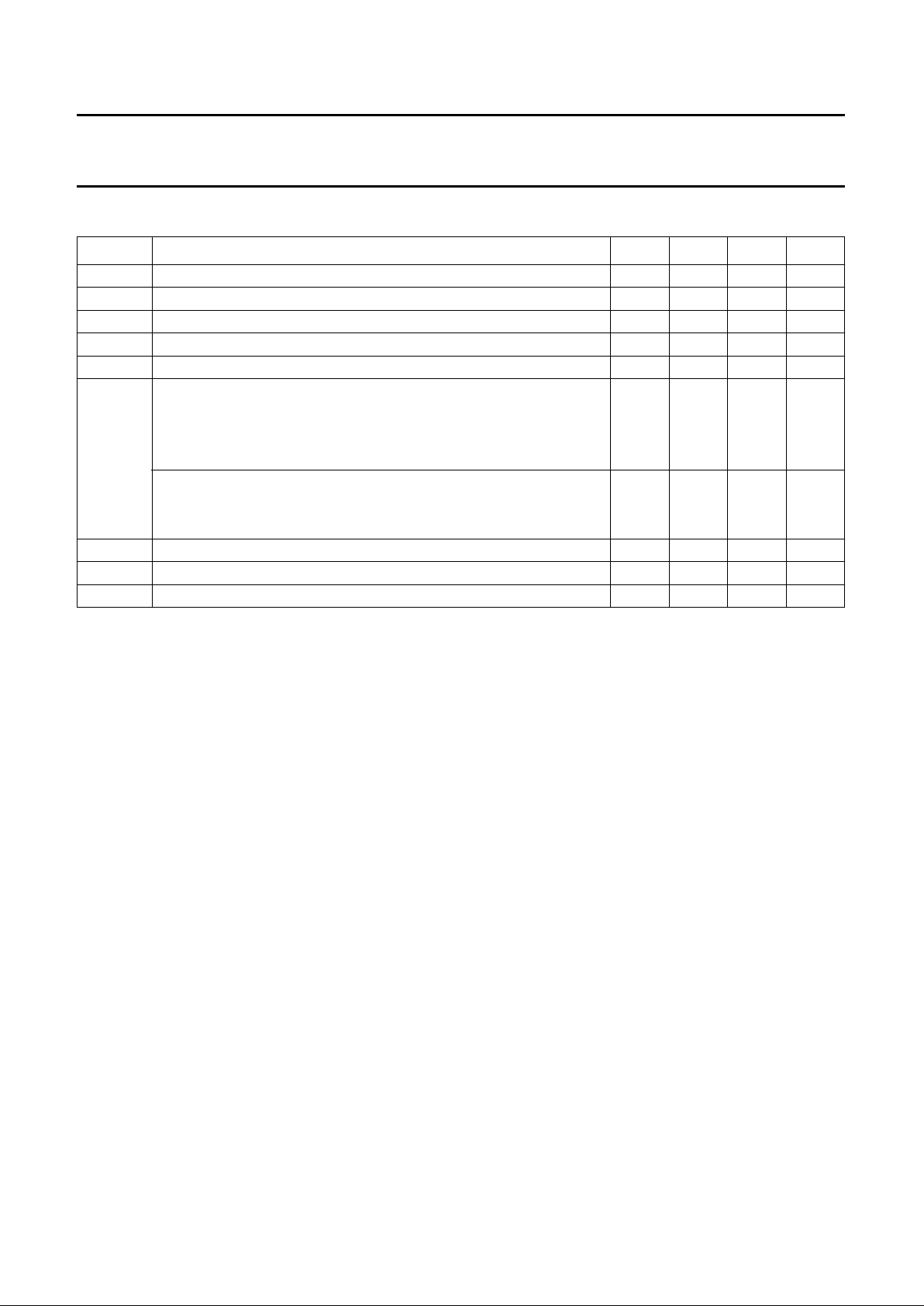

QUICK REFERENCE DATA

SYMBOL PARAMETER MIN. TYP. MAX. UNIT

V

P

supply voltage (pin 5) 7.2 8.0 8.8 V

I

P

supply current (pin 5) − 85 − mA

V

8(p-p)

luminance input (peak-to-peak value) − 0.45 − V

V

6(p-p)

−(B − Y) input (peak-to-peak value) − 1.33 − V

V

7(p-p)

−(R − Y) input (peak-to-peak value) − 1.05 − V

V

14

3-level sandcastle pulse

H+V − 2.5 − V

H − 4.5 − V

BK − 8.0 − V

2-level sandcastle pulse

H+V − 2.5 − V

BK − 4.5 − V

V

i(p-p)

RGB input signals at pins 2, 3, 4, 10, 11 and 12 (peak-to-peak value) − 0.7 − V

V

o(b-w)

RGB outputs at pins 24, 22 and 20 (black-to-white value) − 2.0 − V

T

amb

operating ambient temperature 0 − 70 °C

1996 Oct 25 4

Philips Semiconductors Product specification

Video processor with automatic cut-off and

white level control

TDA4680

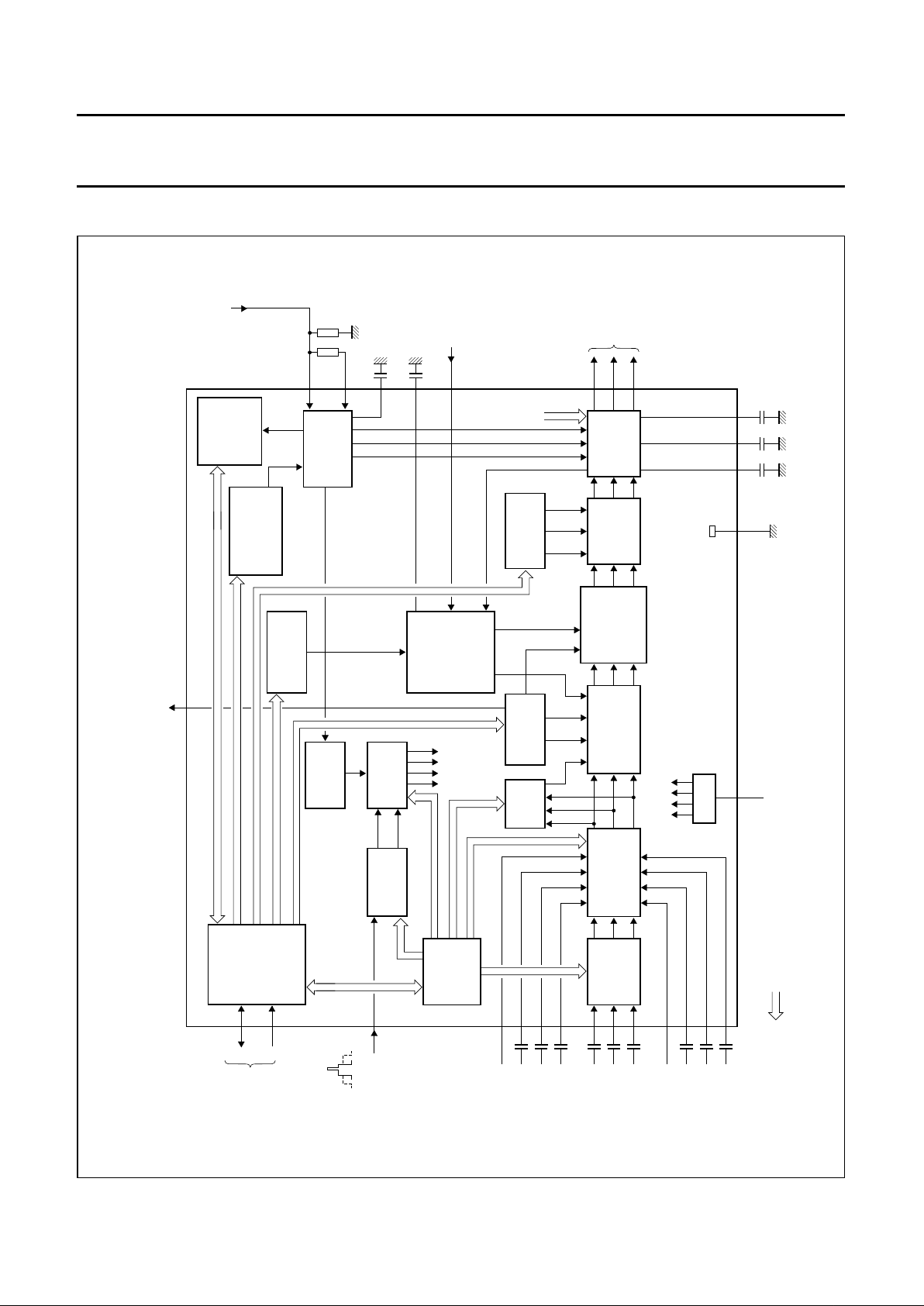

BLOCK DIAGRAM

handbook, full pagewidth

TDA4680

PAL/SECAM,

NTSC

MATRIX

FAST SIGNAL

SOURCE SWITCH,

BLANKING 1

SATURATION

AND CONTRAST

ADJUST

BRIGHTNESS

ADJUST,

BLANKING 2,

MEASUREMENT

PULSES

WHITE

POINT

ADJUST

CUT-OFF

ADJUST,

OUTPUT

STAGES

R

G

B

R

G

B

R

G

B

R

G

B

R

G

B

R

G

B

242220

8

7

6

2

3

4

1

101112

13

R

G

B

2

2

2

R

G

B

1

1

1

Y

−(R − Y)

−(B − Y)

9

R

4 x 6-BIT

D/A

CONVERTERS

3 x 6-BIT

D/A

CONVERTERS

PEAK DRIVE

AND

AVERAGE

BEAM CURRENT

LIMITING

2 x 8-BIT

CONTROL

REGISTERS

Y-MATRIX

SANDCASTLE

PULSE

DETECTOR

TIMING

GENERATOR

BK

H + V

(H)

sandcastle

pulse

14

6-BIT D/A

CONVERTER

1ST AND 2ND

SWITCH-ON

DELAYS

WHITE LEVEL

AND CUT-OFF

COMPARATORS

3 x 2-BIT

WHITE LEVEL

REGISTERS

AND

PONRES

3 x 6-BIT

REFERENCE

REGISTERS,

D/A CONVERTER

I

2

C-BUS

TRANSCEIVER

27

28

SDA

SCL

26

hue control voltage

15

16

average

beam

current

17

timing

pulses

V = 8 V

P

5

leakage,

cut-off and

white level

current

input

18

19

PONRES, CB0 and CB1,

CG0 and CG1, CR0 and CR1

A75 to A70, A85 to A80, A95 to A90

A45 to A40, A55 to A50, A65 to A60

AA5 to AA0

A05 to A00, A15 to A10, A25 to A20, A35 to A30

BREN

SC5

DELOF

BCOF, FSBL, FSWL, WPEN,

VBW2, VBW1, VBW0

SATOF

FSDIS2, FSON2,

FSDIS1, FSON1

NMEN

R

W

R

C

RGB

outputs

SUPPLY

GB

21 23 25

cut-off storage

leakage

storage

peak drive

limiting

storage

white

level

control

cut-off

control

I

2

C-bus

I

2

C-bus data and

control signals

RAR

BCOF

FSW

1

FSW

2

MED693

Fig.1 Block diagram.

1996 Oct 25 5

Philips Semiconductors Product specification

Video processor with automatic cut-off

and white level control

TDA4680

PINNING

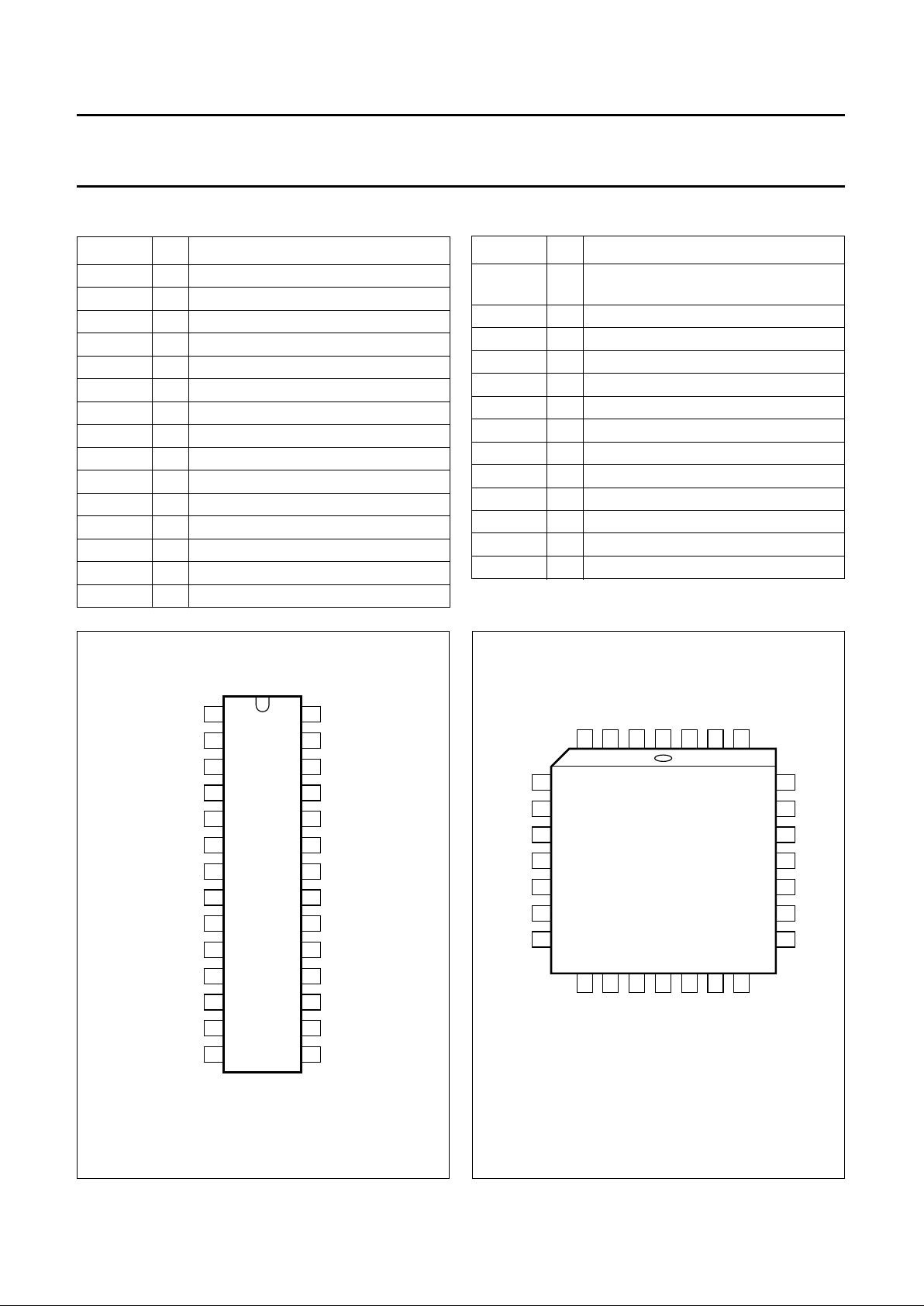

SYMBOL PIN DESCRIPTION

FSW

2

1 fast switch 2 input

R

2

2 red input 2

G

2

3 green input 2

B

2

4 blue input 2

V

P

5 supply voltage

−(B − Y) 6 colour difference input −(B − Y)

−(R − Y) 7 colour difference input −(R −Y)

Y 8 luminance input

GND 9 ground

R

1

10 red input 1

G

1

11 green input 1

B

1

12 blue input 1

FSW

1

13 fast switch 1 input

SC 14 sandcastle pulse input

BCL 15 average beam current limiting input

C

PDL

16

storage capacitor for peak drive

limiting

C

L

17 storage capacitor for leakage current

WI 18 white level measurement input

CI 19 cut-off measurement input

B

O

20 blue output

C

B

21 blue cut-off storage capacitor

G

O

22 green output

C

G

23 green cut-off storage capacitor

R

O

24 red output

C

R

25 red cut-off storage capacitor

HUE 26 hue control output

SDA 27 I

2

C-bus serial data input/output

SCL 28 I

2

C-bus serial clock input

SYMBOL PIN DESCRIPTION

Fig.2 Pin configuration for DIP-version.

handbook, halfpage

TDA4680

MED694

1

2

3

4

5

6

7

8

9

10

11

12

13

14

FSW

2

R

2

G

2

B

2

V

P

−(B − Y)

−(R − Y)

Y

GND

R

1

G

1

B

1

FSW

1

SC

SCL

SDA

HUE

C

R

R

O

C

G

G

O

C

B

B

O

CI

WI

C

L

C

PDL

BCL

28

27

26

25

24

23

22

21

20

19

18

17

16

15

Fig.3 Pin configuration for PLCC-version.

TDA4680WP

MED695

5

6

7

8

9

10

11

V

P

−(B − Y)

−(R − Y)

Y

GND

R

1

G

1

C

R

R

O

C

G

G

O

C

B

B

O

CI

B2G2R2FSW2SCL

SDA

HUE

B

1

FSW

1

SC

BCLCPDL

C

L

WI

25

24

23

22

21

20

19

12

13

14

15

16

17

18

4

3

2

1

28

27

26

1996 Oct 25 6

Philips Semiconductors Product specification

Video processor with automatic cut-off

and white level control

TDA4680

I2C-BUS

Control

The I

2

C-bus transmitter/receiver provides the data bytes to

select and adjust the following functions and parameters:

• Brightness adjust

• Saturation adjust

• Contrast adjust

• Hue control voltage

• RGB gain adjust

• RGB reference voltage levels

• Peak drive limiting

• Selection of the vertical blanking interval and

measurement lines for cut-off and white level control

according to transmission standard

• Selects either 3-level or 2-level (5 V) sandcastle pulse

• Enables/disables input clamping pulse delay

• Enables/disables white level control

• Enables cut-off control; enables output clamping

• Enables/disables full screen white level

• Enables/disables full screen black level

• Selects either PAL/SECAM or NTSC matrix

• Enables saturation adjust; enables nominal saturation

• Enables/disables synchronization of the execution of

I2C-bus commands with the vertical blanking interval

• Reads the result of the comparison of the nominal and

actual RGB signal levels for automatic white level

control.

I

2

C-bustransmitter/receiver and data transfer

I

2

C-BUS SPECIFICATION

The I2C-bus is a bidirectional, two-wire, serial data bus for

intercommunication between ICs in a system.

The microcontroller transmits/receives data from the

I2C-bus transceiver in the TDA4680 over the serial data

line SDA (pin 27) synchronized by the serial clock line SCL

(pin 28). Both lines are normally connected to a positive

voltage supply through pull-up resistors. Data is

transferred when the SCL line is LOW. When SCL is HIGH

the serial data line SDA must be stable. A HIGH-to-LOW

transition of the SDA line when SCL is HIGH is defined as

a START bit. A LOW-to-HIGH transition of the SDA line

when SCL is HIGH is defined as a STOP bit.

Each transmission must start with a START bit and end

with a STOP bit. The bus is busy after a START bit and is

only free again after a STOP bit has been transmitted.

I

2

C-BUS RECEIVER (MICROCONTROLLER WRITE MODE)

Each transmission to/from the I2C-bus transceiver

consists of at least three bytes following the START bit.

Each byte is acknowledged by an acknowledge bit

immediately following each byte. The first byte is the

Module Address (MAD) byte, also called slave address

byte. This consists of the module address, 1000100 for the

TDA4680, plus the R/W bit (see Fig.4). When the

TDA4680 is a slave receiver (R/W = 0) the module

address byte is 10001000 (88H). When the TDA4680 is a

slave transmitter (R/W = 1) the module address byte is

10001001 (89H).

The length of a data transmission is unrestricted, but the

module address and the correct sub-address must be

transmitted before the data byte(s). The order of data

transmission is shown in Figs 5 and 6.

Without auto-increment (BREN = 0 or 1) the module

address (MAD) byte is followed by a Sub-Address (SAD)

byte and one data byte only (see Fig.5).

1996 Oct 25 7

Philips Semiconductors Product specification

Video processor with automatic cut-off

and white level control

TDA4680

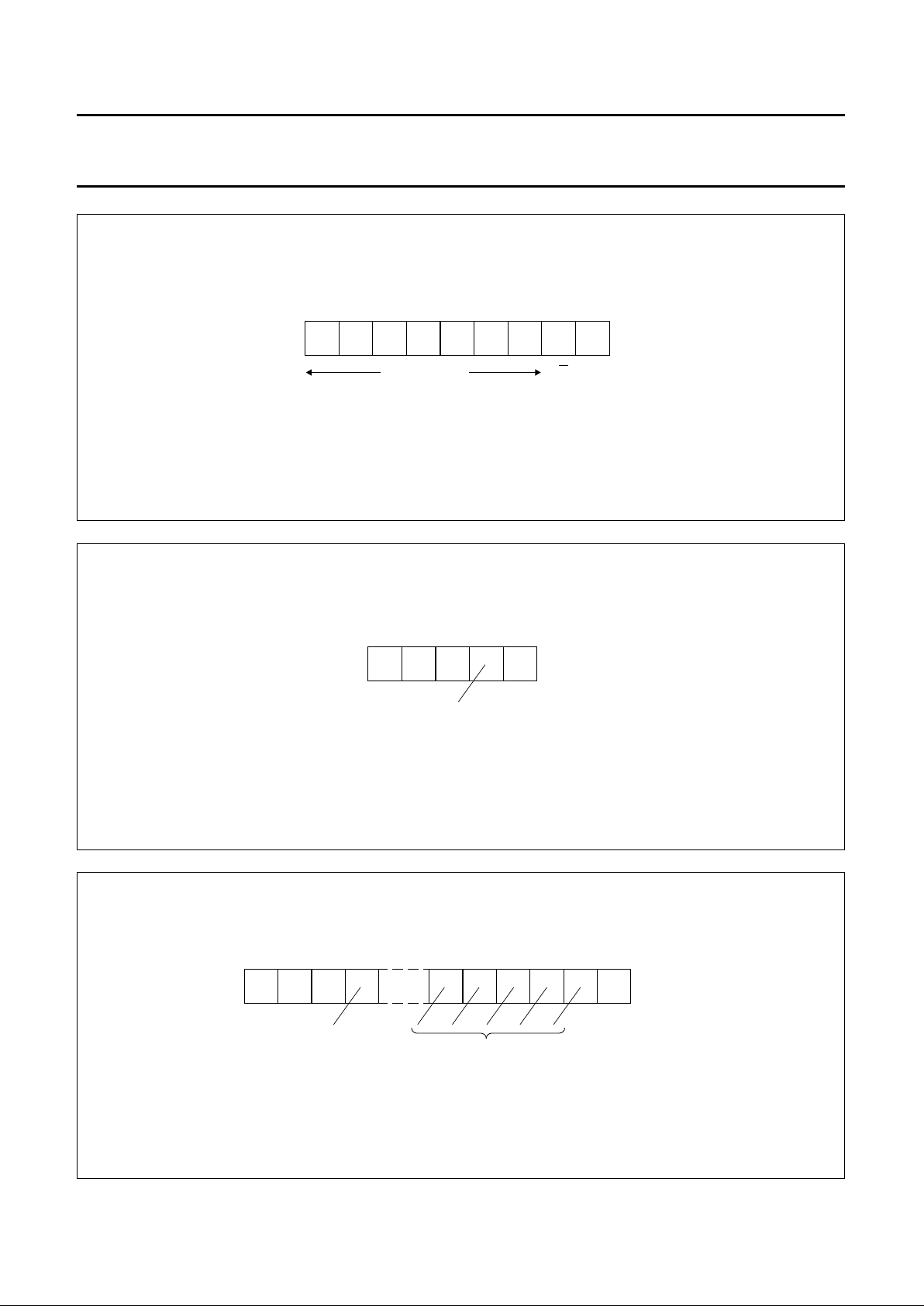

Fig.4 The module address byte.

handbook, full pagewidth

ACKX

R/W

00100

module address

01

MSB LSB

MED696

Fig.5 Data transmission without auto-increment (BREN = 0 or 1).

handbook, full pagewidth

STOSAD

START

condition

data byte

STOP

condition

MADSTA

MED697

Fig.6 Data transmission with auto-increment (BREN = 0).

handbook, full pagewidth

SAD

START

condition

data byte

STOP

condition

MADSTA

MED698

STO

data bytes

1996 Oct 25 8

Philips Semiconductors Product specification

Video processor with automatic cut-off

and white level control

TDA4680

AUTO-INCREMENT

The auto-increment format enables quick slave receiver

initialization by one transmission, when the I2C-bus control

bit BREN = 0 (see control register bits of Table 1).

If BREN = 1 auto-increment is not possible.

If the auto-increment format is selected, the MAD byte is

followed by a SAD byte and by the data bytes of

consecutive sub-addresses (Fig.6).

All sub-addresses from 00H to 0FH are automatically

incremented, the sub-address counter wraps round from

0FH to 00H. Reserved sub-addresses 0BH, 0EH and 0FH

are treated as legal but have no effect. Sub-addresses

outside the range 00H and 0FH are not acknowledged by

the device and neither auto-increment nor any other

internal operation takes place (for versions V1 to V5

sub-addresses outside the range 00H and 0FH are

acknowledged but neither auto-increment nor any other

internal operation takes place).

Sub-addresses are stored in the TDA4680 to address the

following parameters and functions (see Table 1):

• Brightness adjust

• Saturation adjust

• Contrast adjust

• Hue control voltage

• RGB gain adjust

• RGB reference voltage levels

• Peak drive limiting adjust

• Control register functions.

The data bytes D7 to D0 (see Table 1) provide the data of

the parameters and functions for video processing.

C

ONTROL REGISTER 1

VBWx (Vertical Blanking Window):

x = 0, 1 or 2. VBWx selects the vertical blanking interval

and positions the measurement lines for cut-off and

white level control.

The actual lines in the vertical blanking interval after the

start of the vertical pulses selected as measurement lines

for cut-off and white level control are shown in Table 2.

The standards marked with (*) are for progressive line

scan at double line frequency (2fL), i.e. approximately

31 kHz.

NMEN (NTSC Matrix Enable):

0 = PAL/SECAM matrix

1 = NTSC matrix.

WPEN (White Pulse Enable):

0 = white measuring pulse disabled

1 = white measuring pulse enabled.

BREN (Buffer Register Enable):

0 = new data is executed as soon as it is received

1 = data is stored in buffer registers and is transferred to

the data registers during the next vertical blanking

interval.

The I

2

C-bus transceiver does not accept any new data

until this data is transferred into the data registers.

DELOF (Delay Off) delays the leading edge of clamping

pulses:

0 = delay enabled

1 = delay disabled.

SC5 (SandCastle 5 V):

0 = 3-level sandcastle pulse

1 = 2-level (5 V) sandcastle pulse.

C

ONTROL REGISTER 2

FSON2 (Fast Switch 2 ON)

FSDIS2 (Fast Switch 2 Disable)

FSON1 (Fast Switch 1 ON)

FSDIS1 (Fast Switch 1 Disable)

The RGB input signals are selected by FSON2 and

FSON1 or FSW2 and FSW1:

• FSON2 has priority over FSON1

• FSW2 has priority over FSW

1

• FSDIS1 and FSDIS2 disable FSW1 and FSW

2

(see Table 3).

BCOF (Black level Control Off):

0 = automatic cut-off control enabled

1 = automatic cut-off control disabled; RGB outputs are

clamped to fixed DC levels.

FSBL (Full Screen Black Level):

0 = normal mode

1 = full screen black level (cut-off measurement level

during full field).

FSWL (Full Screen White Level):

0 = normal mode

1 = full screen white level (white measurement level

during full field).

1996 Oct 25 9

Philips Semiconductors Product specification

Video processor with automatic cut-off

and white level control

TDA4680

SATOF (Saturation control Off):

0 = saturation control enabled

1 = saturation control disabled, nominal saturation

enabled.

I

2

C-BUS TRANSMITTER (MICROCONTROLLER READ MODE)

As an I2C-bus transmitter, R/W = 1, the TDA4680 sends a

data byte from the status register to the microcontroller.

The data byte consists of following bits: PONRES, CB1,

CB0, CG1, CG0, CR1, CR0 and 0, where PONRES is the

most significant bit.

PONRES (Power On Reset) monitors the state of

TDA4680’s supply voltage:

0 = normal operation

1 = supply voltage has dropped below approximately

6.0 V (usually occurs when the TV receiver is switched

on or the supply voltage was interrupted).

When PONRES changes state from a logic LOW to a logic

HIGH all data and function bits are set to logic LOW.

2-

BIT WHITE LEVEL ERROR SIGNAL (see Table 4)

CB1, CB0 = 2-bit white level of the blue channel.

CG1, CG0 = 2-bit white level of the green channel.

CR1, CR0 = 2-bit white level of the red channel.

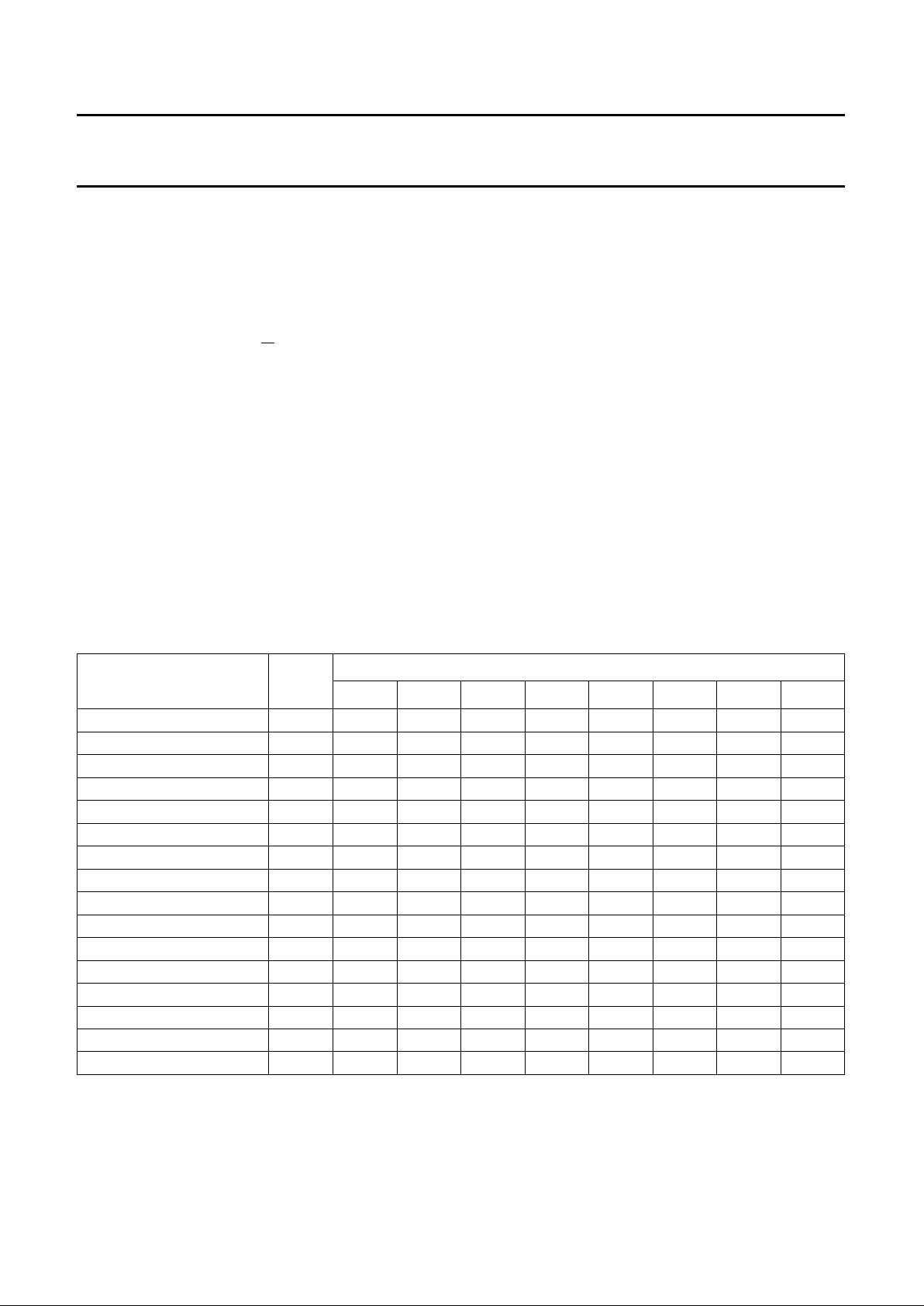

Table 1 Sub-address (SAD) and data bytes; note 1

Note

1. X = don’t care.

FUNCTION

SAD

(HEX)

MSB LSB

D7 D6 D5 D4 D3 D2 D1 D0

Brightness 00 0 0 A05 A04 A03 A02 A01 A00

Saturation 01 0 0 A15 A14 A13 A12 A11 A10

Contrast 02 0 0 A25 A24 A23 A22 A21 A20

Hue control voltage 03 0 0 A35 A34 A33 A32 A31 A30

Red gain 04 0 0 A45 A44 A43 A42 A41 A40

Green gain 05 0 0 A55 A54 A53 A52 A51 A50

Blue gain 06 0 0 A65 A64 A63 A62 A61 A60

Red level reference 07 0 0 A75 A74 A73 A72 A71 A70

Green level reference 08 0 0 A85 A84 A83 A82 A81 A80

Blue level reference 09 0 0 A95 A94 A93 A92 A91 A90

Peak drive limit 0A 0 0 AA5 AA4 AA3 AA2 AA1 AA0

Reserved 0B XXXXXXXX

Control register 1 0C SC5 DELOF BREN WPEN NMEN VBW2 VBW1 VBW0

Control register 2 0D SATOF FSWL FSBL BCOF FSDIS2 FSON2 FSDIS1 FSON1

Reserved 0E XXXXXXXX

Reserved 0F XXXXXXXX

Loading...

Loading...