Philips ne5537, se5537 DATASHEETS

Philips Semiconductors Linear Products Product specification

NE/SE5537Sample-and-hold amplifier

884

August 31, 1994 853-1044 13721

DESCRIPTION

The NE5537 monolithic sample-and-hold amplifier combines the

best features of ion-implanted JFETs with bipolar devices to obtain

high accuracy, fast acquisition time, and low droop rate. This device

is pin-compatible with the LF198, and features superior performance

in droop rate and output drive capability. The circuit shown in Figure

1 contains two operational amplifiers which function as a unity gain

amplifier in the sample mode. The first amplifier has bipolar input

transistors which give the system a low offset voltage. The second

amplifier has JFET input transistors to achieve low leakage current

from the hold capacitor. A unique circuit design for leakage current

cancellation using current mirrors gives the NE5537 a low droop

rate at higher temperature. The output stage has the capability to

drive a 2kΩ load. The logic input is compatible with TTL, PMOS or

CMOS logic. The differential logic threshold is 1.4V with the sample

mode occurring when the logic input is high. It is available in 8-lead

TO-5, 8-pin plastic DIP packages, and 14-pin SO packages.

FEATURES

•Operates from ±5V to ±18V supplies

•Hold leakage current 6pA @ T

J

= 25°C

•Less than 4µs acquisition time

•TTL, PMOS, CMOS compatible logic input

•0.5mV typical hold step at CH=0.01µF

•Low input offset: 1MV (typical)

•0.002% gain accuracy with R

L

=2kΩ

•Low output noise in hold mode

•Input characteristics do not change during hold mode

•High supply rejection ratio in sample or hold

•Wide bandwidth

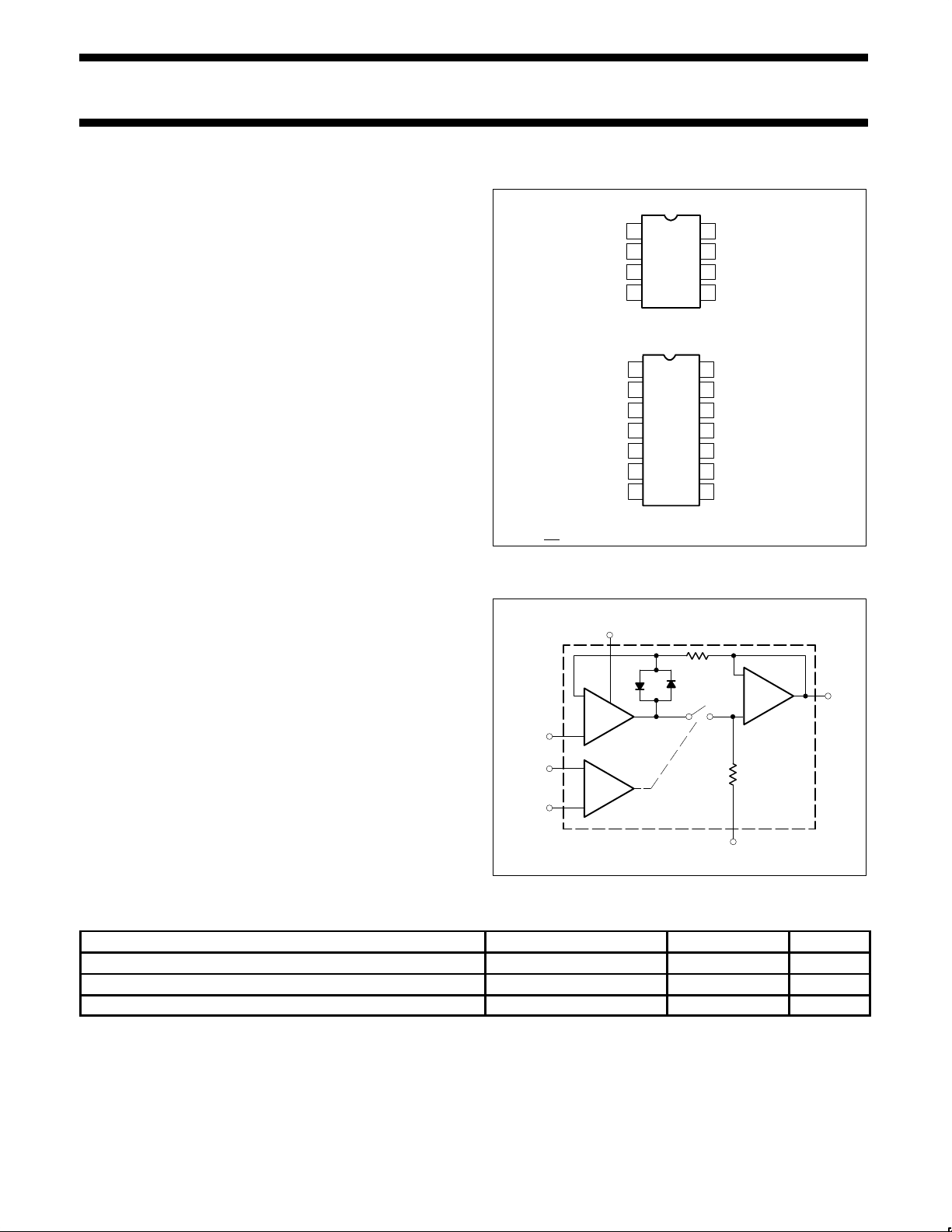

PIN CONFIGURATIONS

FE and N Packages

D

1

Package

NOTE:

1. SO and

non-standard pinouts.

1

2

3

4 5

6

7

8

1

2

3

4

5

6

7 8

14

13

12

11

10

9

V+

OFFSET ADJUST

INPUT

V–

NC

LOGIC

LOGIC REFERENCE

OUTPUT

C

h

V–

INPUT

OUTPUT

NC

NC

V+

LOGIC REFERENCE

NC

C

h

NC

V

OS

ADJ

NC

LOGIC

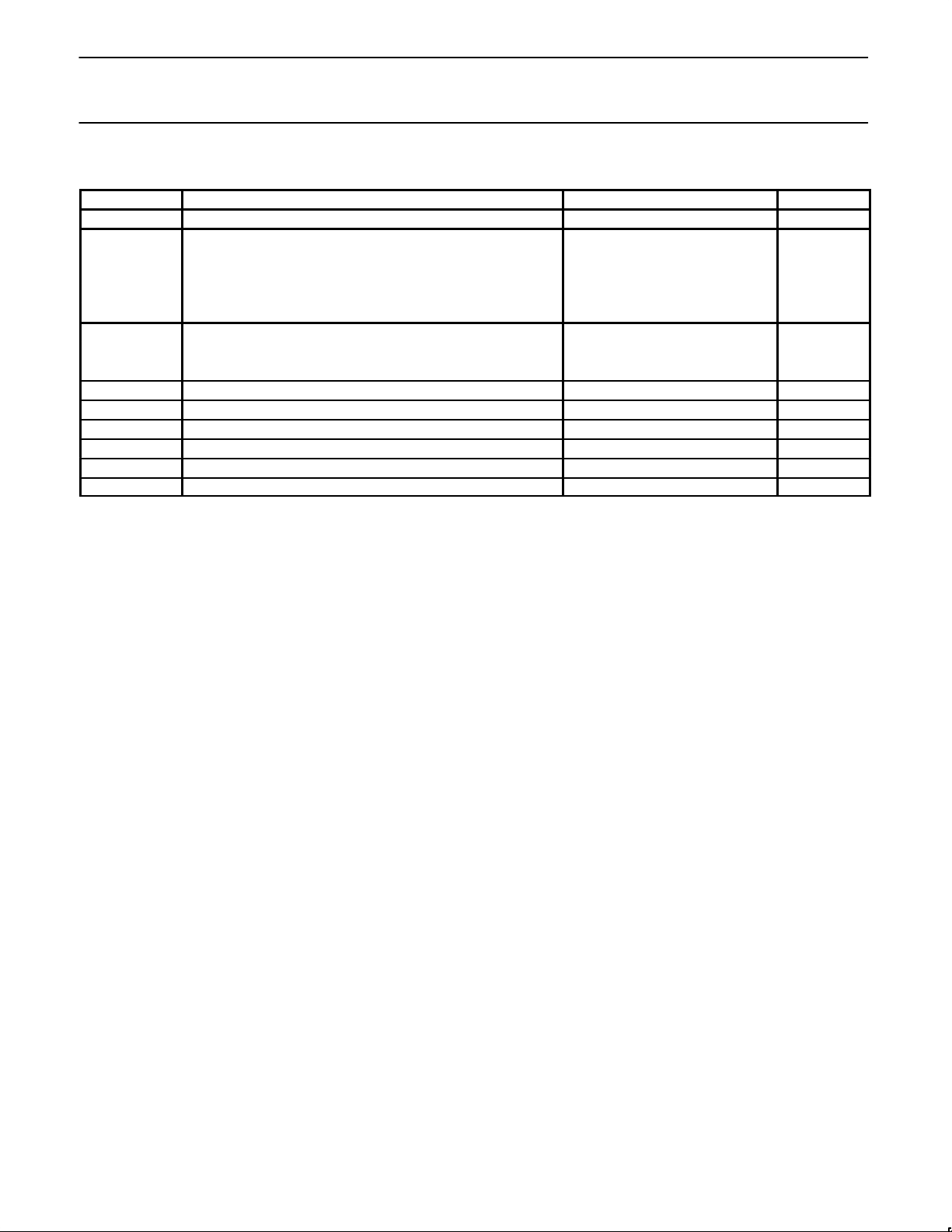

BLOCK DIAGRAM

OFFSET

OUTPUT

INPUT

LOGIC

LOGIC

REFERENCE

HOLD

CAPACITOR

300

30k

2

3

8

7

6

5

–

+

–

+

ORDERING INFORMATION

DESCRIPTION TEMPERATURE RANGE ORDER CODE DWG #

8-Pin Plastic Dual In-Line Package (DIP) 0 to +70°C NE5537N 0404B

14-Pin Plastic Small Outline (SO) Package 0 to +70°C NE5537D 0175D

8-Pin Plastic Dual In-Line Package (DIP) -55°C to +125°C SE5537FE 0404B

Philips Semiconductors Linear Products Product specification

NE/SE5537Sample-and-hold amplifier

August 31, 1994

885

ABSOLUTE MAXIMUM RATINGS

SYMBOL PARAMETER RATING UNIT

V

S

Voltage supply ±18 V

P

D

Maximum power dissipation

T

A

=25°C (still-air)

1

N package 1160 mW

D package 1090 mW

FE package 780 mW

T

A

Operating ambient temperature range

SE5537 -55 to +125 °C

NE5537 0 to +70 °C

T

STG

Storage temperature range -65 to +150 °C

V

IN

Input voltage Equal to supply voltage

Logic to logic reference differential voltage

2

+7, -30 V

Output short circuit duration Indefinite

Hold capacitor short circuit duration 10 s

T

SOLD

Lead soldering temperature (10sec max) 300 °C

NOTES:

1. Derate above 25°C at the following rates:

FE package at 6.2mW/°C

N package at 9.3mW/°C

D package at 8.3mW/°C

2. Although the differential voltage may not exceed the limits given, the common-mode voltage on the logic pins may be equal to the supply

voltages without causing damage to the circuit. For proper logic operation, however, one of the logic pins must always be at least 2V below

the positive supply and 3V above the negative supply.

Philips Semiconductors Linear Products Product specification

NE/SE5537Sample-and-hold amplifier

August 31, 1994

886

DC ELECTRICAL CHARACTERISTICS

1

SE5537 NE5537

SYMBOL

PARAMETER

TEST CONDITIONS

Min Typ Max Min Typ Max

UNIT

TJ=25°C 1 3 2 7 mV

V

OS

Input offset voltage

4

Full temperature range 5 10 mV

TJ=25°C 5 25 10 50 nA

I

BIAS

Input bias current

4

Full temperature range 75 100 nA

Input impedance TJ=25°C 10

10

10

10

Ω

Gain error TJ=25°C 0.002 0.007 0.004 0.01 %

-10V≤VIN≤10V, RL=2kΩ

-11.5V≤V

IN

≤11.5V,

R

L

=10kΩ

Full temperature range 0.02 0.02 %

Feedthrough attenuation

ratio at 1kHz

TJ=25°C, CH=0.01µF 86 96 80 90 dB

Output impedance TJ=25°C, “HOLD” mode 0.5 2 0.5 4 Ω

Full temperature range 4 6

“HOLD” Step

2

TJ=25°C, CH=0.01µF, V

OUT

=0 0.5 2.0 1.0 2.5 mV

I

CC

Supply current

4

TJ=25°C 4.5 6.5 4.5 7.5 mA

Logic and logic reference

input current TJ=25°C 2 10 2 10 µA

Leakage current into hold

capacitor

4

TJ=25°C “hold” mode

3

6 50 6 100 pA

Acquisition time to 0.1%

V

OUT

=10V,

C

H

=1000pF

4 4 µs

CH=0.01µF 20 20 µs

Hold capacitor charging

current

VIN-V

OUT

=2V 5 5 mA

SVRR

Supply voltage rejection

ratio

V

OUT

=0V 80 110 80 110 dB

Differential logic threshold TJ=25°C 0.8 1.4 2.4 0.8 1.4 2.4 V

NOTES:

1. Unless otherwise specified, the following conditions apply: Unit is in “sample” mode. V

S

=±15V, TJ=25°C, -11.5V≤VIN≤11.5V, CH=0.01µF, and

R

L

=2kΩ. Logic reference voltage=0V and logic voltage=2.5V.

2. Hold step is sensitive to stray capacitive coupling between input logic signals and the hold capacitor. 1pF, for instance, will create an

additional 0.5mV step with a 5V logic swing and a 0.01F hold capacitor. Magnitude of the hold step is inversely proportional to hold capacitor

value.

3. Leakage current is measured at a junction temperature of 25°C. The effects of junction temperature rise due to power dissipation or elevated

ambient can be calculated by doubling the 25°C value for each 11°C increase in chip temperature. Leakage is guaranteed over full input

signal range.

4. These parameters guaranteed over a supply voltage range of ±5 to ±18V.

Loading...

Loading...