Philips PLS100A, PLS100F, PLS100FB, PLS100N, PLS101A Datasheet

...

Philips Semiconductors Programmable Logic Devices Product specification

PLS100/PLS101

Programmable logic arrays

(16 × 48 × 8)

49

October 22, 1993 853–0308 11164

DESCRIPTION

The PLS100 (3-State) and PLS101 (Open

Collector) are bipolar, fuse Programmable

Logic Arrays (PLAs). Each device utilizes the

standard AND/OR/Invert architecture to

directly implement custom sum of product

equations.

Each device consists of 16 dedicated inputs

and 8 dedicated outputs. Each output is

capable of being actively controlled by any or

all of the 48 product terms. The True,

Complement, or Don’t Care condition of each

of the 16 inputs and be ANDed together to

comprise one P-term. All 48 P-terms can be

selectively ORed to each output.

The PLS100 and PLS101 are fully TTL

compatible, and chip enable control for

expansion of input variables and output

inhibit. They feature either Open Collector or

3-State outputs for ease of expansion of

product terms and application in

bus-organized systems.

Order codes are listed in the Ordering

Information Table.

FEATURES

•Field-programmable (Ni-Cr link)

•Input variables: 16

•Output functions: 8

•Product terms: 48

•I/O propagation delay: 50ns (max.)

•Power dissipation: 600mW (typ.)

•Input loading: –100µA (max.)

•Chip Enable input

•Output option:

– PLS100: 3-State

– PLS101: Open-Collector

•Output disable function:

– 3-State: Hi-Z

– Open-Collector: High

APPLICATIONS

•CRT display systems

•Code conversion

•Peripheral controllers

•Function generators

•Look-up and decision tables

•Microprogramming

•Address mapping

•Character generators

•Data security encoders

•Fault detectors

•Frequency synthesizers

•16-bit to 8-bit bus interface

•Random logic replacement

PIN CONFIGURATIONS

1

2

3

4

5

6

7

8

9

10

11

12

13

14 15

16

17

18

19

20

21

22

23

24

25

26

27

28

N Package

FE*

I7

I6

I5

I4

I3

I2

I1

I0

F7

F6

F5

F4

GND

V

CC

I8

I9

I10

I11

I12

I14

CE

F0

F1

F2

F3

I15

I13

1234

5

6

7

8

9

10

11

12 13 14 15 16 17

18

19

20

21

22

23

24

25

262728

FE

A Package

F7

I7I6I5

I4

I3

I2

I1

I0

F6

F5 F4

GND

F2

F1 F0

I9I8

V

CC

F3

CE

I10

I11

I12

I14

I15

I13

* Fuse Enable Pin: It is recommended that this pin

be left open or connected to ground during normal

operation.

N = Plastic DIP (600mil-wide)

A = Plastic Leaded Chip Carrier

ORDERING INFORMATION

DESCRIPTION 3-STATE OPEN COLLECTOR DRAWING NUMBER

28-Pin Plastic Dual In-Line 600mil-wide PLS100N PLS101N 0413D

28-Pin Plastic Leaded Chip Carrier PLS100A PLS101A 0401F

Philips Semiconductors Programmable Logic Devices Product specification

PLS100/PLS101

Programmable logic arrays

(16 × 48 × 8)

October 22, 1993

50

LOGIC DIAGRAM

NOTES:

1. All AND gate inputs with a blown link float to a logic “1”.

2. All OR gate inputs with a blown fuse float to logic “0”.

3. Programmable connection.

(LOGIC TERMS–P)

9

8

7

6

5

4

3

2

10

11

12

13

15

16

17

18

I0

I1

I2

I3

I4

I5

I6

I7

F0

F1

F2

F3

F4

F5

F6

F7

47 40 39 32 31 24 23 16

S

0

S

1

S

2

S

3

S

4

S

5

S

6

S

7

X

0

X

1

X

2

X

3

X

4

X

5

X

6

X

7

8 7 0

27

26

25

24

23

22

21

20

I8

I9

I10

I11

I12

I13

I14

I15

19

CE

15

Philips Semiconductors Programmable Logic Devices Product specification

PLS100/PLS101

Programmable logic arrays

(16 × 48 × 8)

October 22, 1993

51

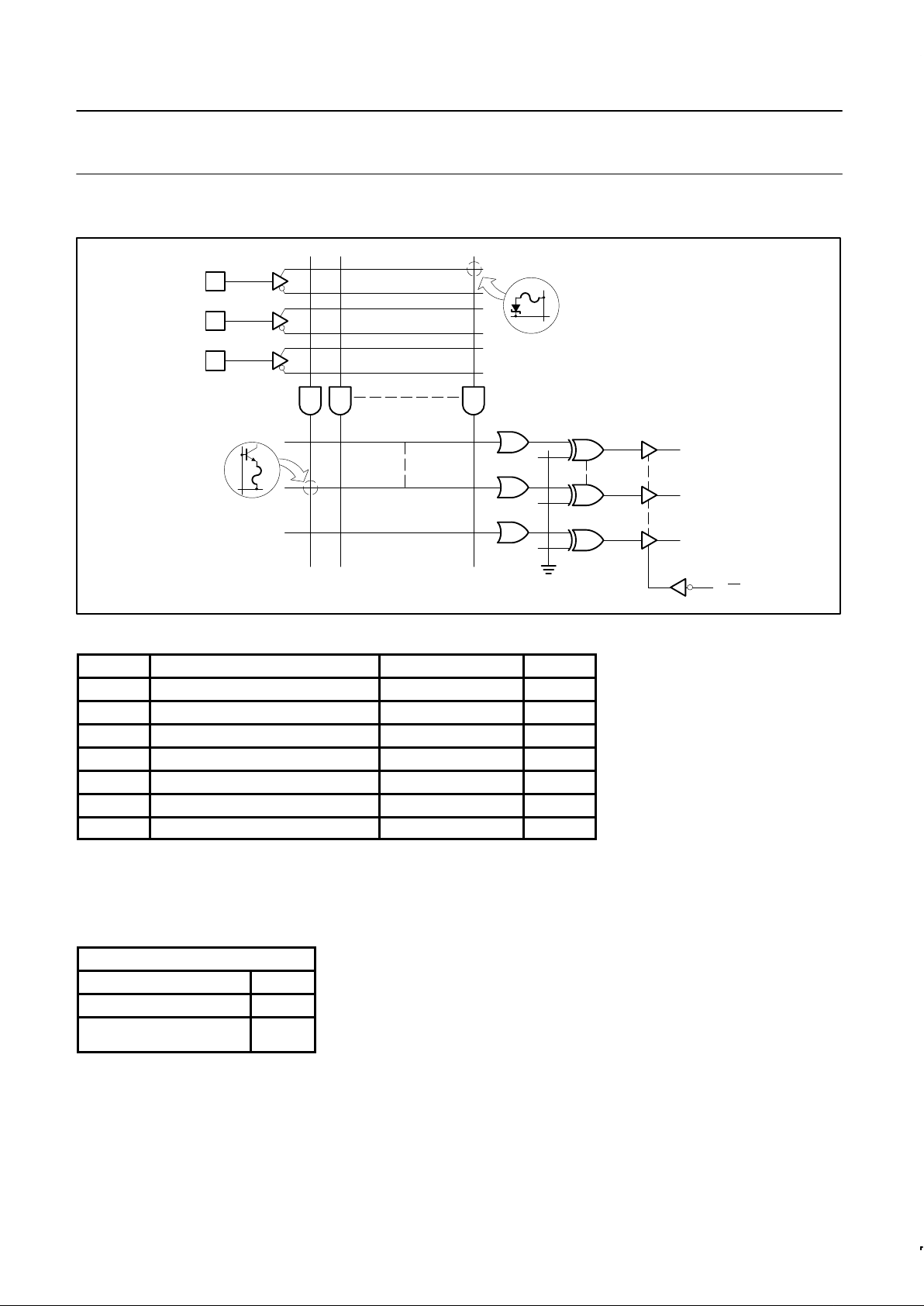

FUNCTIONAL DIAGRAM

I0

I1

I15

TYPICAL CONNECTION

TYPICAL CONNECTION

P

0P1

P

47

S

0

S

6

S

7

F0

F6

F7

CE

ABSOLUTE MAXIMUM RATINGS

1

SYMBOL

PARAMETER RATINGS UNIT

V

CC

Supply voltage +7.0 V

DC

V

IN

Input voltage +5.5 V

DC

V

O

Output voltage +5.5 V

DC

I

IN

Input current ±30 mA

I

OUT

Output current +100 mA

T

amb

Operating temperature range 0 to +75 °C

T

stg

Storage temperature range –65 to +150 °C

NOTE:

1. Stresses above those listed may cause malfunction or permanent damage to the device.

This is a stress rating only. Functional operation at these or any other conditions above

those indicated in the operational and programming specification of the device is not

implied.

THERMAL RATINGS

TEMPERATURE

Maximum junction 150°C

Maximum ambient 75°C

Allowable thermal rise

ambient to junction

75°C

The PLS100 device is also processed to

military requirements for operation over the

military temperature range. For specifications

and ordering information consult the Philips

Semiconductors Military Data Handbook.

Loading...

Loading...