Philips pcf8522e DATASHEETS

INTEGRATED CIRCUITS

DATA SH EET

PCF8522E

256 × 8-bit CMOS EEPROM with

2

I

C-bus interface

Objective specification

Supersedes data of April 1995

File under Integrated Circuits, IC12

1996 Jan 22

Philips Semiconductors Objective specification

256 × 8-bit CMOS EEPROM with I2C-bus

interface

CONTENTS

1 FEATURES

2 APPLICATIONS

3 GENERAL DESCRIPTION

4 ORDERING INFORMATION

5 BLOCK DIAGRAM

6 PINNING

7 FUNCTIONAL DESCRIPTION

7.1 Pinning information

7.1.1 Serial clock (SCL)

7.1.2 Serial data (SDA)

7.1.3 Address pins (A0 to A2)

7.1.4 Write control (WC)

7.2 Endurance and data retention

7.3 Characteristics of the I2C-bus

7.3.1 General description

7.3.2 Input data protocol

7.3.3 START and STOP conditions.

7.4 Device operation

7.4.1 Acknowledge (ACK)

7.4.2 Slave address byte

7.4.3 Read/write bit

7.5 Write operations

7.5.1 Byte write

7.5.2 Page write

7.5.3 Acknowledge polling

7.6 Read operations

7.6.1 Current address byte read

7.6.2 Random address byte read

7.6.3 Sequential read

8 LIMITING VALUES

9 DC CHARACTERISTICS

10 AC CHARACTERISTICS

11 PACKAGE OUTLINE

12 SOLDERING

12.1 Introduction

12.2 Soldering by dipping or by wave

12.3 Repairing soldered joints

13 DEFINITIONS

14 LIFE SUPPORT APPLICATIONS

15 PURCHASE OF PHILIPS I2C COMPONENTS

PCF8522E

1996 Jan 22 2

Philips Semiconductors Objective specification

256 × 8-bit CMOS EEPROM with I2C-bus

interface

1 FEATURES

• Low power CMOS:

– operating current: <2 mA

– standby current: <2 µA

• Hardware write protection:

– Write Control (WC) pin

• Operation supply voltage 2.7 to 5.5 V

• Extended temperature range −40 to +85 °C

• Internally organized as 256 × 8-bit memory bank

• I2C interface (bidirectional data transfer protocol)

• Four-byte page-write mode (minimizes total write time

per byte

• Automatic word address incrementing (sequential

register read)

• Self-timed write cycle

• High reliability:

– endurance: 100000 cycles

– data retention: 10 years

• DIP8 or SO8 package (8 pins).

2 APPLICATIONS

PCF8522E

Typical applications:

• Televisions

• Monitors

• Robotics

• Alarm devices

• Electronic locks

• Measuring devices

• Instrumentation.

3 GENERAL DESCRIPTION

The PCF8522E is a cost effective 2048 bit (256 × 8-bit)

serial Electrical Erasable Programmable Read Only

Memory (EEPROM). The device is fabricated using

advanced CMOS EEPROM technology. This IC operates

from a single supply voltage within the range of

2.7 to 5.5 V.

The PCF8522E is internally organized as a 256 × 8-bit

memory bank. It features an I

software protocol allowing operation on a 2-wire bus.

Up to eight PCF8522Es may be connected to the 2-wire

bus establishing their device addresses using the address

input pins (A0 to A2).

2

C-bus serial interface and

The PCF8522E is ideal for high-volume applications

requiring low power and low density storage.

4 ORDERING INFORMATION

TYPE NUMBER

NAME DESCRIPTION VERSION

PCF8522EP DIP8 plastic dual in-line package; 8 leads (300 mil) SOT97-1

PACKAGE

1996 Jan 22 3

Philips Semiconductors Objective specification

256 × 8-bit CMOS EEPROM with I2C-bus

interface

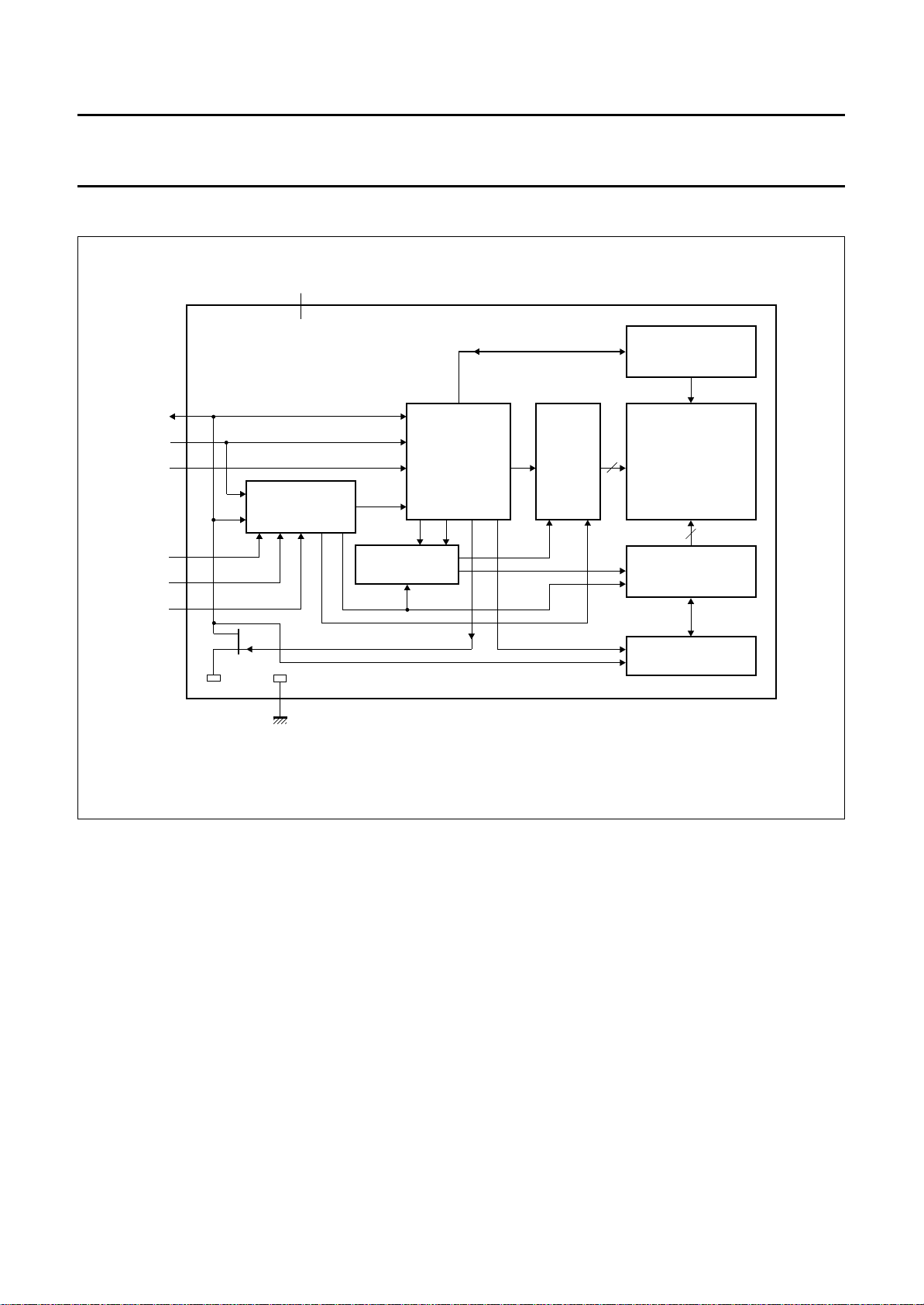

5 BLOCK DIAGRAM

handbook, full pagewidth

SDA

SCL

WC

A2

A1

A0

5

6

7

3

2

1

V

CC

8

PCF8522E

SLAVE ADDRESS

REGISTER AND

COMPARATOR

CONTROL

LOGIC

WORD ADDRESS

COUNTER

X

DECODER

HIGH VOLTAGE

GENERATOR

TIMING AND CONTROL

64

64 X 32

MEMORY

CORE

32

Y

DECODER

PCF8522E

acknowledge clock

data I/O

4

V

SS

DATA REGISTER

MGC070

Fig.1 Block diagram.

1996 Jan 22 4

Philips Semiconductors Objective specification

256 × 8-bit CMOS EEPROM with I2C-bus

interface

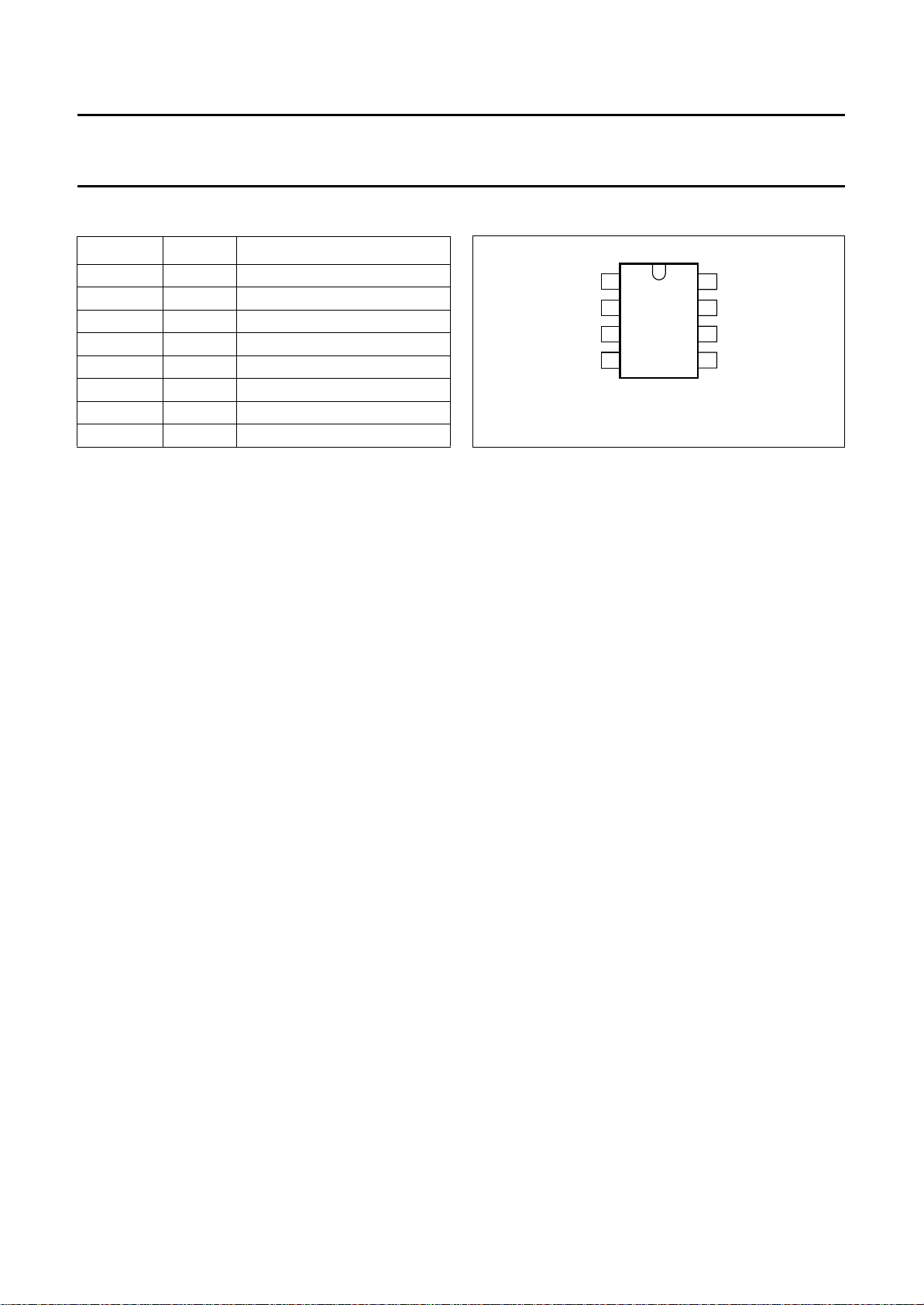

6 PINNING

SYMBOL PIN DESCRIPTION

A0 1 address 1 input

A1 2 address 2 input

A2 3 address 3 input

V

SS

SDA 5 serial data input/output (I/O)

SCL 6 serial clock input

WC 7 write control input

V

CC

7 FUNCTIONAL DESCRIPTION

7.1 Pinning information

7.1.1 S

ERIAL CLOCK (SCL)

The SCL input is used to clock data into and out of the

device. In the write mode, data must remain stable when

SCL is HIGH. In the read mode, data is clocked out on the

falling edge of SCL.

4 ground

8 supply voltage

PCF8522E

handbook, halfpage

A0

1

2

A1

A2

V

SS

PCF8522E

3

4

MGC071

Fig.2 Pin configuration.

7.3 Characteristics of the I

7.3.1 G

ENERAL DESCRIPTION

2

The I2C-bus is designed for two-way, 2-line serial

communication for different integrated circuits.

The 2-lines are:

1. Serial Data line (SDA).

2. Serial Clock Line (SCL).

8

7

6

5

C-bus

V

CC

WC

SCL

SDA

7.1.2 S

ERIAL DATA (SDA)

The SDA pin is a bidirectional pin used to transfer data into

and out of the device. Data may only change when SCL is

LOW, except START and STOP conditions. It is an

open-drain output, and may be wire-ORed with any

number of open-drain or open-collector outputs.

7.1.3 A

DDRESS PINS (A0 TO A2)

The address inputs are used to set the 3-bit device

address of the PCF8522E which will identify it on the

I2C-bus. The address pins may be tied HIGH or LOW, or

they may be actively driven. These inputs allow up to eight

PCF8522E devices to be distinguished on the I2C-bus.

7.1.4 W

RITE CONTROL (WC)

The write control input pin is used to disable the write

circuitry to the memory. If WC = HIGH the write function is

disabled, to protect previously written data. If WC = LOW

the write function is enabled.

7.2 Endurance and data retention

The PCF8522E is designed for applications requiring up to

100000 write cycles and unlimited number of read cycles.

It provides 10 years of secure data retention, with or

without supply voltage applied, after the execution of

100000 write cycles.

The SDA line must be connected to the positive supply

voltage by a pull-up resistor, located somewhere on the

I2C-bus (see Fig.3)). Data transfer between devices may

be initiated with a START condition only when SCL and

SDA are HIGH (I2C-bus is not busy).

7.3.2 I

NPUT DATA PROTOCOL

One data bit is transferred during each clock pulse. The

data on the SDA line must remain stable while the clock is

HIGH, because changes on the data line, while SCL is

HIGH will be interpreted as a ‘START’ or ‘STOP’ condition

(see Fig.4).

7.3.3 START

AND STOP CONDITIONS.

When both data (SDA) and clock (SCL) lines are HIGH,

the I2C-bus is referred to as ‘not busy’. A HIGH-to-LOW

transition of the data line, while the clock is HIGH is

defined as the ‘START’ condition. A LOW-to-HIGH

transition of the data line, while the clock is HIGH, is

defined as the ‘STOP’ condition (see Fig.5).

1996 Jan 22 5

Philips Semiconductors Objective specification

256 × 8-bit CMOS EEPROM with I2C-bus

interface

7.4 Device operation

The device supports the I2C-bus bidirectional data

transmission protocol. The protocol defines any device

that sends data onto the I2C-bus as a ‘transmitter’ and the

receiving device as the ‘receiver’. The device controlling

the data transmission is the ‘master’ and the controlled

device is the ‘slave’. In all events the PCF8522E will be a

‘slave’ device because it never initiates any data transfers.

Up to eight PCF8522Es can be connected to the I2C-bus

and can be selected by the A0 to A2 device addresses.

A0 to A2 must be connected to either V

may be actively driven. A0 to A2 define the address of the

device. Other devices may be connected to the I2C-bus

but each device needs its own device identification code.

7.4.1 A

Acknowledge is a software convention used to indicate

successful data transfers. The transmitting device, either

the master or the slave, will release the I2C-bus after

transmitting 8-bits. During the ninth clock cycle, the

receiver will pull the SDA line LOW to acknowledge that it

has received 8-bits of data (see Fig.6).

CKNOWLEDGE (ACK)

, VSS or they

CC

PCF8522E

If an acknowledge is not detected, the PCF8522E

terminates further data transmissions and awaits a STOP

condition before returning to the standby power mode.

7.4.2 S

Following a START condition, the master must output the

address to be accessed. The most significant 4 bits of the

slave address are the ‘device type identifier’. For a

PCF8522E the address identifier is 1010 (see Table 1).

The next 3 bits are device address, addressing a particular

device. Using this addressing scheme, a system may

cascade up to eight PCF8522E devices on the I

The device address is defined by the state of the A0 to A2

input pins.

7.4.3 R

The last bit of the slave address defines the operation to

be performed. When R/W = 1, a read operation is

selected. If R/W = 0, a write operation is selected

(see Table 1).

Table 1 Slave address byte

LAVE ADDRESS BYTE

EAD/WRITE BIT

2

C-bus.

The PCF8522E will respond with an acknowledge after

recognition of a START condition and its slave address

byte. If both the device and a write operation have been

selected, the PCF8522E will respond with an acknowledge

after the receipt of each subsequent 8-bit word.

In the read mode, the PCF8522E transmits 8-bits of data,

then releases the SDA line, and monitors the line for an

acknowledge signal. If an acknowledge is detected, and

no STOP condition is generated by the master, the

PCF8522E will continue to transmit data.

DEVICE TYPE

IDENTIFIER

1 0 1 0 A2 A1 A0 note 1

Note

1. This is the read/write bit:

a) When R/

b) When R/W = 0, a write operation is selected.

W = 1, a read operation is selected.

DEVICE

ADDRESS

R/

W

1996 Jan 22 6

Loading...

Loading...