Philips p8xc591 DATASHEETS

INTEGRATED CIRCUITS

DATA SH EET

P8xC591

Single-chip 8-bit microcontroller

with CAN controller

Preliminary Specification

File under Integrated Circuits, IC28

2000 Jul 26

Philips Semiconductors Preliminary Specification

Single-chip 8-bit microcontroller with CAN controller P8xC591

CONTENTS

1 FEATURES

1.1 80C51 Related Features of the 8xC591

1.2 CAN Related Features of the 8xC591

2 GENERAL DESCRIPTION

3 ORDERING INFORMATION

4 BLOCK DIAGRAM

5 FUNCTIONAL DIAGRAM

6 PINNING INFORMATION

6.1 Pinning diagram

6.2 Pin description

7 MEMORY ORGANIZATION

7.1 Program Memory

7.2 Addressing

7.3 Expanded Data RAM addressing

7.4 Dual DPTR

8 I/O FACILITIES

9 OSCILLATOR CHARACTERISTICS

10 RESET

11 LOW POWER MODES

11.1 Stop Clock Mode

11.2 Idle Mode

11.3 Power-down Mode

12 CAN, CONTROLLER AREA NETWORK

12.1 Features of the PeliCAN controller

12.2 PeliCAN structure

12.3 Communication between PeliCAN controller

and CPU

12.4 Register and Message Buffer description

12.5 CAN Registers

13 SERIAL I/O

14 SIO0 STANDARDSERIAL INTERFACE UART

14.1 Multiprocessor Communications

14.2 Serial Port Control Register

14.3 Baud Rate Generation

14.4 More about UART Modes

14.5 Enhanced UART

2

15 SIO1, I

15.1 Modes of Operation

15.2 SIO1 Implementation and Operation

15.3 Software Examples of SIO1 Service Routines

16 TIMER 2

16.1 Features of Timer 2

C SERIAL IO

17 WATCHDOG TIMER (T3)

18 PULSE WIDTH MODULATED OUTPUTS

18.1 Prescaler Frequency Control Register (PWMP)

18.2 Pulse Width Register 0 (PWM0)

18.3 Pulse Width Register 1 (PWM1)

19 PORT 1 OPERATION

20 ANALOG-TO-DIGITAL CONVERTER (ADC)

20.1 ADC features

20.2 ADC functional description

20.3 10-Bit Analog-to-Digital Conversion

20.4 10-Bit ADC Resolution and Analog Supply

20.5 Power Reduction Modes

21 INTERRUPTS

21.1 Interrupt Enable Registers

21.2 Interrupt Enable and Priority Registers

21.3 Interrupt priority

21.4 Interrupt Vectors

22 INSTRUCTION SET

22.1 Addressing Modes

23 LIMITING VALUES

24 DC CHARACTERISTICS

25 AC CHARACTERISTICS

25.1 Timing symbol definitions

26 EPROM CHARACTERISTICS

26.1 Program verification

26.2 Security bits

27 PACKAGE OUTLINES

28 SOLDERING

28.1 Plastic leaded-chip carriers/quad flat-packs

29 DEFINITIONS

30 LIFE SUPPORT APPLICATIONS

2000 Jul 26 2

Philips Semiconductors Preliminary Specification

Single-chip 8-bit microcontroller with CAN controller P8xC591

1 FEATURES

1.1 80C51 Related Features of the 8xC591

• Full static 80C51 Central Processing Unit available as

OTP, ROM and ROMless

• 16 Kbytes internal Program Memory expandable

externally to 64 Kbytes

• 512 bytes on-chip Data RAM expandable externally to

64 Kbytes

• Three 16-bit timers/counters T0, T1 (standard 80C51)

and additional T2 (capture & compare)

• 10-bit ADC with 6 multiplexed analog inputs with fast

8-bit ADC option

• Two 8-bit resolution, Pulse Width Modulated outputs

• 32 I/O port pins in the standard 80C51 pinout

2

C-bus serial I/O port with byte oriented master and

• I

slave functions

• On-chip Watchdog Timer T3

• Extended temperature range: −40 to +85°C

• Accelerated (prescaler 1:1) instruction cycle time

500 ns @ 12 MHz

• Operation voltage range: 5 V ± 5%

• Security bits:

– ROM version has 2 bits

– OTP/EPROM version has 3 bits

• 32 bytes Encryption array

• 4 level priority interrupt, 15 interrupt sources

• Full-duplex enhanced UART with programmable

Baudrate Generator

• Power Control Modes:

– Clock can be stopped and resumed

– Idle Mode

– Power-down Mode

• ADC active in Idle Mode

• Second DPTR register

• ALE inhibit for EMI reduction

• Programmable I/O port pins (pseudo bi-directional,

push-pull, high impedance, open drain)

• Wake-up from Power-down by external interrupts

• Software reset bit (AUXR1.5)

• Low active reset pin

• Power-on detect reset

• Once mode

1.2 CAN Related Features of the 8xC591

• CAN 2.0B active controller, supporting 11-bit Standard

and 29-bit Extended indentifiers

• 1 Mbit/s CAN bus speed with 8 MHz clock achievable

• 64 byte receive FIFO (can capture sequential Data

Frames from the

Transport Layer of higher protocols such as DeviceNet,

CANopen and OSEK)

• 13 byte transmit buffer

• EnhancedPeliCANcore(fromthe SJA1000 stand-alone

CAN2.0B controller)

1.2.1 P

• Four independently configurable Screeners

(Acceptance Filters)

• Each Screener has two 32-bit specifies:

– 32-bit Match and

– 32-bit Mask

• 32-bits of Mask

addressing per

• Higher layer protocols especially supported in Standard

CAN format with:

– Up to four, 11-bit ID Screeners that also Screen the

– i.e.,Data Frames are Screenedbythe CAN ID andby

• Up to eight, 11-bit ID Screeners half of which

Screen the

• All Screeners are changeable “on the fly”

• Listen Only Mode, Self Test Mode

• Error Code Capture, Arbitration Lost Capture, readable

Error Counters

ELICAN FEATURES

two (2) Data Bytes

Data Byte content

same

per Screener

Screener

first

Data Byte

source as required by the

allows

unique

Group

also

2000 Jul 26 3

Philips Semiconductors Preliminary Specification

Single-chip 8-bit microcontroller with CAN controller P8xC591

2 GENERAL DESCRIPTION

The P8xC591 is a single-chip 8-bit-high-performance

microcontroller, with on-chip CAN-controller, derived from

the 80C51 microcontroller family.

Ituses thepowerful 80C51 instructionset and includesthe

successful PeliCAN functionality of the SJA1000 CAN

controller from Philips Semiconductors.

The fully static core provides extended power save

provisions as the oscillator can be stopped and easily

restarted without loss of data. The improved internal clock

prescalerof 1:1achieves a 500 nsinstruction cycle timeat

12 MHz external clock rate.

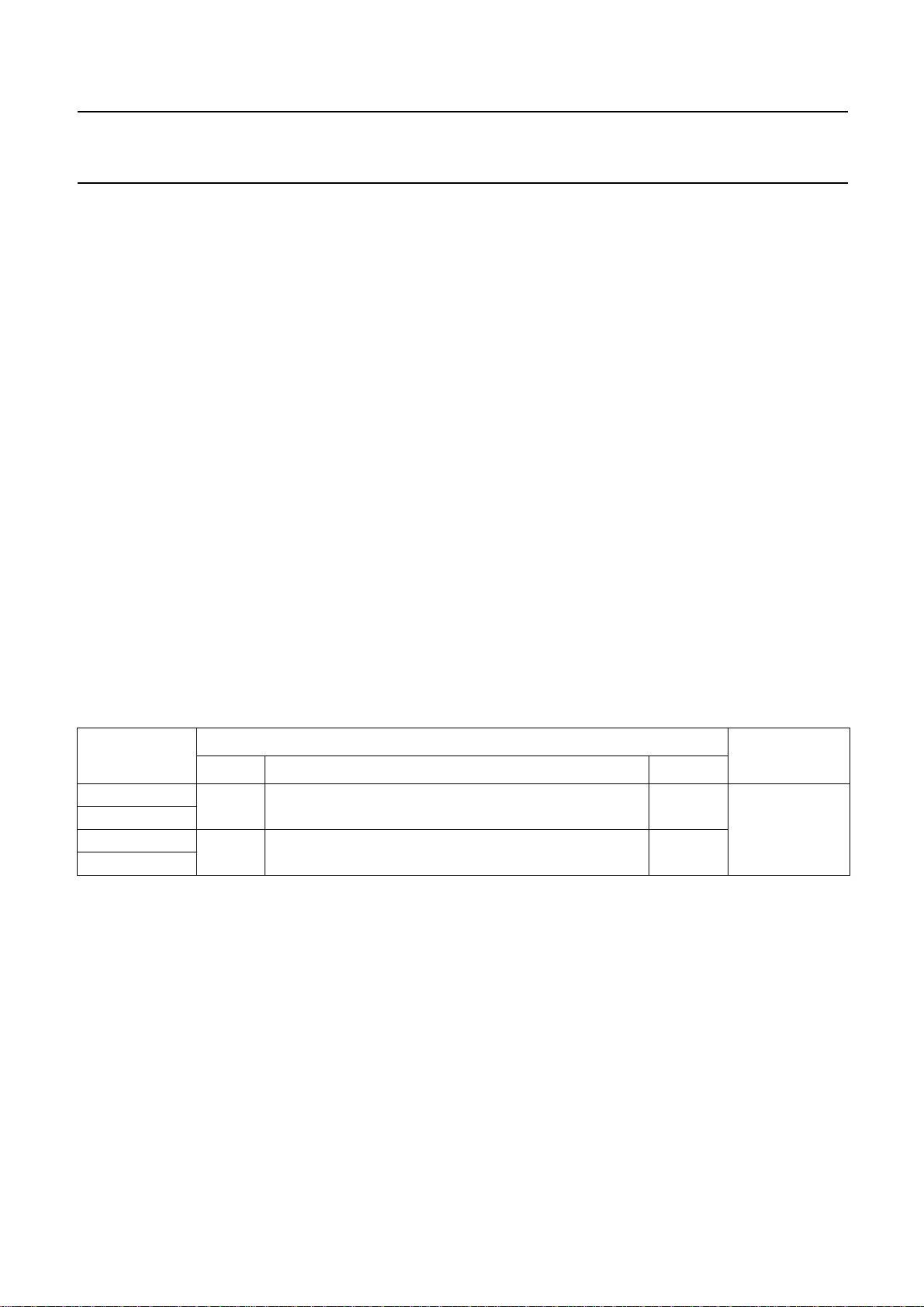

Figure 1 shows a Block Diagram of the P8xC591. The

microcontroller is manufactured in an advanced CMOS

process, and is designed for use in automotive and

general industrial applications. In addition to the 80C51

standard features, the device provides a number of

dedicated hardware functions for these applications.

Two versions of the P8xC591 will be offered:

• P83C591 (with ROM)

• P87C591 (with OTP)

The temperature range includes (max. f

• -40 to +85 °C version, for general applications

The P8xC591 combines the functions of the P87C554

(microcontroller) and the SJA1000 (stand-alone

CAN-controller) with the following enhanced features:

• Enhanced CAN receive interrupt (level sensitive)

• Extended acceptance filter

• Acceptance filter changeable “on the fly”.

The main differences between P8xC591 and P87C554

are:

• CAN-controller on chip

• 6-input ADC

• Low active Reset

• 44 leads.

= 12 MHz):

CLK

Hereafter these versions will be referred to as P8xC591.

3 ORDERING INFORMATION

TYPE NUMBER

P83C591VFA

P87C591VFA

P83C591VFB

P87C591VFB

NAME DESCRIPTION VERSION

PLCC44 plastic leaded chip carrier; 44 leads SOT187-2

QFP44

plastic quad flat package; 44 leads (lead length 1.3 mm);

body 10 × 10 × 1.75 mm

PACKAGE

TEMPERATURE

RANGE (°C)

−40 to +85

SOT307-2

2000 Jul 26 4

Philips Semiconductors Preliminary Specification

Single-chip 8-bit microcontroller with CAN controller P8xC591

4 BLOCK DIAGRAM

handbook, full pagewidth

A0 to A7

V

V

XTAL1

XTAL2

DD

SS

INT1INT0

80C51 CONFIGURABLE CORE

CPU

CORE

OSCILLATOR

TIMER/EVENT

T1T0

TWO 16-BIT

COUNTERS

(T0/T1)

WATCHDOG

TIMER (T3)

PSEN

ALE

16 KBYTES

PROGRAM

PARALLEL

I/O PORTS

WR

MEMORY

RD

EA PWM1

ref+AVSS

512 BYTES

ADC

DATA

MEMORY

PWM0AN0 to 5AV

P8xC591

16-BIT TIMER/EVENT

COUNTER WITH CAPTURE

RT2

P3P2P1P0RST

T2

(T2)

CT0x/INTx

CMSR0 to 5

CMT0 to 1

PWM

2

I

C SERIAL

INTERFACE

RXD TXD

UART

CPU

INTERFACE

(SFRs)

CAN 2.0 B

INTERFACE

TXDCSCLSDA

RXDC

MHI001

Fig.1 Block diagram P8xC591.

2000 Jul 26 5

Philips Semiconductors Preliminary Specification

Single-chip 8-bit microcontroller with CAN controller P8xC591

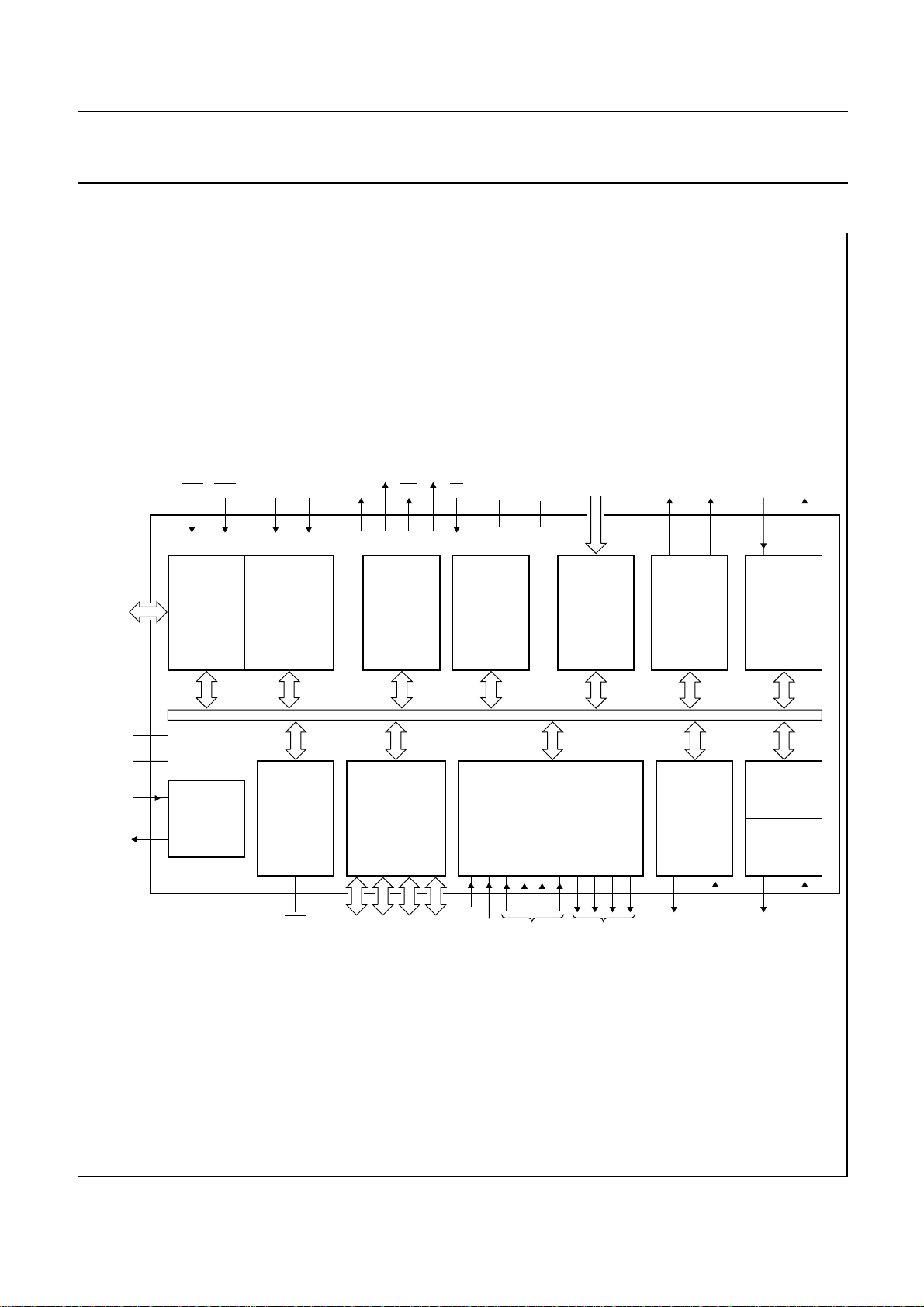

5 FUNCTIONAL DIAGRAM

handbook, full pagewidth

CSMR0

CSMR1

CSMR2

CSMR3

T2

RT2

RXD

TXD

INT0

INT1

T0

T1

WR

RD

PORT 3

RST

PSEN

ALE

AV

ref+

AV

SS

PWM0

PWM1

XTAL1

XTAL2

EA

0

1

2

3

4

5

6

7

V

DD

P8xC591

(44-PIN)

V

SS

MHI002

alternative functions

0

1

2

3

PORT 0

4

5

6

7

0

1

2

3

PORT 1

4

5

6

7

0

1

2

3

PORT 2 address bus

4

5

6

7

AD0

AD1

AD2

AD3

AD4

AD5

AD6

AD7

RXDC

TXDC

ADC0

ADC1

ADC2

ADC3

ADC4

ADC5

and data bus

low order address

CAN

CT0I/INT2

CT1I/INT3

CT2I/INT4

CT3I/INT5

SCL

I2C

SDA

Fig.2 Functional diagram.

2000 Jul 26 6

Philips Semiconductors Preliminary Specification

Single-chip 8-bit microcontroller with CAN controller P8xC591

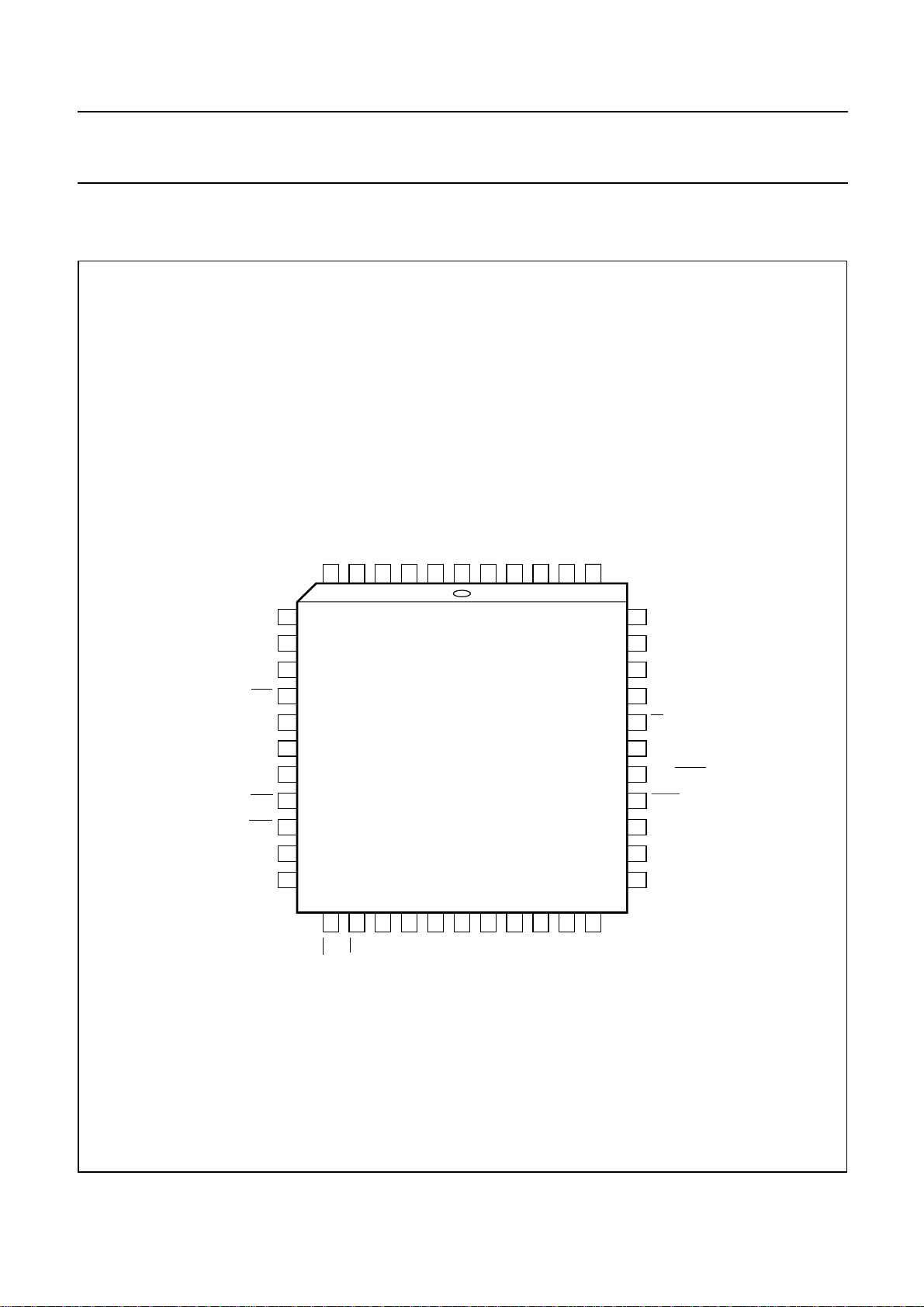

6 PINNING INFORMATION

6.1 Pinning diagram

handbook, full pagewidth

CT3I/INT5/ADC3/P1.5

SCL/ADC4/P1.6

SDA/ADC5/P1.7

RST

T2/P3.0/RXD

PWM0

RT2/P3.1/TXD

CMSR0/P3.2/INT0

CMSR1/P3.3/INT1

CMSR2/P3.4/T0

CMSR3/P3.5/T1

P1.4/ADC2/INT4/CT2I

P1.3/ADC1/INT3/CT1I

P1.2/ADC0/INT2/CT0I

P1.1/TXDC

P1.0/RXDC

6

5

4

3

2

7

8

9

10

11

21

XTAL1

P8xC591

22

SS

V

12

13

14

15

16

17

18

19

20

XTAL2

P3.7/RD

P3.6/WR

AVSSAV

1

44

23

24

DD

V

P2.0/A8

ref+

P0.0/AD0

P0.1/AD1

43

42

25

26

P2.1/A9

P2.2/A10

P0.2/AD2

P0.3/AD3

41

40

27

28

P2.3/A11

P2.4/A12

39

38

37

36

35

34

33

32

31

30

29

MHI003

P0.4/AD4

P0.5/AD5

P0.6/AD6

P0.7/AD7

EA/V

PP

PWM1

ALE/PROG

PSEN

P2.7/A15

P2.6/A14

P2.5/A13

Fig.3 Pinning Diagram for 44-lead LCC Package.

2000 Jul 26 7

Philips Semiconductors Preliminary Specification

Single-chip 8-bit microcontroller with CAN controller P8xC591

handbook, full pagewidth

P1.5/ADC3/INT5/CT3I

P1.6/ADC4/SCL

P1.7/ADC5/SDA

RST

P3.0/T2/RXD

PWM0

RT2/P3.1/TXD

CMSR0/P3.2/INT0

CMSR1/P3.3/INT1

CMSR2/P3.4/T0

CMSR3/P3.5/T1

P1.4/ADC2/INT4/CT2I

P1.3/ADC1/INT3/CT1I

P1.2/ADC0/INT2/CT0I

P1.1/TXDC

P1.0/RXDC

44

43

42

41

40

1

2

3

4

5

15

XTAL1

P8xC591

16

SS

V

6

7

8

9

10

11

12

13

14

XTAL2

P3.7/RD

P3.6/WR

AVSSAV

39

38

17

18

DD

V

P2.0/A8

ref+

P0.0/AD0

P0.1/AD1

37

36

19

20

P2.1/A9

P2.2/A10

P0.2/AD2

P0.3/AD3

35

34

21

22

P2.3/A11

P2.4/A12

33

32

31

30

29

28

27

26

25

24

23

MHI004

P0.4/AD4

P0.5/AD5

P0.6/AD6

P0.7/AD7

EA/V

PP

PWM1

ALE/PROG

PSEN

P2.7/A15

P2.6/A14

P2.5/A13

Fig.4 Pinning Diagram for 44-lead Plastic Quad Flat Package (QFP).

2000 Jul 26 8

Philips Semiconductors Preliminary Specification

Single-chip 8-bit microcontroller with CAN controller P8xC591

6.2 Pin description Table 1 Pin description for QFP44/PLCC44, see Note 1.

SYMBOL

DESCRIPTION

QFP44 PLCC44

RST 4 10 Reset: A Input to reset the P8xC591. It also provides a reset pulse as output

when Timer T3 overflows.

P3.0to P3.7 Port 3 (P3.0 to P3.7): 8-bit programmable I/O port lines; Port 3 can

sink/source 4 LSTTL inputs.

Port 3 pins serve alternate functions as follows:

P3.0/RXD 5 11 RXD: Serial input port for UART;

T2: T2 event input

P3.1/TXD 7 13 TXD: Serial output port for UART;

RT2: T2 timer reset signal. Rising edge triggered.

PIN

INT0/CMSR0 8 14 INT0: External interrupt input 0;

P3.2/

CMSR0: Compare and Set/Reset output for Timer T2.

INT1/

P3.3/

CMSR1

915INT1: External interrupt input 1;

CMSR1: Compare and Set/Reset output for Timer T2.

P3.4/T0/CMSR2 10 16 T0: Timer 0 external interrupt input;

CMSR2: Compare and Set/Reset output for Timer T2.

P3.5/T1/CMSR3 11 17 T1: Timer 1 external interrupt input;

CMSR3: Compare and Set/Reset output for Timer T2.

WR 12 18 WR: External Data Memory Write strobe;

P3.6/

RD 13 19 RD: External Data Memory Read strobe.

P3.7/

During reset, Port 3 will be asynchronously driven resistive HIGH.

Port 3 has four modes selected on a per bit basis by writing to the P3M1 and

P3M2 registers as follows:

P3M1.x

P3M2.x

0

0

1

1

Mode Description

0

Pseudo-bidirectional (standard c51 configuration default)

1

Push-Pull

0

High impedance

1

Open drain

XTAL2 14 20 Crystal pin 2: output of the inverting amplifier that forms the oscillator. Left

open-circuit when an external oscillator clock is used.

XTAL1 15 21 Crystal pin 1: input to the inverting amplifier that forms the oscillator, and

input to the internal clock generator. Receives the external oscillator clock

signal when an external oscillator is used.

V

SS

V

DD

16 22 Ground; circuit ground potential.

17 23 Power supply; power supply pin during normal operation and power

reduction modes.

2000 Jul 26 9

Philips Semiconductors Preliminary Specification

Single-chip 8-bit microcontroller with CAN controller P8xC591

SYMBOL

DESCRIPTION

QFP44 PLCC44

PIN

P2.0/A08 to

P2.7/A15

18 to 25 24 to 31 Port 2 (P2.0 to P2.7): 8-bit programmable I/O port lines;

A08 to A15: High-order address byte for external memory.

Alternate function: High-order address byte for external memory (A08-A15).

Port 2 is also used to input the upper order address during EPROM

programming and verification. A8 is on P2.0, A9 on P2.1, through A12 on

P2.4.

During reset, Port 2 will be asynchronously driven HIGH.

Port 2 has four output modes selected on a per bit basis by writing to the

P2M1 and P2M2 registers as follows:

P2M1.x

P2M2.x

0

0

1

1

Mode Description

0

Pseudo-bidirectional (standard c51 configuration default)

1

Push-Pull

0

High impedance

1

Open drain

PSEN 26 32 Program Store Enable output: read strobe to the external Program Memory

via Ports 0 and 2. Is activated twice each machine cycle during fetches from

external Program Memory. When executing out of external Program Memory

two activations of

Memory.

PSEN is not activated (remains HIGH) during no fetches from

external Program Memory.

PSEN are skipped during each access to external Data

PSEN can sink/source 8 LSTTL inputs. It can

drive CMOS inputs without external pull-ups.

PROG 27 33 Address Latch Enable output. Latches the low byte of the address during

ALE/

access of external memory in normal operation. It is activated every six

oscillator periods except during an external Data Memory access. ALE can

sink/source 8 LSTTL inputs. It can drive CMOS inputs without an external

pull-up. To prohibit the toggling of ALE pin (RFI noise reduction) the bit A0

(SFR: AUXR.0) must be set by software; see Table 4.

PROG: the programming pulse input; alternative function for the P87C591.

EA/V

PP

29 35 External Access input. If, during reset, EA is held at a TTL level HIGH the

CPU executes out of the internal Program Memory.If, during reset,

EA is held

at a TTL level LOW the CPU executes out of external Program Memory via

Port 0 and Port 2.

EA is not allowed to float. EA is latched during reset and

don’t care after reset.

: the programming supply voltage; alternative function for the P87C591.

V

PP

P0.0/AD0 to

P0.7/AD7

30 to 37 36 to 43 Port 0: 8-bit open-drain bidirectional I/O port.

During reset, Port 0 is HIGH-Impedance (Tri-State).

AD7 to AD0: Multiplexed Low-order address and Data bus for external

memory. During these accesses internal pull-ups are activated. Port 0 can

sink/source up to 8 LSTTL inputs.

AV

AV

ref+

SS

38 44 Analog to Digital Conversion Reference Resistor: High-end.

39 1 Analog ground.

2000 Jul 26 10

Philips Semiconductors Preliminary Specification

Single-chip 8-bit microcontroller with CAN controller P8xC591

SYMBOL

DESCRIPTION

QFP44 PLCC44

PIN

P1.0 to P1.4

P1.5 to P1.7

40 to 44

1to3

2to6

7to9

Port 1: 8-bit I/O port with a user configurable output type. The operation of

Port 1 pins asinputs or outputs depends upon the port configuration selected.

Each port pin is configured independently.

Port 1 also provides various special functions as described below:

P1.0 40 2 RXDC: CAN Receiver input line.

P1.1 41 3 TXDC: CAN Transmit output line.

During reset, Port P1.0 and P1.1 will be asynchronously driven resistive

HIGH, P1.2 to P1.7 is High-Impedance (Tri-state).

P1.2 to P1.4 42 to 44 4 to 6 CT0I/INT2 / CT1I/INT3 / CT2I/INT4: T2 Capture timer inputs or External

Interrupt inputs.

ADC0 to ADC2: Alternate function: Input channels to ADC.

P1.5 to P1.7 1 to 3 7 to 9

ADC3 to ADC5: Input channels to ADC:

P1.5 1 7 CT3I/INT5: T2 Capture timer input or External Interrupt inputs.

P1.6 2 8 SCL: Serial port clock line I

2

implemented at I

C.

P1.7 3 9 SDA: Serial data clock line I

2

implemented at I

C.

2

C. Push-pull or pseudo bidrectional modes is not

2

C.Push-pull or pseudo bidrectional modes is not

Port 1 has four modes selected on a per bit basis by writing to the P1M1 and

P1M2 registers as follows:

P1M1.x

P1M2.x

0

0

1

1

Mode Description

0

Pseudo-bidirectional (standard c51 configuration default

(2)

1

0

1

)

Push-Pull

(2)

High impedance Open drain

Port 1 is also used to input the lower order address byte during EPROM

programming and verification. A0 is on P1.0, etc.

PWM0 6 12 Pulse Width Modulation: Output 0.

PWM1 28 34 Pulse Width Modulation: Output 1.

Notes

1. Toavoid “latch-up” effectas power-on, the voltageon any pinatany time mustnot be higher orlower than V

−0.5 V.

or V

SS

2. Not implemented for P1.6 and P1.7.

2000 Jul 26 11

DD

+0.5 V

Philips Semiconductors Preliminary Specification

Single-chip 8-bit microcontroller with CAN controller P8xC591

7 MEMORY ORGANIZATION

The Central Processing Unit (CPU) manipulates operands in three memory spaces as follows (see Fig.5):

• 16 Kbytes internal resp. 64 Kbytes external Program Memory

• 512 bytes internal Data Memory Main-and Auxiliary RAM

• up to 64 Kbytes external Data Memory (with 256 bytes residing in the internal Auxiliary RAM).

handbook, full pagewidth

16384

16383

0

64K

EXTERNAL

INTERNAL

(EA = 1)

PROGRAM MEMORY

EXTERNAL

(EA = 0)

255

INDIRECT ONLY

127

DIRECT AND

0

OVERLAPPED SPACE

INDIRECT

MAIN RAM

INTERNAL DATA MEMORY

SFRs

AUXILIARY

RAM

(EXTRAM = 0)

MHI005

64K

256

EXTERNAL

DATA MEMORY

Fig.5 Memory map and address space with EXTRAM = 0.

2000 Jul 26 12

Philips Semiconductors Preliminary Specification

Single-chip 8-bit microcontroller with CAN controller P8xC591

7.1 Program Memory

The P8xC591 contains 16 Kbytes of on-chip Program

Memorywhich canbe extended to64 Kbytes with external

memories. When

fetches instructions from internal ROMunless theaddress

exceeds 3FFFh. Locations 4000h to FFFFh are fetched

from external Program Memory. When the

LOW, all instruction fetches are from external memory.

EA pin is latched during reset and is “don’t care” after

The

reset.

Both, for the ROM and EPROM version of the P8xC591,

precautions are implemented to protectthe deviceagainst

illegal Program Memory code reading.

7.2 Addressing

The P8xC591 has five methods for addressing the

Program and Data memory:

• Register

• Direct

• Register-Indirect

• Immediate

• Base-Register plus Index-Register-Indirect.

For more details about Addressing modes please refer to

Section 22.1 “Addressing Modes”.

7.3 Expanded Data RAM addressing

The P8xC591 has internal data memory that is mapped

into four separate segments: the lower 128 bytes of RAM,

upper 128 bytes of RAM, 128 bytes Special Function

Register (SFR), and 256 bytes AuxiliaryRAM (AUX-RAM)

as shown in Figure 5.

The four segments are:

1. The Lower 128 bytes of RAM (addresses 00H to 7FH)

are directly and indirectly addressable (see Fig.6).

2. The Upper 128 bytes of RAM(addresses 80H to FFH)

are indirectly addressable.

3. The Special Function Registers, SFRs, (addresses

80H to FFH) are directly addressable only. All these

SFRs are described in Table 4.

4. The 256-bytes AUX-RAM (00H - FFH) are indirectly

accessed by move external instruction, MOVX, and

within the EXTRAM bit cleared, see Table 3.

The Lower 128 bytes can be accessed by either direct or

indirect addressing. The Upper 128 bytes can be

accessed by indirect addressing only. The Upper 128

bytes occupy the same address space as the SFR. That

EA pin is held HIGH, the P8xC591

EA pin is held

means they have the same address, but are physically

separate from SFR space.

When an instruction accesses an internal location above

address 7FH, the CPU knowswhether theaccess isto the

upper 128 bytes of data RAM or to SFR space by the

addressing mode used in the instruction. Instructions that

use direct addressing access SFR space.

For example:

MOV 0A0H,#data

accesses the SFR at location 0A0H (which is P2).

Instructions that use indirect addressingaccess theUpper

128 bytes of data RAM.

For example:

MOV @ R0,#data

where R0 contains 0A0H, accesses the data byte at

address 0A0H, rather than P2 (whose address is 0A0H).

The AUX-RAM can be accessed by indirect addressing,

with EXTRAM bit cleared and MOVX instructions. This

part of memory is physically located on-chip, logically

occupies the first 256-bytes of external data memory.

With EXTRAM = 0, the AUX-RAM is indirectly addressed,

using the MOVX instruction in combination with any of the

registers R0, R1 of the selected bank or DPTR. An access

to AUX-RAM will not affectports P0,P3.6 (WR#)and P3.7

(RD#). P2 SFR is output during external addressing. For

example, with EXTRAM = 0,

MOV @ R0,#data

where R0 contains 0A0h, access the AUX-RAM at

address 0A0H rather than external memory. An access to

external data memory locations higher than FFH (i.e.,

0100H to FFFFH) willbe performed with the MOVX DPTR

instructions in the same way as in the standard 80C51, so

with P0 and P2 as data/address bus, and P3.6 and P3.7

as write and read timing signals. Refer to Table 4.

With EXTRAM = 1, MOVX @ Ri and MOVX @ DPTR will

be similar to the standard 80C51. MOVX @ Ri will provide

an 8-bit address multiplexed with data on Port 0 and any

output port pins can be used to output higher order

address bits. This is to provide the external paging

capability. MOVX @ DPTR will generate a 16-bit address.

Port 2 outputs the high-order eight address bits (the

contents of DPH) while Port 0 multiplexes the low-order

eightaddressbits (DPL) with data.MOVX@Ri and MOVX

@ DPTR will generate either read or write signals on P3.6

(#WR) and P3.7 (#RD).

The stack pointer (SP) may be located anywhere in the

256 bytes RAM (lower and upper RAM) internal data

memory. The stack cannot be located in the AUX-RAM.

2000 Jul 26 13

Philips Semiconductors Preliminary Specification

Single-chip 8-bit microcontroller with CAN controller P8xC591

Table 2 AUX-RAM Page Register (address 8EH)

76543210

- - - - - LVADC EXTRAM AO

Table 3 Description of AUX-RAM bits

BIT SYMBOL FUNCTION

7 to 3 − Reserved for future use; see Note 1.

2 LVADC Enable A/D low voltage operation.

LVADC

0

1

1 EXTRAM Internal/External RAM (00H - FFH) access using MOVX @ RI / @ DPTR

EXTRAM

0

1

0 AO Disable/Enable ALE.

AO

0

1

Operating Mode

Turns off A/D charge pump.

Turns on A/D charge pump. Required for operation below 4 V.

Operating Mode

Internal AUX-RAM (00H - FH) access using MOVX @ RI / @ DPTR.

External data memory access.

Operating Mode

ALE is permitted at a constant rate of 1/6 the oscillator frequency.

ALE is active only during a MOVX or MOVC instruction.

Notes

1. Usersoftware shouldnot write ‘1’sto reserved bits.These bits maybe used infuture 80C51 familyproducts toinvoke

new features. In that case, the reset or inactive of the new bitwill be 0, and its active value will be ‘1’. The value read

from a reserved bit is indeterminate.

2. Reset value is ‘xxxxxx10B’.

2000 Jul 26 14

Philips Semiconductors Preliminary Specification

Single-chip 8-bit microcontroller with CAN controller P8xC591

handbook, full pagewidth

7Fh

(MSB) (LSB)

7F 7E 7D 7C 7B 7A 79 78

2Fh

2Eh

77 76 75 74 73 72 71 70

6F 6E 6D 6C 6B 6A 69 68

2Dh

67 66 65 64 63 62 61 60

2Ch

2Bh

5F 5E 5D 5C 5B 5A 59 58

2Ah

57 56 55 54 53 52 51 50

29h

4F 4E 4D 4C 4B 4A 49 48

28h

47 46 45 44 43 42 41 40

27h

3F 3E 3D 3C 3B 3A 39 38

26h

37 36 35 34 33 32 31 30

25h

2F 2E 2D 2C 2B 2A 29 28

24h

27 26 25 24 23 22 21 20

23h

1F 1E 1D 1C 1B 1A 19 18

22h

17 16 15 14 13 12 11 10

21h

0F 0E 0D 0C 0B 0A 09 08

20h

07 06 05 04 03 02 01 00

1Fh

18h

17h

10h

0Fh

08h

07h

00h

REGISTER BANK 3

REGISTER BANK 2

REGISTER BANK 1

REGISTER BANK 0

127

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

24

23

16

15

8

7

0

MHI006

Fig.6 Internal Main RAM bit addresses.

2000 Jul 26 15

Philips Semiconductors Preliminary Specification

Single-chip 8-bit microcontroller with CAN controller P8xC591

7.3.1 SPECIAL FUNCTION REGISTERS Table 4 Special Function Register Bit Address, Symbol or Alternate Port Function

* = SFRs are bit addressable; # = SFRs are modified from or added to the 80C51 SFRs.

NAME DESCRIPTION

ACC* Accumulator E0H E7 E6 E5 E4 E3 E2 E1 E0 00H

ADCH# A/D converter high C6H xxxxxxxxb

ADCON# A/D control C5H ADC.1 ADC.0 - ADCI ADCS AADR2 AADR1 AADR0 xx000000b

AUXR Auxiliary 8EH - - - - - LVADC EXTRAM A0 xxxxx110B

AUXR1 Auxiliary A2H ADC8 AIDL SRST WDE WUPD 0 - DPS 000000x0B

B* B register F0H F7 F6 F5 F4 F3 F2 F1 F0 00H

CTCON# Capture control EBH CTN3 CTP3 CTN2 CTP2 CTN1 CTP1 CTN0 CTP0 00H

CTH3# Capture high 3 CFH xxxxxxxxB

CTH2# Capture high 2 CEH xxxxxxxxB

CTH1# Capture high 1 CDH xxxxxxxxB

CTH0# Capture high 0 CCH xxxxxxxxB

CMH2# Compare high 2 CBH 00H

CMH1# Compare high 1 CAH 00H

CMH0# Compare high 0 C9H 00H

CTL3# Capture low 3 AFH xxxxxxxxB

CTL2# Capture low 2 AEH xxxxxxxxB

CTL1# Capture low 1 ADh xxxxxxxxB

CTL0# Capture low 0 ACH xxxxxxxxB

CML2# Compare low 2 ABH 00H

CML1# Compare low 1 AAH 00H

CML0# Compare low 0 A9H 00H

DPTR: Data Pointer (2 bytes):

DPH Data Pointer High 83h 00H

DPL Data Pointer Low 82h 00H

IENO*# Interrupt Enable 0 A8H EA EAD ES1 ES0 ET1 EX1 ET0 EX0 00H

IEN1*# Interrupt Enable 1 E8H ET2 ECAN ECM1 ECM0 ECT3 ECT2 ECT1 ECT0 00H

IP0*# Interrupt Priority 0 B8H - PAD PS1 PS0 PT1 PX1 PT0 PX0 x0000000B

IP0H Interrupt Priority 0 high B7H - PADH PS1H PS0H PT1H PX1H PT0H PX0H x0000000B

IP1*# Interrupt Priority 1 F8h PT2 PCAN PCM1 PCM0 PCT3 PCT2 PCT1 PCT0 00H

IP1H Interrupt Priority 1 high F7H PT2H PCANH PCM1H PCM0H PCT3H PCT2H PCT1H PCT0H 00H

CANMOD CAN Mode Register C4H 00H

CANCON CAN Command (w) and

Interrupt (r)

CANDAT CAN Data C2H 00H

CANADR CAN Address C1H 00H

CANSTA* CAN Status (r) C0H BS ES TS RS TCS TBS DOS RBS 00H

CAN Interrupt Enable (w) BEIE ALIE EPIE WUIE DOIE EIE TIE RIE

SFR

ADDR

C3H 00H

MSB LSB

AF AE AD AC AB AA A9 A8

EF EE ED EC EB EA E9 E8

BF BE BD BC BB BA B9 B8

FF FE FD FC FB FA F9 F8

C7 C6 C5 C4 C3 C2 C1 C0

BIT FUNCTIONS AND ADDRESSES

RESET

VALUE

2000 Jul 26 16

Philips Semiconductors Preliminary Specification

Single-chip 8-bit microcontroller with CAN controller P8xC591

NAME DESCRIPTION

P1M1 Port 1 output mode 1 92H FCH

P1M2 Port 1 output mode 2 93H 00H

P2M1 Port 2 output mode 1 94H 00H

P2M2 Port 2 output mode 2 95H 00H

P3M1 Port 3 output mode 1 9AH 00H

P3M2 Port 3 output mode 2 9BH 00H

P3* Port 3 B0H

P2* Port 2 A0H A15 A14 A13 A12 A11 A10 A9 A8 FFH

P1* Port 1 90H SDA SCL CT3I CT2I CT1I CT0I TXDC RXDC FFH

P0* Port 0 80H AD7 AD6 AD5 AD4 AD3 AD2 AD1 AD0 FFH

PCON Power Control 87H SMOD1 SMOD0 POF WLE GF1 GF0 PD IDL 00x00000B

PSW Program Status Word D0H CY AC F0 RS1 RS0 OV F1 P 00H

PWMP# PWM Prescaler FEH 00H

PWMP1# PWM Register 1 FDH 00H

PWMP0# PWM Register 0 FCH 00H

RTE# Reset Enable EFH RP35 RP34 RP33 RP32 xxxx0000B

S0ADDR Serial 0 Slave Address F9H 00H

S0ADEN Slave Address Mask B9H 00H

SP Stack Pointer 81H 07H

S0BUF Serial 0 Data Buffer 99H xxxxxxxxB

S0PSL Prescaler Value UART FAH 00H

S0PSH Prescaler/Value UART FBH SPS Prescaler higher nibble 0xxx0000B

S0CON* Serial 0 Control 98H SM0/FE SM1 SM2 REN TB8 RB8 TI RI 00H

S1CON#* Serial 1Control D8H CR2 ENS1 STA ST0 SI AA CR1 CR0 00H

S1ADR# Serial 1 Address DBH SLAVE ADDRESS GC 00H

S1DAT# Serial 1 Data DAH 00H

S1STA# Serial 1 Status D9H SC4 SC3 SC2 SC1 SC0 0 0 0 F8H

STE# Set Enable EEH SP35 SP34 SP33 SP32 xxxx0000B

TH1 Timer High 1 8DH 00H

TH0 Timer High 0 8CH 00H

TL1 Timer Low 1 8BH 00H

TL0 Timer Low 0 8AH 00H

TMH2# Timer High 2 EDH 00H

TML2# Timer Low 2 ECH 00H

SFR

ADDR

MSB LSB

B7 B6 B5 B4 B3 B2 B1 B0

- - CSMR3 CSMR2 CSMR1 CSMR0 RT2 T2

RD WR T1 T0 INT1 INT0 TXD RXD FFH

A7 A6 A5 A4 A3 A2 A1 A0

97 96 95 94 93 92 91 90

ADC5 ADC4 ADC3 ADC2 ADC1 ADC0 −−

87 86 85 84 83 82 81 80

9F 9E 9D 9C 9B 9A 99 98

DF DE DD DC DB DA D9 D8

BIT FUNCTIONS AND ADDRESSES

RESET

VALUE

2000 Jul 26 17

Philips Semiconductors Preliminary Specification

Single-chip 8-bit microcontroller with CAN controller P8xC591

NAME DESCRIPTION

TMOD Timer Mode 89H GATE C/T M1 M0 GATE C/T M1 M0 00H

TCON* Timer Control 88H TF1 TR1 TF0 TR0 IE1 IT1 IE0 IT0 00H

TM2CON# Timer 2 Control EAH T2IS1 T2IS0 T2ER T2B0 T2P1 T2P0 T2MS1 T2MS0 00H

TM2IR#* Timer 2/CAN Int Flag Reg C8H T2OV CMI2/

T3# Timer 3 FFH 00H

SFR

ADDR

MSB LSB

8F 8E 8D 8C 8B 8A 89 88

CF CE CD CC CB CA C9 C8

BIT FUNCTIONS AND ADDRESSES

CMI1 CMI0 CTI3 CTI2 CTI1 CTI0 00H

CAN

RESET

VALUE

2000 Jul 26 18

Philips Semiconductors Preliminary Specification

Single-chip 8-bit microcontroller with CAN controller P8xC591

7.4 Dual DPTR

The dual DPTR structure (see Figure 7) is a way by which

the chip will specify the address of an external data

memorylocation. There aretwo 16-bit DPTRregistersthat

address the external memory, and a single bit called DPS

= AUXR1/bit0 that allows the program code to switch

between them.

The DPS bit status should be saved by software when

switching between DPTR0 and DPTR1.

Note that bit 2is not writable and is always read as a zero.

This allows the DPS bit to be quickly toggled simply by

executing an INC AUXR1 instruction without affecting the

other bits.

DPTR Instructions

Theinstructions that refer toDPTRrefer to thedatapointer

that is currently selected using the AUXR1/bit 0 register.

The six instructions that use the DPTR are as follows:

INC DPTRIncrements the data pointer by 1

MCV DPTR, #data 16 Loadsthe DPTRwith a16-bit

constant

MOV A, @ A+DPTR Move code byte relative to

DPTR to ACC

MOVX A, @ DPTR Move external RAM (16-bit

address) to ACC

MOVX @ DPTR, A Move ACC to external RAM

(16-bit address)

JMP @ A + DPTR Jump indirect relative to

DPTR

The data pointer canbe accessed on a byte-by-byte basis

by specifying the low or high byte in an instruction which

accesses the SFRs. See application note AN458 for more

details.

handbook, full pagewidth

DPS

BT0

AUXR1

DPH

(83H)

DPTR1

DPTR0

DPL

(82H)

Fig.7 Dual DPTR:

EXTERNAL

DATA

MEMORY

MHI007

2000 Jul 26 19

Philips Semiconductors Preliminary Specification

Single-chip 8-bit microcontroller with CAN controller P8xC591

7.4.1 AUXR1 PAGE REGISTER

Table 5 AUXR1 Page Register (address A2H)

76543210

ADC8 AIDL SRST WDE WUPD 0 − DSP

Table 6 Description of AUXR1 of bits

User software should not write 1s to reserved bits. Theses bits may be used in future 8051 family products to invoke

new features. Inthat case, the reset or inactive valueof the new bit will be logic 0, and its activevalue will be logic 1. The

value read from a reserved bit is indeterminate. The reset value of AUXR1 is (000000xB).

BIT SYMBOL DESCRIPTION

7 ADC8 ADC Mode Switch. Switches between 10-bit conversion and 8-bit conversion

ADC8

6 AIDL Enables the ADC during Idle mode.

5 SRST Software Reset.

4 WDE Watchdog Timer Enable Flag.

3 WUPD Enable Wake-up from Power-down.

20Reserved.

1 − Reserved.

0 DSP Data Pointer Switch. Switches between DPRT0 and DPTR1.

ADC8

Operating Mode

0

10-bit conversion (50 machine cycles)

1

8-bit conversion (24 machine cycles)

Operating Mode

0

DPTR0

1

DPTR1

2000 Jul 26 20

Philips Semiconductors Preliminary Specification

Single-chip 8-bit microcontroller with CAN controller P8xC591

8 I/O FACILITIES

The P8xC591 consists of 32 I/O Port lines with partly

multiple functions. The I/O’s are held HIGH during reset

(asynchronous, before oscillator is running).

Ports 0, 1, 2 and 3 perform the following alternative

functions:

Port 0 is the same as in the 80C51. After reset the Port

Special Function Register is set to ‘FFh’ as known

from other 80C51 derivatives. Port 0 also provides

the multiplexed low-order address and data bus

used for expanding the P8xC591 with standard

memories and peripherals.

Port 1 supports several alternative functionalities. For this

reason it has different I/O stages. Note, port P1.0

and P1.1 are Driven-High and P1.2 to P1.7 are

High-Impedance (Tri-state) after reset.

Port 2 is the same as in the 80C51. After reset the Port

Special Function Register is set to ‘FFh’ as known

from other 80C51 derivatives. Port 2 also provides

the high-order address bus when the P8xC591 is

expanded with external Program Memory and/or

external Data Memory.

Port 3 is the same as in the 80C51. During reset the Port

3Special Function Register issetto‘FFh’ as known

from other 80C51 derivatives.

A pulse of such short duration is necessary in order to

recover from a processor or system fault as fast as

possible.

Note that the short reset pulse from Timer T3 cannot

discharge the power-on reset capacitor (see Figure 8).

Consequently,when the watchdog timerisalso used to set

externaldevices, this capacitor arrangementshouldnot be

connected to the

RST pin, and adifferent circuitshould be

used to perform the power-on reset operation. A timer T3

overflow, if enabled, will force a reset condition to the

P8xC591 by an internal connection, whether the output

RST is pulled-up HIGH or not.

A reset may be performed in software by setting the

software reset bit, SRST (AUXR1.5).

This device also has a Power-on Detect Reset circuit as

transitions from VCC past V

V

CC

on-chip

resistor

V

DD

handbook, halfpage

RST

SCHMITT

TRIGGER

RST

.

CIRCUITRY

RESET

9 OSCILLATOR CHARACTERISTICS

XTAL1 and XTAL2 are the input and output, respectively,

of an inverting amplifier. The pins can be configured for

use as an on-chip oscillator, as shown in the logic symbol.

To drive the device from an external clock source, XTAL1

should be driven while XTAL2 is left unconnected. There

are no requirementson the duty cycle ofthe externalclock

signal. However, minimum and maximum high and low

times specified in the data sheet must be observed.

10 RESET

A reset is accomplished by holding the

RST pin LOW for

at least two machine cycles (12 oscillator periods), while

the oscillator is running. To insure a good power-on reset,

RSTpin must be lowlongenough to allow theoscillator

the

time to start up (normally a few milliseconds) plus two

machine cycles.

RST line can also be pulled LOW internally by a

The

pull-down transistor activated by the watchdog timer T3.

Thelength of theoutputpulse from T3is3 machine cycles.

Fig.8 On-Chip Reset Configuration.

handbook, halfpage

2.2 µF

V

DD

R

RST

RST

P8xC591

MHI009

Fig.9 Power-on Reset.

overflow

timer T3

MHI008

2000 Jul 26 21

Philips Semiconductors Preliminary Specification

Single-chip 8-bit microcontroller with CAN controller P8xC591

11 LOW POWER MODES

11.1 Stop Clock Mode

The static design enables the clock speed to be reduced

down to 0 MHz (stopped). When the oscillator is stopped,

the RAM and Special Function Registers retain their

values. This mode allows step-by-step utilization and

permits reduced system power consumption by lowering

the clock frequency down to any value. For lowest power

consumption the Power-down mode is suggested.

11.2 Idle Mode

In the Idlemode (seeTable 7), the CPU puts itselfto sleep

while all of the on-chip peripherals stay active. The

instruction to invoke the idle mode is the last instruction

executed in the normal operating mode before the Idle

mode is activated. The CPU contents, the on-chip RAM,

andall of the specialfunctionregisters remain intact during

this mode. The Idle mode can be terminated either by any

enabled interrupt (at which time the process is picked up

at the interrupt service routine and continued), or by a

hardware reset which starts the processor in the same

manner as a Power-on reset.

11.3 Power-down Mode

To save even more power, a Power-down mode (see

Table 7) can be invoked by software. In this mode, the

oscillatorisstopped and the instructionthatinvokedPower

Down is the last instruction executed. The on-chip RAM

and Special FunctionRegisters retain their values downto

2.0 Vand care mustbetaken to returnV

tothe minimum

CC

specifiedoperating voltages beforethePower-down Mode

is terminated.

A hardware reset or external interrupt can be used to exit

from Power-down. The Wake-up from Power-down bit,

WUPD (AUXR1.3) must be set in order for an interrupt to

cause a Wake-up from Power-down. Reset redefines all

the SFRs but does not change the on-chip RAM. A

Wake-up allows both the SFRs and the on-chip RAM to

retain their values.

To properly terminate Power-down the reset or external

interrupt should not be executed before V

is restored to

CC

its normal operating level and must be held active long

enough for the oscillator to restart and stabilize (normally

less than 10 ms).

Table 7 Status of external pins during Idle and Power-down modes

MODE MEMORY ALE

PSEN PORT 0 PORT 1 PORT 2 PORT 3

PWM0/

PWM1

Idle internal 1 1 port data port data port data port data high

external 1 1 float port data address port data high

Power-down internal 0 0 port data port data port data port data high

external 0 0 float port data port data port data high

With an externalinterrupt,

INT0 and INT1must beenabled and configured as level-sensitive. Holding thepin lowrestarts

the oscillator but bringing the pin back high completes the exit. Once the interrupt is serviced, the next instruction to be

executed after RETI will be the one following the instruction that put the device into Power-down.

2000 Jul 26 22

Philips Semiconductors Preliminary Specification

Single-chip 8-bit microcontroller with CAN controller P8xC591

11.3.1 POWER OFF FLAG The Power Off Flag (POF) is set by on-chip circuitry when

theV

levelon the P8xC591rises from 0to5 V. The POF

CC

bit can be set or cleared by software allowing a user to

determine if the reset is the result of a power-on or warm

after Power-down. The V

for the POF to remain unaffected by the V

11.3.2 D

ESIGN CONSIDERATION

level must remain above 3 V

CC

level.

CC

• When the Idle mode is terminated by a hardware reset,

the device normally resumes program execution, from

where it left off, up to two machine cycles before the

internal reset algorithm takes control.On-chip hardware

inhibits access to internal RAM in this event, but access

to the port pins is not inhibited. To eliminate the

possibility of an unexpected write when Idle is

terminated by reset, the instruction following the one

that invokes Idle should not be one that writes to a port

pin or to external memory.

11.3.5 P

OWER CONTROL REGISTER (PCON)

11.3.3 ONCE

TM

MODE

The ONCETM (“On-Circuit Emulation”) Mode facilities

testing and debugging of systems without the device

having to be removed from the circuit.The ONCE Mode is

invoked by:

1. Pull ALE low while the device is in reset an

PSEN is

high,

2. Hold ALE low as

RST is deactivated.

While the device is in ONCE Mode, the Port 0 pins go into

a float state, and the other port pins and ALE and

PSEN

are weakly pulled high. The oscillator circuit remains

active.While the deviceis inthismode, anemulatoror test

CPU can be used to drive the circuit. Normal operation is

restored when a normal reset is applied.

11.3.4 R

EDUCED EMI MODE

The ALE-Off bit, AO (AUXR.0) can be set to 0 disable the

ALE output. It will automatically become active when

required for external memoryaccesses and resume to the

OFF state after completing the external memory access.

Table 8 Power Control Register (address 87H)

76543210

SMOD1 SMOD0 POF WLE GF1 GF0 PD IDL

Table 9 Description of PCON bits

If logic 1s are written to PD and IDL at the same time, PD takes precedence. The reset value of PCON is (0XX00000).

BIT SYMBOL DESCRIPTION

7 SMOD1 Double Baud rate. When set to logic 1 the baud rate is doubled when the serial port

SIO0 is being used in Modes 1, 2 and 3.

6 SMOD0 Double Baud rate. Selects SM0/FE for SCON.7 bit.

5 POF Power Off flag.

4 WLE Watchdog Load Enable. This flag must be set by software prior to loading T3

(Watchdog Timer). It is cleared when T3 is loaded.

3 GF1 General purpose flag bits.

2 GF0

1PDPower-down mode select. Setting this bit activates Power-down mode. It can only be

set if the Watchdog timer enable bit ‘WDE’ is set to logic 0.

0 IDL Idle mode select. Setting this bit activates the Idle mode.

2000 Jul 26 23

Philips Semiconductors Preliminary Specification

Single-chip 8-bit microcontroller with CAN controller P8xC591

12 CAN, CONTROLLER AREA NETWORK

Controller Area Network is the definition of a high

performance communication protocol for serial data

communication.TheCAN controller circuitry is designedto

provide a full implementation of the CAN-Protocol

according to the CAN Specification Version 2.0 B.

Microcontroller including this on-chip CAN controller are

used to build powerful local networks, both for general

industrial and automotive environments. The result is a

strongly reduced wiring harness and enhanced diagnostic

and supervisory capabilities.

TheP8xC591 includesthe same functionsknown from the

SJA1000 stand-alone CAN controller from Philips

Semiconductors with the following improvements:

• Enhanced receive interrupt

• Enhanced acceptance filter

– 8 filter for standard frame formats

– 4 filter for extended formats

– “change on the fly” feature.

12.1 Features of the PeliCAN controller

12.1.1 G

ENERAL CAN FEATURES

12.1.2 P8

• Supports 11-bit identifier as well as 29-bit identifier

• Bit rates up to 1 Mbit/s

• Error Counters with read / write access

• Programmable Error Warning Limit

• Error Code Capture with detailed bit position

• Arbitration Lost Interrupt with detailed bit position

• Single Shot Transmission (no re-transmission)

• Listen Only Mode (no acknowledge, no active error

flags)

• Hot Plugging support (software driven bit rate detection)

• Extended receive buffer (FIFO, 64 byte)

• Receive Buffer level sensitive Receive Interrupt

• High Priority Acceptance Filters for Receive Interrupt

• Acceptance Filters with “change on the fly” feature

• Reception of “own” messages (Self Reception Request)

• Programmable CAN output driver configuration.

XC591 PELICAN FEATURES (ADDITIONAL TO

CAN 2.0B)

• CAN 2.0B protocol compatibility

• Multi-master architecture

• Bus access priority determined by the message

identifier (11 bit or 29 bit)

• Non destructive bit-wise arbitration

• Guaranteed latency time for high priority messages

• Programmable transfer rate (up to 1Mbit/s)

• Multicast and broadcast message facility

• Data length from 0 up to 8 bytes

• Powerful error handling capability

• Non-return-to-zero (NRZ) coding/decoding with

bit-stuffing

• Suitable for use in a wide range of networks including

SAE’s network classes A, B, C.

2000 Jul 26 24

Philips Semiconductors Preliminary Specification

Single-chip 8-bit microcontroller with CAN controller P8xC591

12.2 PeliCAN structure

A 80C51 CPU Interface connects the PeliCAN to the internal bus of the P8xC591 microcontroller. Via five Special

Function Registers CANADR, CANDAT, CANMOD, CANSTA and CANCON the CPU has access to the PeliCAN. The

SFR will described later on.

handbook, full pagewidth

control

address/data

TRANSMIT

BUFFER

RECEIVE

FIFO

ACCEPTANCE

FILTER

INTERFACE

MANAGEMENT

LOGIC

PeliCAN Core BlockMESSAGE BUFFER

ERROR

MANAGEMENT

LOGIC

BIT

TIMING

LOGIC

BIT

STREAM

PROCESSOR

TRANSMIT

MANAGEMENT

LOGIC

MHI010

TXDC

TX

RXDC

RX

Fig.10 Block Diagram of the PeliCAN.

2000 Jul 26 25

Philips Semiconductors Preliminary Specification

Single-chip 8-bit microcontroller with CAN controller P8xC591

12.2.1 INTERFACE MANAGEMENT LOGIC (IML)

The Interface Management Logic interprets commands

from the CPU, controls addressing of the CAN Registers

and provides interrupts and statusinformation tothe CPU.

Additionally it drivesthe universal interface of thePeliCAN.

12.2.2 T

RANSMIT BUFFER (TXB)

The Transmit Buffer is an interface between the CPU and

the Bit Stream Processor (BSP) and is able to store a

complete CAN message which shouldbe transmittedover

the CAN network. The buffer is 13 bytes long, written by

the CPU and read out by the BSP or the CPU itself.

12.2.3 R

ECEIVE BUFFER (RXB, RXFIFO)

The Receive Buffer is an interface between the

Acceptance Filter and the CPU and stores the received

and accepted messages from the CAN Bus line. The

Receive Buffer (RXB) represents a CPU-accessible

13-byte-windowof the ReceiveFIFO(RXFIFO), which has

a total length of 64 bytes. With the help of this FIFO the

CPU is able to process one message while other

messages are being received.

12.2.4 A

CCEPTANCE FILTER (ACF)

12.2.7 B

IT TIMING LOGIC (BTL)

The Bit Timing Logic monitors the serial CAN bus line and

handles the Bus line-related bit timing. It synchronizes to

the bit stream on the CAN Bus on a “recessive” to

“dominant” Bus line transition at the beginning of a

message (hard synchronization) and resynchronizes on

further transitions during the reception of a message (soft

synchronization). The BTL also provides programmable

time segments to compensate for the propagation delay

times and phase shifts (e.g., due to oscillator drifts) and to

define the sampling timeand thenumber of samples to be

taken within a bit time.

12.2.8 T

RANSMIT MANAGEMENT LOGIC (TML)

The Transmit Management Logic provides the driver

signals for the push-pull CAN TX transistor stage.

Depending on the programmable output driver

configuration the external transistors are switched on or

off. Additionally a short circuit protection and the

asynchronous float on hardware reset is performed here.

The Acceptance Filter compares the received identifier

with the Acceptance Filter Table contents and decides

whether this message should be accepted or not. In case

of a positive acceptance test, the complete message is

stored in the RXFIFO. The ACF contains 4 independent

Acceptance Filter banks supporting extended and

standard CAN frames with “change on the fly” feature.

12.2.5 B

IT STREAM PROCESSOR (BSP)

The Bit Stream Processor is a sequencer, controlling the

datastream between theTransmitBuffer,RXFIFO and the

CAN-Bus. It also performs the error detection, arbitration,

stuffing and error handling on the CAN bus.

12.2.6 E

RROR MANAGEMENT LOGIC (EML)

The EML is responsible for the error confinement of the

transfer-layer modules. It gets error announcements from

the BSP and then informs the BSP and IML about error

statistics.

2000 Jul 26 26

Philips Semiconductors Preliminary Specification

Single-chip 8-bit microcontroller with CAN controller P8xC591

12.3 Communication between PeliCAN controller

and CPU

A 80C51 CPU Interface connects the PeliCAN to the

internal bus of an 80C51microcontroller. SpecialFunction

Registers, allows a smart and fast access to the PeliCAN

registersand RAM area. Becauseofthe big address range

to be supported, an indirect pointer based addressing is

handbook, full pagewidth

80C51

CORE

read

write

data

address

INTERFACE CAN CONTROLLER

CANADR

CANDAT

CANCON

CANSTA

CANMOD

included allowing a fast register access with address

autoincrement mode. This reduces the needed number of

Special Function Registers to an amount of 5.

• Five Special Function Registers (SFRs)

• Register address generation in auto-increment mode

• Access to the complete address range of the PeliCAN

SFRs

PeliCAN

Fig.11 CPU to CAN Interfacing.

12.3.1 SPECIAL FUNCTION REGISTERS

Via the five Special Function Registers CANADR,

CANDAT, CANMOD, CANSTA and CANCON the CPU

has access to the PeliCAN Block. Note that CANCON and

CANSTA have different registers mapped depending on

the direction of the access.

2000 Jul 26 27

MHI020

The PeliCAN registers may be accessed in two different

ways. The most important registers, which should support

softwarepolling orare controlling majorCAN functions are

accessible directly as separate SFRs. Other parts of the

PeliCAN Block are accessible using an indirect pointer

mechanism. In order to achieve a high data throughput

even if the indirect access is used, an address

auto-increment feature is included here.

Philips Semiconductors Preliminary Specification

Single-chip 8-bit microcontroller with CAN controller P8xC591

Table 10 CAN Special Function Registers

SFR ACCESS

CANADR Read/

Write

CANDAT Read/

Write

CANMOD Read/

Write

CANSTA Read Status BS ES TS RS TCS TBS DOS RBS C0

Write Interrupt

CANCON Read Interrupt BEI ALI EPI WUI DOI EI TI RI C3

Write Command - - - SRR CDO RRB AT TR

12.3.2 CANADR

This read/write register defines the address of one of the

PeliCAN internal registers to be accessed via CANDAT. It

could be interpreted as a pointer to the PeliCAN.

The read andwrite access tothe PeliCAN Blockregisteris

performed using the CANDAT register.

Withthe implemented autoaddress increment modeafast

stack-like reading and writing of CAN controller internal

registers is provided. If the currently defined address

within CANADR is above or equal to 32 decimal, the

contentofCANADR is incremented automatically afterany

read or write access to CANDAT. For instance, loading a

message into the Transmit Buffer can be done by writing

the first Transmit Buffer Address (112 decimal) into

CANADR and then moving byte by byte of the message to

CANDAT. Incrementing CANADR beyond FFh resets

CANADR to 00h.

In case CANADR is below 32 decimal, there is no

automatic address incrementation performed. CANADR

keepsits valueeven if CANDATis accessed forreading or

writing. This is to allow polling of registers in the lower

address space of the PeliCAN controller.

12.3.3 CANDAT R

CANDAT is implemented as a read/write register.

TheSpecial FunctionRegister CANDAT appearsas a port

to the CAN controller’s internal register (memory location)

being selected by CANADR. Reading or writing CANDAT

is effectively an access to that PeliCAN internal register,

PELICAN

REG.

- CANA7 CANA6 CANA5 CANA4 CANA3 CANA2 CANA1 CANA0 C1

- CAND7 CAND6 CAND5 CAND4 CAND3 CAND2 CAND1 CAND0 C2

Mode TM RIPM RPM SM − STM LOM RM C4

Enable

EGISTER

BIT7 BIT6 BIT5 BIT4 BIT3 BIT2 BIT1 BIT0

BEIE ALIE EPIE WUIE DOIE EIE TIE RIE

which is selected by CANADR. CANDAT is implemented

as a read/write register.

Note that any access to this register automatically

increments CANADR if the current address within

CANADR is above or equal to 32 decimal.

12.3.4 CANMOD

With a read or write access to CANMOD the Mode

Register of the PeliCAN is accessed directly. The Mode

register is located at address 00h within the PeliCAN

Block.

12.3.5 CANSTA The CANSTA SFR provides a direct access to the Status

Register of the PeliCAN as well as to the Interrupt Enable

Register, depending on the direction of the access.

Reading CANSTA is an access to the Status Register of

the PeliCAN (address 2). When writing to CANSTA the

Interrupt Enable Register is accessed (address 4).

12.3.6 CANCON The CANCON SFR provides a direct access to the

Interrupt Register of the PeliCAN as well as to the

Command register, depending on the direction of the

access.

When reading CANCON the Interrupt Register of the

PeliCAN is accessed (address 3), while writing to

CANCON means an access to the Command Register

(address 1).

ADDR

SFR

2000 Jul 26 28

Philips Semiconductors Preliminary Specification

Single-chip 8-bit microcontroller with CAN controller P8xC591

12.4 Register and Message Buffer description

12.4.1 A

DDRESS LAYOUT

The PeliCAN internal registers appear to the host CPU as on-chip memory mapped peripheral registers. Because the

PeliCAN can operate in different modes (Operating / Reset, see also Mode Register), one have to distinguish between

different internal address definitions. Starting from CAN Address 128 the complete internal FIFO RAM is mapped to the

CPU Interface.

Table 11 Address allocation

CAN

ADDR.

0 Mode Mode Mode Mode

1 (00) Command (00) Command

2 Status - Status 3 Interrupt - Interrupt 4 Interrupt Enable Interrupt Enable Interrupt Enable Interrupt Enable

5 Rx Interrupt Level Rx Interrupt Level Rx Interrupt Level Rx Interrupt Level

6 Bus Timing 0 - Bus Timing 0 Bus Timing 0

7 Bus Timing 1 - Bus Timing 1 Bus Timing 1

8 See Note

9 Rx Message Counter - Rx Message Counter 10 Rx Buffer Start Address - Rx Buffer Start Address 11 Arbitration Lost Capture - Arbitration Lost Capture 12 Error Code Capture - Error Code Capture 13 Error Warning Limit Error Warning Limit Error Warning Limit Error Warning Limit

14 Rx Error Counter - Rx Error Counter Rx Error Counter

15 TX Error Counter - TX Error Counter TX Error Counter

16 to 28 reserved (00) - reserved (00) -

29 ACF Mode - ACF Mode ACF Mode

30 ACF Enable ACF Enable ACF Enable ACF Enable

31 ACF Priority ACF Priority ACF Priority ACF Priority

32

33 Acceptance Code 1 Acceptance Code 1 Acceptance Code 1 Acceptance Code 1

34 Acceptance Code 2 Acceptance Code 2 Acceptance Code 2 Acceptance Code 2

35 Acceptance Code 3 Acceptance Code 3 Acceptance Code 3 Acceptance Code 3

36 Acceptance Mask 0 Acceptance Mask 0 Acceptance Mask 0 Acceptance Mask 0

37 Acceptance Mask 1 Acceptance Mask 1 Acceptance Mask 1 Acceptance Mask 1

38 Acceptance Mask 2 Acceptance Mask 2 Acceptance Mask 2 Acceptance Mask 2

39 Acceptance Mask 3 Acceptance Mask 3 Acceptance Mask 3 Acceptance Mask 3

40

41 Acceptance Code 1 Acceptance Code 1 Acceptance Code 1 Acceptance Code 1

42 Acceptance Code 2 Acceptance Code 2 Acceptance Code 2 Acceptance Code 2

43 Acceptance Code 3 Acceptance Code 3 Acceptance Code 3 Acceptance Code 3

44 Acceptance Mask 0 Acceptance Mask 0 Acceptance Mask 0 Acceptance Mask 0

45 Acceptance Mask 1 Acceptance Mask 1 Acceptance Mask 1 Acceptance Mask 1

46 Acceptance Mask 2 Acceptance Mask 2 Acceptance Mask 2 Acceptance Mask 2

47 Acceptance Mask 3 Acceptance Mask 3 Acceptance Mask 3 Acceptance Mask 3

Acceptance Code 0 Acceptance Code 0 Acceptance Code 0 Acceptance Code 0

B

A

N

K

1

Acceptance Code 0 Acceptance Code 0 Acceptance Code 0 Acceptance Code 0

B

A

N

K

2

READ WRITE READ WRITE

2 ---

OPERATING MODE RESET MODE

2000 Jul 26 29

Philips Semiconductors Preliminary Specification

Single-chip 8-bit microcontroller with CAN controller P8xC591

CAN

ADDR.

48

49 Acceptance Code 1 Acceptance Code 1 Acceptance Code 1 Acceptance Code 1

50 Acceptance Code 2 Acceptance Code 2 Acceptance Code 2 Acceptance Code 2

51 Acceptance Code 3 Acceptance Code 3 Acceptance Code 3 Acceptance Code 3

52 Acceptance Mask 0 Acceptance Mask 0 Acceptance Mask 0 Acceptance Mask 0

53 Acceptance Mask 1 Acceptance Mask 1 Acceptance Mask 1 Acceptance Mask 1

54 Acceptance Mask 2 Acceptance Mask 2 Acceptance Mask 2 Acceptance Mask 2

55 Acceptance Mask 3 Acceptance Mask 3 Acceptance Mask 3 Acceptance Mask 3

56

57 Acceptance Code 1 Acceptance Code 1 Acceptance Code 1 Acceptance Code 1

58 Acceptance Code 2 Acceptance Code 2 Acceptance Code 2 Acceptance Code 2

59 Acceptance Code 3 Acceptance Code 3 Acceptance Code 3 Acceptance Code 3

60 Acceptance Mask 0 Acceptance Mask 0 Acceptance Mask 0 Acceptance Mask 0

61 Acceptance Mask 1 Acceptance Mask 1 Acceptance Mask 1 Acceptance Mask 1

62 Acceptance Mask 2 Acceptance Mask 2 Acceptance Mask 2 Acceptance Mask 2

63 Acceptance Mask 3 Acceptance Mask 3 Acceptance Mask 3 Acceptance Mask 3

64 to 95 reserved (00) - reserved (00) -

96 Rx Frame Info Rx Frame Info - Rx Frame Info Rx Frame Info Rx Frame Info Rx Frame Info

97 Rx Identifier 1 Rx Identifier 1 - Rx Identifier 1 Rx Identifier 1 Rx Identifier 1 Rx Identifier 1

98 Rx Identifier 2 Rx Identifier 2 - Rx Identifier 2 Rx Identifier 2 Rx Identifier 2 Rx Identifier 2

99 Rx Data 1 Rx Identifier 3 - Rx Data 1 Rx Identifier 3 Rx Data 1 Rx Identifier 3

100 Rx Data 2 Rx Identifier 4 - Rx Data 2 Rx Identifier 4 Rx Data 2 Rx Identifier 4

101 Rx Data 3 Rx Data 1 - Rx Data 3 Rx Data 1 Rx Data 3 Rx Data 1

102 Rx Data 4 Rx Data 2 - Rx Data 4 Rx Data 2 Rx Data 4 Rx Data 2

103 Rx Data 5 Rx Data 3 - Rx Data 5 Rx Data 3 Rx Data 5 Rx Data 3

104 Rx Data 6 Rx Data 4 - Rx Data 6 Rx Data 4 Rx Data 6 Rx Data 4

105 Rx Data 7 Rx Data 5 - Rx Data 7 Rx Data 5 Rx Data 7 Rx Data 5

106 Rx Data 8 Rx Data 6 - Rx Data 8 Rx Data 6 Rx Data 8 Rx Data 6

107 (FIFO RAM)

108 (FIFO RAM)

109 to 111 reserved (00) - reserved (00) -

112 Tx Frame Info Tx Frame Info Tx Frame Info Tx Frame Info Tx Frame Info Tx Frame Info Tx Frame Info Tx Frame Info

113 Tx Identifier 1 Tx Identifier 1 Tx Identifier 1 Tx Identifier 1 Tx Identifier 1 Tx Identifier 1 Tx Identifier 1 Tx Identifier 1

114 Tx Identifier 2 Tx Identifier 2 Tx Identifier 2 Tx Identifier 2 Tx Identifier 2 Tx Identifier 2 Tx Identifier 2 Tx Identifier 2

Acceptance Code 0 Acceptance Code 0 Acceptance Code 0 Acceptance Code 0

B

A

N

K

3

Acceptance Code 0 Acceptance Code 0 Acceptance Code 0 Acceptance Code 0

B

A

N

K

4

READ WRITE READ WRITE

(SFF) (EFF) (SFF) (EFF) (SFF) (EFF)

(1)

(1)

(SFF) (EFF) (SFF) (EFF) (SFF) (EFF)

OPERATING MODE RESET MODE

Rx Data 7 - (FIFO RAM)

Rx Data 8 - (FIFO RAM)

(1)

Rx Data 7 (FIFO RAM)

(1)

Rx Data 8 (FIFO RAM)

(1)

(1)

Rx Data 7

Rx Data 8

2000 Jul 26 30

Loading...

Loading...