Page 1

INTEGRATED CIRCUITS

USER

MANUAL

P89LPC920/921/922

80C51 8-bit microcontroller with two-clock core

2 KB/4 KB/8 KB 3 V low-power Flash with 256 Byte RAM

2003 Nov 6

Page 2

Philips Semiconductors

80C51 8-bit microcontroller with two-cycle instructions

2KB/4KB/8KB Flash with 256 Byte RAM

User Manual - Subject to Change

P89LPC920/921/922

2003 Nov 6 2

Page 3

Philips Semiconductors

User Manual - Subject to Change

P89LPC920/921/922

Table of Contents

1. General Description................................................................................... 9

Pin configuration...................................................................................................... 9

20-Pin TSSOP, DIP Package .................................................................................. 9

Logic symbol............................................................................................................ 9

Pin Descriptions....................................................................................................... 11

Special Function Registers...................................................................................... 14

Memory organization ............................................................................................... 18

Data RAM arrangement................................................................................ 19

2. Clocks........................................................................................................ 21

Enhanced CPU........................................................................................................ 21

Clocks...................................................................................................................... 21

Clock definitions ...................................................................................................... 21

Oscillator clock (OSCCLK) ........................................................................... 21

Low speed oscillator option .......................................................................... 21

Medium speed oscillator option .................................................................... 21

High speed oscillator option.......................................................................... 21

Clock output............................................................................................................. 21

On-chip RC oscillator option.................................................................................... 22

Watchdog oscillator option ...................................................................................... 22

External clock input option....................................................................................... 23

Oscillator Clock (OSCCLK) wakeup delay .............................................................. 23

CPU Clock (CCLK) modification: DIVM register...................................................... 23

Low power select..................................................................................................... 24

3. Interrupts ................................................................................................... 25

Interrupt priority structure ........................................................................................ 25

External Interrupt pin glitch suppression ................................................................. 26

4. I/O Ports .................................................................................................... 29

Port configurations................................................................................................... 29

Quasi-bidirectional output configuration .................................................................. 29

Open drain output configuration .............................................................................. 30

Input-only configuration ........................................................................................... 31

Push-pull output configuration ................................................................................. 31

Port 0 analog functions............................................................................................ 31

Additional port features............................................................................................ 32

5. Power Monitoring Functions ...................................................................... 33

Brownout Detection ................................................................................................. 33

Power-on Detection ................................................................................................. 34

Power reduction modes........................................................................................... 34

6. Reset ......................................................................................................... 39

Reset vector ............................................................................................................ 40

7. Timers 0 and 1........................................................................................... 41

2003 Nov 6 3

Page 4

Philips Semiconductors

User Manual - Subject to Change

P89LPC920/921/922

Mode 0..................................................................................................................... 42

Mode 1..................................................................................................................... 42

Mode 2..................................................................................................................... 43

Mode 3..................................................................................................................... 43

Mode 6..................................................................................................................... 43

Timer overflow toggle output ................................................................................... 46

8. Real-Time Clock/System Timer................................................................. 47

Real-time Clock source ........................................................................................... 47

Changing RTCS1-0 ................................................................................................. 47

Real-time Clock interrupt/wake up........................................................................... 48

Reset sources affecting the Real-time Clock........................................................... 48

9. UART......................................................................................................... 51

Mode 0..................................................................................................................... 51

Mode 1..................................................................................................................... 51

Mode 2..................................................................................................................... 51

Mode 3..................................................................................................................... 51

SFR space............................................................................................................... 51

Baud Rate Generator and selection ........................................................................ 52

Updating the BRGR1 and BRGR0 SFRs ................................................................ 52

Framing Error .......................................................................................................... 53

Break Detect............................................................................................................ 53

More about UART Mode 0....................................................................................... 55

More about UART Mode 1....................................................................................... 56

More about UART Modes 2 and 3........................................................................... 57

Framing Error and RI in Modes 2 and 3 with SM2 = 1 ............................................ 57

Break Detect............................................................................................................ 57

Double buffering ...................................................................................................... 58

Double buffering in different modes......................................................................... 58

Transmit interrupts with double buffering enabled (Modes 1, 2 and 3) ................... 58

The 9th bit (bit 8) in double buffering (Modes 1, 2 and 3)........................................ 59

Multiprocessor communications .............................................................................. 60

Automatic address recognition ................................................................................ 60

10. I2C interface ............................................................................................ 63

I2C Data register ..................................................................................................... 64

I2C Slave Address register...................................................................................... 64

I2C Control register ................................................................................................. 64

I2C Status register................................................................................................... 66

I2C SCL Duty Cycle registers I2SCLH and I2SCLL ................................................ 66

I2C operation mode................................................................................................. 67

Master Transmitter Mode.............................................................................. 67

Master Receiver Mode.................................................................................. 68

Slave Receiver Mode.................................................................................... 69

Slave Transmitter Mode................................................................................ 69

11. Analog comparators ................................................................................ 79

2003 Nov 6 4

Page 5

Philips Semiconductors

User Manual - Subject to Change

P89LPC920/921/922

Comparator configuration ........................................................................................ 79

Internal reference voltage........................................................................................ 80

Comparator interrupt ............................................................................................... 80

Comparators and power reduction modes .............................................................. 80

Comparator configuration example ......................................................................... 81

12. Keypad Interrupt (KBI)............................................................................. 83

13. Watchdog Timer ...................................................................................... 85

Watchdog Function.................................................................................................. 85

Feed Sequence ....................................................................................................... 86

Watchdog Clock Source .......................................................................................... 88

Watchdog Timer in Timer Mode .............................................................................. 89

Power down operation............................................................................................. 90

Periodic wakeup from Power down without an external oscillator........................... 90

14. Additional Features.................................................................................. 91

Software reset ......................................................................................................... 91

Dual Data Pointers .................................................................................................. 91

15. Flash Memory.......................................................................................... 93

General description ................................................................................................. 93

Features .................................................................................................................. 93

Flash programming and erase................................................................................. 93

Using Flash as data storage: IAP-Lite..................................................................... 93

In-Circuit Programming (ICP) .................................................................................. 97

ISP and IAP capabilities of the P89LPC920/921/922.............................................. 97

Boot ROM................................................................................................................ 98

Power-On reset code execution .............................................................................. 98

Hardware activation of the Boot Loader .................................................................. 98

In-System Programming (ISP)................................................................................. 99

Using the In-System Programming.......................................................................... 99

In-Application Programming method ....................................................................... 104

IAP Authorization Key.............................................................................................. 104

User configuration bytes.......................................................................................... 109

User security bytes.................................................................................................. 110

Boot Vector.............................................................................................................. 111

Boot Status.............................................................................................................. 111

16. Instruction set .......................................................................................... 113

17. Revision History....................................................................................... 117

18. Index........................................................................................................ 119

2003 Nov 6 5

Page 6

Philips Semiconductors

User Manual - Subject to Change

P89LPC920/921/922

2003 Nov 6 6

Page 7

Philips Semiconductors

80C51 8-bit microcontroller with two-cycle instructions

2KB/4KB/8KB Flash with 256 Byte RAM

User Manual - Subject to Change

P89LPC920/921/922

List of Figures

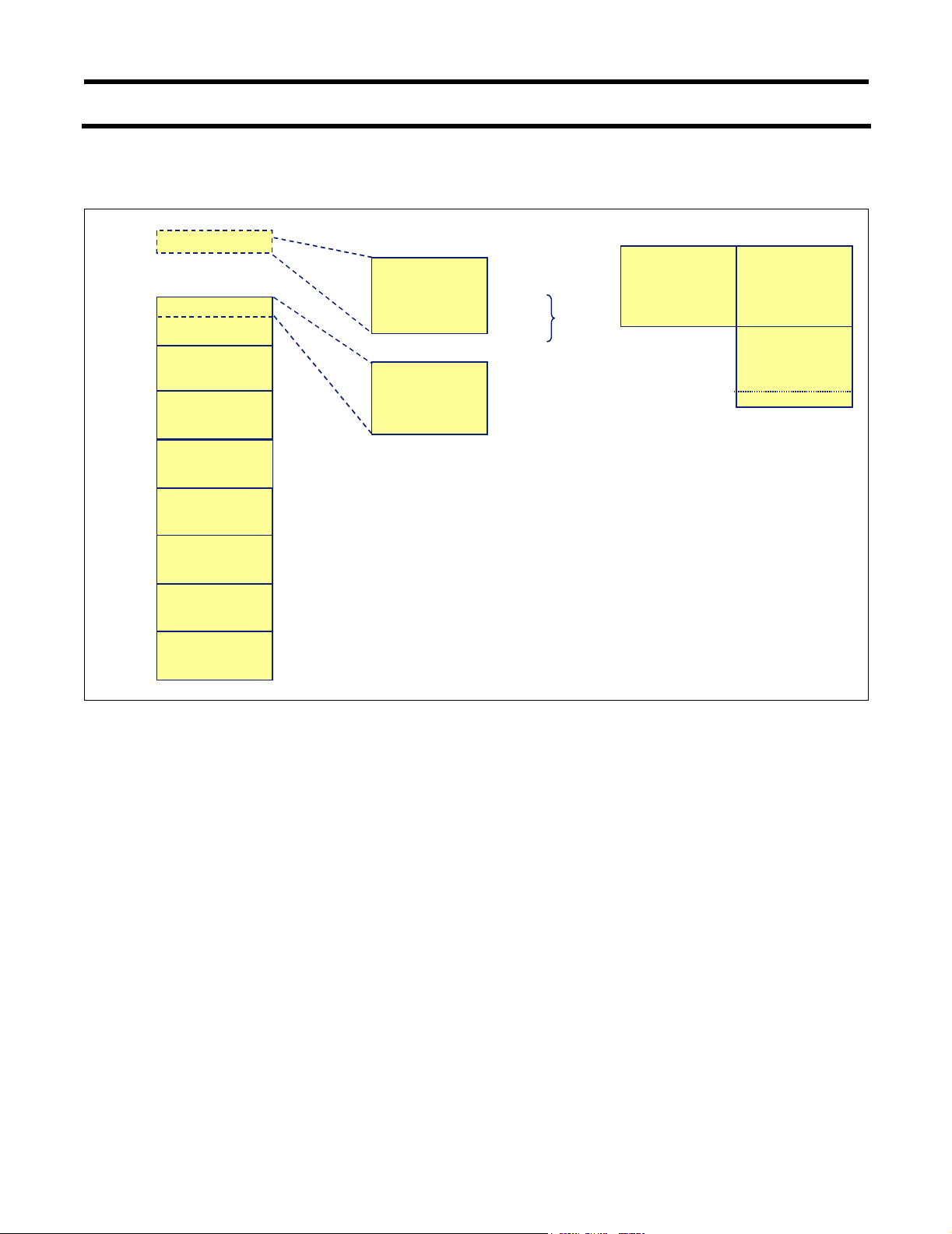

P89LPC920/921/922 memory map. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

On-chip data memory usage. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Using the crystal oscillator. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

On-chip RC oscillator TRIM register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

Block diagram of oscillator control. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

Interrupt priority level. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

Summary of interrupts. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

Interrupt sources, interrupt enables, and power down wake-up sources . . . . . . . . . . . . . 27

.Number of I/O pins available . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

Port output configuration settings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

Quasi-bidirectional output . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

Open drain output . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

Input -only . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

Push-pull output . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

Port output configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

Brownout options. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

Power reduction modes. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

Power Control register (PCON). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

Power Control register A (PCONA) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

Block diagram of Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

Reset Sources register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

Timer/Counter Mode Control register (TMOD) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

Timer/Counter Auxiliary Mode Control register (TAMOD). . . . . . . . . . . . . . . . . . . . . . . . . 42

Timer/Counter Control register (TCON) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

Timer/Counter 0 or 1 in Mode 0 (13-bit counter) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

Timer/Counter 0 or 1 in Mode 1 (16-bit counter) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

Timer/Counter 0 or 1 in Mode 2 (8-bit auto-reload). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

Timer/Counter 0 Mode 3 (two 8-bit counters) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

Timer/Counter 0 or 1 in Mode 6 (PWM auto-reload) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

Real-time Clock/System Timer block diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

Real-time Clock/System Timer clock sources . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

RTCCON Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

SFR Locations for UARTs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

Baud rate generation for UART. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

BRGCON register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

Baud rate generation for UART (Modes 1, 3) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

Serial Port Control register (SCON) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

Serial Port Status register (SSTAT) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

Serial Port Mode 0 (double buffering must be disabled) . . . . . . . . . . . . . . . . . . . . . . . . . . 56

Serial Port Mode 1 (only single transmit buffering case is shown) . . . . . . . . . . . . . . . . . . 56

Serial Port Mode 2 or 3 (only single transmit buffering case is shown). . . . . . . . . . . . . . . 57

FE and RI when SM2 = 1 in Modes 2 and 3 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

Transmission with and without double buffering . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

2003 Nov 6 7

Page 8

Philips Semiconductors

80C51 8-bit microcontroller with two-cycle instructions

2KB/4KB/8KB Flash with 256 Byte RAM

User Manual - Subject to Change

P89LPC920/921/922

I2C-bus configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

I2C Data register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

I2C Slave Address register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

I2C Control register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

I2C Status register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

I2C clock rates selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

I2C Control register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

Format in the Master Transmitter Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

Format of Master Receiver Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

A Master Receiver switches to Master Transmitter after sending Repeated Start . . . . . . 68

I2C Control register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

Format of Slave Receiver Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

Format of Slave Transmitter Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70

I2C-bus serial interface block diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

Master Transmitter Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 72

Master Receiver Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

Slave Receiver Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 74

Slave Transmitter Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

Comparator control registers (CMP1 and CMP2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 79

Comparator input and output connections . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80

Comparator configurations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 81

Keypad Pattern register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83

Keypad Control register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83

Keypad Interrupt Mask register (KBM) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 84

Watchdog timer configuration.. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 85

Watchdog Prescaler . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 86

Watchdog Timer Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 87

P89LPC920/921/922 Watchdog Timeout Values.. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 88

Watchdog Timer in Watchdog Mode (WDTE = 1). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 89

Watchdog Timer in Timer Mode (WDTE = 0) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 90

AUXR1 register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 91

Flash Memory Control Registe . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 95

Assembly language routine to erase/program all or part of a page. . . . . . . . . . . . . . . . . . 96

C-language routine to erase/program all or part of a page . . . . . . . . . . . . . . . . . . . . . . . . 97

Boot Loader Address and Default Boot Vector . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98

Forcing ISP Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 99

In-System Programming (ISP) hex record formats . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 100

IAP error status . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 105

IAP function calls. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 105

Flash User Configuration Byte 1 (UCFG1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 109

User sector Security Bytes (SEC0, ..., SEC7). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 110

Effects of Security Bits . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 110

Boot Vector (BOOTVEC). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 111

Boot Status (BOOTSTAT). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 111

Instruction set summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 113

2003 Nov 6 8

Page 9

Philips Semiconductors

User’s Manual - Preliminary -

General Description

P89LPC920/921/922

1. General Description

The P89LPC920/921/922 is a single-chip microcontroller designed for applications demanding high-integration, low cost

solutions over a wide range of performance requirements. The P89LPC920/921/922 is based on a high performance processor

architecture that executes instructions in two to four clocks, six times the rate of standard 80C51 devices. Many system level

functions have been incorporated into the P89LPC920/921/922 in order to reduce component count, board space, and system

cost.

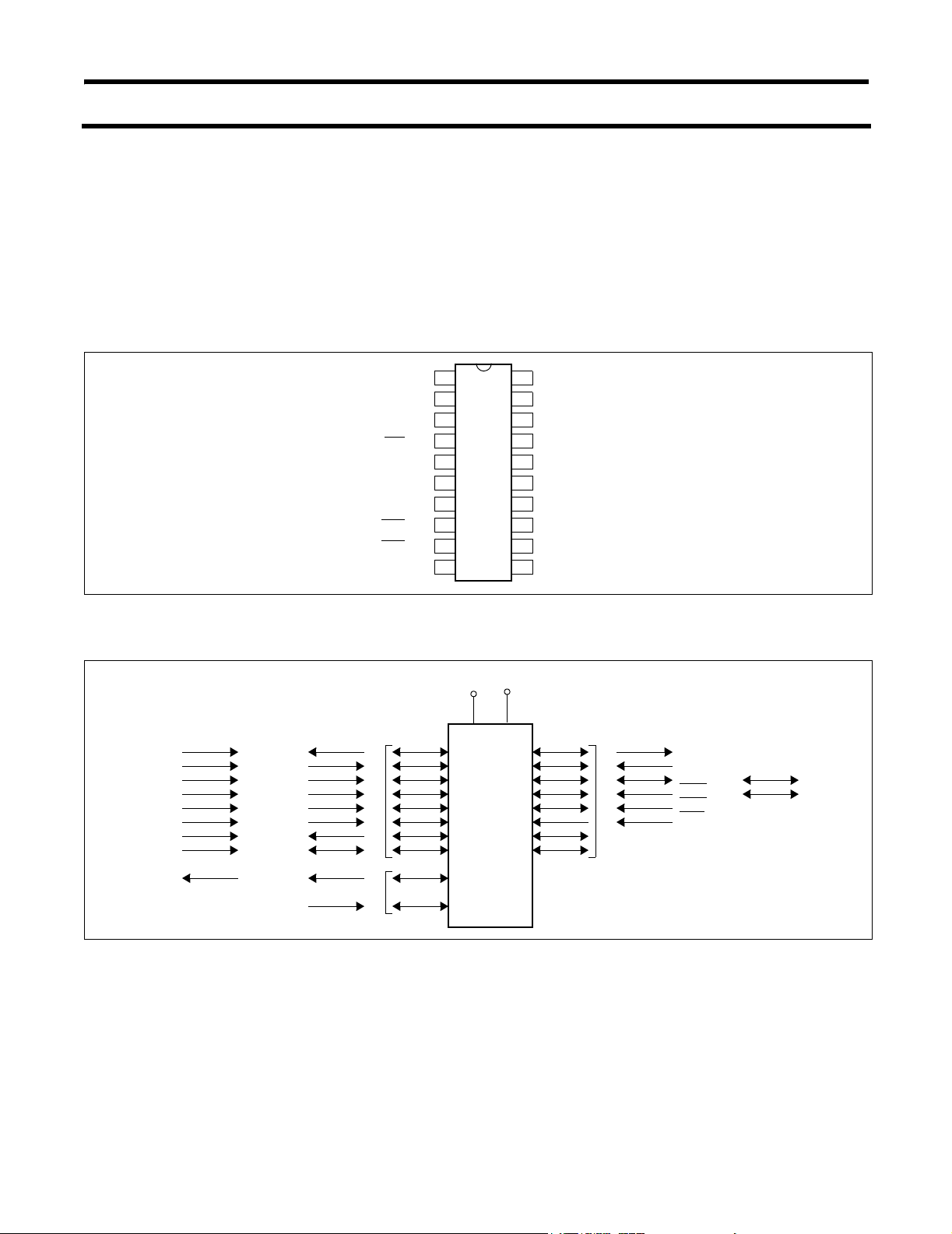

Pin configuration

20-Pin TSSOP, DIP Package

P0.1/CIN2B/KBI1KBI0/CMP2/P0.0

20

P0.2/CIN2A/KBI2

19

P0.3/CIN1B/KBI3

18

P0.4/CIN1A/KBI4

17

P0.5/CMPREF/KBI5

16

VDD

15

P0.6/CMP1/KBI6

14

P0.7/T1/KBI7

13

P1.0/TXD

12

P1.1/RXD

11

P1.7

P1.6

/P1.5

RST

VSS

XTAL1/P3.1

CLKOUT/XTAL2/P3.0

INT1

/P1.4

SDA/INT0

/P1.3

SCL/T0/P1.2

1

2

3

4

5

6

7

8

9

10

Logic symbol

KBI0

KBI1

KBI2

KBI3

KBI4

KBI5

KBI6

KBI7

CLKOUT

CMP2

CIN2B

CIN2A

CIN1B

CIN1A

CMPREF

CMP1

T1

XTAL2

XTAL1

PORT0PORT3

VDDV

SS

P89

LPC920

/921/

922

PORT1

TxD

RxD

T0

INT0

INT1

RST

SCL

SDA

2003 Nov 6 9

Page 10

Philips Semiconductors

User’s Manual - Preliminary -

General Description

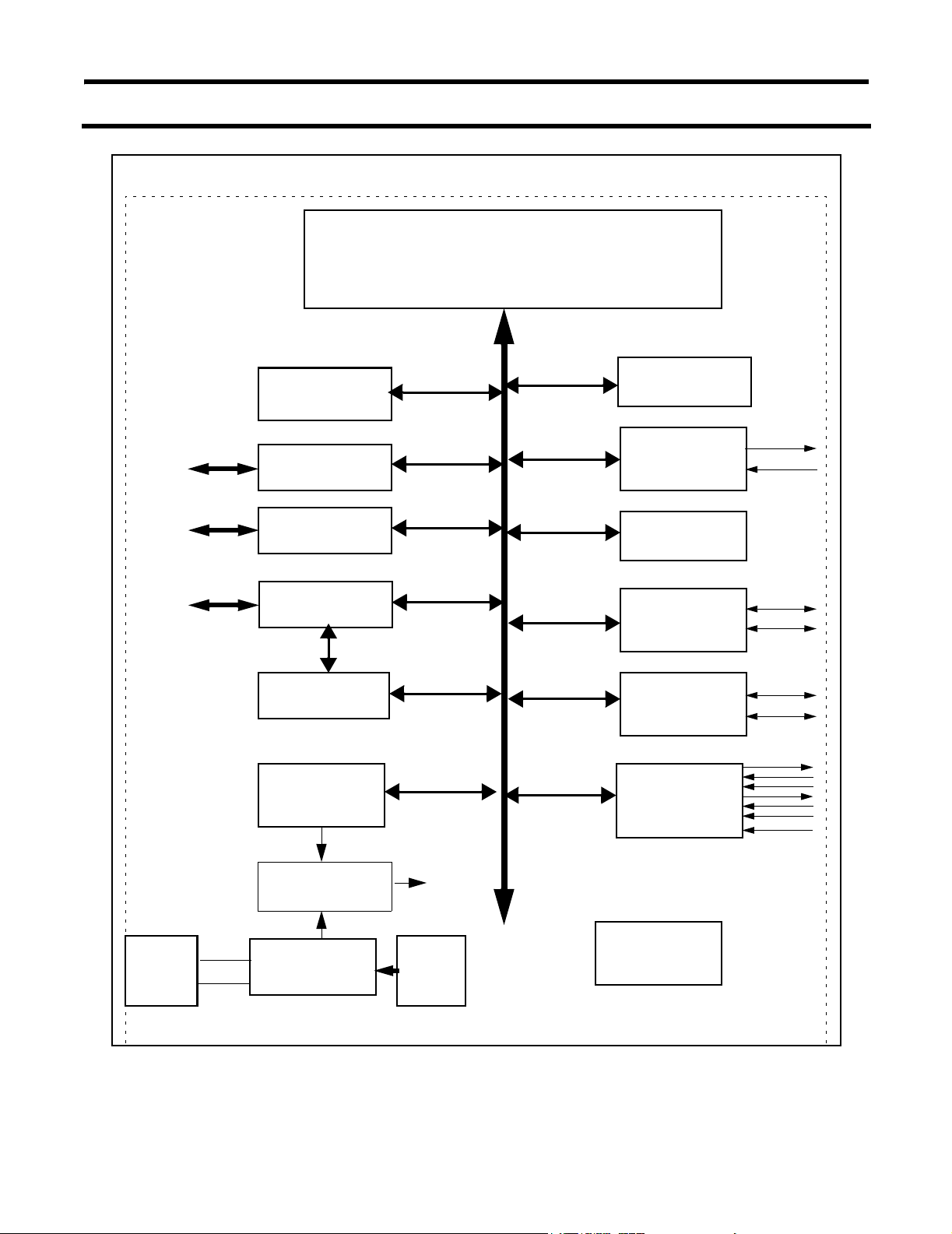

Block diagram

2KB/ 4KB/ 8KB

Code Flash

Port 3

Configurable I/Os

Port 1

Configurable I/Os

P89LPC920/921/922

High Performance

LPC920/921/922 CPU

256 Byte

Data RAM

Internal Bus

UART

Real-Time Clock/

System Timer

Crystal or

Resonator

Port 0

Configurable I/Os

Keypad

Interrupt

Watchdog Timer

and Oscillator

Programmable

Oscillator Divider

Configurable

Oscillator

CPU

Clock

On-Chip

RC

Oscillator

I2C

Timer0

Timer1

Analog

Comparators

Power Monitor

(Power-On Reset,

Brownout Reset)

2003 Nov 6 10

Page 11

Philips Semiconductors

User’s Manual - Preliminary -

General Description

Pin Descriptions

Mnemonic Pin no. Type Name and function

P0.0 - P0.7 1, 20, 19,

18, 17,

16, 14,

13

1I/OP0.0 Port 0 bit 0.

20 I/O P0.1 Port 0 bit 1.

19 I/O P0.2 Port 0 bit 2.

18 I/O P0.3 Port 0 bit 3.

17 I/O P0.4 Port 0 bit 4.

16 I/O P0.5 Port 0 bit 5.

14 I/O P0.6 Port 0 bit 6.

13 I/O P0.7 Port 0 bit 7.

I/O Port 0: Port 0 is an 8-bit I/O port with a user-configurable output type. During reset

Port 0 latches are configured in the input only mode with the internal pullup

disabled. The operation of port 0 pins as inputs and outputs depends upon the port

configuration selected. Each port pin is configured independently. Refer to the

section on I/O port configuration and the DC Electrical Characteristics for details.

The Keypad Interrupt feature operates with port 0 pins.

All pins have Schmitt triggered inputs.

Port 0 also provides various special functions as described below.

O CMP2 Comparator 2 output.

I KBI0 Keyboard Input 0.

I CIN2B Comparator 2 positive input B.

I KBI1 Keyboard Input 1.

I CIN2A Comparator 2 positive input A.

I KBI2 Keyboard Input 2.

I CIN1B Comparator 1 positive input B.

I KBI3 Keyboard Input 3.

I CIN1A Comparator 1 positive input A.

I KBI4 Keyboard Input 4.

I CMPREFComparator reference (negative) input.

I KBI5 Keyboard Input 5.

O CMP1 Comparator 1 output.

I KBI6 Keyboard Input 6.

I/O T1 Timer/counter 1 external count input or overflow output.

I KBI7 Keyboard Input 7.

P89LPC920/921/922

2003 Nov 6 11

Page 12

Philips Semiconductors

User’s Manual - Preliminary -

General Description

Mnemonic Pin no. Type Name and function

P1.0 - P1.7 12, 11,

10, 9, 8,

4, 3, 2

12 I/O P1.0 Port 1 bit 0.

11 I/O P1.1 Port 1 bit 1.

10 I/O P1.2 Port 1 bit 2. (Open-drain when used as outputs)

9I/OP1.3 Port 1 bit 3. (Open-drain when used as outputs)

8I/OP1.4 Port 1 bit 4.

4IP1.5 Port 1 bit 5. (Input only)

3I/OP1.6 Port 1 bit 6.

2I/OP1.7 Port 1 bit 7.

P3.0 - P3.1 7, 6 I/O Port 3: Port 3 is an 2-bit I/O port with a user-configurable output type. During reset

7I/OP3.0 Port 3 bit 0.

I/O

Port 1: Port 1 is an 8-bit I/O port with a user-configurable output type, except for

(for

three pins as noted below. During reset Port 1 latches are configured in the input

P1.0-

only mode with the internal pullup disabled. The operation of the configurable port 1

P1.4,

pins as inputs and outputs depends upon the port configuration selected. Each of

P1.6-

the configurable port pins are programmed independently. Refer to the section on

P1.7),

I/O port configuration and the DC Electrical Characteristics for details. P1.2 - P1.3

I (for

are open drain when used as outputs. P1.5 is input only.

P1.5)

All pins have Schmitt triggered inputs.

Port 1 also provides various special functions as described below.

O TxD Transmitter output for the serial port.

I RxD Receiver input for the serial port.

I/O T0 Timer/counter 0 external count input or overflow output. (Open-drain

when used as outputs)

2

I/O SCL I

I INT0

I/O SDA I2C serial data input/output.

I INT1

I RST

Port 3 latches are configured in the input only mode with the internal pullup

disabled. The operation of port 3 pins as inputs and outputs depends upon the port

configuration selected. Each port pin is configured independently. Refer to the

section on I/O port configuration and the DC Electrical Characteristics for details.

All pins have Schmitt triggered inputs.

Port 3 also provides various special functions as described below:

O XTAL2 Output from the oscillator amplifier (when a crystal oscillator option is

O CLKOUTCPU clock divided by 2 when enabled via SFR bit (ENCLK - TRIM.6).

C serial clock input/output.

External interrupt 0 input.

External interrupt 1 input.

External Reset input (if selected via FLASH configuration). A low on

this pin resets the microcontroller, causing I/O ports and peripherals to

take on their default states, and the processor begins execution at

address 0.

selected via the FLASH configuration).

It can be used if the CPU clock is the internal RC oscillator, watchdog

oscillator or external clock input, except when XTAL1/XTAL2 are used

to generate clock source for the real time clock/system timer.

P89LPC920/921/922

2003 Nov 6 12

Page 13

Philips Semiconductors

User’s Manual - Preliminary -

General Description

Mnemonic Pin no. Type Name and function

6I/OP3.1 Port 3 bit 1.

I XTAL1 Input to the oscillator circuit and internal clock generator circuits (when

selected via the FLASH configuration). It can be a port pin if internal

RC oscillator or watchdog oscillator is used as the CPU clock source,

AND if XTAL1/XTAL2 are not used to generate the clock for the real

time clock/system timer.

V

SS

V

DD

5IGround: 0V reference.

15 I Power Supply: This is the power supply voltage for normal operation as well as

Idle and Power Down modes.

P89LPC920/921/922

2003 Nov 6 13

Page 14

Philips Semiconductors

User’s Manual - Preliminary -

General Description

P89LPC920/921/922

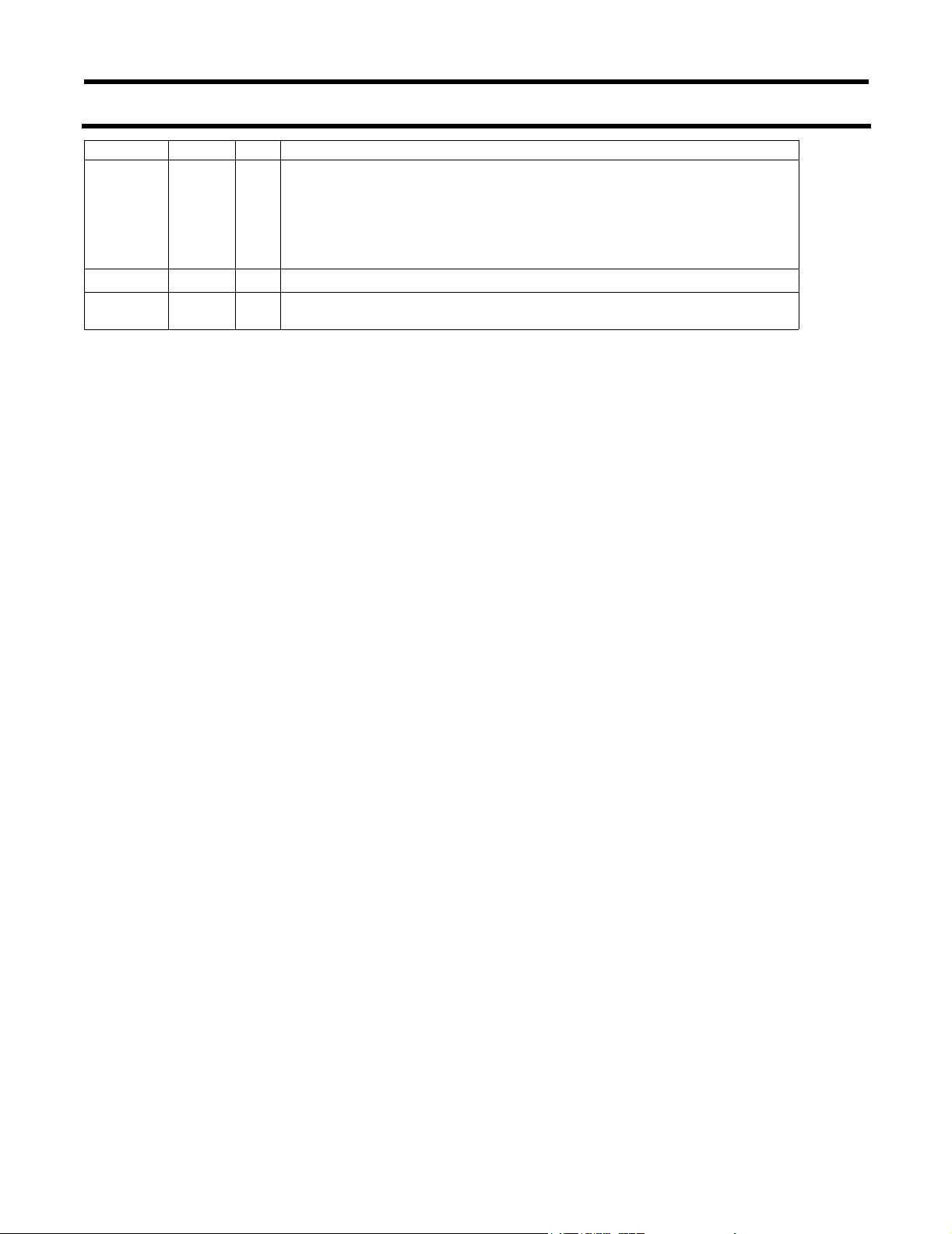

Special Function Registers

Note: Special Function Registers (SFRs) accesses are restricted in the following ways:

1. User must NOT attempt to access any SFR locations not defined.

2. Accesses to any defined SFR locations must be strictly for the functions for the SFRs.

3. SFR bits labeled ’-’, ’0’ or ’1’ can ONLY be written and read as follows:

- ’-’ Unless otherwise specified, MUST be written with ’0’, but can return any value when read (even if it was written with ’0’).

It is a reserved bit and may be used in future derivatives.

- ’0’ MUST be written with ’0’, and will return a ’0’ when read.

- ’1’ MUST be written with ’1’, and will return a ’1’ when read

Name Description

ACC* Accumulator E0H 00H 00000000

AUXR1# Auxiliary Function Register A2H CLKLP EBRR ENT1 ENT0 SRST 0 - DPS 00H

B* B Register F0H 00H 00000000

SFR

Address

MSB

E7 E6 E5 E4 E3 E2 E1 E0

F7 F6 F5 F4 F3 F2 F1 F0

Bit Functions and Addresses Reset Value

LSB

Hex Binary

1

000000x0

BRGR0#§ Baud Rate Generator Rate Low BEH 00H 00000000

BRGR1#§ Baud Rate Generator Rate High BFH 00H 00000000

%

BRGCON#Baud Rate Generator Control BDH------SBRGSBRGEN00H

CMP1# Comparator 1 Control Register ACH - - CE1 CP1 CN1 OE1 CO1 CMF1 00H

CMP2# Comparator 2 Control Register ADH - - CE2 CP2 CN2 OE2 CO2 CMF2 00H

DIVM# CPU Clock Divide-by-M Control 95H 00H 00000000

DPTR Data Pointer (2 bytes)

DPH Data Pointer High 83H 00H 00000000

DPL Data Pointer Low 82H 00H 00000000

FMADRH# Program Flash Address High E7H 00H 00000000

FMADRL# Program Flash Address Low E6H 00H 00000000

Program Flash Control (Read)

FMCON#

FMDATA# Program Flash Data E5H 00H 00000000

I2ADR# I

I2CON*# I

I2DAT# I

I2SCLH#

Program Flash Control (Write)

2

C Slave Address Register DBH I2ADR.6 I2ADR.5 I2ADR.4 I2ADR.3 I2ADR.2 I2ADR.1 I2ADR.0 GC 00H 00000000

2

C Control Register D8H - I2EN STA STO SI AA - CRSEL 00H x00000x0

2

C Data Register DAH

Serial Clock Generator/SCL Duty

Cycle Register High

BUSY - - - HVA HVE SV OI 70H 01110000

E4H

FMCMD.7FMCMD.6FMCMD.5FMCMD.4FMCMD.3FMCMD.2FMCMD.1FMCMD.

DF DE DD DC DB DA D9 D8

DDH 00H 00000000

0

xxxxxx00

1

xx000000

1

xx000000

2003 Nov 6 14

Page 15

Philips Semiconductors

User’s Manual - Preliminary -

General Description

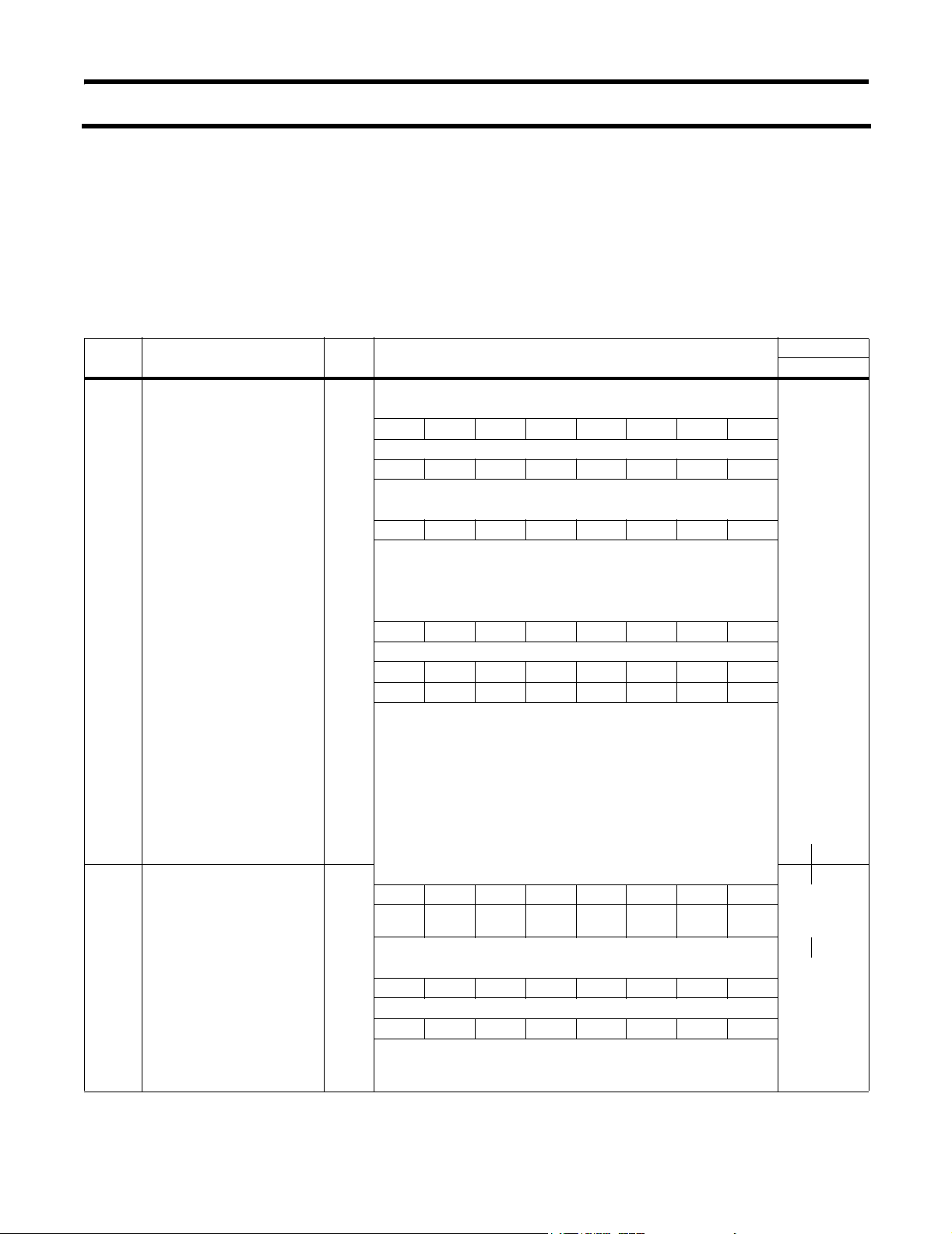

Name Description

I2SCLL#

I2STAT# I

Serial Clock Generator/SCL Duty

Cycle Register Low

2

C Status Register D9H STA.4 STA.3 STA.2 STA.1 STA.0 0 0 0 F8H 11111000

SFR

Address

MSB

Bit Functions and Addresses Reset Value

DCH 00H 00000000

P89LPC920/921/922

LSB

Hex Binary

ICRAH#

AF AE AD AC AB AA A9 A8

IEN0* Interrupt Enable 0 A8H EA EWDRT EBO ES/ESR ET1 EX1 ET0 EX0 00H 00000000

EF EE ED EC EB EA E9 E8

1

IEN1*# Interrupt Enable 1 E8H - EST - - - EC EKBI EI2C 00H

00x00000

BF BE BD BC BB BA B9 B8

1

IP0* Interrupt Priority 0 B8H - PWDRT PBO PS/PSR PT1 PX1 PT0 PX0 00H

IP0H# Interrupt Priority 0 High B7H -

PWDRT

H

PBOH

PSH/

PSRH

PT1H PX1H PT0H PX0H 00H

x0000000

1

x0000000

FF FE FD FC FB FA F9 F8

IP1*# Interrupt Priority 1 F8H - PST - - - PC PKBI PI2C 00H

1

00x00000

1

IP1H# Interrupt Priority 1 High F7H - PSTH - - - PCH PKBIH PI2CH 00H

KBCON#Keypad Control Register 94H------

PATN_S

EL

KBIF 00H

00x00000

1

xxxxxx00

KBMASK# Keypad Interrupt Mask Register 86H 00H 00000000

KBPATN# Keypad Pattern Register 93H FFH 11111111

87 86 85 84 83 82 81 80

P0* Port 0 80H T1/KB7

KBI6

CMPREF/

KBI5

CIN1A/

KBI4

CIN1B/

KBI3

CIN2A/

KBI2

CIN2B/

KBI1

CMP2/

KBI0

Note 1

CMP1/

97 96 95 94 93 92 91 90

P1* Port 1 90H - - RST

INT1

INT0/

SDA

T0/SCL RxD TxD Note 1

B7 B6 B5 B4 B3 B2 B1 B0

P3*Port 3 B0H------XTAL1XTAL2Note 1

P0M1# Port 0 Output Mode 1 84H (P0M1.7) (P0M1.6) (P0M1.5) (P0M1.4) (P0M1.3) (P0M1.2) (P0M1.1) (P0M1.0) FFH 11111111

P0M2# Port 0 Output Mode 2 85H (P0M2.7) (P0M2.6) (P0M2.5) (P0M2.4) (P0M2.3) (P0M2.2) (P0M2.1) (P0M2.0) 00H 00000000

1

P1M1# Port 1 Output Mode 1 91H (P1M1.7) (P1M1.6) - (P1M1.4) (P1M1.3) (P1M1.2) (P1M1.1) (P1M1.0) D3H

P1M2# Port 1 Output Mode 2 92H (P1M2.7) (P1M2.6) - (P1M2.4) (P1M2.3) (P1M2.2) (P1M2.1) (P1M2.0) 00H

P3M1#Port 3 Output Mode 1 B1H------(P3M1.1)(P3M1.0)03H

P3M2#Port 3 Output Mode 2 B2H------(P3M2.1)(P3M2.0)00H

11x11111

1

00x00000

1

xxxxxx11

1

xxxxxx00

PCON# Power Control Register 87H SMOD1 SMOD0 BOPD BOI GF1 GF0 PMOD1 PMOD0 00H 00000000

1

PCONA# Power Control Register A B5H RTCPD - VCPD I2PD - SPD -

00H

00000000

2003 Nov 6 15

Page 16

Philips Semiconductors

User’s Manual - Preliminary -

General Description

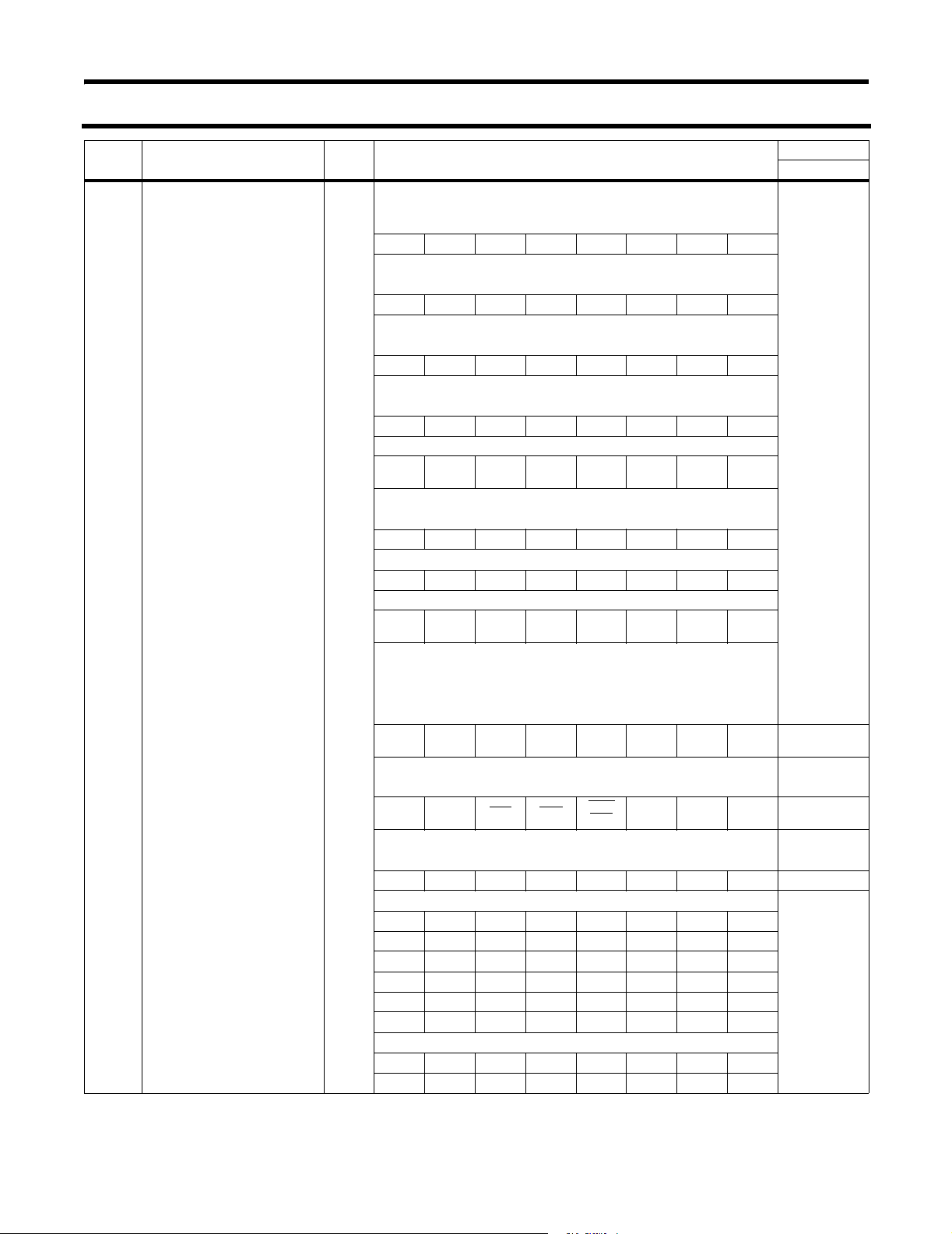

Name Description

PSW* Program Status Wword D0H CY AC F0 RS1 RS0 OV F1 P 00H 00000000

PT0AD# Port 0 Digital Input Disable F6H - - PT0AD.5 PT0AD.4 PT0AD.3 PT0AD.2 PT0AD.1 - 00H xx00000x

RSTSRC# Reset Source Register DFH - - BOF POF R_BK R_WD R_SF R_EX Note 2

RTCCON# Real-Time Clock Control D1H RTCF RTCS1 RTCS0 - - - ERTC RTCEN

RTCH# Real-Time Clock Register High D2H 00H

RTCL# Real-Time Clock Register Low D3H 00H

SADDR# Serial Port Address Register A9H 00H 00000000

SADEN# Serial Port Address Enable B9H 00H 00000000

SBUF Serial Port Data Buffer Register 99H xxH xxxxxxxx

SCON* Serial Port Control 98H SM0/FE SM1 SM2 REN TB8 RB8 TI RI 00H 00000000

SFR

Address

MSB

D7 D6 D5 D4 D3 D2 D1 D0

9F 9E 9D 9C 9B 9A 99 98

Bit Functions and Addresses Reset Value

P89LPC920/921/922

LSB

Hex Binary

1,

60H

011xxx00

5

5

00000000

5

00000000

SSTAT# Serial Port Extended Status Register BAH DBMOD INTLO CIDIS DBISEL FE BR OE STINT 00H 00000000

SP Stack Pointer 81H 07H 00000111

TAMOD# Timer 0 and 1 Auxiliary Mode 8FH - - - T1M2 - - - T0M2 00H xxx0xxx0

8F 8E 8D 8C 8B 8A 89 88

TCON* Timer 0 and 1 Control 88H TF1 TR1 TF0 TR0 IE1 IT1 IE0 IT0 00H 00000000

TH0 Timer 0 High 8CH 00H 00000000

TH1 Timer 1 High 8DH 00H 00000000

TL0 Timer 0 Low 8AH 00H 00000000

TL1 Timer 1 Low 8BH 00H 00000000

TMOD Timer 0 and 1 Mode 89H T1GATE T1C/T T1M1 T1M0 T0GATE T0C/T T0M1 T0M0 00H 00000000

TRIM# Internal Oscillator Trim Register 96H - ENCLK TRIM.5 TRIM.4 TRIM.3 TRIM.2 TRIM.1 TRIM.0 Notes 4,5

WDCON# Watchdog Control Register A7H PRE2 PRE1 PRE0 - - WDRUN WDTOF WDCLK Notes 3,5

WDL# Watchdog Load C1H FFH 11111111

WFEED1# Watchdog Feed 1 C2H

WFEED2# Watchdog Feed 2 C3H

2003 Nov 6 16

Page 17

Philips Semiconductors

User’s Manual - Preliminary -

General Description

P89LPC920/921/922

Notes:

* SFRs are bit addressable.

# SFRs are modified from or added to the 80C51 SFRs.

- Reserved bits, must be written with 0’s.

§ BRGR1 and BRGR0 must only be written if BRGEN in BRGCON SFR is ’0’. If any of them is written if BRGEN = 1, result is unpredictable.

Unimplemented bits in SFRs (labeled ’-’ ) are X (unknown) at all times. Unless otherwise specified, ones should not be written to these bits since

they may be used for other purposes in future derivatives. The reset values shown for these bits are ’0’s although they are unknown when

read.

1. All ports are in input only (high impendance) state after power-up.

2. The RSTSRC register reflects the cause of the LPC920/921/922 reset. Upon a power-up reset, all reset source flags are cleared except POF

and BOF - the power-on reset value is xx110000.

3. After reset, the value is 111001x1, i.e., PRE2-PRE0 are all 1, WDRUN=1 and WDCLK=1. WDTOF bit is 1 after watchdog reset and is 0 after

power-on reset. Other resets will not affect WDTOF.

4. On power-on reset, the TRIM SFR is initialized with a factory preprogrammed value. Other resets will not cause initialization of the TRIM

register.

5. The only reset source that affects these SFRs is power-on reset.

2003 Nov 6 17

Page 18

Philips Semiconductors

User’s Manual - Preliminary -

General Description

Memory organization

The P89LPC920/921/922 memory map is shown in Figure 1-1.

FF00h

FFEFh

1FFFh

1E00h

1C00h

1BFFh

1800h

17FFh

1400h

13FFh

1000h

0FFFh

0C00h

0BFFh

0800h

07FFh

0400h

03FFh

0000h

IAP entry-points

ISP CODE (512B)*

Sector 7

Sector 6

Sector 5

Sector 4

Sector 3

Sector 2

Sector 1

Sector 0

Read- protected

IAP calls only

IAP routines

entry points for:

- 51 ASM. code

C code

-

ISP

serial loader

-

UART (auto-baud)

-I2C, SPI etc. *

Flexible choices:

- as supplied (UART)

- Phil ips libraries

-user-defined

Note: ISP code is located at the end of Sector

1 on the LPC920, at the end of Sector 4 on the

LPC92 1, AND AT THE END OF Sector 7 on

the LPC922.

P89LPC920/921/922

FFEFh

FF1Fh

FF00h

1FFFh

1E00h

Special Function

Regi sters

(directly addressable)

entry points

I DATA (incl. DATA)

128 Bytes On-Chip

Data Memory (stack

and indirect addr. )

DATA

128 Bytes On-Chip

Data Memory (stack,

direct and indir. addr.)

4 Reg. Banks R0-R7

Data Memory

(DATA, IDATA)

*

Figure 1-1: P89LPC920/921/922 memory map

The various P89LPC920/921/922 memory spaces are as follows:

DATA 128 bytes of internal data memory space (00h..7Fh) accessed via direct or indirect addressing, using instructions

other than MOVX and MOVC. All or part of the Stack may be in this area.

IDATA Indirect Data. 256 bytes of internal data memory space (00h:FFh) accessed via indirect addressing using

instructions other than MOVX and MOVC. All or part of the Stack may be in this area. This area includes the DATA

area and the 128 bytes immediately above it.

SFR Special Function Registers. Selected CPU registers and peripheral control and status registers, accessible only via

direct addressing.

CODE 64 KB of Code memory space, accessed as part of program execution and via the MOVC instruction. The

P89LPC920/921/922 has 2 KB/ 4 KB/ 8 KB of on-chip Code memory.).

2003 Nov 6 18

Page 19

Philips Semiconductors

User’s Manual - Preliminary -

General Description

P89LPC920/921/922

DATA RAM ARRANGEMENT

The 256 bytes of on-chip RAM is organized as follows:

Type Data RAM Size (Bytes)

DATA Memory that can be addressed directly and indirectly 128

IDATA Memory that can be addressed indirectly (includes DATA) 256

Table 1-1: On-chip data memory usage.

2003 Nov 6 19

Page 20

Philips Semiconductors

User’s Manual - Preliminary -

General Description

P89LPC920/921/922

2003 Nov 6 20

Page 21

Philips Semiconductors

User’s Manual - Preliminary -

CLOCKS

P89LPC920/921/922

2. CLOCKS

Enhanced CPU

The P89LPC920/921/922 uses an enhanced 80C51 CPU which runs at 6 times the speed of standard 80C51 devices. A machine

cycle consists of two CPU clock cycles, and most instructions execute in one or two machine cycles.

Clocks

Clock definitions

The P89LPC920/921/922 device has several internal clocks as defined below:

• OSCCLK - Input to the DIVM clock divider. OSCCLK is selected from one of four clock sources (see Figure 2-3) and can also

be optionally divided to a slower frequency (see section "CPU Clock (CCLK) modification: DIVM register").

Note: f

• CCLK - CPU clock; output of the DIVM clock divider. There are two CCLK cycles per machine cycle, and most instructions are

executed in one to two machine cycles (two or four CCLK cycles).

• RCCLK - The internal 7.373 MHz RC oscillator output.

• PCLK - Clock for the various peripheral devices and is CCLK/2.

is defined as the OSCCLK frequency.

OSC

Oscillator clock (OSCCLK)

The P89LPC920/921/922 provides several user-selectable oscillator options. This allows optimization for a range of needs from

high precision to lowest possible cost. These options are configured when the FLASH is programmed and include an on-chip

watchdog oscillator, an on-chip RC oscillator, an oscillator using an external crystal, or an external clock source. The crystal

oscillator can be optimized for low, medium, or high frequency crystals covering a range from 20 kHz to 12 MHz.

Low speed oscillator option

This option supports an external crystal in the range of 20 kHz to 100 kHz. Ceramic resonators are also supported in this

configuration.

Medium speed oscillator option

This option supports an external crystal in the range of 100 kHz to 4 MHz. Ceramic resonators are also supported in this

configuration.

High speed oscillator option

This option supports an external crystal in the range of 4 MHz to 12 MHz. Ceramic resonators are also supported in this

configuration.

Clock output

The P89LPC920/921/922 supports a user-selectable clock output function on the XTAL2 / CLKOUT pin when the crystal

oscillator is not being used. This condition occurs if a different clock source has been selected (on-chip RC oscillator,watchdog

oscillator, external clock input on X1) and if the Real-time Clock is not using the crystal oscillator as its clock source. This allows

external devices to synchronize to the P89LPC920/921/922. This output is enabled by the ENCLK bit in the TRIM register

The frequency of this clock output is 1/2 that of the CCLK. If the clock output is not needed in Idle mode, it may be turned off prior

to entering Idle, saving additional power. Note: on reset, the TRIM SFR is initialized with a factory preprogrammed value.

2003 Nov 6 21

Page 22

Philips Semiconductors

User’s Manual - Preliminary -

CLOCKS

P89LPC920/921/922

Therefore when setting or clearing the ENCLK bit, the user should retain the contents of bits 5:0 of the TRIM register. This can

be done by reading the contents of the TRIM register (into the ACC for example), modifying bit 6, and writing this result back into

the TRIM register. Alternatively,the “ANL direct” or “ORL direct” instructions can be used to clear or set bit 6 of the TRIM register.

Quartz crystal or

ceramic resonator

The oscillator must be configured in

one of the following modes:

- Low Frequency Crystal

- Medium Frequency Crystal

- High Frequency Crystal

*

* A series resistor may be required to limit

crystal drive levels. This is especially

important for low frequency crystals (see

text).

Figure 2-1: Using the crystal oscillator

On-chip RC oscillator option

P89LPC920/921/922

XTAL1

XTAL2

The P89LPC920/921/922 has a 6-bit TRIM register that can be used to tune the frequency of the RC oscillator. During reset, the

TRIM value is initialized to a factory pre-programmed value to adjust the oscillator frequency to 7.373 MHz, ±1%. (Note: the initial

value is better than 1%; please refer to the datasheet for behavior over temperature). End user applications can write to the TRIM

register to adjust the on-chip RC oscillator to other frequencies. Increasing the TRIM value will decrease the oscillator frequency.

TRIM

Address: 96h

Not bit addressable

Reset Source(s): Power-up only

Reset Value: On power-up reset, ENCLK = 0, and TRIM.5-0 are loaded with the factory programmed value.

BIT SYMBOL FUNCTION

TRIM.7 - Reserved.

TRIM.6 ENCLK When ENCLK =1, CCLK/ 2 is output on the XTAL2 pin (P3.0) provided that the crystal

TRIM.5-0 Trim value.

Note: on reset, the TRIM SFR is initialized with a factory preprogrammed value. When setting or clearing the ENCLK bit,

the user should retain the contents of bits 5:0 of the TRIM register. This can be done by reading the contents of the TRIM

register (into the ACC for example), modifying bit 6, and writing this result back into the TRIM register. Alternatively, the

“ANL direct” or “ORL direct” instructions can be used to clear or set bit 6 of the TRIM register.

76543210

- ENCLK TRIM.5 TRIM.4 TRIM.3 TRIM.2 TRIM.1 TRIM.0

oscillator is not being used. When ENCLK=0, no clock output is enabled.

Figure 2-2: On-chip RC oscillator TRIM register

Watchdog oscillator option

The watchdog has a separate oscillator which has a frequency of 400 kHz. This oscillator can be used to save power when a

high clock frequency is not needed.

2003 Nov 6 22

Page 23

Philips Semiconductors

User’s Manual - Preliminary -

CLOCKS

P89LPC920/921/922

External clock input option

In this configuration, the processor clock is derived from an external source driving the XTAL1 / P3.1 pin. The rate may be from

0 Hz up to 12 MHz. The XTAL2 / P3.0 pin may be used as a standard port pin or a clock output.

RTCS1:0

XTAL1

XTAL2

RC Oscillator

(7.3728MHz)

Watchdog

Oscillator

High freq.

Med freq.

Low freq.

FOSC2:0

OSC

CLK

DIVM

CPU

Clock

CCLK

RTC

CPU

/2

WDT

PCLK

(400KHz)

Baud Rate

Generator

UART

Figure 2-3: Block diagram of oscillator control

Timer 0 & 1

Peripheral Clock

I2C

Oscillator Clock (OSCCLK) wakeup delay

The P89LPC920/921/922 has an internal wakeup timer that delays the clock until it stabilizes depending to the clock source used.

If the clock source is any of the three crystal selections, the delay is 992 OSCCLK cycles plus 60-100µs. If the clock source is

either the internal RC oscillator or the Watchdog oscillator, the delay is 224 OSCCLK cycles plus 60-100µs.

CPU Clock (CCLK) modification: DIVM register

The OSCCLK frequency can be divided down, by an integer, up to 510 times by configuring a dividing register, DIVM, to provide

CCLK. This produces the CCLK frequency using the following formula:

CCLK frequency = f

Where: f

Since N ranges from 0 to 255, the CCLK frequency can be in the range of f

This feature makes it possible to temporarily run the CPU at a lower rate, reducing power consumption. By dividing the clock, the

CPU can retain the ability to respond to events other than those that can cause interrupts (i.e. events that allow exiting the Idle

mode) by executing its normal program at a lower rate. This can often result in lower power consumption than in Idle mode. This

is the frequency of OSCCLK

OSC

N is the value of DIVM.

OSC

/ (2N)

OSC

to f

/510. (for N =0, CCLK = f

OSC

OSC

) .

2003 Nov 6 23

Page 24

Philips Semiconductors

User’s Manual - Preliminary -

CLOCKS

P89LPC920/921/922

can allow bypassing the oscillator start-up time in cases where Power down mode would otherwise be used. The value of DIVM

may be changed by the program at any time without interrupting code execution.

Low power select

The P89LPC920/921/922 is designed to run at 12 MHz (CCLK) maximum. However, if CCLK is 8 MHz or slower, the CLKLP

SFR bit (AUXR1.7) can be set to a ‘1’ to lower the power consumption further. On any reset, CLKLP is ‘0’ allowing highest

performance. This bit can then be set in software if CCLK is running at 8 MHz or slower.

2003 Nov 6 24

Page 25

Philips Semiconductors

User’s Manual - Preliminary -

INTERRUPTS

P89LPC920/921/922

3. INTERRUPTS

The P89LPC920/921/922 uses a four priority level interrupt structure. This allows great flexibility in controlling the handling of the

P89LPC920/921/922’s 12 interrupt sources.

Each interrupt source can be individually enabled or disabled by setting or clearing a bit in the interrupt enable registers IEN0 or

IEN1. The IEN0 register also contains a global enable bit, EA, which enables all interrupts.

Each interrupt source can be individually programmed to one of four priority levels by setting or clearing bits in the interrupt priority

registers IP0, IP0H, IP1, and IP1H. An interrupt service routine in progress can be interrupted by a higher priority interrupt, but

not by another interrupt of the same or lower priority. The highest priority interrupt service cannot be interrupted by any other

interrupt source. If two requests of different priority levels are received simultaneously, the request of higher priority level is

serviced.

If requests of the same priority level are pending at the start of an instruction cycle, an internal polling sequence determines which

request is serviced. This is called the arbitration ranking. Note that the arbitration ranking is only used for pending requests of

the same priority level.

Table summarizes the interrupt sources, flag bits, vector addresses, enable bits, priority bits, arbitration ranking, and whether

each interrupt may wake up the CPU from a Power down mode.

Interrupt priority structure

There are four SFRs associated with the four interrupt levels: IP0, IP0H, IP1, IP1H. Every interrupt has two bits in IPx and IPxH

(x = 0,1) and can therefore be assigned to one of four levels, as shown in Table .

Table 3-1: Interrupt priority level

Priority bits

IPxH IPx

0 0 Level 0 (lowest priority)

Interrupt priority level

0 1 Level 1

1 0 Level 2

1 1 Level 3 (highest priority)

2003 Nov 6 25

Page 26

Philips Semiconductors

User’s Manual - Preliminary -

INTERRUPTS

Table 3-2: Summary of interrupts

Description

External Interrupt 0 IE0 0003h EX0 (IEN0.0) IP0H.0, IP0.0 1 (highest) Yes

Timer 0 Interrupt TF0 000Bh ET0 (IEN0.1) IP0H.1, IP0.1 4 No

External Interrupt 1 IE1 0013h EX1 (IEN0.2) IP0H.2, IP0.2 6 Yes

Timer 1 Interrupt TF1 001Bh ET1 (IEN0.3) IP0H.3, IP0.3 8 No

Serial Port Tx and Rx

Serial Port Rx

Brownout Detect BOF 002Bh EBO (IEN0.5) IP0H.5, IP0.5 2 Yes

Watchdog Timer/Realtime Clock

2

C Interrupt SI 0033h EI2C (IEN1.0) IP1H.0, IP1.0 5 No

I

KBI Interrupt KBIF 003Bh EKBI (IEN1.1) IP1H.1, IP1.1 7 Yes

Comparators 1/2 interrupt CMF1/CMF2 0043h EC (IEN1.2) IP1H.2, IP1.2 9 Yes

Serial Port Tx

1. SSTAT.5 = 0 selects combined Serial Port (UART) Tx and Rx interrupt; SSTAT.5 = 1 selects Serial Port Rx interrupt only

(Tx interrupt will be different, see Note 3 below).

2. This interrupt is used as Serial Port (UART) Tx interrupt if and only if SSTAT.5 = 1, and is disabled otherwise.

3. If SSTAT.0 = 1, the following Serial Port additional flag bits can cause this interrupt: FE, BR, OE

2

1,3

1,3

Interrupt

flag bit(s)

TI & RI

RI

WDOVF/

RTCF

TI 006Bh EST (IEN1.6) P1H.6, IP1.6 10 No

Vector

address

0023h

0053h

Interrupt

enable bit(s)

ES/ESR

(IEN0.4)

EWDRT

(IEN0.6)

Interrupt

priority

IP0H.4, IP0.4 11 No

IP0H.6, IP0.6 3 Yes

P89LPC920/921/922

Arbitration

ranking

Power down

wakeup

The P89LPC920/921/922 has two external interrupt inputs in addition to the Keypad Interrupt function. The two interrupt inputs

are identical to those present on the standard 80C51 microcontrollers.

These external interrupts can be programmed to be level-triggered or edge-triggered by clearing or setting bit IT1 or IT0 in

Register TCON. If ITn = 0, external interrupt n is triggered by a low level detected at the INTn

is edge triggered. In this mode if consecutive samples of the INTn pin show a high level in one cycle and a low level in the next

cycle, interrupt request flag IEn in TCON is set, causing an interrupt request.

Since the external interrupt pins are sampled once each machine cycle, an input high or low level should be held for at least one

machine cycle to ensure proper sampling. If the external interrupt is edge-triggered, the external source has to hold the request

pin high for at least one machine cycle, and then hold it low for at least one machine cycle. This is to ensure that the transition is

detected and that interrupt request flag IEn is set. IEn is automatically cleared by the CPU when the service routine is called.

If the external interrupt is level-triggered, the external source must hold the request active until the requested interrupt is

generated. If the external interrupt is still asserted when the interrupt service routine is completed, another interrupt will be

generated. It is not necessary to clear the interrupt flag IEn when the interrupt is level sensitive, it simply tracks the input pin level.

If an external interrupt is enabled when the P89LPC920/921/922 is put into Power down or Idle mode, the interrupt occurance

will cause the processor to wake up and resume operation. Refer to the section on Power Reduction Modes for details.

pin. If ITn = 1, external interrupt n

External Interrupt pin glitch suppression

Most of the P89LPC920/921/922 pins have glitch suppression circuits to reject short glitches (please refer to the P89LPC920/

921/922 datasheet, AC Electrical Characteristics for glitch filter specifications) . However, pins SDA/INT0

do not have the glitch suppression circuits. Therefore, INT1

has glitch suppression while INT0 does not.

/P1.3 and SCL/T0/P1.2

2003 Nov 6 26

Page 27

Philips Semiconductors

User’s Manual - Preliminary -

INTERRUPTS

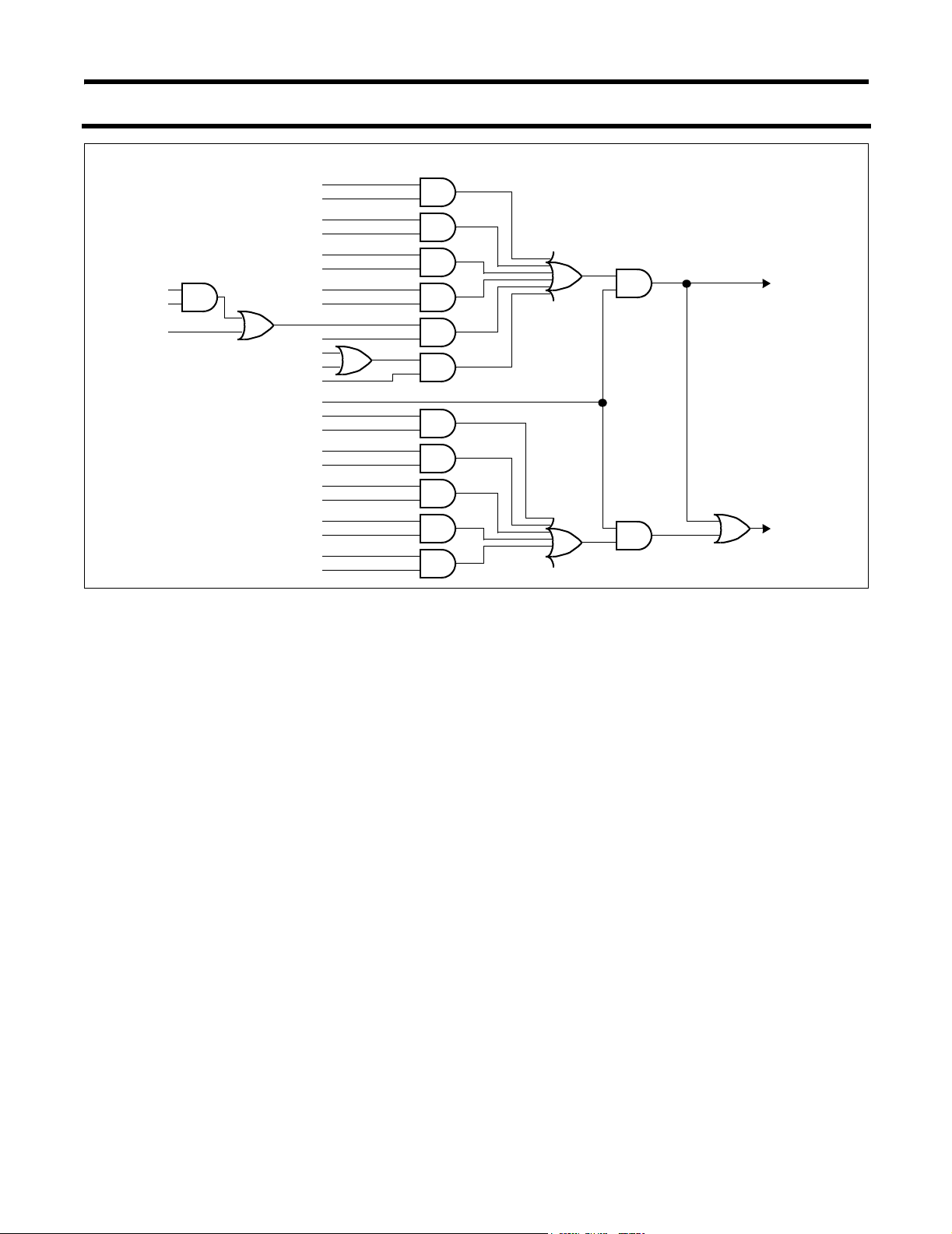

RTCF

ERTC

(RTCCON.1)

WDOVF

IE0

EX0

IE1

EX1

BOPD

EBO

KBIF

EKBI

EWDRT

CMF2

CMF1

EC

EA (IE0.7)

TF0

ET0

TF1

ET1

TI & RI/RI

ES/ESR

EST

EI2C

P89LPC920/921/922

Wakeup (if in

Power down)

TI

SI

Interrupt to CPU

Figure 3-1: Interrupt sources, interrupt enables, and power down wake-up sources

2003 Nov 6 27

Page 28

Philips Semiconductors

User’s Manual - Preliminary -

INTERRUPTS

P89LPC920/921/922

2003 Nov 6 28

Page 29

Philips Semiconductors

User’s Manual - Preliminary -

P89LPC920/921/922

I/O PORTS

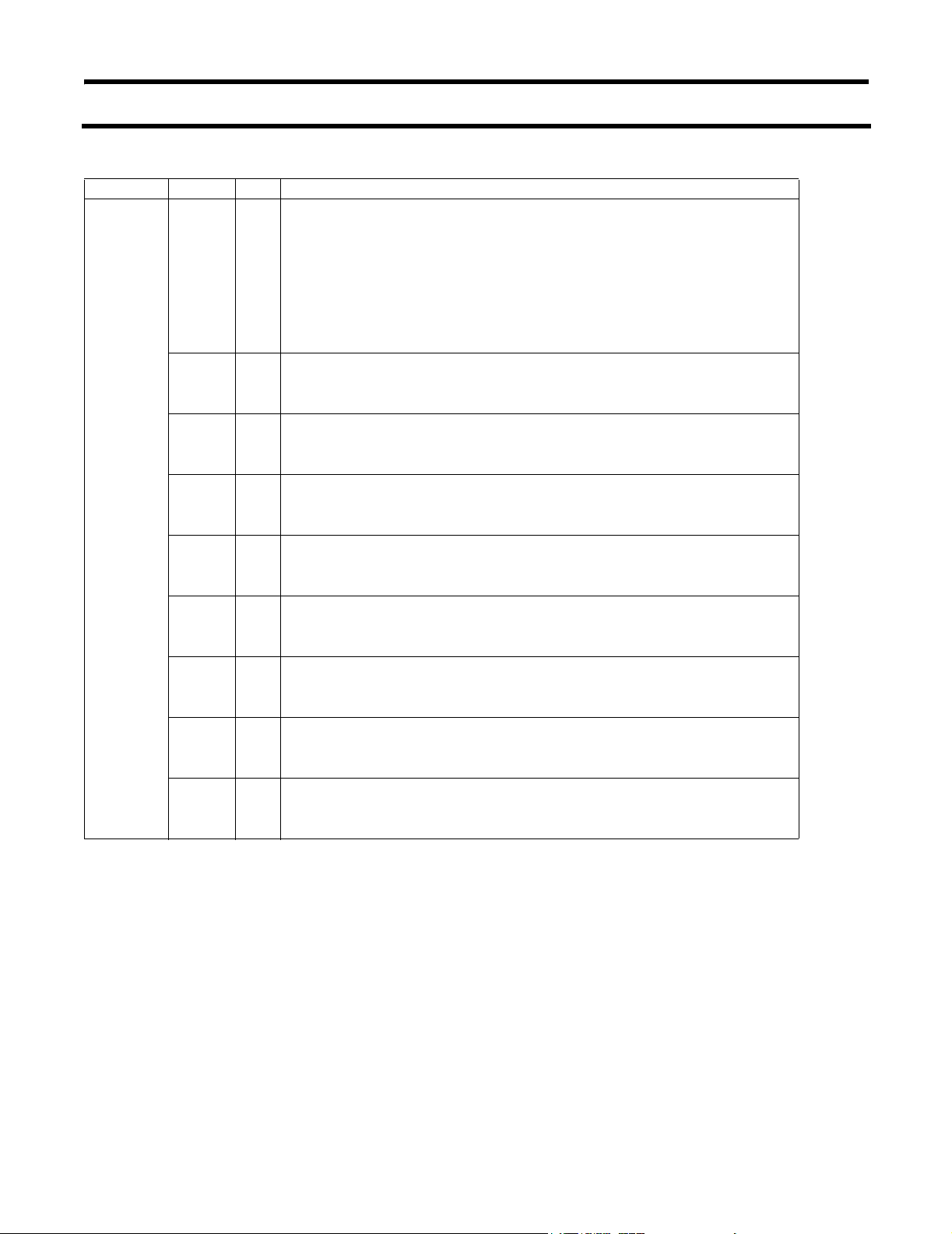

4. I/O PORTS

The P89LPC920/921/922 has 3 I/O ports: Port 0, Port 1, and Port 3. Ports 0 and 1 are 8-bit ports and Port 3 is a 2-bit port. The

exact number of I/O pins available depends upon the clock and reset options chosen (see Table 4-1)

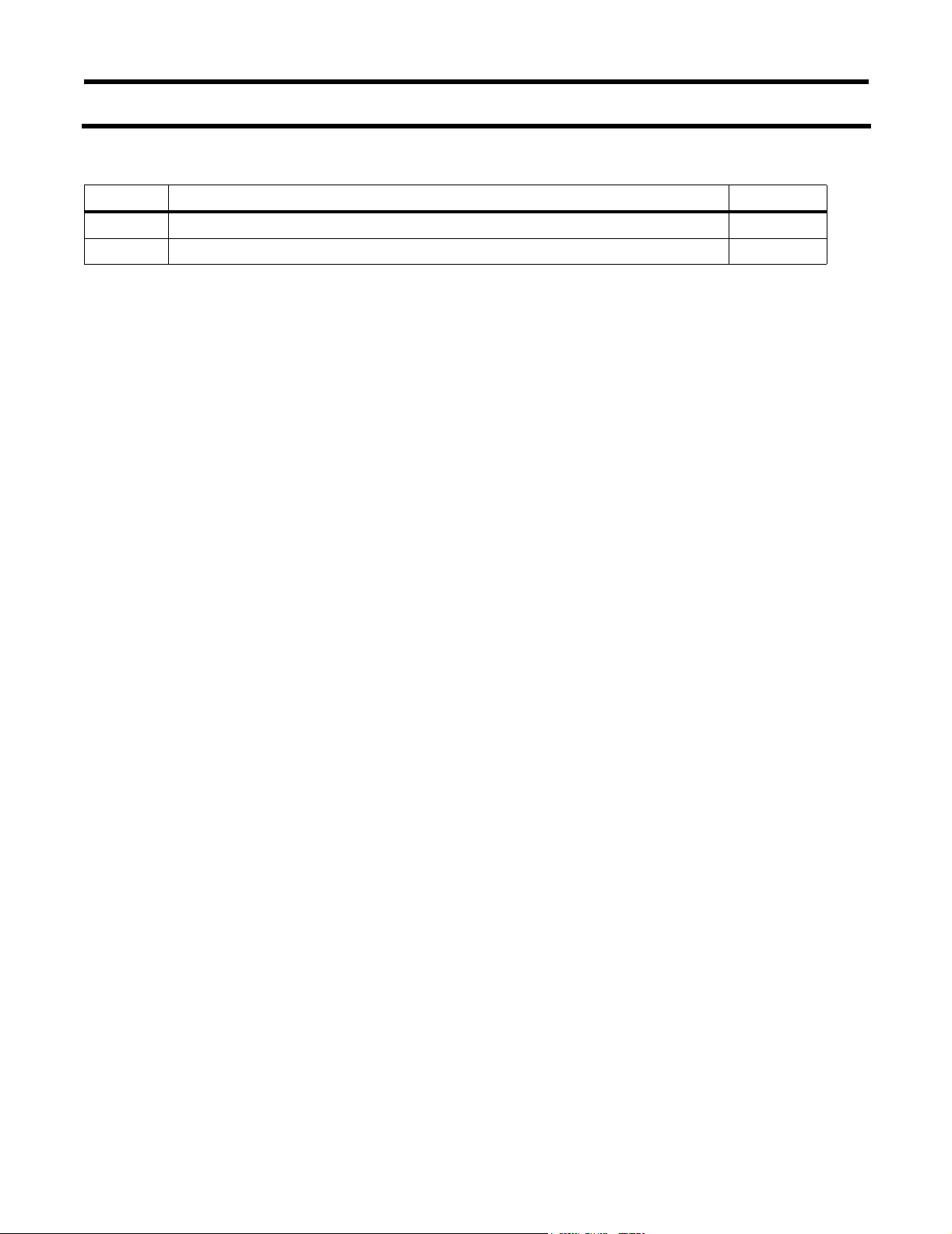

Table 4-1: .Number of I/O pins available

Clock source Reset option Number of I/O pins

On-chip oscillator or watchdog

oscillator

External clock input

No external reset (except during power-up) 18

External RST

No external reset (except during power-up) 17

External RST

pin supported 17

pin supported 16

Low/medium/high speed oscillator

(external crystal or resonator)

No external reset (except during power-up) 16

External RST

pin supported 15

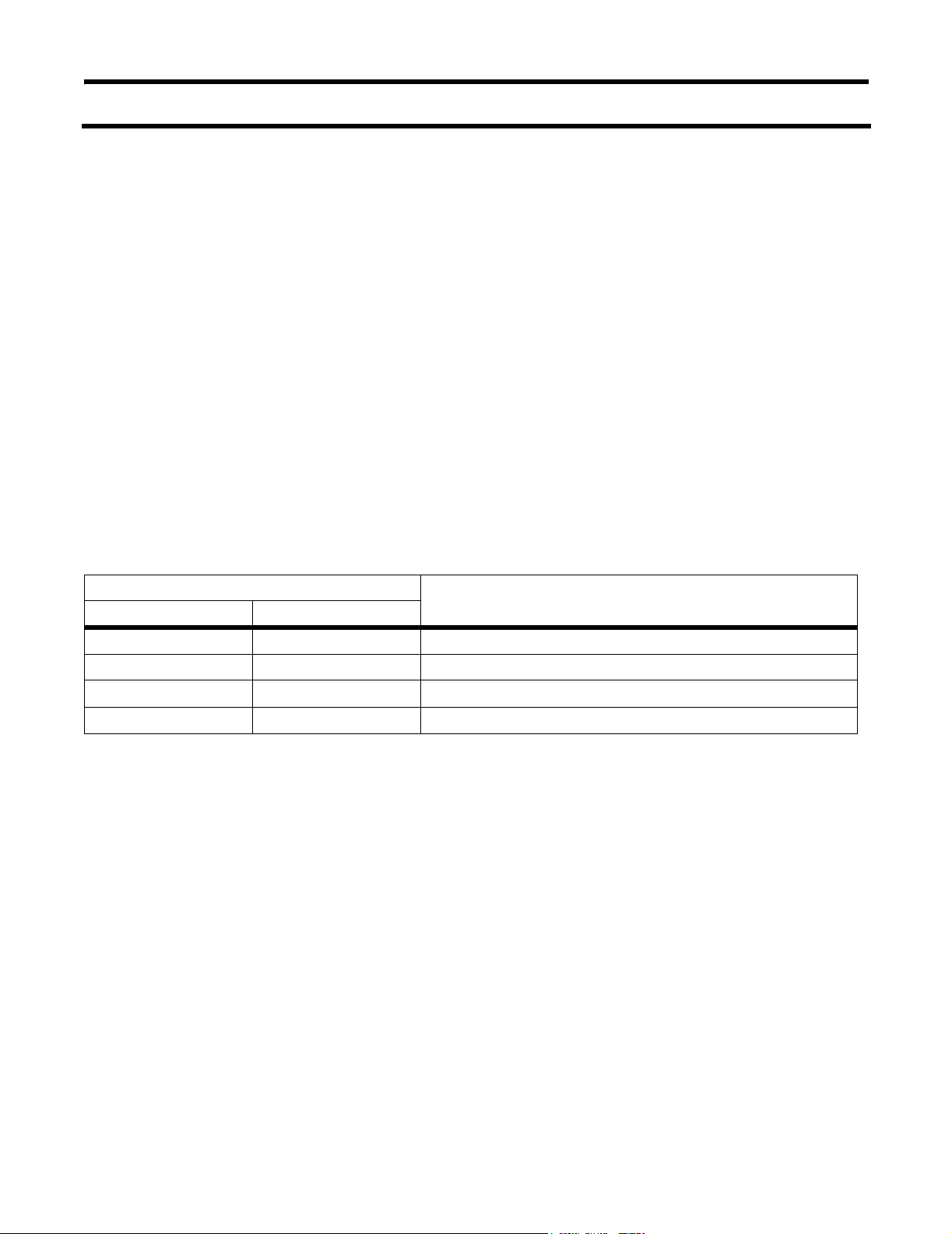

Port configurations

All but three I/O port pins on the P89LPC920/921/922 may be configured by software to one of four types on a pin-by-pin basis,

as shown in Table 4-3. These are: quasi-bidirectional (standard 80C51 port outputs), push-pull, open drain, and input-only. Two

configuration registers for each port select the output type for each port pin.

P1.5 (RST) can only be an input and cannot be configured.

P1.2 (SCL/T0) and P1.3 (SDA/INT0) may only be configured to be either input-only or open drain.

Table 4-2: Port output configuration settings

PxM1.y PxM2.y Port output mode

0 0 Quasi-bidirectional

0 1 Push-Pull

1 0 Input Only (High Impedance)

11 Open Drain

Quasi-bidirectional output configuration

Quasi-bidirectional outputs can be used both as an input and output without the need to reconfigure the port. This is possible

because when the port outputs a logic high, it is weakly driven, allowing an external device to pull the pin low. When the pin is

driven low, it is driven strongly and able to sink a large current. There are three pull-up transistors in the quasi-bidirectional output

that serve different purposes.

One of these pull-ups, called the “very weak” pull-up, is turned on whenever the port latch for the pin contains a logic 1. This very

weak pull-up sources a very small current that will pull the pin high if it is left floating.

A second pull-up, called the “weak” pull-up, is turned on when the port latch for the pin contains a logic 1 and the pin itself is also

at a logic 1 level. This pull-up provides the primary source current for a quasi-bidirectional pin that is outputting a 1. If this pin is

pulled low by an external device, the weak pull-up turns off, and only the very weak pull-up remains on. In order to pull the pin

low under these conditions, the external device has to sink enough current to overpower the weak pull-up and pull the port pin

below its input threshold voltage.

2003 Nov 6 29

Page 30

Philips Semiconductors

User’s Manual - Preliminary -

P89LPC920/921/922

I/O PORTS

The third pull-up is referred to as the “strong” pull-up. This pull-up is used to speed up low-to-high transitions on a quasibidirectional port pin when the port latch changes from a logic 0 to a logic 1. When this occurs, the strong pull-up turns on for two

CPU clocks quickly pulling the port pin high .

The quasi-bidirectional port configuration is shown in Figure 4-1.

Although the P89LPC920/921/922 is a 3 V device most of the pins are 5 V-tolerant. If 5 V is applied to a pin configured in quasibidirectional mode, there will be a current flowing from the pin to VDD causing extra power consumption. Therefore, applying 5 V

to pins configured in quasi-bidirectional mode is discouraged.

A quasi-bidirectional port pin has a Schmitt-triggered input that also has a glitch suppression circuit.

(Please refer to the P89LPC920/921/922 datasheet, AC Electrical Characteristics for glitch filter specifications)

port latch data

2 CPU

clock delay

V

DD

strong

V

DD

very

weak

V

DD

weak

port

pin

input data

Figure 4-1: Quasi-bidirectional output

glitch rejection

Open drain output configuration

The open drain output configuration turns off all pull-ups and only drives the pulldown transistor of the port pin when the port latch

contains a logic 0. To be used as a logic output, a port configured in this manner must have an external pull-up, typically a resistor

tied to V

The open drain port configuration is shown in Figure 4-2.

An open drain port pin has a Schmitt-triggered input that also has a glitch suppression circuit.

Please refer to the P89LPC920/921/922 datasheet, AC Electrical Characteristics for glitch filter specifications).

. The pulldown for this mode is the same as for the quasi-bidirectional mode.

DD

port latch data

input data

glitch rejection

port

pin

Figure 4-2: Open drain output

2003 Nov 6 30

Page 31

Philips Semiconductors

User’s Manual - Preliminary -

P89LPC920/921/922

I/O PORTS

Input-only configuration

The input port configuration is shown in Figure 4-3. It is a Schmitt-triggered input that also has a glitch suppression circuit.

(Please refer to the P89LPC920/921/922 datasheet, AC Electrical Characteristics for glitch filter specifications)

input data

glitch rejection

Figure 4-3: Input -only

port

pin

Push-pull output configuration

The push-pull output configuration has the same pulldown structure as both the open drain and the quasi-bidirectional output

modes, but provides a continuous strong pull-up when the port latch contains a logic 1. The push-pull mode may be used when

more source current is needed from a port output.

The push-pull port configuration is shown in Figure 4-4.

A push-pull port pin has a Schmitt-triggered input that also has a glitch suppression circuit.

(Please refer to the P89LPC920/921/922 datasheet, AC Electrical Characteristics for glitch filter specifications)

V

DD

strong

port latch data

port

pin

input data

Figure 4-4: Push-pull output

glitch rejection

Port 0 analog functions

The P89LPC920/921/922 incorporates two Analog Comparators. In order to give the best analog performance and minimize

power consumption, pins that are being used for analog functions must have both the digital outputs and digital inputs disabled.

Digital outputs are disabled by putting the port pins into the input-only mode as described in the Port Configurations section (see

Table 4-3).

Digital inputs on Port 0 may be disabled through the use of the PT0AD register. Bits 1 through 5 in this register correspond to

pins P0.1 through P0.5 of Port 0, respectively. Setting the corresponding bit in PT0AD disables that pin’s digital input. Port bits

that have their digital inputs disabled will be read as 0 by any instruction that accesses the port.

On any reset, PT0AD bits 1 through 5 default to ‘0’s to enable the digital functions.

2003 Nov 6 31

Page 32

Philips Semiconductors

I/O PORTS

Table 4-3: Port output configuration

Port pin

P0.0 P0M1.0 P0M2.0 KBI0,CMP2

P0.1 P0M1.1 P0M2.1 KBI1,CIN2B

P0.2 P0M1.2 P0M2.2 KBI2,CIN2A

P0.3 P0M1.3 P0M2.3 KBI3,CIN1B

P0.4 P0M1.4 P0M2.4 KBI4,CIN1A

P0.5 P0M1.5 P0M2.5 KBI5,CMPREF

P0.6 P0M1.6 P0M2.6 KBI6,CMP1

P0.7 P0M1.7 P0M2.7 KBI7,T1

P1.0 P1M1.0 P1M2.0 TxD

P1.1 P1M1.1 P1M2.1 RxD

P1.2 P1M1.2 P1M2.2 T0,SCL input-only or open-drain

P1.3 P1M1.3 P1M2.3 INT0

P1.4 P1M1.4 P1M2.4 INT1

P1.5 not configurable RST

P1.6 P1M1.6 P1M2.6

P1.7 P1M1.7 P1M2.7

P3.0 P3M1.0 P3M2.0 XTAL2,CLKOUT

P3.1 P3M1.1 P3M2.1 XTAL1

Configuration SFR bits

PxM1.y PxM2.y

Alternate usage Notes

Refer to section "Port 0 analog functions" for usage as

analog inputs (CIN2B, CIN2A, CIN1B, CIN1A and

CMPREF)

,SDA input-only or open-drain

Input only. Usage as general purpose input or RST is

determined by User Configuration Bit RPD (UCFG1.6).

Always a reset input during a power-on sequence.

User’s Manual - Preliminary -

P89LPC920/921/922

Additional port features

After power-up, all pins are in Input-Only mode. Please note that this is different from the LPC76x series of devices.

• After power-up, all I/O pins except P1.5, may be configured by software.

• Pin P1.5 is input only. Pins P1.2 and P1.3 are configurable for either input-only or open drain.

Every output on the P89LPC920/921/922 has been designed to sink typical LED drive current. However, there is a maximum

total output current for all ports which must not be exceeded. Please refer to the P89LPC920/921/922 Datasheet for detailed

specifications.

All ports pins that can function as an output have slew rate controlled outputs to limit noise generated by quickly switching output

signals. The slew rate is factory-set to approximately 10 ns rise and fall times.

2003 Nov 6 32

Page 33

Philips Semiconductors

User’s Manual - Preliminary -

P89LPC920/921/922

POWER MONITORING FUNCTIONS

5. POWER MONITORING FUNCTIONS

The P89LPC920/921/922 incorporates power monitoring functions designed to prevent incorrect operation during initial poweron and power loss or reduction during operation. This is accomplished with two hardware functions: Power-on Detect and

Brownout Detect.

Brownout Detection

The Brownout Detect function determines if the power supply voltage drops below a certain level. The default operation for a

Brownout Detection is to cause a processor reset. However, it may alternatively be configured to generate an interrupt by setting

the BOI (PCON.4) bit and the EBO (IEN0.5) bit.

Enabling and disabling of Brownout Detection is done via the BOPD (PCON.5) bit, bit field PMOD1-0 (PCON.1-0) and user

configuration bit BOE (UCFG1.5). If BOE is in an unprogrammed state, brownout is disabled regardless of PMOD1-0 and BOPD.

If BOE is in a programmed state, PMOD1-0 and BOPD will be used to determine whether Brownout Detect will be disabled or

enabled. PMOD1-0 is used to select the power reduction mode. If PMOD1-0 = ‘11’, the circuitry for the Brownout Detection is

disabled for lowest power consumption. BOPD defaults to ‘0’, indicating brownout detection is enabled on power-on if BOE is

programmed.

If Brownout Detection is enabled, the operating voltage range for V

VDD falls below the Brownout trip voltage, V

If Brownout Detection is disabled, the operating voltage range for VDD is 2.4 V-3.6 V. If the P89LPC920/921/922 device is to

operate with a power supply that can be below 2.7 V, BOE should be left in the unprogrammed state so that the device can

operate at 2.4 V, otherwise continuous brownout reset may prevent the device from operating.

If Brownout Detect is enabled (BOE programmed, PMOD1-0 ≠ ‘11’, BOPD = 0), BOF (RSTSRC.5) will be set when a brownout

is detected, regardless of whether a reset or an interrupt is enabled, . BOF will stay set until it is cleared in software by writing ‘0’

to the bit. Note that if BOE is unprogrammed, BOF is meaningless. If BOE is programmed, and a initial power-on occurs, BOF

will be set in addition to the power-on flag (POF - RSTSRC.4).

For correct activation of Brownout Detect, certain V

specifications.

(see D.C. Electrical Characteristics), and is negated when VDD rises above VBO.

BO

rise and fall times must be observed. Please see the datasheet for

DD

is 2.7 V-3.6 V, and the brownout condition occurs when

DD

2003 Nov 6 33

Page 34

Philips Semiconductors

POWER MONITORING FUNCTIONS

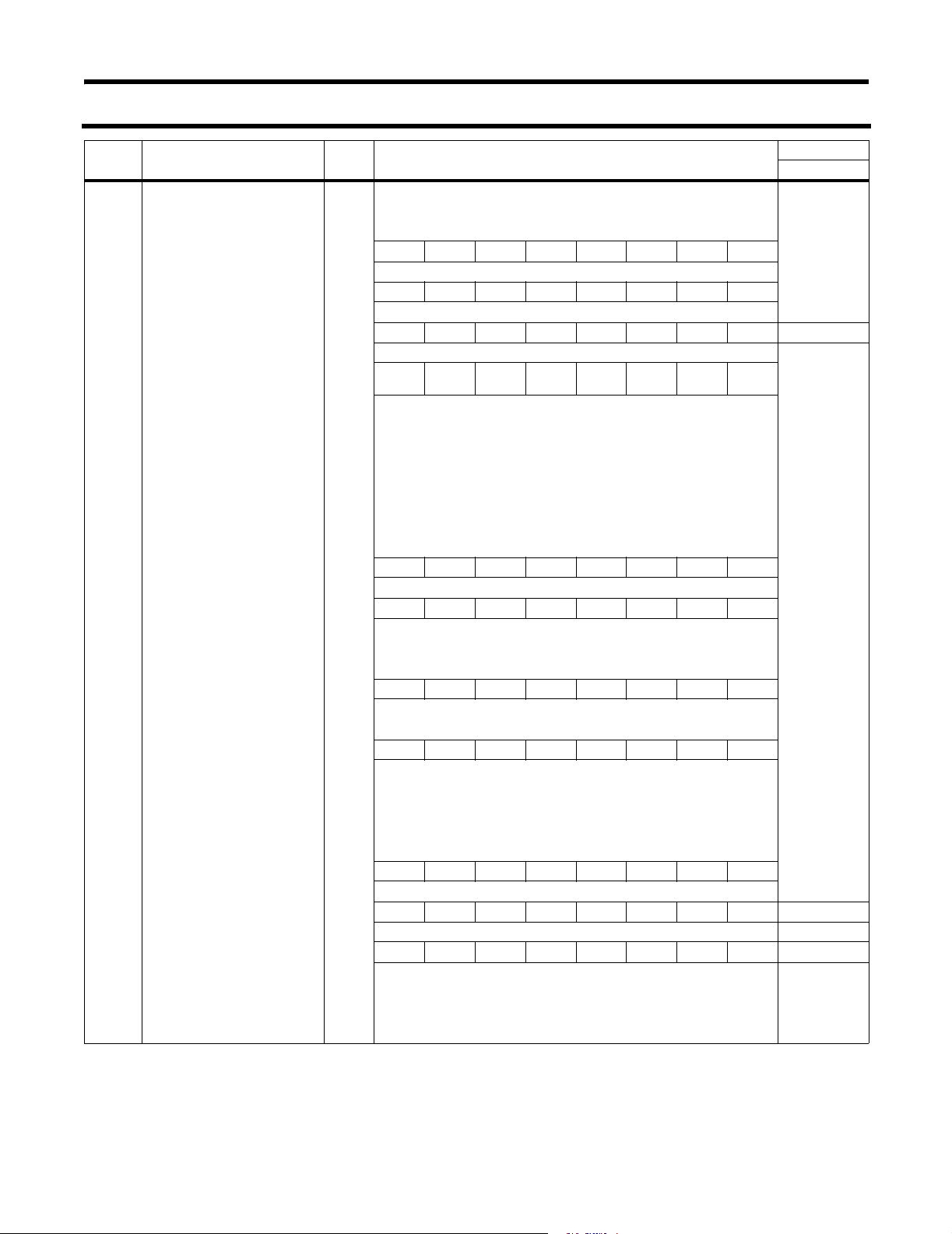

Table 5-1: Brownout options

BOE

(UCFG1.5)

0 (erased)XX XXXX

1 (programmed)

PMOD1-0

(PCON.1-0)

11

(total power

down)

≠ 11

(any mode

other than

total power

down)

BOPD

(PCON.5)

XXXX

1

(brownout

detect

powered

down)

0

(brownout

detect

active)

BOI

(PCON.4)

XXX

0

(brownout

detect

generates

reset)

1

(brownout

detect

generates

an

interrupt)

EBO

(IEN0.5)

XX

1

(enable

brownout

interrupt)

0 X Both brownout reset and interrupt disabled. V

X0

EA

(IEN0.7)

1

(global

interrupt

enable)

User’s Manual - Preliminary -

P89LPC920/921/922

Description

Brownout disabled. V

Brownout disabled. V

However, BOPD is default to ‘0’ upon power-up.

Brownout reset enabled. V

3.6 V. Upon a brownout reset, BOF (RSTSRC.5) will be

set to indicate the reset source. BOF can be cleared by

writing ‘0’ to the bit.

Brownout interrupt enabled. V

3.6 V. Upon a brownout interrupt, BOF (RSTSRC.5) will

be set. BOF can be cleared by writing ‘0’ to the bit.

operating range is 2.4 V-3.6 V. However, BOF

(RSTSRC.5) will be set when V

Detection trip point. BOF can be cleared by writing ‘0’ to

the bit.

operating range is 2.4 V-3.6 V.

DD

operating range is 2.4 V-3.6 V.

DD

operating range is 2.7 V-

DD

operating range is 2.7 V-

DD

DD

falls to the Brownout

DD

Power-on Detection

The Power-On Detect has a function similar to the Brownout Detect, but is designed to work as power initially comes up, before

the power supply voltage reaches a level where the Brownout Detect can function. The POF flag (RSTSRC.4) is set to indicate

an initial power-on condition. The POF flag will remain set until cleared by software by writing ‘0’ to the bit. Note that if BOE

(UCFG1.5) is programmed, BOF (RSTSRC.5) will be set when POF is set. If BOE is unprogrammed, BOF is meaningless.

Power reduction modes

The P89LPC920/921/922 supports three different power reduction modes as determined by SFR bits PCON.1-0 (see Table 5-2):

2003 Nov 6 34

Page 35

Philips Semiconductors

POWER MONITORING FUNCTIONS

User’s Manual - Preliminary -

P89LPC920/921/922

PMOD1

(PCON.1)

PMOD0

(PCON.0)

0 0 Normal mode (default) - no power reduction.

01

Idle mode. The Idle mode leaves peripherals running in order to allow them to activate the processor

when an interrupt is generated. Any enabled interrupt source or reset may terminate Idle mode.

Power down mode:

The Power down mode stops the oscillator in order to minimize power consumption.

The P89LPC920/921/922 exits Power down mode via any reset, or certain interrupts - external pins

/INT1, brownout Interrupt, keyboard, Real-time Clock/System Timer), watchdog, and comparator

INT0

trips. Waking up by reset is only enabled if the corresponding reset is enabled, and waking up by interrupt

is only enabled if the corresponding interrupt is enabled and the EA SFR bit (IEN0.7) is set.

In Power down mode the internal RC oscillator is disabled unless both the RC oscillator has been

selected as the system clock AND the RTC is enabled.

In Power down mode, the power supply voltage may be reduced to the RAM keep-alive voltage V

This retains the RAM contents at the point where Power down mode was entered. SFR contents are not

guaranteed after V

has been lowered to V

DD