Philips N74F85N, N74F85D Datasheet

INTEGRATED CIRCUITS

74F85

4-bit magnitude comparator

Product specification 1994 Sep 27

IC15 Data Handbook

Philips Semiconductors

Philips Semiconductors Product specification

74F854-bit magnitude comparator

FEA TURES

•High-impedance NPN base inputs for reduced loading

(20µA in High and Low states)

•Magnitude comparison of any binary words

•Serial or parallel expansion without extra gating

DESCRIPTION

The 74F85 is a 4-bit magnitude comparator that can be expanded to

almost any length. It compares two 4-bit binary, BCD, or other

monotonic codes and presents the three possible magnitude results

at the outputs. The 4-bit inputs are weighted (A0–A3) and (B0–B3)

where A3 and B3 are the most significant bits. The operation of the

74F85 is described in the Function Table, showing all possible logic

conditions. The upper part of the table describes the normal

operation under all conditions that will occur in a single device or in

a series expansion scheme. In the upper part of the table the three

outputs are mutually exclusive. In the lower part of the table, the

outputs reflect the feed-forward conditions that exist in the parallel

expansion scheme. The expansion inputs I

are the least significant bit positions. When used for series

expansion, the A>B, A=B and A<B outputs of the lease significant

word are connected to the corresponding I

of the next higher stage. Stages can be added in this manner to any

length, but a propagation delay penalty of about 15ns is added with

each additional stage. For proper operation, the expansion inputs of

the least significant word should be tied as follows: I

I

= High, and I

A=B

A<B

= Low.

A>B

A>B

, and I

, I

A=B

A=B

and I

A>B

and I

A<B

= Low,

A<B

inputs

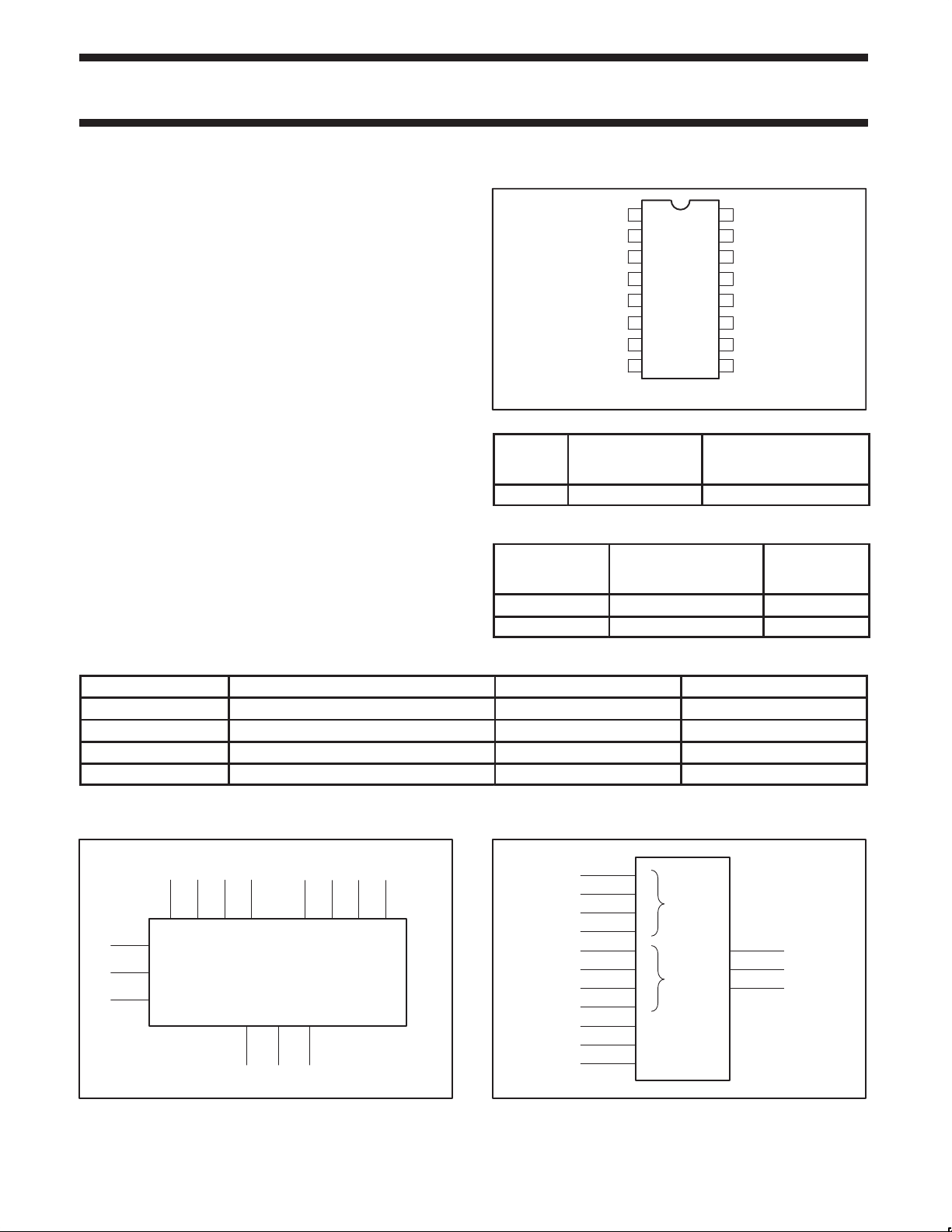

PIN CONFIGURATION

1

B3

2

I

A<B

3

I

A=B

4

I

A>B

A>B

5

A=B

6

A<B

TYPE TYPICAL

PROPAGATION

DELAY

74F85 7.0ns 40mA

16

V

CC

15

A3

14

B2

13

A2

A1

12

B1

11

107

A0

98GND B0

SF00075

TYPICAL

SUPPLY CURRENT

(TOTAL)

ORDERING INFORMATION

COMMERCIAL RANGE

DESCRIPTION

16-pin plastic DIP N74F85N SOT38-4

16-pin plastic SO N74F85D SOT162-1

VCC = 5V ±10%,

T

= 0°C to +70°C

amb

PKG DWG #

INPUT AND OUTPUT LOADING AND FAN OUT TABLE

PINS DESCRIPTION 74F (U.L.) HIGH/LOW LOAD VALUE HIGH/LOW

A0–A3 Comparing inputs 1.0/0.033 20µA/20µA

B0–B3 Comparing inputs 1.0/0.033 20µA/20µA

I

, I

A=B

, I

A>B

A<B

A<B, A=B, A>B Data outputs (active High) 50/33 1.0mA/20mA

NOTE: One (1.0) FAST unit load is defined as: 20µA in the High state and 0.6mA in the Low state.

LOGIC SYMBOL

10 12 13 15 9 11 14

A0 A1 A2 A3 B0 B1 B2 B3

2

3

4

V

CC

GND = Pin 8

= Pin 16

I

A<B

I

A=B

I

A>B

Expansion inputs (active High) 1.0/0.033 20µA/20µA

IEC/IEEE SYMBOL

COMP

0

P

3

0

3

<

=

>

P<Q

P=Q

Q

P>Q

A>B A=B A<B

567

1

SF00076

10

12

13

15

9

11

14

1

2

3

4

7

6

5

SF00077

September 27, 1994 853–0055 13903

2

Philips Semiconductors Product specification

74F854-bit magnitude comparator

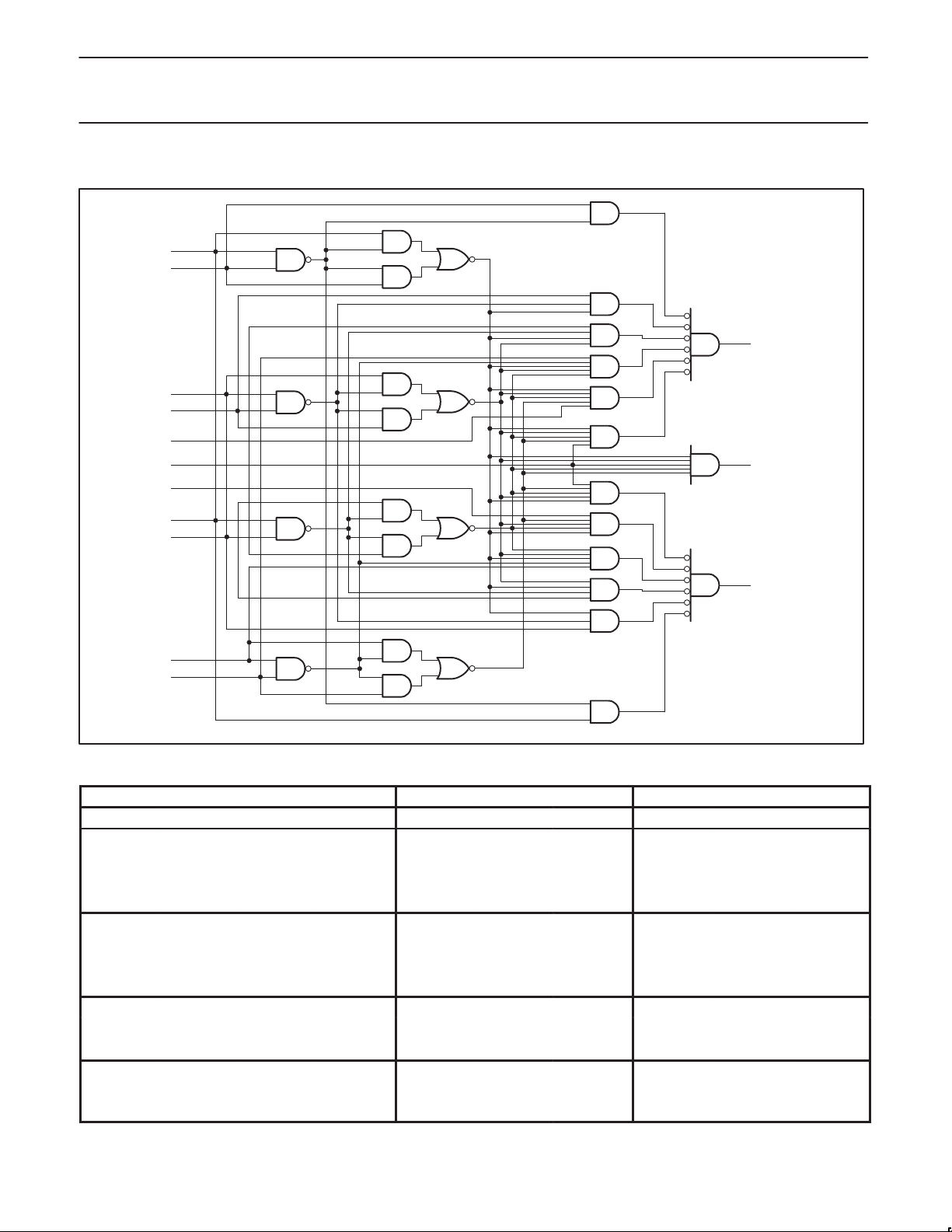

LOGIC DIAGRAM

15

A3

1

B3

5

A>B

13

A2

14

B2

2

I

A<B

I

A=B

I

A>B

A1

B1

3

4

12

11

6

A=B

7

A<B

10

A0

9

B0

V

= Pin 16

CC

GND = Pin 8

SF00078

FUNCTION TABLE

COMPARING INPUTS EXPANSION INPUTS OUTPUTS

A3,B3 A2,B2 A1,B1 A0,B0 I

A>B

A3>B3 X X X X X X H L L

A3<B3 XXXXXXLHL

A3=B3 A2>B2 X X X XXHLL

A3=B3 A2<B2 X X X XXLHL

A3=B3 A2=B2 A1>B1 X X X X H L L

A3=B3 A2=B2 A1<B1 X X XXLHL

A3=B3 A2=B2 A1=B1 A0>B0 X XXHLL

A3=B3 A2=B2 A1=B1 A0<B0 X XXLHL

A3=B3 A2=B2 A1=B1 A0=B0 H L L H L L

A3=B3 A2=B2 A1=B1 A0=B0 L HLLHL

A3=B3 A2=B2 A1=B1 A0=B0 L LHLLH

A3=B3 A2=B2 A1=B1 A0=B0 X X H L L H

A3=B3 A2=B2 A1=B1 A0=B0 H HLLLL

A3=B3 A2=B2 A1=B1 A0=B0 L L L H H L

H = High voltage level

L = Low voltage level

X = Don’t care

I

A<B

I

A=B

A>B A<B A=B

September 27, 1994

3

Loading...

Loading...