Philips N74F621N, N74F621D Datasheet

INTEGRATED CIRCUITS

74F621

Octal bus transceiver, non-inverting

(open collector)

Product specification 1996 Jan 05

IC15 Data Handbook

Philips Semiconductors Product specification

74F621Octal bus transceiver, non-inverting (open collector)

FEA TURES

•High-impedance NPN base inputs for reduced loading

(20µA in High and Low states)

•Octal bidirectional bus interface

•Open collector outputs sink 64mA

•Non-inverting

DESCRIPTION

The 74F621 is an octal transceiver featuring non-inverting open

collector bus-compatible outputs in both send and receive

directions. The outputs are capable of sinking 64mA, providing very

good capacitive drive characteristics.

This octal bus transceiver is designed for asynchronous two-way

communication between data buses. The control function

implementation allows for maximum flexibility in timing.

The device allows data transmission from the A bus to the B bus or

from the B bus to the A bus, depending upon the logic levels at the

Enable inputs (OEBA

disable the device so that the buses are effectively isolated.

The dual-enable configuration gives the 74F621 the capability to

store data by the simultaneous enabling of OEBA

output reinforces its input in this transceiver configuration. Thus,

when both control inputs are enabled and all other data sources to

the two sets of the bus lines are at high impedance, both sets of bus

lines (16 in all) will remain in their last states.

and OEAB). The Enable inputs can be used to

and OEAB. Each

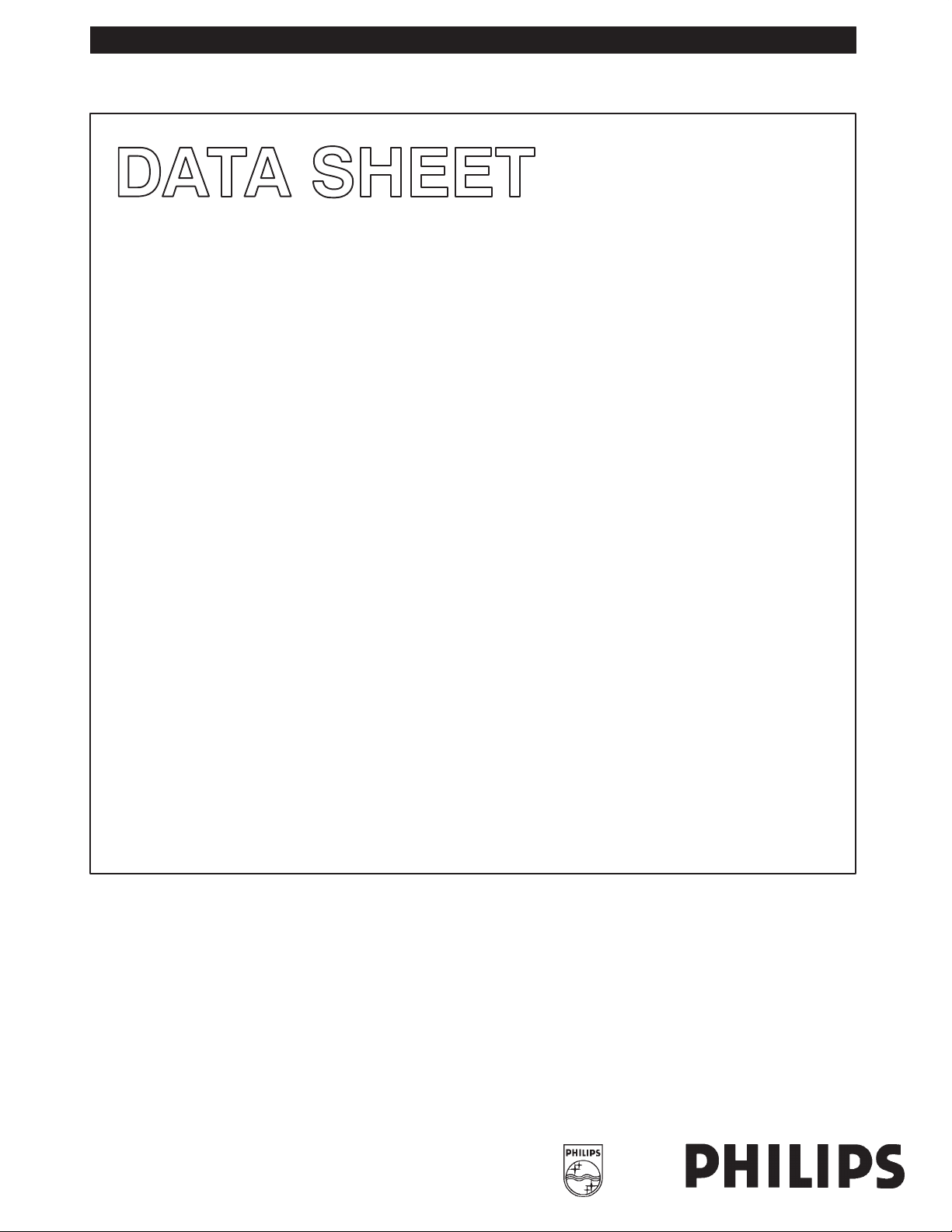

PIN CONFIGURATION

1

OEAB

2

A0

3

A1

4

A2

5

A3

6

A4

7

A5

8

A6

9

A7

10 11

GND

TYPICAL

TYPE

PROPAGATION

DELAY

74F621 8.0ns 105mA

20

V

CC

19

OEBA

B0

18

B1

17

B2

16

B3

15

B4

14

B5

13

B6

12

B7

SF01135

TYPICAL SUPPLY CURRENT

(TOTAL)

ORDERING INFORMATION

COMMERCIAL RANGE

DESCRIPTION

VCC = 5V ±10%,

T

= 0°C to +70°C

amb

20-pin plastic DIP N74F621N SOT146-1

20-pin plastic SOL N74F621D SOT163-1

PKG

DWG #

INPUT AND OUTPUT LOADING AND FAN-OUT TABLE

PINS DESCRIPTION

74F(U.L.)

HIGH/LOW

A0 - A7, B0 - B7 Data inputs 1.0/0.033 20µA/20µA

OEBA, OEAB Output Enable inputs 1.0/0.033 20µA/20µA

A0 - A7 Data outputs OC/40 OC/24mA

B0 - B7 Data outputs OC/106.7 OC/64mA

NOTE: One (1.0) FAST unit load is defined as: 20µA in the High state and 0.6mA in the Low state. OC = Open Collector.

LOAD VALUE

HIGH/LOW

1996 Jan 05 853–0380 16185

2

Philips Semiconductors Product specification

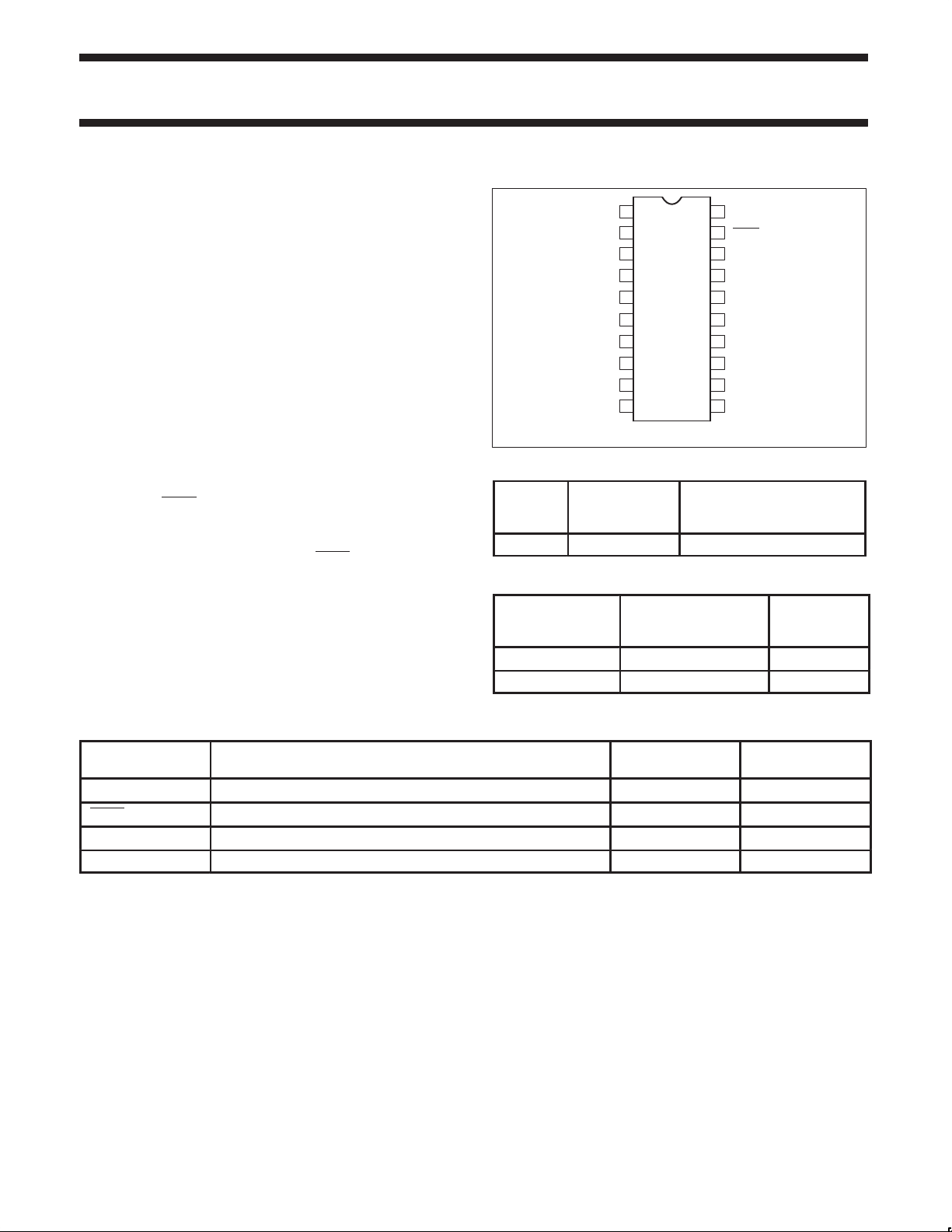

OPERATING MODES

L

H

74F621Octal bus transceiver, non-inverting (open collector)

LOGIC SYMBOL

23

A0 A1

1

OEAB

19

OEBA

B0 B1 B2 B3

18 17 16 15 14 13 12 11

VCC= Pin 20

GND = Pin 10

LOGIC DIAGRAM

19

OEBA

1

OEAB

2

A0

3

A1

4

A2

5

A3

456

A2 A3

A4 A5 A67A7

B4 B5 B6 B7

89

SF01126

18

B0

17

B1

16

B2

15

B3

LOGIC SYMBOL (IEEE/IEC)

19

1

2

3

4

5

6

7

9

EN1

EN2

1

2

8

18

17

16

15

14

13

12

11

SF01137

FUNCTION TABLE

INPUTS

OEBA OEAB

L L B data to A bus

H H A data to B bus

H L OFF

B data to A bus

A data to B bus

H = High voltage level

L = Low voltage level

X = Don’t care

OFF= High if pull-up resistor is connected to open collector output

VCC= Pin 20

GND = Pin 10

1996 Jan 05

6

A4

7

A5

8

A6

9

A7

14

13

12

11

SF01130

B4

B5

B6

B7

3

Loading...

Loading...