Philips N74F541N, N74F541D, N74F540N, N74F540D Datasheet

74F540

Octal inverter buffer (3- State)

74F541

Octal buffer (3- State)

Product specification

IC15 Data Handbook

1990 Jan 08

INTEGRATED CIRCUITS

Philips Semiconductors Product specification

74F540, 74F541Buffers

74F540 Octal Inverter Buffer (3-State)

74F541 Octal Buffer (3-State)

2

1990 Jan 08 853–0068 98494

FEA TURES

•High impedance NPN base inputs for reduced loading

(20µA in High and Low states)

•Low power, light bus loading

•Functionally similar to the 74F240 and 74F241

•Provides ideal interface and increases fan-out of MOS

microprocessors

•Efficient pinout to facilitate PC board layout

•Octal bus interface

•3-State buffer outputs sink 64mA

•15mA source current

DESCRIPTION

The 74F540 and 74F541 are octal buffers that are ideal for driving

bus lines or buffer memory address registers. The outputs are

capable of sinking 64mA and sourcing up to 15mA, producing very

good capacitive drive characteristics. The devices feature input and

outputs on opposite sides of the package to facilitate printed circuit

board layout.

TYPE

TYPICAL

PROPAGATION DELAY

TYPICAL SUPPL Y

CURRENT

(TOT AL)

74F540 3.5ns 58mA

74F541 5.5ns 55mA

ORDERING INFORMATION

DESCRIPTION

COMMERCIAL RANGE

VCC = 5V ±10%,

T

amb

= 0°C to +70°C

PKG DWG #

20-Pin Plastic DIP N74F540, N74F541N SOT146-1

20-Pin Plastic SOL N74F540D, N74F541D SOT163-1

INPUT AND OUTPUT LOADING AND FAN-OUT TABLE

PINS DESCRIPTION

74F(U.L.)

HIGH/LOW

LOAD VALUE

HIGH/LOW

I0–I7 Data inputs 1.0/0.033 20µA/20µA

OE0, OE1 3-State output enable inputs (active Low) 1.0/0.033 20µA/20µA

Y0 - Y7 Data outputs (74F541) 750/106.7 15mA/64mA

Y0 - Y7 Data outputs (74F540) 750/106.7 15mA/64mA

NOTE: One (1.0) FAST Unit Load is defined as: 20µA in the High state and 0.6mA in the Low state.

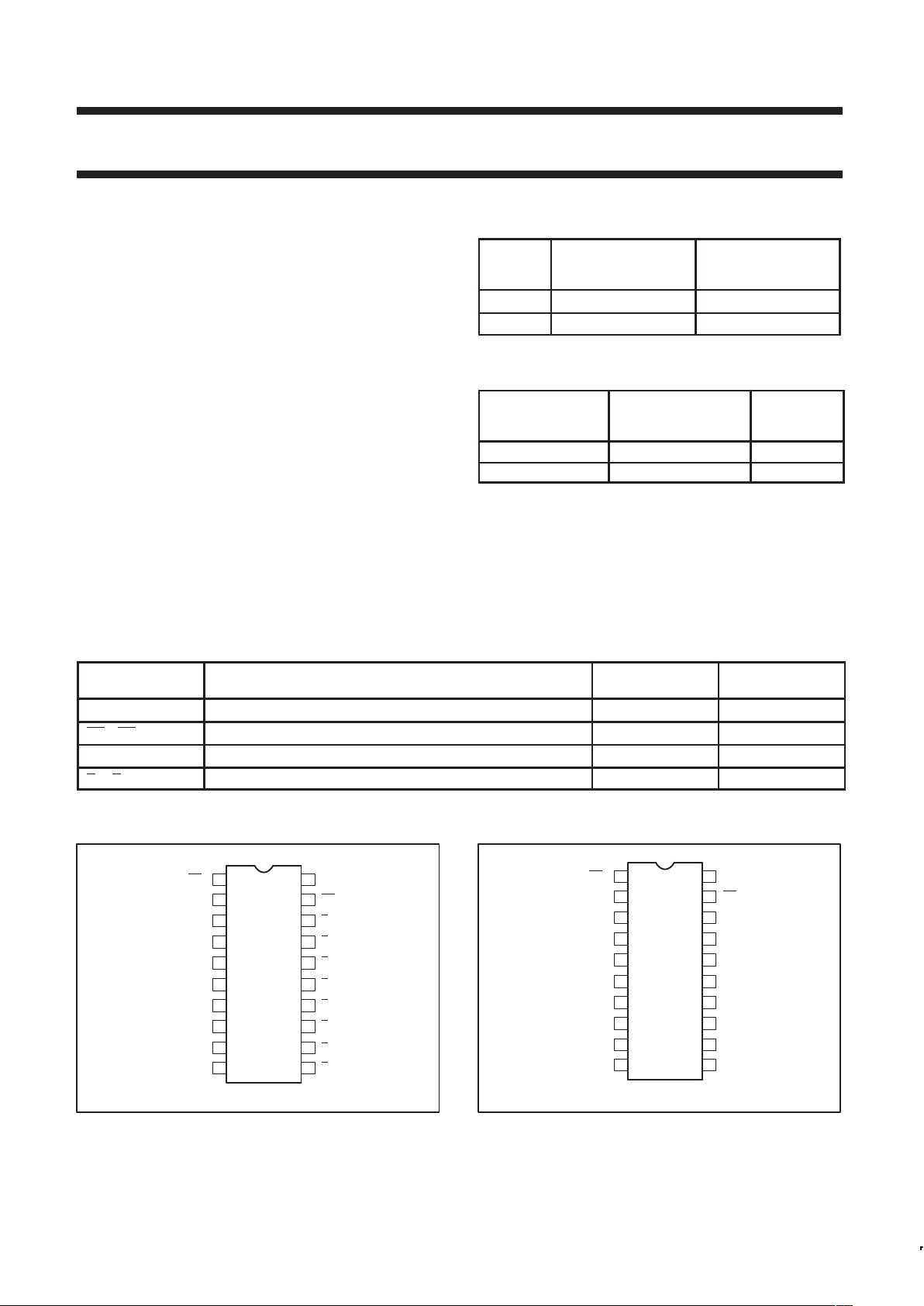

PIN CONFIGURATION – 74F540

20

19

18

17

16

15

14

13

12

10 11

9

8

7

6

5

4

3

2

1

V

CC

OE1

Y

0

Y

1

Y4

Y

5

Y6

Y

7

OE

0

I0

I1

I4

I5

I6

I7

GND

Y

2

Y3

I3

I2

SF01060

PIN CONFIGURATION – 74F541

20

19

18

17

16

15

14

13

12

10 11

9

8

7

6

5

4

3

2

1

V

CC

OE1

Y0

Y1

Y4

Y5

Y6

Y7

OE

0

I0

I1

I4

I5

I6

I7

GND

Y2

Y3

I3

I2

SF01021

Philips Semiconductors Product specification

74F540, 74F541Buffers

1990 Jan 08

3

LOGIC SYMBOL – 74F540

234

V

CC

= Pin 20

GND = Pin 10

18 17 16 15 14 13 12 11

1

19

SF01022

OE1

Y0 Y1 Y4 Y5 Y6 Y7

OE0

I0 I1 I4 I5 I6 I7

Y2 Y3

I3I2

56789

LOGIC SYMBOL – 74F541

234

V

CC

= Pin 20

GND = Pin 10

18 17 16 15 14 13 12 11

1

19

SF01023

OE1

Y0 Y1 Y4 Y5 Y6 Y7

OE0

I0 I1 I4 I5 I6 I7

Y2 Y3

I3I2

56789

LOGIC SYMBOL (IEEE/IEC) – 74F540

2

3

4

5

6

7

8

9

1

19

18

17

16

15

14

13

12

11

EN

SF01024

&

LOGIC SYMBOL (IEEE/IEC) – 74F541

2

3

4

5

6

7

8

9

1

19

18

17

16

15

14

13

12

11

EN

SF01025

&

LOGIC DIAGRAM – 74F540

VCC= Pin 20

GND = Pin 10

SF01026

11

12

13

14

15

16

17

18

OE0

OE

1

Y0

Y

1

Y

4

Y

5

Y

6

Y

7

I0

I1

I4

I5

I6

I7

Y

2

Y

3

I3

I2

1

19

2

3

4

5

6

7

8

9

LOGIC DIAGRAM – 74F541

VCC= Pin 20

GND = Pin 10

SF01027

Y0

Y1

Y2

Y3

Y4

Y5

Y6

Y7

11

12

13

14

15

16

17

18

OE0

OE

1

I0

I1

I4

I5

I6

I7

I3

I2

1

19

2

3

4

5

6

7

8

9

Loading...

Loading...