Philips N74ALS646-1D, N74ALS646-1N, N74ALS646D, N74ALS646N, N74ALS648D Datasheet

...

74ALS646/74ALS646–1

74ALS648/74ALS648–1

Transceiver/register

Product specification

IC05 Data Handbook

1991 Feb 08

INTEGRATED CIRCUITS

Philips Semiconductors Product specification

74ALS646/74ALS646-1

74ALS648/74ALS648-1

T ransceiver/register

74ALS646/646-1 Octal transceiver/register, non-inverting (3-State)

74ALS648/648-1 Octal transceiver/register, inverting (3-State)

2

1991 Feb 08 853–1408 01670

FEA TURES

•Combines 74ALS245 and two 74ALS374 type functions in

one chip

•Independent registers for A and B buses

•Multiplexed real-time and stored data

•Choice of non-inverting and inverting data paths

•3-State outputs

•The -1 version sink 48mA I

OL

within the ±5% VCC range

DESCRIPTION

The 74ALS646/74ALS646-1 and 74ALS648/74ALS648-1

transceivers/registers consist of bus transceiver circuits with 3-State

outputs, D-type flip-flops, and control circuitry arranged for

multiplexed transmission of data directly from the input bus or the

internal registers. Data on the A or B bus will be clocked into the

registers as the appropriate clock pin goes High. Output enable

(OE

) and direction (DIR) and select (SAB, SBA) pins are provided

for bus management.

The 74ALS646-1 and 74ALS648-1 will sink 48mA if the VCC is

limited to 5.0V ±0.25V.

TYPE

TYPICAL f

MAX

TYPICAL

SUPPLY CURRENT

(TOTAL)

74ALS646/646-1 140MHz 48mA

74ALS648/648-1 140MHz 54mA

ORDERING INFORMATION

ORDER CODE

DESCRIPTION

COMMERCIAL RANGE

V

CC

= 5V ±10%,

T

amb

= 0°C to +70°C

DRAWING

NUMBER

24-pin plastic DIP

74ALS646N, 74ALS646-1N,

74ALS648N, 74ALS648-1N

SOT222-1

24-pin plastic SOL

74ALS646D, 74ALS646-1D,

74ALS648D, 74ALS648-1D

SOT137-1

INPUT AND OUTPUT LOADING AND FAN-OUT TABLE

PINS DESCRIPTION

74ALS (U.L.)

HIGH/LOW

LOAD VALUE

HIGH/LOW

A0 – A7 A inputs 1.0/1.0 20µA/0.1mA

B0 – B7 B inputs 1.0/1.0 20µA/0.1mA

CPAB A-to-B clock input 1.0/1.0 20µA/0.1mA

CPBA B-to-A clock input 1.0/1.0 20µA/0.1mA

SAB A-to-B select input 1.0/1.0 20µA/0.1mA

SBA B-to-A select input 1.0/1.0 20µA/0.1mA

DIR Data flow directional control input 1.0/1.0 20µA/0.1mA

OE Output enable input 1.0/1.0 20µA/0.1mA

A0 – A7, B0 – B7 Data outputs 750/240 15mA/24mA

A0 – A7, B0 – B7 Data outputs (-1 version) 750/480 15mA/48mA

NOTE: One (1.0) ALS unit load is defined as: 20µA in the High state and 0.1mA in the Low state.

Philips Semiconductors Product specification

74ALS646/74ALS646-1

74ALS648/74ALS648-1

Transceiver/register

1991 Feb 08

3

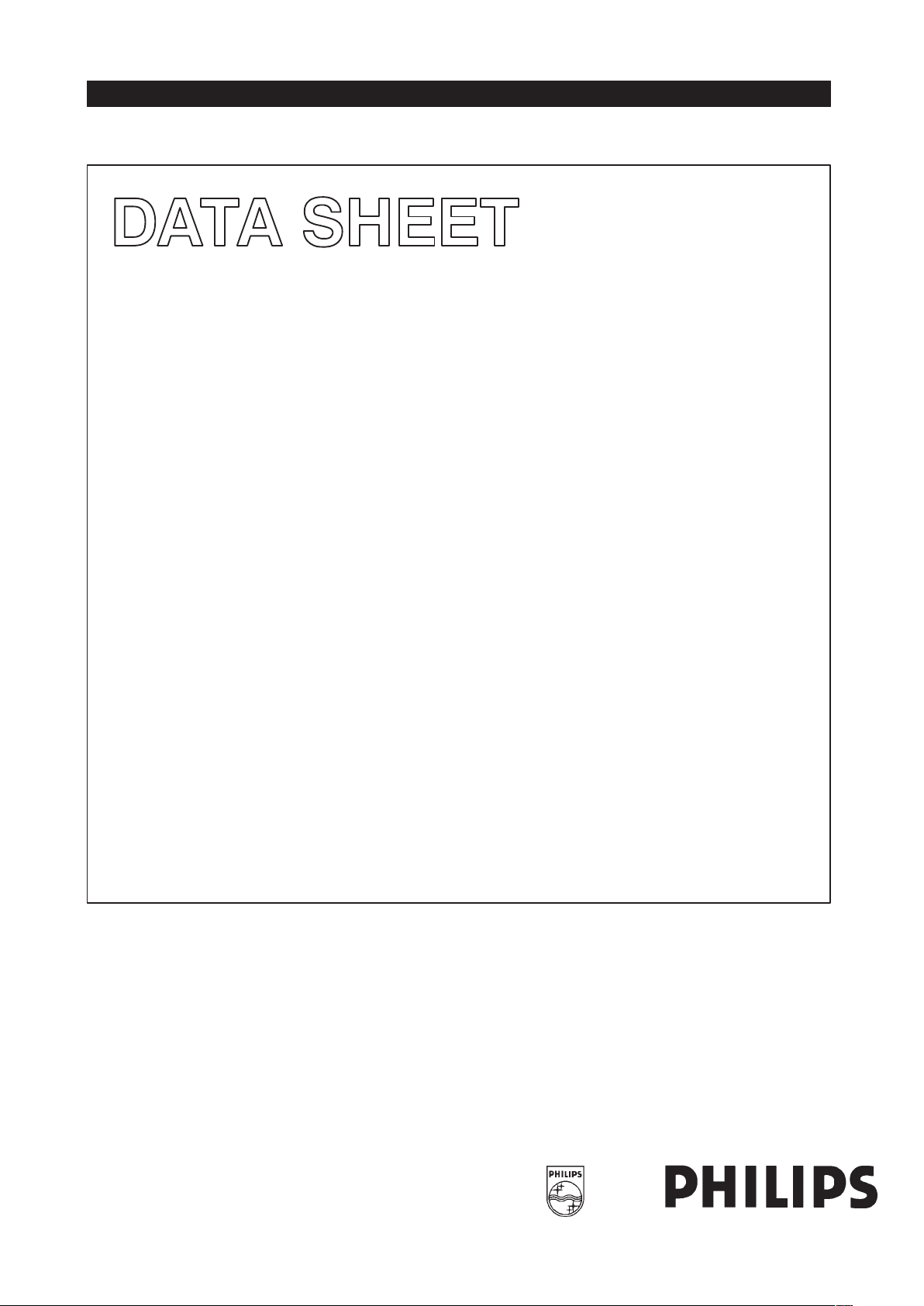

PIN CONFIGURATION – 74ALS646/646-1

1

2

3

4

5

6

7

8

9

10

11

12 13

14

15

16

17

18

19

20

21

22

23

24

CPAB

SAB

DIR

A0

A1

A2

A3

A4

A5

A6

A7

V

CC

CPBA

SBA

OE

B0

B1

B2

B4

B3

B5

B6

B7

GND

SC00118

PIN CONFIGURATION – 74ALS648/648-1

1

2

3

4

5

6

7

8

9

10

11

12 13

14

15

16

17

18

19

20

21

22

23

24

CPAB

SAB

DIR

A0

A1

A2

A3

A4

A5

A6

A7

V

CC

CPBA

SBA

OE

B0

B

1

B

2

B

4

B3

B

5

B

6

B

7

GND

SC00119

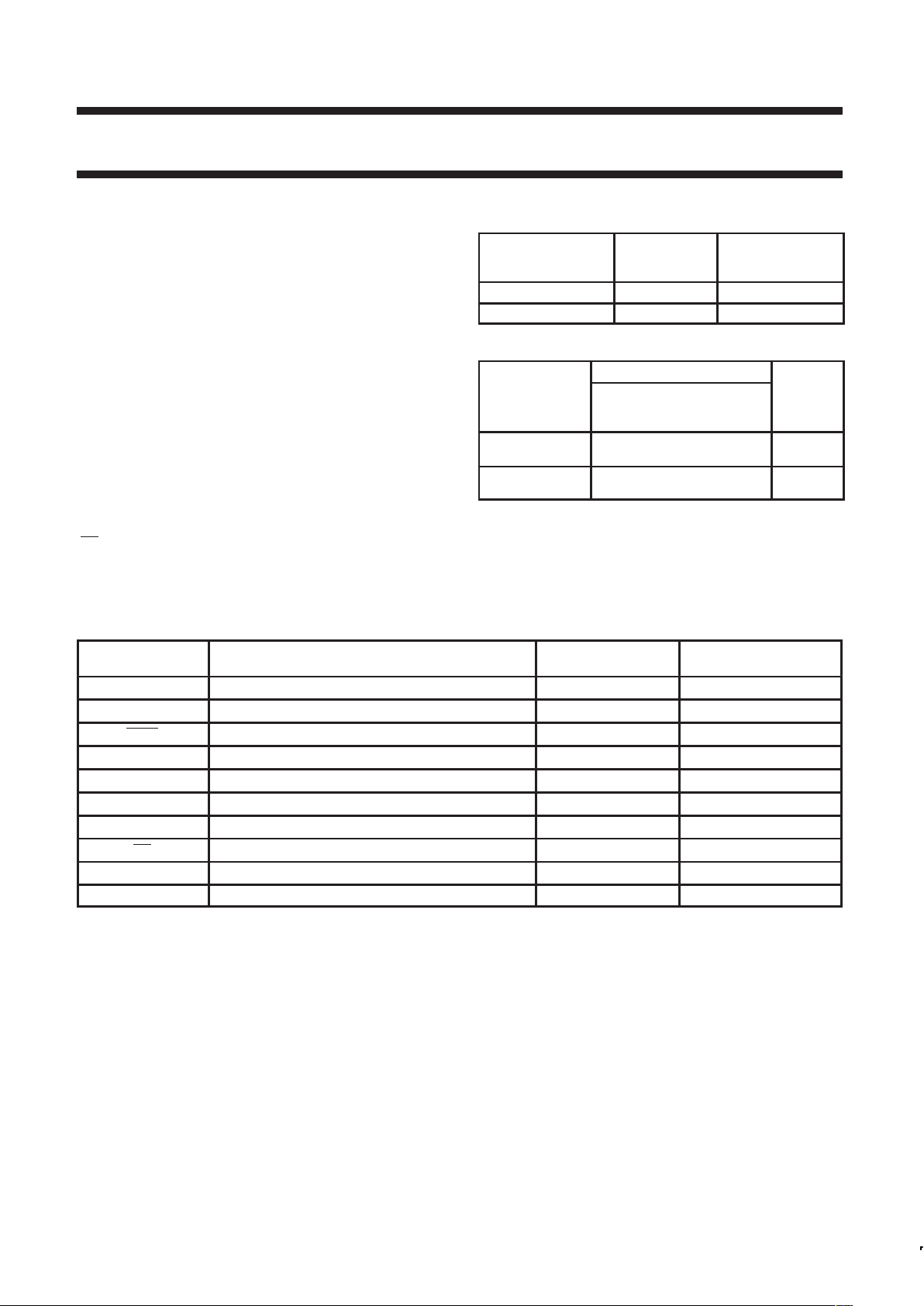

LOGIC SYMBOL – 74ALS646/646-1

B0 B1 B2 B3 B4 B5 B6 B7

A0 A1 A2 A3 A4 A5 A6 A7

4567891011

20 19 18 17 16 15 14 13

V

CC

= Pin 24

GND = Pin 12

SC00120

CPAB

SAB

DIR

SPBA

SBA

OE

1

2

3

23

22

21

LOGIC SYMBOL – 74ALS648/648-1

B0 B1 B2 B3 B4 B5 B6 B7

A0 A1 A2 A3 A4 A5 A6 A7

4567891011

20 19 18 17 16 15 14 13

VCC = Pin 24

GND = Pin 12

SC00121

CPAB

SAB

DIR

SPBA

SBA

OE

1

2

3

23

22

21

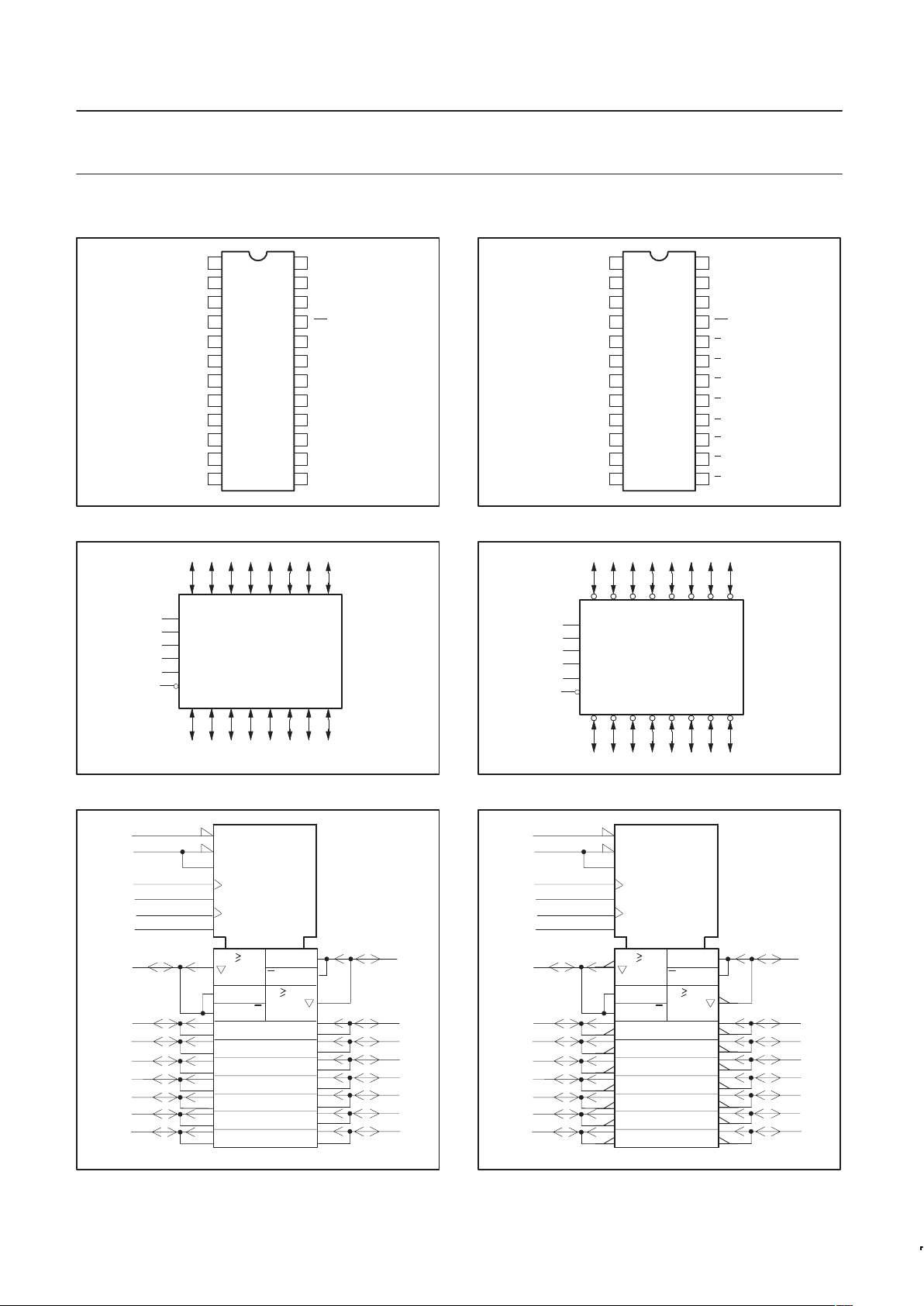

IEC/IEEE SYMBOL – 74ALS646/646-1

2

1

C4

G5

G7

C6

20

7

5

6D

4D

1

1

1

1

4

21

SC00122

G3

3 EN1 [BA]

3 EN2 [AB]

3

23

22

1

2

5

6

7

8

9

10

11

19

18

17

16

15

14

13

5

7

IEC/IEEE SYMBOL – 74ALS648/648-1

2

1

C4

G5

G7

C6

20

7

5

6D

4D

1

1

1

1

4

21

SC00123

G3

3 EN1 [BA]

3 EN2 [AB]

3

23

22

1

2

5

6

7

8

9

10

11

19

18

17

16

15

14

13

5

7

Philips Semiconductors Product specification

74ALS646/74ALS646-1

74ALS648/74ALS648-1

Transceiver/register

1991 Feb 08

4

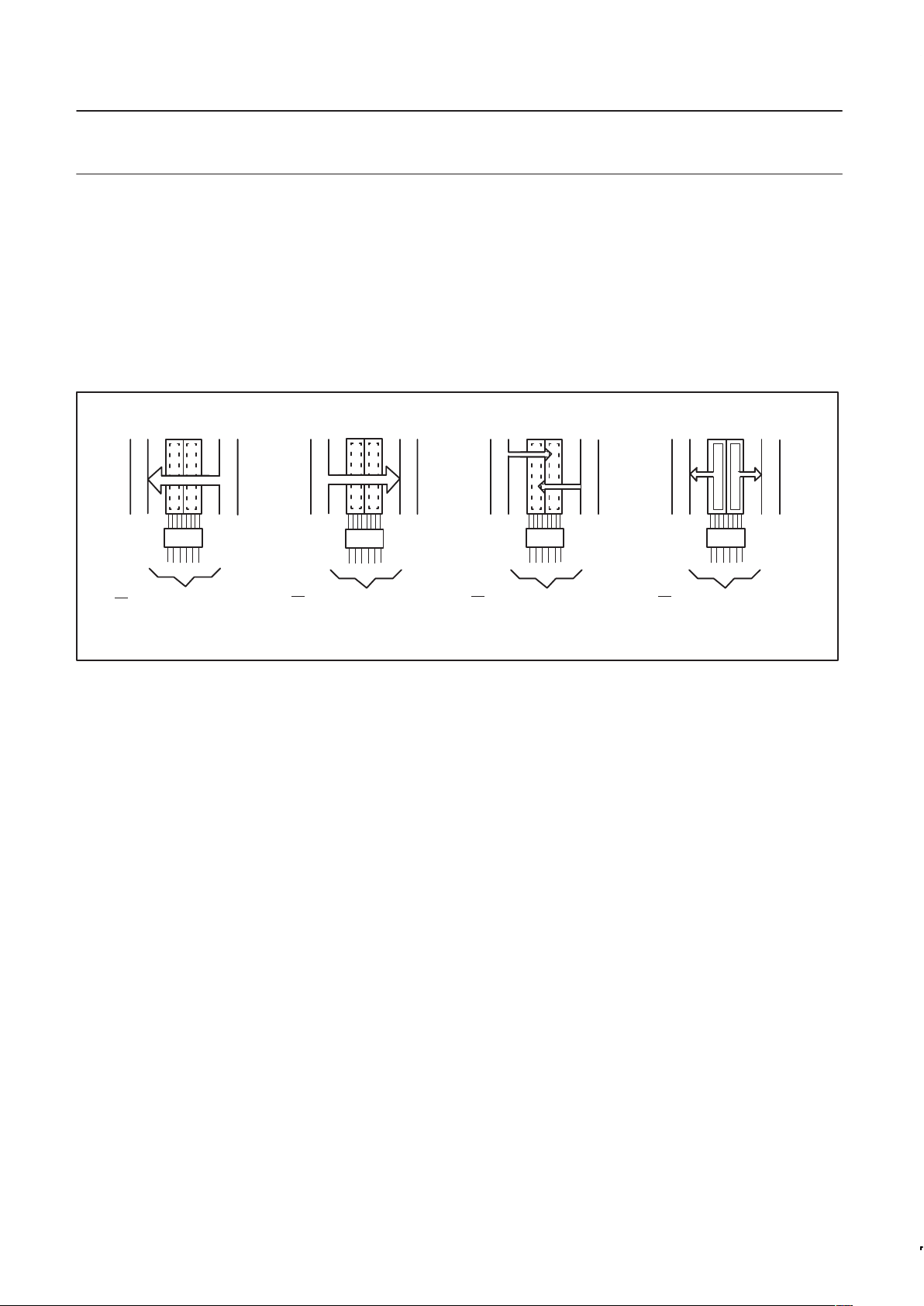

BUS MANAGEMENT FUNCTIONS

The following examples demonstrate the four fundamental

bus-management functions that can be performed with the

74ALS646/646-1 and 74ALS648/648-1.

The select pins determine whether data is stored or transferred

through the device in real time.

The DIR determines which bus will receive data when the OE pin is

Low.

REAL TIME BUS TRANSFER

BUS B TO BUS A

REAL TIME BUS TRANSFER

BUS A TO BUS B

STORAGE FROM

A, B, OR A AND B

TRANSFER STORED DATA

TO A AND/OR B

OE DIR CPABCPBA SAB SBA

LL X X X L

BUS A

BUS A BUS A

BUS A BUS BBUS BBUS B

BUS B

OE

DIR CPABCPBA SAB SBA

LH X X L X

OE DIR CPABCPBA SAB SBA

XX ↑ XXX

XX X ↑ XX

HX ↑↑XX

OE

DIR CPABCPBA SAB SBA

L L X H or L X H

L H H or L X H X

SF00392

Loading...

Loading...