Philips N74ALS161BD, N74ALS161BDB, N74ALS161BN, N74ALS163BD, N74ALS163BDB Datasheet

...

74ALS161B/74ALS163B

4-bit binary counter

Product specification 1991 Feb 08

INTEGRATED CIRCUITS

IC05 Data Handbook

Philips Semiconductors Product specification

74ALS161B/74ALS163B4-bit binary counter

74ALS161B 4-bit binary counter, asynchronous reset

74ALS163B 4-bit binary counter, synchronous reset

2

1991 Feb 08 853–1350 01670

FEA TURES

•Synchronous counting and loading

•Two count enable inputs for n-bit cascading

•Positive edge-triggered clock

•Asynchronous reset (74ALS161B)

•Synchronous reset (74ALS163B)

•High speed synchronous expansion

•Typical count rate of 140MHz

TYPE

TYPICAL f

MAX

TYPICAL

SUPPLY CURRENT

(TOTAL)

74ALS161B 140MHz 10mA

74ALS163B 140MHz 10mA

ORDERING INFORMATION

ORDER CODE

DESCRIPTION COMMERCIAL RANGE

V

CC

= 5V ±10%,

T

amb

= 0°C to +70°C

DRAWING

NUMBER

16-pin plastic DIP 74ALS161BN, 74ALS163BN SOT38-4

16-pin plastic SO 74ALS161BD, 74ALS163BD SOT109-1

16-pin plastic SSOP

Type II

74ALS161BDB,

74ALS163BDB

SOT338-1

DESCRIPTION

Synchronous presettable 4-bit binary counters (74ALS161B,

74ALS163B) feature an internal carry look-ahead and can be used

for high speed counting. Synchronous operation is provided by

having all flip-flops clocked simultaneously on the positive-going

edge of the clock. The clock input is buffered.

The outputs of the counters may be preset to High or Low level. A

Low level at the parallel enable (PE

) input disables the counting

action and causes the data at the D0 – D3 inputs to be loaded into

the counter on the positive-going edge of the clock (provided that

the setup and hold requirements for PE

are met). Preset takes place

regardless of the levels at count enable (CEP, CET) inputs.

A Low level at the master reset (MR

) input sets all the four outputs

of the flip-flops (Q0 – Q3) in 74ALS161B to Low levels, regardless of

the levels at CP, PE

, CET and CEP inputs (thus providing an

asynchronous clear function).

For the 74ALS163B the clear function is synchronous. A Low level

at the synchronous reset (SR

) input sets all four outputs of the

flip-flops (Q0 – Q3) to Low levels after the next positive-going

transition on the clock (CP) input ( provided that the setup and hold

time requirements for SR

are met). This action occurs regardless of

the levels at CP, PE

, CET and CEP inputs. The synchronous reset

feature enables the designer to modify the maximum count with only

one external NAND gate (see Figure 1).

The carry look-ahead simplifies serial cascading of the counters.

Both count enable (CEP and CET) inputs must be High to count.

The CET input is fed forward to enable the TC output. The TC

output thus enabled will produce a High output pulse of a duration

approximately equal to the High level output of Q0. This pulse can

be used to enable the next cascaded stage (see Figure 2).

The TC output is subjected to decoding spikes due to internal race

conditions, Therefore, it is not recommended for use as clock or

asynchronous reset for flip-flops, registers, or counters.

INPUT AND OUTPUT LOADING AND FAN-OUT TABLE

PINS DESCRIPTION

74ALS (U.L.)

HIGH/LOW

LOAD VALUE

HIGH/LOW

D0 – D3 Data inputs 1.0/1.0 20µA/0.1mA

CEP Count enable parallel input (active-Low) 1.0/1.0 20µA/0.1mA

CET Count enable trickle input (active-Low) 1.0/1.0 20µA/0.1mA

CP Clock input (active rising edge) 1.0/1.0 20µA/0.1mA

PE Parallel enable input (active-Low) 1.0/1.0 20µA/0.1mA

MR Asynchronous master reset input (active-Low) for 74ALS161B 1.0/1.0 20µA/0.1mA

SR Asynchronous reset input (active-Low) for 74ALS163B 1.0/1.0 20µA/0.1mA

Q0 – Q3 Flip-flop outputs 20/80 0.4mA/8mA

TC T erminal count output (active-Low) 20/80 0.4mA/8mA

NOTE: One (1.0) ALS unit load is defined as: 20µA in the High state and 0.1mA in the Low state.

Philips Semiconductors Product specification

74ALS161B/74ALS163B4-bit binary counter

1991 Feb 08

3

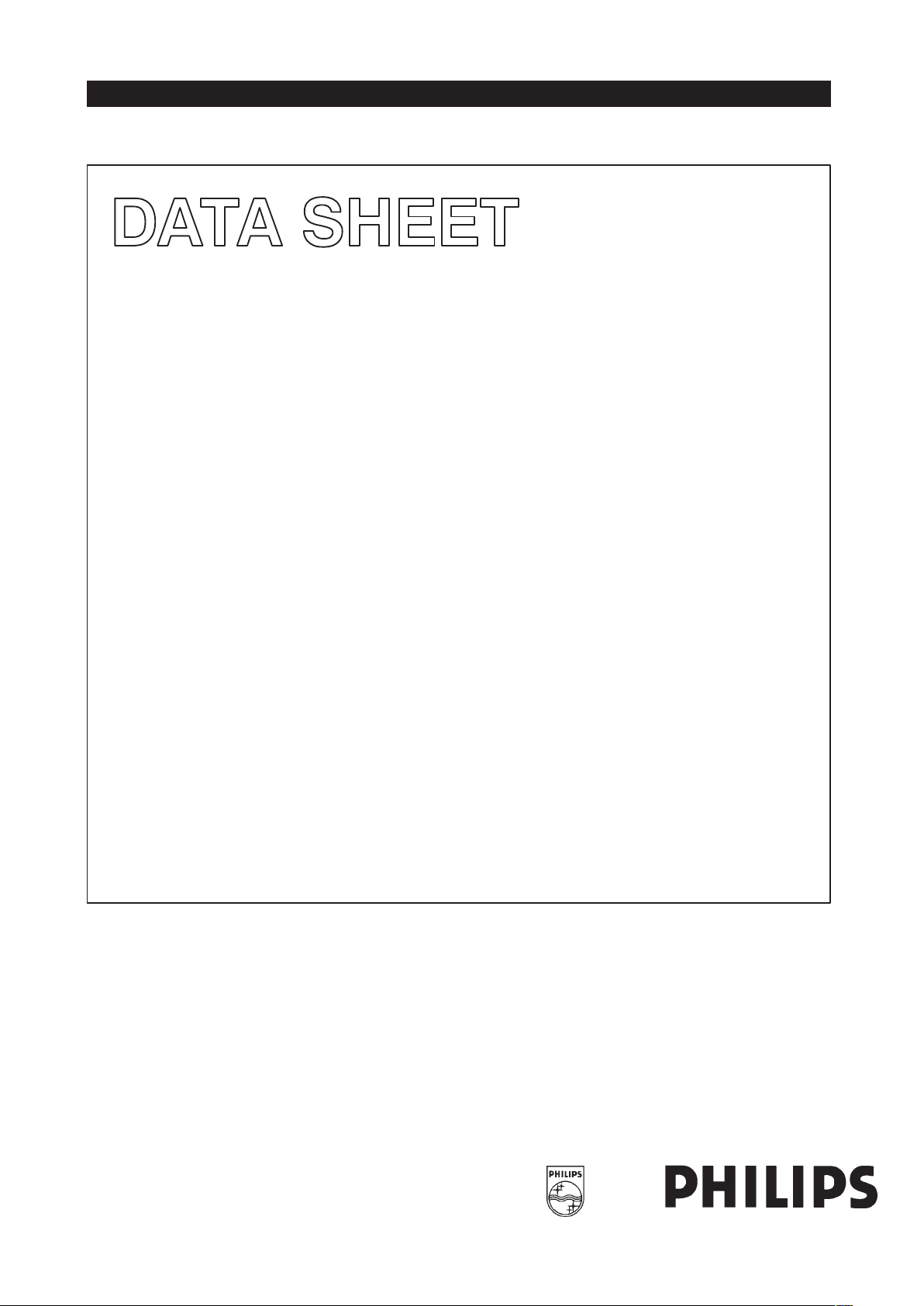

ST ATE DIAGRAM

8

7

6

5

4

12 11 10 9

13

14

15

0 1 2 3

SF00664

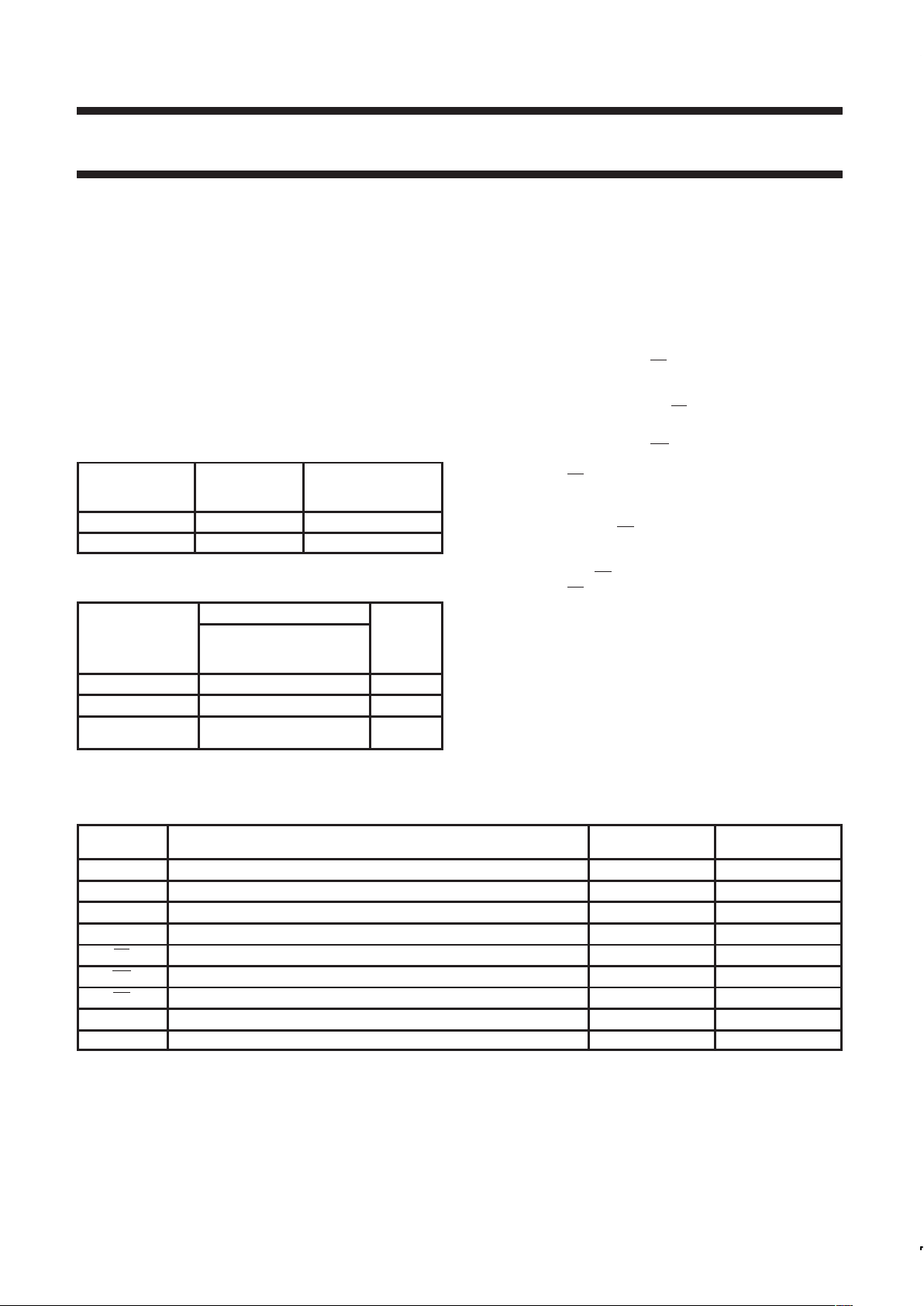

APPLICATIONS

Q0 Q1 Q2 Q3

CLOCK

PE

CEP

CET

CP

D1 D2

SC00086

D3D0

SR

TC74ALS163B

V

CC

Figure 1. Maximum Count Modifying Scheme

Terminal Count = 6

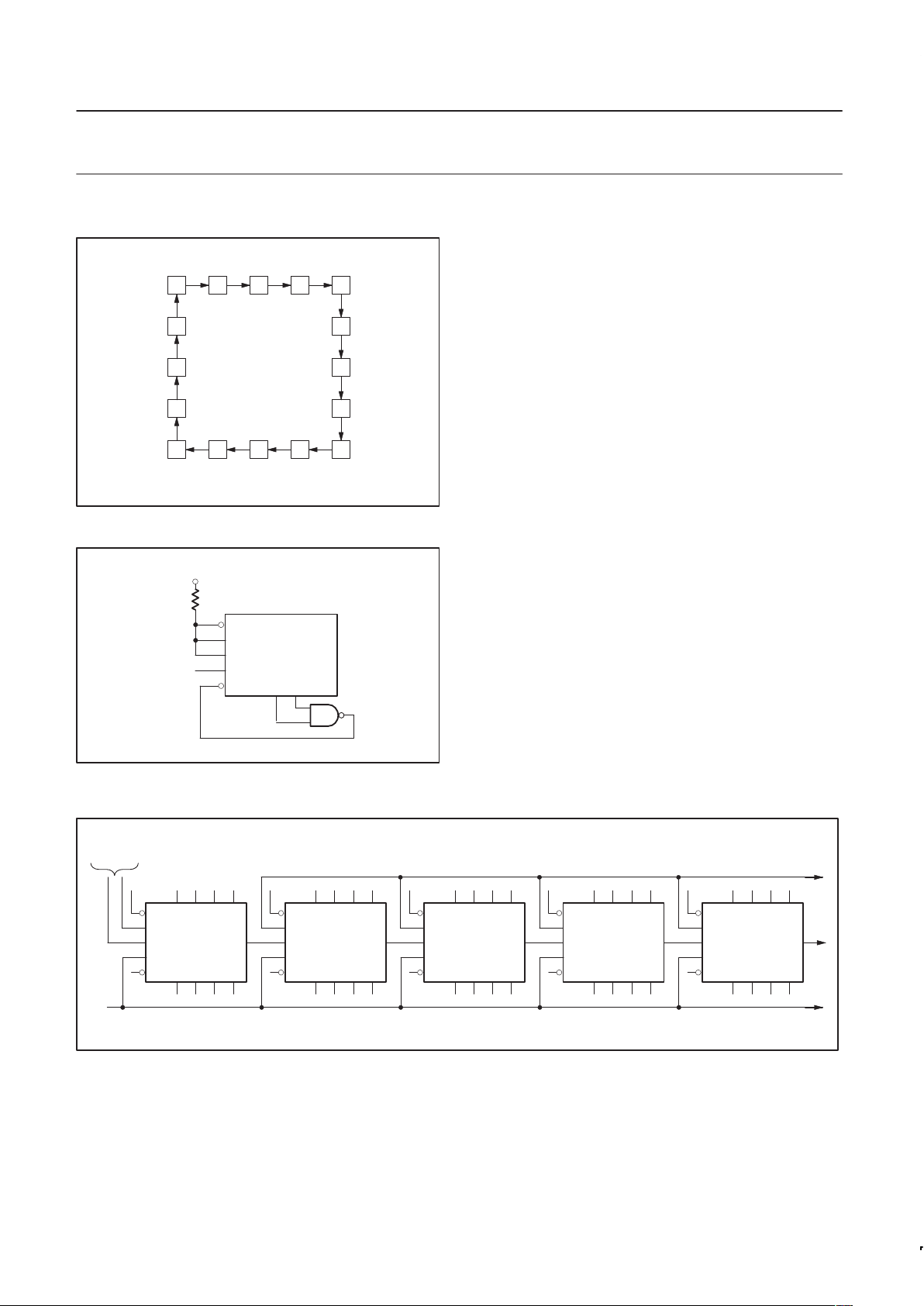

Q0 Q1 Q2 Q3

PE

CEP

CET

CP

D1 D2

SC00087

D3D0

SR

TC

Q0 Q1 Q2 Q3

PE

CEP

CET

CP

D1 D2 D3D0

SR

TC

Q0 Q1 Q2 Q3

PE

CEP

CET

CP

D1 D2 D3D0

SR

TC

Q0 Q1 Q2 Q3

PE

CEP

CET

CP

D1 D2 D3D0

SR

TC

Q0 Q1 Q2 Q3

PE

CEP

CET

CP

D1 D2 D3D0

SR

TC

74ALS163B

CP

H H = Enable count

or

L L = Disable count

74ALS163B 74ALS163B 74ALS163B 74ALS163B

Figure 2. Synchronous Multistage Counting Scheme

Philips Semiconductors Product specification

74ALS161B/74ALS163B4-bit binary counter

1991 Feb 08

4

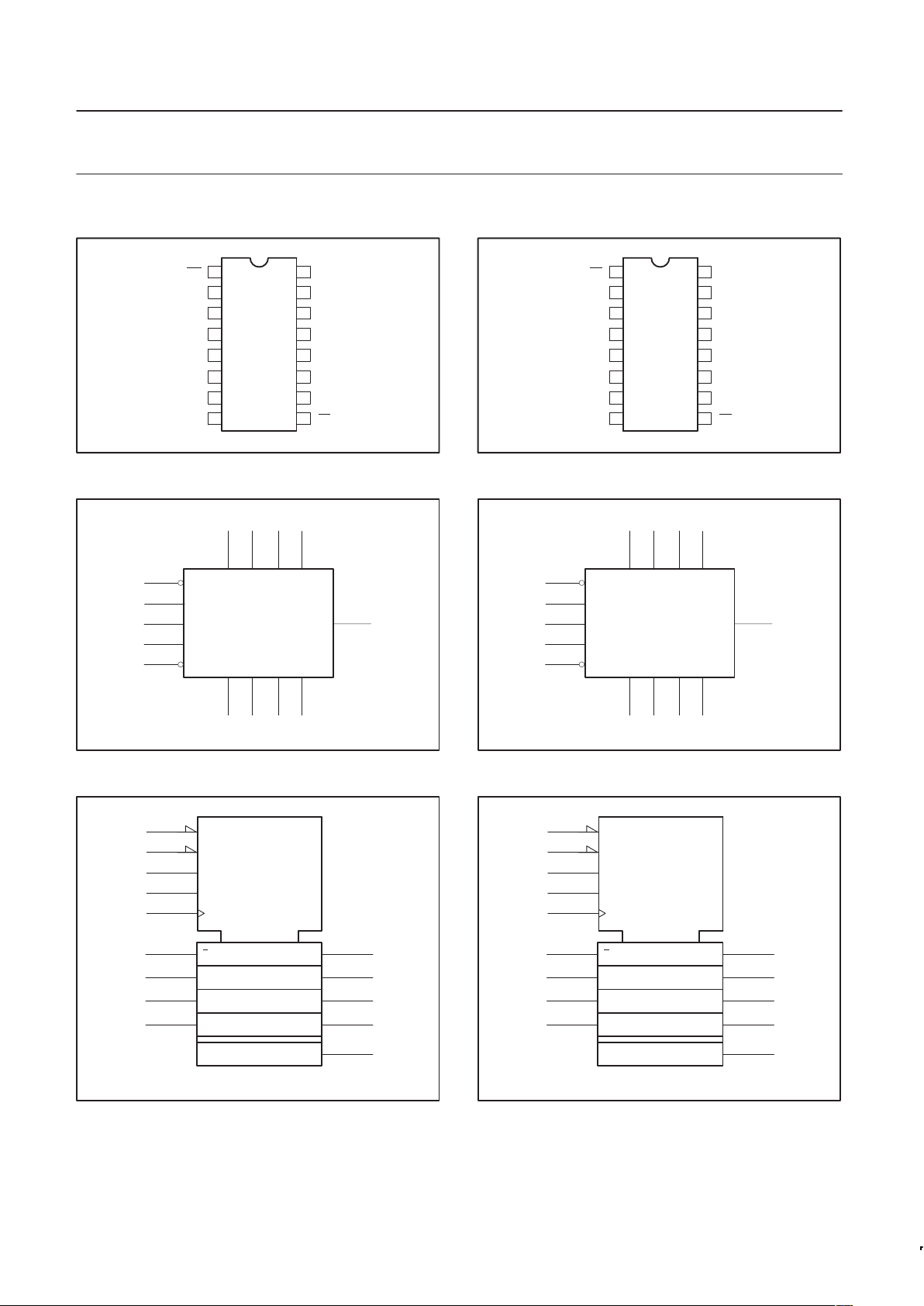

PIN CONFIGURATION – 74ALS161B

16

15

14

13

12

11

107

6

5

4

3

2

1

CEP

V

CC

Q2

Q3

CET

Q1

TC

Q0

MR

CP

D3

D0

D1

D2

98GND PE

SF00656

PIN CONFIGURATION – 74ALS163B

16

15

14

13

12

11

107

6

5

4

3

2

1

CEP

V

CC

Q2

Q3

CET

Q1

TC

Q0

SR

CP

D3

D0

D1

D2

98GND PE

SF00657

LOGIC SYMBOL – 74ALS161B

Q0 Q1

Q2 Q3

14 13

12 11V

CC

= Pin 16

GND = Pin 8

9

7

10

2

PE

CEP

CET

CP

D1 D2

56

SF00658

D3D0

34

1MR

TC 15

LOGIC SYMBOL – 74ALS163B

Q0 Q1

Q2 Q3

14 13

12 11V

CC

= Pin 16

GND = Pin 8

9

7

10

2

PE

CEP

CET

CP

D1 D2

56

SF00659

D3D0

34

1SR

TC 15

IEC/IEEE SYMBOL – 74ALS161B

SF00660

3

1

,2 D

1

9

M1

4

5

6

14

13

12

11

15

4 CT=15

7

G3

10

G4

2

C2 /1,3,4+

R

CTR DIV 16

IEC/IEEE SYMBOL – 74ALS163B

SF00661

3

1

,2 D

1

9

M1

4

5

6

14

13

12

11

15

4 CT=15

7

G3

10

G4

2

C2 /1,3,4+

2R

CTR DIV 16

Philips Semiconductors Product specification

74ALS161B/74ALS163B4-bit binary counter

1991 Feb 08

5

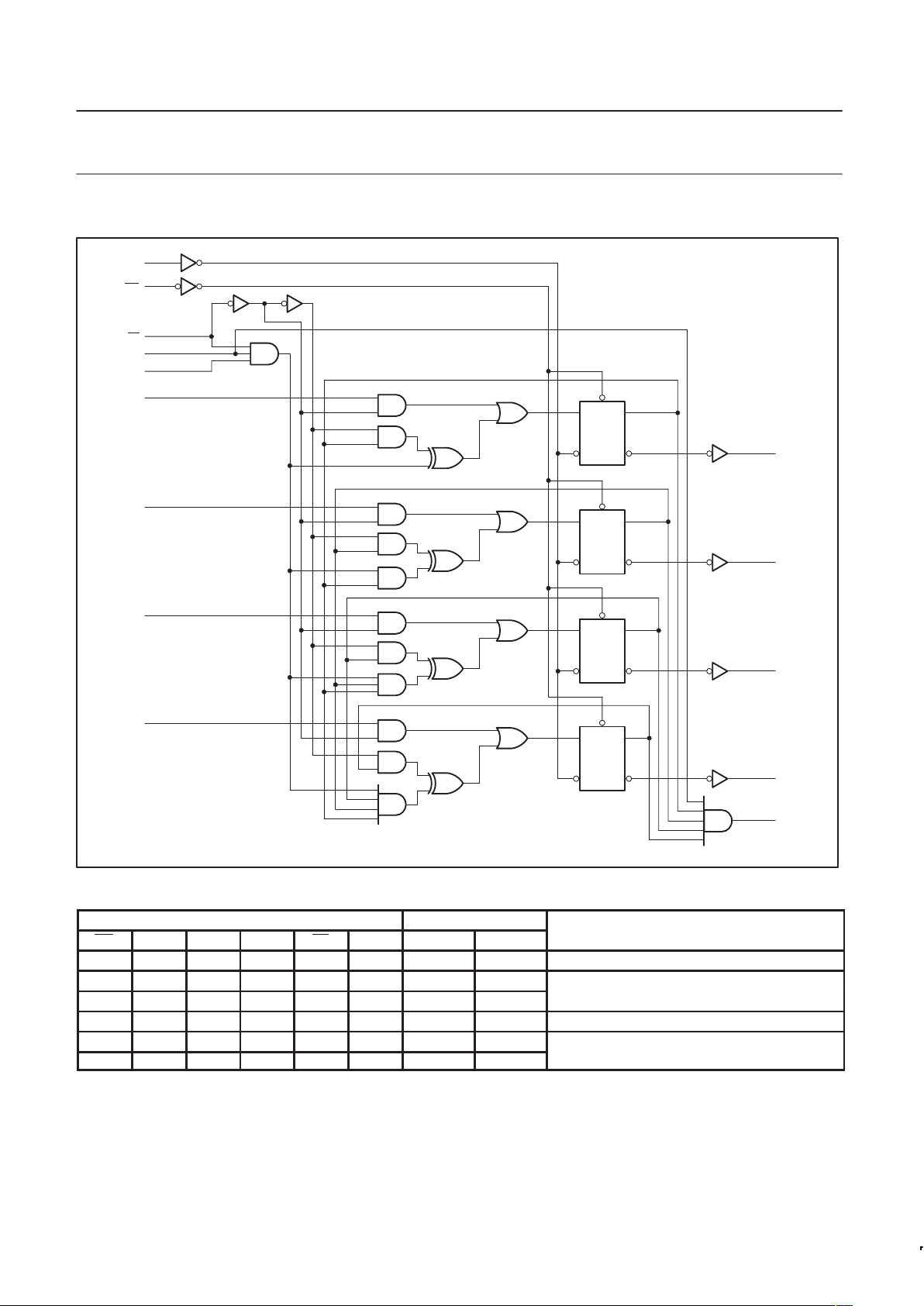

LOGIC DIAGRAM – 74ALS161B

R

DCPQ

Q

R

DCPQ

Q

R

DCPQ

Q

R

DCPQ

Q

14

Q0

13

Q1

12

Q2

11

Q3

15

TC

6

D3

5

D2

4

D1

3

D0

7

CEP

10

CET

9

PE

1

MR

2

CP

SF00662

VCC = Pin 16

GND = Pin 8

MODE SELECTION FUNCTION TABLE – 74ALS161B

INPUTS OUTPUTS

MR CP CEP CET PE Dn Qn TC

OPERATING MODE

L X X X X X L L Reset (clear)

H ↑ X X l l L L

H ↑ X X l h H (a)

Parallel load

H ↑ h h h X count (a) Count

h X l X h X qn (a)

h X X l h X qn L

Hold (do nothing)

H = High-voltage level

h = High state must be present one setup time before the Low-to-High clock transition

L = Low-voltage level

l = Low state must be present one setup time before the Low-to-High clock transition

qn = Lower case letters indicate the state of the referenced output prior to the Low-to-High clock transition

X = Don’t care

(a) = The output is High when CET is High and the counter is at terminal count (HHHH)

↑ = Low-to-High clock transition

Loading...

Loading...