Page 1

INTEGRATED CIRCUITS

LPC2119/2129/2194/2292/2294

USER MANUAL

Preliminary

Supersedes data of 2004 Feb 03

2004 May 03

Page 2

Philips Semiconductors Preliminary User Manual

LPC2119/2129/2194/2292/2294ARM-based Microc ontroller

2 May 03, 2004

Page 3

Philips Semiconductors Preliminary User Manual

LPC2119/2129/2194/2292/2294ARM-based Microc ontroller

Table of Contents

List of Figures . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

List of Tables . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Document Revision History . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

General Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

Applications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Device information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Architectural Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

ARM7TDMI-S Processor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

On-Chip Flash Memory System . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

On-Chip Static RAM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

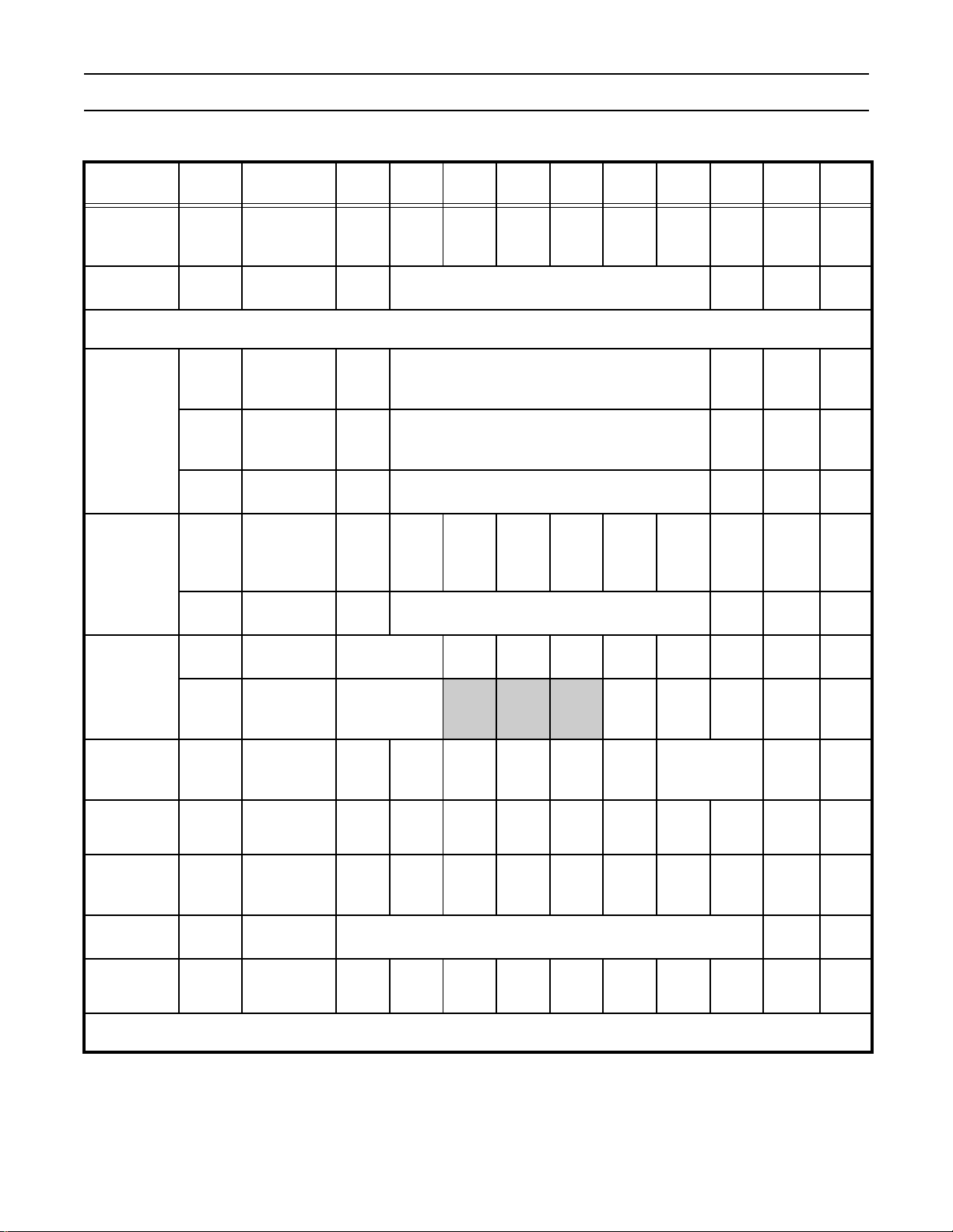

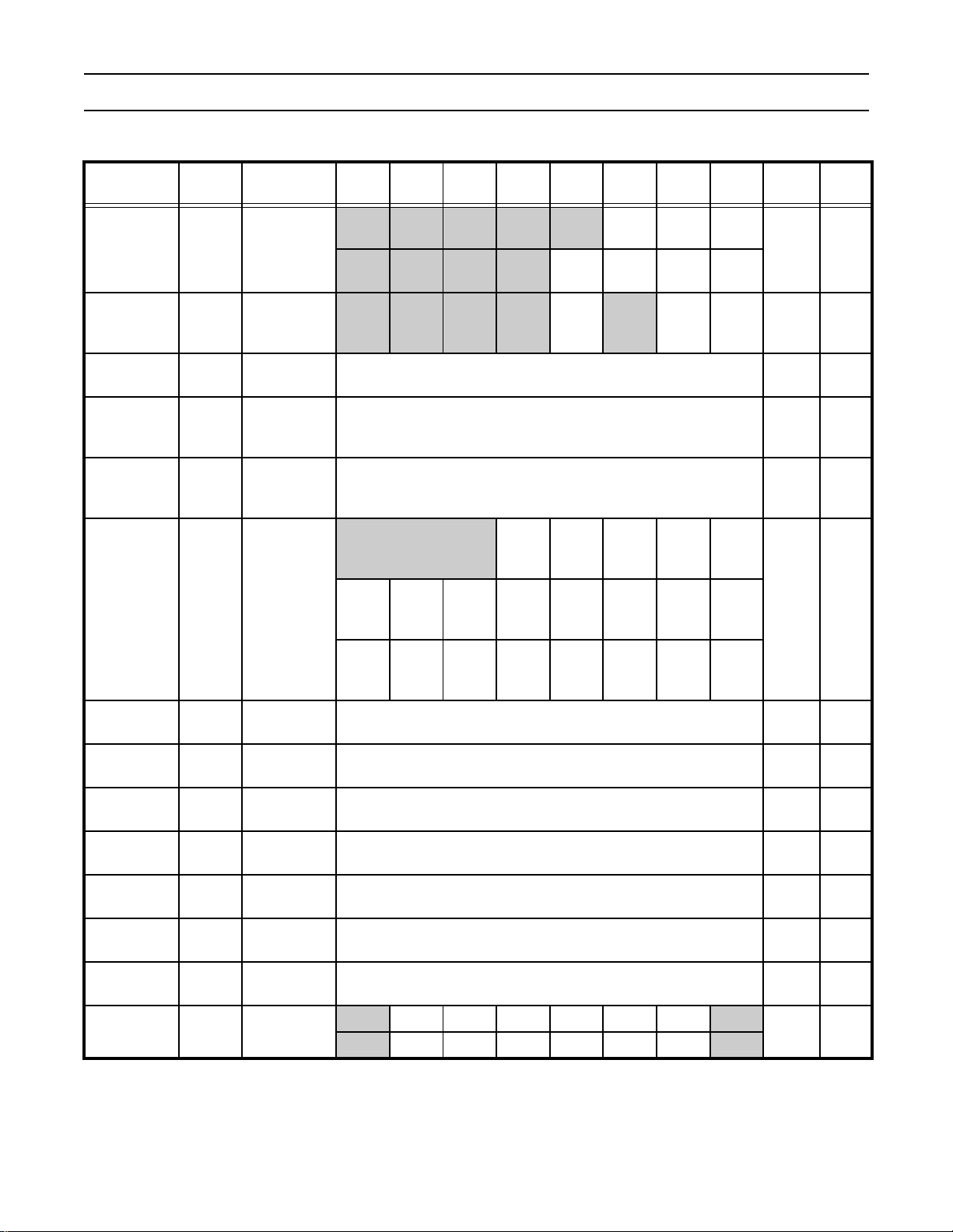

LPC2119/2129/2292/2194/2294 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

LPC2119/2129/2292/2294 Memory Addressing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

Memory Maps . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

LPC2119/2129/2194/2292/2294 Memory Re-mapping and Boot Block . . . . . . . . . . . . . . . . . . . . 52

Prefetch Abort and Data Abort Exceptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

External Memory Controller (EMC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

Pin Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

Register Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

External Memory Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

Typical Bus Sequences . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

External Memory Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

System Control Block . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

Summary of System Control Block Functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

Pin Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

Register Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

Crystal Oscillator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

External Interrupt Inputs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

Memory Mapping Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 74

PLL (Phase Locked Loop) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 75

Power Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 81

Power Control Usage Notes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 84

Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 85

VPB Divider . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 86

Wakeup Timer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 88

Memory Accelerator Module (MAM) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 90

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 90

Memory Accelerator Module Operating Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 92

MAM Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 93

Register Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 93

MAM Usage Notes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 94

3 May 03, 2004

Page 4

Philips Semiconductors Preliminary User Manual

LPC2119/2129/2194/2292/2294ARM-based Microc ontroller

Vectored Interrupt Controller (VIC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 96

Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 96

Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 96

Register Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 97

VIC Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 99

Interrupt Sources . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 103

Spurious Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 106

VIC Usage Notes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 109

Pin Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 110

LPC2119/2129/2194 Pinout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 110

Pin Description for LPC2119/2129/2194 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 111

LPC2292/2294 Pinout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 116

Pin Description for LPC2292/2294 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 117

Pin Connect Block . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 126

Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 126

Applications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 126

Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 126

Register Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 126

Boot Control on 144-pin Package . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 133

GPIO . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 134

Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 134

Applications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 134

Pin Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 134

Register Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 134

GPIO Usage Notes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 137

UART0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 140

Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 140

Pin Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 140

Register Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 141

Architecture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 149

UART1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 152

Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 152

Pin Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 152

Register Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 153

Architecture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 164

I2C Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 166

Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 166

Applications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 166

Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 166

Pin Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 170

Register Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 171

Architecture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 177

SPI Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 178

Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 178

Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 178

Pin Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 182

Register Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 183

Architecture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 186

4 May 03, 2004

Page 5

Philips Semiconductors Preliminary User Manual

LPC2119/2129/2194/2292/2294ARM-based Microc ontroller

CAN Controllers and Acceptance Filter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 188

CAN Controllers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 188

Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 188

Pin Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 189

Memory Map of the CAN Block . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 189

CAN Controller Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 189

CAN Controller Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 202

Centralized CAN Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 204

Global Acceptance Filter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 205

Acceptance Filter Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 207

Examples of Acceptance Filter Tables and ID Index Values . . . . . . . . . . . . . . . . . . . . . . . . . . . . 209

FullCAN Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 210

Timer0 and Timer1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 214

Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 214

Applications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 214

Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 215

Pin Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 215

Register Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 216

Example Timer Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 221

Architecture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 222

Pulse Width Modulator (PWM) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 224

Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 224

Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 224

Pin Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 229

Register Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 230

A/D Converter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 238

Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 238

Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 238

Pin DescriptionS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 238

Register Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 238

OPERATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 240

Real Time Clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 242

Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 242

Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 242

Architecture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 243

Register Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 243

RTC Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 245

Miscellaneous Register Group . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 246

Consolidated Time Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 249

Time Counter Group . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 251

Alarm Register Group . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 252

RTC Usage Notes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 252

Reference Clock Divider (Prescaler) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 253

Watchdog . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 256

Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 256

Applications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 256

Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 256

Register Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 257

Usage Notes on Watchdog Reset and External Start . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 259

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 260

Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 261

5 May 03, 2004

Page 6

Philips Semiconductors Preliminary User Manual

LPC2119/2129/2194/2292/2294ARM-based Microc ontroller

Flash Memory System and Programming . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 262

Flash Memory System . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 262

Flash boot Loader . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 262

Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 262

Applications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 262

Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 262

Boot process FlowChart . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 266

Sector Numbers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 268

Code Read Protection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 269

JTAG FLASH Programming interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 285

EmbeddedICE Logic . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 286

Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 286

Applications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 286

Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 286

Pin Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 287

Reset State of Multiplexed Pins . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 287

Register Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 288

Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 289

Embedded Trace Macrocell . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 290

Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 290

Applications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 290

Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 290

Pin Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 291

Reset State of Multiplexed Pins . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 291

Register Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 292

Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 293

RealMonitor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 294

Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 294

Applications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 294

Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 294

How to Enable RealMonitor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 298

RealMonitor build options . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 304

6 May 03, 2004

Page 7

Philips Semiconductors Preliminary User Manual

LPC2119/2129/2194/2292/2294ARM-based Microc ontroller

List of Figures

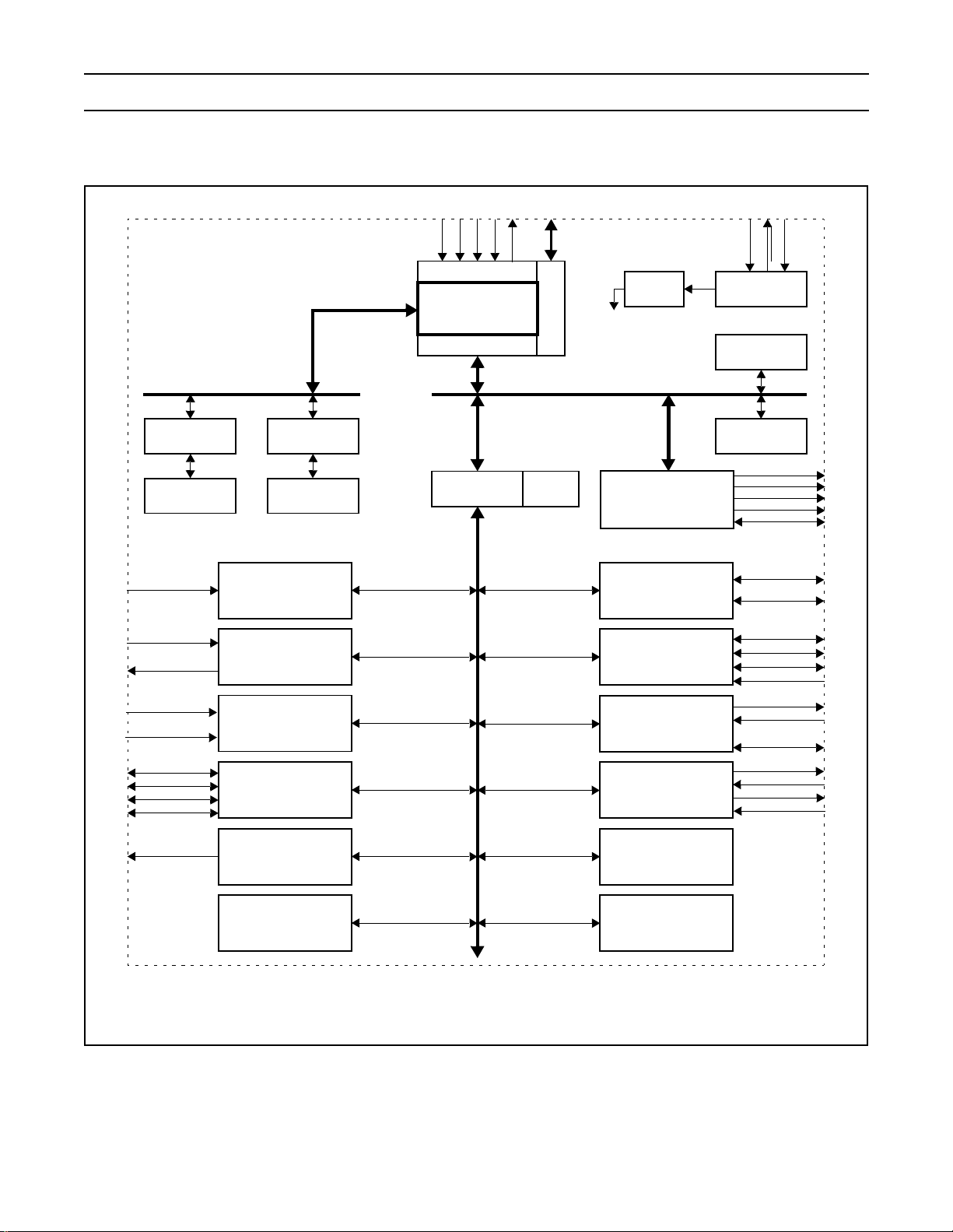

Figure 1: LPC2119/2129/2194/2292/2294 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Figure 2: System Memory Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

Figure 3: Peripheral Memory Map. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

Figure 4: AHB Peripheral Map. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

Figure 5: VPB Peripheral Map. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

Figure 6: Map of lower memory is showing re-mapped and re-mappable areas (128 kB Flash).. . . . . . . 54

Figure 7: 32 Bit Bank External Memory Interfaces . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

Figure 8: 16 Bit Bank External Memory Interfaces . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

Figure 9: 8 Bit Bank External Memory Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

Figure 10: External memory read access (WST1=0 and WST1=1 examples) . . . . . . . . . . . . . . . . . . . . . . 61

Figure 11: External memory write access (WST2=0 and WST2=1 examples) . . . . . . . . . . . . . . . . . . . . . . 61

Figure 12: Oscillator modes and models: a) slave mode of operation, b) oscillation mode of operation,

c) external crystal model used for CX1/X2 evaluation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

Figure 13: FOSC selection algorithm. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

Figure 14: External Interrupt Logic. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

Figure 15: PLL Block Diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 76

Figure 16: Reset Block Diagram including Wakeup Timer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 85

Figure 17: VPB Divider Connections. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 87

Figure 18: Simplified Block Diagram of the Memory Accelerator Module . . . . . . . . . . . . . . . . . . . . . . . . . . 91

Figure 19: Block Diagram of the Vectored Interrupt Controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 105

Figure 20: LPC2119/2129/2194 64-pin package. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 110

Figure 21: LPC2292/2294 144-pin package . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 116

Figure 22: UART0 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 150

Figure 23: UART1 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 165

Figure 24: I2C Bus Configuration. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 167

Figure 25: Slave Mode Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 167

Figure 26: Format in the master transmitter mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 168

Figure 27: Format of master receiver mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 168

Figure 28: A master receiver switch to master transmitter after sending repeated START. . . . . . . . . . . . 169

Figure 29: Slave Mode Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 169

Figure 30: Format of slave receiver mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 170

Figure 31: Format of slave transmitter mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 170

Figure 32: I2C Architecture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 177

Figure 33: SPI Data Transfer Format (CPHA = 0 and CPHA = 1). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 179

Figure 34: SPI Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 186

Figure 35: Entry in fullCAN and Individual Standard Identifier Tables. . . . . . . . . . . . . . . . . . . . . . . . . . . . 205

Figure 36: Entry in Standard Identifier Range Table . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 205

Figure 37: Entry in either Extended Identifier Table. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 206

Figure 38: Detailed Example of Acceptance Filter Tables and ID Index Values . . . . . . . . . . . . . . . . . . . . 210

Figure 39: A timer cycle in which PR=2, MRx=6, and both interrupt and reset on match are enabled.. . . 221

Figure 40: A timer cycle in which PR=2, MRx=6, and both interrupt and stop on match are enabled. . . . 221

Figure 41: Timer block diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 222

Figure 42: PWM block diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 226

Figure 43: Sample PWM waveforms. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 227

Figure 44: RTC block diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 243

Figure 45: RTC Prescaler block diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 254

Figure 46: Watchdog Block Diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 261

Figure 47: Map of lower memory after any reset (128 kB Flash part).. . . . . . . . . . . . . . . . . . . . . . . . . . . . 263

Figure 48: Boot Process flowchart (Bootloader revisions before 1.61) . . . . . . . . . . . . . . . . . . . . . . . . . . . 266

Figure 49: Boot Process flowchart (Bootloader revisions 1.61 and later) . . . . . . . . . . . . . . . . . . . . . . . . . 267

Figure 50: IAP Parameter passing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 281

Figure 51: EmbeddedICE Debug Environment Block Diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 289

Figure 52: ETM Debug Environment Block Diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 293

Figure 53: RealMonitor components . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 295

Figure 54: RealMonitor as a state machine. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 296

7 May 03, 2004

Page 8

Philips Semiconductors Preliminary User Manual

LPC2119/2129/2194/2292/2294ARM-based Microc ontroller

Figure 55: Exception Handlers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 299

8 May 03, 2004

Page 9

Philips Semiconductors Preliminary User Manual

LPC2119/2129/2194/2292/2294ARM-based Microc ontroller

List of Tables

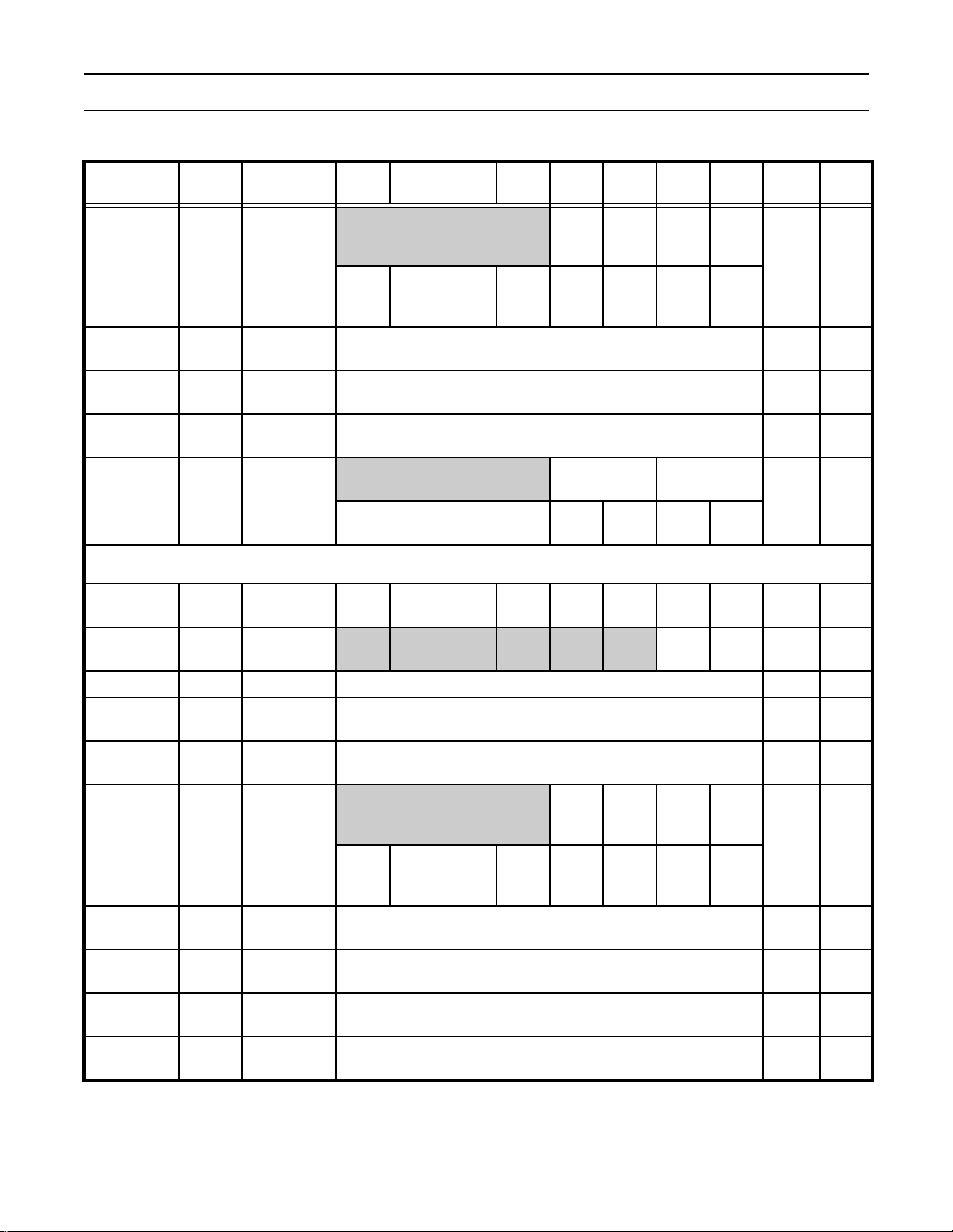

Table 1: LPC2119/2129/2194/2292/2294 device information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Table 2: LPC2119/2129/2194/2292/2294 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

Table 3: ARM Exception Vector Locations. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

Table 4: LPC2119/2129/2194/2292/2294 Memory Mapping Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

Table 5: Address Ranges of External Memory Banks (LPC2292/2294only) . . . . . . . . . . . . . . . . . . . . . . . 56

Table 6: External Memory Controller Pin Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

Table 7: External Memory Controller Register Map. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

Table 8: Bank Configuration Registers 0-3 (BCFG0-3 - 0xFFE00000-0C). . . . . . . . . . . . . . . . . . . . . . . . 58

Table 9: Default memory widths at Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

Table 10: External memory and system requirements. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

Table 11: Pin summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

Table 12: Summary of System Control Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

Table 13: Recommended values for CX1/X2 in oscillation mode

(crystal and external components parameters) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

Table 14: External Interrupt Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

Table 15: External Interrupt Flag Register (EXTINT - 0xE01FC140). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70

Table 16: External Interrupt Wakeup Register (EXTWAKE - 0xE01FC144) . . . . . . . . . . . . . . . . . . . . . . . . 71

Table 17: External Interrupt Mode Register (EXTMODE - 0xE01FC148) . . . . . . . . . . . . . . . . . . . . . . . . . . 71

Table 18: External Interrupt Polarity Register (EXTPOLAR - 0xE01FC14C). . . . . . . . . . . . . . . . . . . . . . . . 72

Table 19: MEMMAP Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 74

Table 20: Memory Mapping Control Register (MEMMAP - 0xE01FC040). . . . . . . . . . . . . . . . . . . . . . . . . . 74

Table 21: PLL Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 75

Table 22: PLL Control Register (PLLCON - 0xE01FC080) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

Table 23: PLL Configuration Register (PLLCFG - 0xE01FC084) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

Table 24: PLL Status Register (PLLSTAT - 0xE01FC088) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 78

Table 25: PLL Control Bit Combinations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 78

Table 26: PLL Feed Register (PLLFEED - 0xE01FC08C). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 79

Table 27: PLL Divider Values. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80

Table 28: PLL Multiplier Values. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80

Table 29: Power Control Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 81

Table 30: Power Control Register (PCON - 0xE01FC0C0). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 82

Table 31: Power Control for Peripherals Register for LPC2119/2129/2292 (PCONP - 0xE01FC0C4) . . . . 82

Table 32: Power Control for Peripherals Register for LPC2194/2294 (PCONP - 0xE01FC0C4) . . . . . . . . 83

Table 33: VPBDIV Register Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 86

Table 34: VPB Divider Register (VPBDIV - 0xE01FC100). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 86

Table 35: MAM Responses to Program Accesses of Various Types. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 92

Table 36: MAM Responses to Data and DMA Accesses of Various Types. . . . . . . . . . . . . . . . . . . . . . . . . 92

Table 37: Summary of System Control Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 93

Table 38: MAM Control Register (MAMCR - 0xE01FC000). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 94

Table 39: MAM Timing Register (MAMTIM - 0xE01FC004) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 94

Table 40: VIC Register Map. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 97

Table 41: Software Interrupt Register (VICSoftInt - 0xFFFFF018, Read/Write) . . . . . . . . . . . . . . . . . . . . . 99

Table 42: Software Interrupt Clear Register (VICSoftIntClear - 0xFFFFF01C, Write Only). . . . . . . . . . . . . 99

Table 43: Raw Interrupt Status Register (VICRawIntr - 0xFFFFF008, Read-Only). . . . . . . . . . . . . . . . . . . 99

Table 44: Interrupt Enable Register (VICINtEnable - 0xFFFFF010, Read/Write) . . . . . . . . . . . . . . . . . . . 100

Table 45: Software Interrupt Clear Register (VICIntEnClear - 0xFFFFF014, Write Only) . . . . . . . . . . . . . 100

Table 46: Interrupt Select Register (VICIntSelect - 0xFFFFF00C, Read/Write) . . . . . . . . . . . . . . . . . . . . 100

Table 47: IRQ Status Register (VICIRQStatus - 0xFFFFF000, Read-Only) . . . . . . . . . . . . . . . . . . . . . . . 100

Table 48: IRQ Status Register (VICFIQStatus - 0xFFFFF004, Read-Only) . . . . . . . . . . . . . . . . . . . . . . . 101

Table 49: Vector Control Registers (VICVectCntl0-15 - 0xFFFFF200-23C, Read/Write) . . . . . . . . . . . . . 101

Table 50: Vector Address Registers (VICVectAddr0-15 - 0xFFFFF100-13C, Read/Write). . . . . . . . . . . . 101

Table 51: Default Vector Address Register (VICDefVectAddr - 0xFFFFF034, Read/Write) . . . . . . . . . . . 101

Table 52: Vector Address Register (VICVectAddr - 0xFFFFF030, Read/Write). . . . . . . . . . . . . . . . . . . . 102

Table 53: Protection Enable Register (VICProtection - 0xFFFFF020, Read/Write). . . . . . . . . . . . . . . . . . 102

Table 54: Connection of Interrupt Sources to the Vectored Interrupt Controller . . . . . . . . . . . . . . . . . . . . 103

9 May 03, 2004

Page 10

Philips Semiconductors Preliminary User Manual

LPC2119/2129/2194/2292/2294ARM-based Microc ontroller

Table 55: Pin description for LPC2119/2129/2194 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 111

Table 56: Pin description for LPC2292/2294 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 117

Table 57: Pin Connect Block Register Map. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 126

Table 58: Pin Function Select Register 0 for LPC2119/2129/2292 (PINSEL0 - 0xE002C000) . . . . . . . . 127

Table 59: Pin Function Select Register 0 for LPC2194/2294 (PINSEL0 - 0xE002C000) . . . . . . . . . . . . . 127

Table 60: Pin Function Select Register 1 for LPC2119/2129/2292 (PINSEL1 - 0xE002C004) . . . . . . . . . 128

Table 61: Pin Function Select Register 1 for LPC2194/2294 (PINSEL1 - 0xE002C004) . . . . . . . . . . . . . 129

Table 62: Pin Function Select Register 2 for LPC2119/2129/2194 (PINSEL2 - 0xE002C014) . . . . . . . . 129

Table 63: Pin Function Select Register 2 for LPC2292/2294 (PINSEL2 - 0xE002C014) . . . . . . . . . . . . . 131

Table 64: Pin Function Select Register Bits. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 132

Table 65: Boot Control on BOOT1:0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 133

Table 66: GPIO Pin Description. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 134

Table 67: GPIO Register Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 135

Table 68: GPIO Pin Value Register (IO0PIN - 0xE0028000, IO1PIN - 0xE0028010,

IO2PIN - 0xE0028020, IO3PIN - 0xE0028030) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 136

Table 69: GPIO Output Set Register (IO0SET - 0xE0028004, IO1SET - 0xE0028014,

IO2SET - 0xE0028024, IO3SET - 0xE0028034) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 136

Table 70: GPIO Output Clear Register (IO0CLR - 0xE002800C, IO1CLR - 0xE002801C,

IO2CLR - 0xE002802C, IO3CLR - 0xE002803C) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 137

Table 71: GPIO Direction Register (IO0DIR - 0xE0028008, IO1DIR - 0xE0028018,

IO2DIR - 0xE0028028, IO3DIR - 0xE0028038). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 137

Table 72: UART0 Pin Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 140

Table 73: UART0 Register Map. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 141

Table 74: UART0 Receiver Buffer Register (U0RBR - 0xE000C000 when DLAB = 0, Read Only). . . . . . 142

Table 75: UART0 Transmit Holding Register (U0THR - 0xE000C000 when DLAB = 0, Write Only). . . . . 142

Table 76: UART0 Divisor Latch LSB Register (U0DLL - 0xE000C000 when DLAB = 1). . . . . . . . . . . . . . 142

Table 77: UART0 Divisor Latch MSB Register (U0DLM - 0xE000C004 when DLAB = 1). . . . . . . . . . . . . 142

Table 78: UART0 Interrupt Enable Register Bit Descriptions (U0IER - 0xE000C004 when DLAB = 0) . . 143

Table 79: UART0 Interrupt Identification Register Bit Descriptions (U0IIR - 0xE000C008, Read Only) . . 143

Table 80: UART0 Interrupt Handling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 144

Table 81: UART0 FIFO Control Register Bit Descriptions (U0FCR - 0xE000C008) . . . . . . . . . . . . . . . . . 145

Table 82: UART0 Line Control Register Bit Descriptions (U0LCR - 0xE000C00C). . . . . . . . . . . . . . . . . . 146

Table 83: UART0 Line Status Register Bit Descriptions (U0LSR - 0xE000C014, Read Only) . . . . . . . . . 147

Table 84: UART0 Scratchpad Register (U0SCR - 0xE000C01C) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 148

Table 85: UART1 Pin Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 152

Table 86: UART1 Register Map. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 153

Table 87: UART1 Receiver Buffer Register (U1RBR - 0xE0010000 when DLAB = 0, Read Only). . . . . . 154

Table 88: UART1 Transmit Holding Register (U1THR - 0xE0010000 when DLAB = 0, Write Only). . . . . 154

Table 89: UART1 Divisor Latch LSB Register (U1DLL - 0xE0010000 when DLAB = 1). . . . . . . . . . . . . . 154

Table 90: UART1 Divisor Latch MSB Register (U1DLM - 0xE0010004 when DLAB = 1). . . . . . . . . . . . . 155

Table 91: UART1 Interrupt Enable Register Bi t Descriptions (U1IER - 0xE0010004 when DLAB = 0). . . 155

Table 92: UART1 Interrupt Identification Register Bit Descriptions (IIR - 0xE0010008, Read Only). . . . . 156

Table 93: UART1 Interrupt Handling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 157

Table 94: UART1 FCR Bit Descriptions (U1FCR - 0xE0010008) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 158

Table 95: UART1 Line Control Register Bit Descriptions (U1LCR - 0xE001000C). . . . . . . . . . . . . . . . . . 159

Table 96: UART1 Modem Control Register Bit Descriptions (U1MCR - 0xE0010010) . . . . . . . . . . . . . . . 160

Table 97: UART1 Line Status Register Bit Descriptions (U1LSR - 0xE0010014, Read Only). . . . . . . . . . 161

Table 98: UART1 Modem Status Register Bit Descriptions (U1MSR - 0x0xE0010018) . . . . . . . . . . . . . . 162

Table 99: UART1 Scratchpad Register (U1SCR - 0xE001001C) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 163

Table 100: I2C Pin Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 170

Table 101: I2C Register Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 171

Table 102: I2C Control Set Register (I2CONSET - 0xE001C000) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 173

Table 103: I2C Control Clear Register (I2CONCLR - 0xE001C018). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 173

Table 104: I2C Status Register (I2STAT - 0xE001C004) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 174

Table 105: I2C Data Register (I2DAT - 0xE001C008) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 174

Table 106: I2C Slave Address Register (I2ADR - 0xE001C00C) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 174

Table 107: I2C SCL High Duty Cycle Register (I2SCLH - 0xE001C010) . . . . . . . . . . . . . . . . . . . . . . . . . . 175

10 May 03, 2004

Page 11

Philips Semiconductors Preliminary User Manual

LPC2119/2129/2194/2292/2294ARM-based Microc ontroller

Table 108: I2C SCL Low Duty Cycle Register (I2SCLL - 0xE001C014). . . . . . . . . . . . . . . . . . . . . . . . . . . 175

Table 109: I2C Clock Rate Selections for VPB Clock Divider = 1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 175

Table 110: I2C Clock Rate Selections for VPB Clock Divider = 2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 176

Table 111: I2C Clock Rate Selections for VPB Clock Divider = 4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 176

Table 112: SPI Data To Clock Phase Relationship. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 179

Table 113: SPI Pin Description. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 182

Table 114: SPI Register Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 183

Table 115: SPI Control Register (S0SPCR - 0xE0020000, S1SPCR - 0xE0030000). . . . . . . . . . . . . . . . . 183

Table 116: SPI Status Register (S0SPSR - 0xE0020004, S1SPSR - 0xE0030004). . . . . . . . . . . . . . . . . . 184

Table 117: SPI Data Register (S0SPDR - 0xE0020008, S1SPDR - 0xE0030008). . . . . . . . . . . . . . . . . . . 184

Table 118: SPI Clock Counter Register (S0SPCCR - 0xE002000C, S1SPCCR - 0xE003000C). . . . . . . . 184

Table 119: SPI Interrupt Register (S0SPINT - 0xE002001C, S1SPINT - 0xE003001C). . . . . . . . . . . . . . . 185

Table 120: CAN Pin Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 189

Table 121: Memory Map of the CAN Block. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 189

Table 122: CAN Acceptance Filter and Central CAN Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 189

Table 123: CAN1, CAN2, CAN3 and CAN4 Controller Register Map. . . . . . . . . . . . . . . . . . . . . . . . . . . . . 190

Table 124: CAN Mode Register (CANMOD - 0xE00x x000). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 192

Table 125: CAN Command Register (CANCMR - 0xE00x x004) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 193

Table 126: CAN Global Status Register (CANGSR - 0xE00x x008). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 194

Table 127: CAN Interrupt and Capture Register (CANICR - 0xE00x x00C) . . . . . . . . . . . . . . . . . . . . . . . . 195

Table 128: CAN Interrupt Enable Register (CANIER - 0xE00x x010). . . . . . . . . . . . . . . . . . . . . . . . . . . . . 196

Table 129: CAN Bus Timing Register (CANBTR - 0xE00x x014). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 197

Table 130: CAN Error Warning Limit Register (CANEWL - 0xE00x x018) . . . . . . . . . . . . . . . . . . . . . . . . . 197

Table 131: CAN Status Register (CANSR - 0xE00x x01C). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 197

Table 132: CAN Rx Frame Status Register (CANRFS - 0xE00x x020) . . . . . . . . . . . . . . . . . . . . . . . . . . . 199

Table 133: CAN Rx Identifier Register when FF=0 (CANRID - 0xE00x x024) . . . . . . . . . . . . . . . . . . . . . . 199

Table 134: CAN Rx Identifier Register when FF=1 (CANRID - 0xE00x x024) . . . . . . . . . . . . . . . . . . . . . . 199

Table 135: CAN Rx Data Register 1 (CANRDA - 0xE00x x028). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 200

Table 136: CAN Rx Data Register B (CANRDB - 0xE00x x02C) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 200

Table 137: CAN Tx Frame Information Register (CANTFI1, 2, 3 - 0xE00x x030, 40, 50). . . . . . . . . . . . . . 201

Table 138: CAN Tx Identifi er Register when FF=0 (CANTID1, 2, 3 - 0xE00x x034, 44, 54). . . . . . . . . . . . 201

Table 139: CAN Tx Identifi er Register when FF=1 (CANTID1, 2, 3 - 0xE00x x034, 44, 54). . . . . . . . . . . . 201

Table 140: CAN Tx Data Register A (CANTDA1, 2, 3 - 0xE00x x038, 48, 58). . . . . . . . . . . . . . . . . . . . . . 202

Table 141: CAN Tx Data Register B (CANTDB1, 2, 3 - 0xE00x x03C, 4C, 5C) . . . . . . . . . . . . . . . . . . . . . 202

Table 142: CAN Central Transmit Status Register (CANTxSR - 0xE004 0000). . . . . . . . . . . . . . . . . . . . . 204

Table 143: CAN Central Receive Status Register (CANRxSR - 0xE004 0004) . . . . . . . . . . . . . . . . . . . . . 204

Table 144: CAN Central Miscellaneous Status Register (CANMSR - 0xE004 0008) . . . . . . . . . . . . . . . . . 205

Table 145: Acceptance Filter Modes Register (AFMR - 0xE003 C000) . . . . . . . . . . . . . . . . . . . . . . . . . . . 207

Table 146: Standard Frame Start Address Register (SFF_sa - 0xE003 C004) . . . . . . . . . . . . . . . . . . . . . 207

Table 147: Standard Frame Group Start Address Reg (SFF_GRP_sa - 0xE003 C008) . . . . . . . . . . . . . . 207

Table 148: Extended Frame Start Address Register (EFF_sa - 0xE003 C00C). . . . . . . . . . . . . . . . . . . . . 208

Table 149: Extended Frame Group Start Addr Register (EFF_GRP_sa - 0xE003 C010). . . . . . . . . . . . . . 208

Table 150: End of AF Tables Register (ENDofTable - 0xE003 C014) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 208

Table 151: LUT Error Address Register (LUTerrAd - 0xE003 C018) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 208

Table 152: LUT Error Register (LUTerr - 0xE003 C01C) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 209

Table 153: Example of Acceptance Filter Tables and ID Index Values. . . . . . . . . . . . . . . . . . . . . . . . . . . . 209

Table 154: Format of Automatically Stored Rx Message . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 211

Table 155: Pin summary. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 215

Table 156: TIMER0 and TIMER1 Register Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 216

Table 157: Interrupt Register

(IR: TIMER0 - T0IR: 0xE0004000; TIMER1 - T1IR: 0xE0008000) . . . . . . . . . . . . . . . . . . . . . . 217

Table 158: Timer Control Register

(TCR: TIMER0 - T0TCR: 0xE0004004; TIMER1 - T1TCR: 0xE0008004). . . . . . . . . . . . . . . . . 217

Table 159: Match Control Register

(MCR: TIMER0 - T0MCR: 0xE0004014; TIMER1 - T1MCR: 0xE0008014). . . . . . . . . . . . . . . . 218

Table 160: Capture Control Register

(CCR: TIMER0 - T0CCR: 0xE0004028; TIMER1 - T1CCR: 0xE0008028) . . . . . . . . . . . . . . . . 219

11 May 03, 2004

Page 12

Philips Semiconductors Preliminary User Manual

LPC2119/2129/2194/2292/2294ARM-based Microc ontroller

Table 161: External Match Register

(EMR: TIMER0 - T0EMR: 0xE000403C; TIMER1 - T1EMR: 0xE000803C) . . . . . . . . . . . . . . . 220

Table 162: External Match Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 220

Table 163: Set and Reset inputs for PWM Flip-Flops. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 227

Table 164: Pin summary. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 229

Table 165: Pulse Width Modulator Register Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 230

Table 166: PWM Interrupt Register (PWMIR - 0xE0014000) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 232

Table 167: PWM Timer Control Register (PWMTCR - 0xE0014004) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 233

Table 168: PWM Match Control Register (PWMMCR - 0xE0014014) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 234

Table 169: PWM Control Register (PWMPCR - 0xE001404C). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 235

Table 170: PWM Latch Enable Register (PWMLER - 0xE0014050). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 236

Table 171: A/D Pin Description. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 238

Table 172: A/D Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 238

Table 173: A/D Control Register (ADCR - 0xE0034000). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 239

Table 174: A/D Data Register (ADDR - 0xE0034004). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 240

Table 175: Real Time Clock Register Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 244

Table 176: Miscellaneous Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 246

Table 177: Interrupt Location Register Bits (ILR - 0xE0024000). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 246

Table 178: Clock Tick Counter Bits (CTC - 0xE0024004). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 246

Table 179: Clock Control Register Bits (CCR - 0xE0024008). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 247

Table 180: Counter Increment Interrupt Register Bits (CIIR - 0xE002400C) . . . . . . . . . . . . . . . . . . . . . . . 247

Table 181: Alarm Mask Register Bits (AMR - 0xE0024010) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 248

Table 182: Consolidated Time Register 0 Bits (CTIME0 - 0xE0024014) . . . . . . . . . . . . . . . . . . . . . . . . . . 249

Table 183: Consolidated Time Register 1 Bits (CTIME1 - 0xE0024018) . . . . . . . . . . . . . . . . . . . . . . . . . . 249

Table 184: Consolidated Time Register 2 Bits (CTIME2 - 0xE002401C) . . . . . . . . . . . . . . . . . . . . . . . . . . 250

Table 185: Time Counter Relationships and Values. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 251

Table 186: Time Counter registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 251

Table 187: Alarm Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 252

Table 188: Reference Clock Divider registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 253

Table 189: Prescaler Integer Register (PREINT - 0xE0024080). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 253

Table 190: Prescaler Fraction Register (PREFRAC - 0xE0024084). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 253

Table 191: Prescaler cases where the Integer Counter reload value is incremented. . . . . . . . . . . . . . . . . 255

Table 192: Watchdog Register Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 257

Table 193: Watchdog Mode Register (WDMOD - 0xE0000000). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 258

Table 194: Watchdog Feed Register (WDFEED - 0xE0000008) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 259

Table 195: Watchdog Timer Value Register (WDTV - 0xE000000C) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 259

Table 196: Sectors in a device with 128K bytes of Flash . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 268

Table 197: ISP Command Summary. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 270

Table 198: ISP Unlock command description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 270

Table 199: ISP Set Baud Rate command description. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 271

Table 200: Correlation between possible ISP baudrates and external crystal frequency (in MHz). . . . . . . 271

Table 201: ISP Echo command description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 271

Table 202: ISP Write to RAM command description. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 272

Table 203: ISP Read Memory command description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 273

Table 204: ISP Prepare sector(s) for write operation command description. . . . . . . . . . . . . . . . . . . . . . . . 274

Table 205: ISP Copy RAM to Flash command description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 274

Table 206: ISP Go command description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 275

Table 207: ISP Erase sector command description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 275

Table 208: ISP Blank check sector(s) command description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 276

Table 209: ISP Read Part ID command description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 276

Table 210: ISP Read Boot Code version command description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 276

Table 211: ISP Compare command description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 277

Table 212: ISP Return Codes Summary. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 278

Table 213: IAP Command Summary. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 280

Table 214: IAP Prepare sector(s) for write operation command description. . . . . . . . . . . . . . . . . . . . . . . . 281

Table 215: IAP Copy RAM to Flash command description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 282

Table 216: IAP Erase Sector(s) command description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 282

12 May 03, 2004

Page 13

Philips Semiconductors Preliminary User Manual

LPC2119/2129/2194/2292/2294ARM-based Microc ontroller

Table 217: IAP Blank check sector(s) command description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 283

Table 218: IAP Read Part ID command description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 283

Table 219: IAP Read Boot Code version command description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 283

Table 220: IAP Compare command description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 284

Table 221: IAP Status Codes Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 284

Table 222: EmbeddedICE Pin Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 287

Table 223: EmbeddedICE Logic Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 288

Table 224: ETM Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 290

Table 225: ETM Pin Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 291

Table 226: ETM Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 292

Table 227: RealMonitor stack requirement . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 298

13 May 03, 2004

Page 14

Philips Semiconductors Preliminary User Manual

LPC2119/2129/2194/2292/2294ARM-based Mic rocontroller

DOCUMENT REVISION HISTORY

2003 Dec 03:

• Prototype LPC2119/2129/2194/2292/2294 User Manual created from the design specification.

2003 Dec 09:

• External Memory Controller and Pin Connect Block chapters updated.

2003 Dec 15/16:

• System Control Block chapter updated.

2003 Dec 18:

• A/D Converter Block chapter updated.

2004 Jan 07:

• CAN and PLL related material updated.

2004 Jan 26:

• System Control Block (Crystal Oscillator section - new frequencies added) and CAN Chapter updated.

2004 Feb 03:

• Introduction chapter (register list) updated.

2004 May 03:

• P0.16 description in "Pin Connect Block" chapter corrected from "Reserved" to "Capture 0.2 (TIMER0)".

• LPC2212 Flash size corrected in "Introduction" chapter corrected from 256 to 128 kB.

• Interrupt source #17 in "Vectored Interrupt Controller (VIC)" corrected from "EINT2" to "EINT3".

• Parallel ports 2 and 3 related registers added to "Introduction" and "GPIO" chapters

• Trigger levels deter mined by bits 7 and 6 in U0 FCR and U1FCR ("UART0" and "UART1" chapters) now showed in both decim al

and hexadecimal notations

• References to DBGSEL pin removed from entire document (pin does not exist in this family of microcontrollers)

• Pin 20 in figure showing 64-pin package ("Pin Configuration" chapter) corrected from "1.3" to "1.31"

•V

replaced with V3A in "A/D Converter" chapter and V3A description updated in "Pin Configuration" chapter

ddA

• Warning on analog input levels added to "A/D Converter" chapter

• On-chip upper RAM boundary corrected from 0x4000 1FFF to 0x4000 3FFF in "LPC2119/2129/2292/2294 Memory

Addressing" chapter

• Port pin tolerance, pull-up presence and voltage considerations added in "Pin Configuration" and "A/D Converter" chapter

• Baudrates in "Flash Memory System and Programming" corrected: 115200 and 230400 instead of 115000 and 230000

• CAN related interrupt sources fixed in "Vectored Interrupt Controller (VIC)" chapter

• ERRBIT field in CANICR CAN register ("Vectored Interrupt Controller (VIC)" chapter) updated

• Number of the on-ch ip Fla sh era se and wr it e c ycles a dde d i nto "Introduction" and "Fl ash M em ory Sy ste m and Prog ram ming"

chapters

• Pins capable of providing an External Interrupt functionality are acounted and listed in "System Control Block" chapter

• Access to ports with respect to GPIO configured pins clarified in "GPIO" and "Pin Connect Block" chapters

• Description of Code Read Protection feature added in "Flash Memory System and Programming" chapter

14 May 03, 2004

Page 15

Philips Semiconductors Preliminary User Manual

LPC2119/2129/2194/2292/2294ARM-based Mic rocontroller

• IOPIN0 and IOPIN1 tyopografic errors corrected in "System Control Block" chapter

• PINSEL2 added to to "Introduction" chapter

• T0IR, T0CCR, T0TCR, T1TCR, T0EMR and PCONP updated in "Introduction" chapter

• EXTMODE and EXTPOLAR registers added in "Introduction" chapter and updated in "System Control Block" chapter

• Power Control Usage Notes for reducing the total power added to "System Control Block" chapter

• PINSEL2 register as well as booting procedure updated in "Pin Connect Block" and "Watchdog" chapters

• references to the pclk in "External Memory Controller (EMC)" chapter corrected to the cclk

• LPC2292/2294 PINSEL2 table in "Pin Connect Block" chapter corrected

• A/D pin description in "A/D Converter" chapter rephrased

• Information on Spurious Interrupts added into "Vectored Interrupt Controller (VIC)" chapter

• Details on the checksum generation in case of Read Memory and Write to RAM ISP commands added in "Flash Memory

System and Programming" chapter

15 May 03, 2004

Page 16

Philips Semiconductors Preliminary User Manual

LPC2119/2129/2194/2292/2294ARM-based Mic rocontroller

1. INTRODUCTION

GENERAL DESCRIPTION

The LPC2119/2129/2194/2292/2294 are based on a 16/32 bit ARM7TDMI-STM CPU with real-time emulation and embedded

trace support, together with 128/256 kilobytes (kB) of embedded high speed flash memory. A 128-bit wide internal memory

interface and a unique accelerator architecture enable 32-bit code execution at maximum clock rate. For critical code size

applications, the alternative 16-bit Thumb Mode reduces code by more than 30% with minimal performance penalty.

With their comapct 64 and 144 pin packages, low power con sumption, various 32 -bit timers, combination of 4-channel 10-bit ADC

and 2/4 advanced CAN channels or 8-channel 10-bit ADC and 2/4 advanced CAN channels (64 and 144 pin packages

respectively), and up to 9 external interrupt pins these microcontrollers are particularly suitable for industrial control, medical

systems, access control and point-of-sale.

Number of availabl e GPIOs goes up to 46 in 64 pin package. In 144 pin packages number of available GPIOs tops 76 (with

external memory i n us e) th rou gh 1 12 (s in gle - ch ip a ppl ic ati on). Being equipped wide ran ge o f se rial co mm unications interfaces ,

they are also very well suited for communication gateways, protocol converters and embedded soft modems as well as many

other general-purpose applications.

FEATURES

• 16/32-bit ARM7TDMI-S microcontroller in a 64 or 144 pin package.

• 16 kB on-chip Static RAM

• 128/256 kB on-chip Flash Progra m Memory (at least 10,000 erat e/write cycles over the whole temperature range). 128-bit wi de

interface/accelerator enables high speed 60 MHz operation.

• External 8, 16 or 32-bit bus (144 pin package only)

• In-System Programming (ISP) and In-Application Programming (IAP) via on-chip boot-loader software. Flash programming

takes 1 ms per 512 byte line. Single sector or full chip erase takes 400 ms.

• EmbeddedICE-RT interface enables breakpoints and watch points. Interrupt service routines can continue to execute whilst

the foreground task is debugged with the on-chip RealMonitor software.

• Embedded Trace Macrocell enables non-intrusive high speed real-time tracing of instruction execution.

• Two/four interconnected CAN interfaces with advanced acceptance filters.

• Four/eight channel (64/144 pin package) 10-bit A/D converter with conversion time as low as 2.44 ms.

• Two 32-bit timers (with 4 capture and 4 compare channels), PWM unit (6 outputs), Real Time Clock and Watchdog.

2

• Multiple serial interfaces including two UARTs (16C550), Fast I

• 60 MHz maximum CPU clock available from programmable on-chip Phase-Locked Loop.

• Vectored Interrupt Controller with configurable priorities and vector addresses.

• Up to forty-six (64 pin) and hundred-twelve (144 pin package) 5 V tolerant general purpose I/O pins. Up to 12 independent

external interrupt pins available (EIN and CAP functions).

• On-chip crystal oscillator with an operating range of 1 MHz to 30 MHz.

• Two low power modes, Idle and Power-down.

• Processor wake-up from Power-down mode via external interrupt.

• Individual enable/disable of peripheral functions for power optimization.

• Dual power supply.

- CPU operating voltage range of 1.65V to 1.95V (1.8V +/- 8.3%).

- I/O power supply range of 3.0V to 3.6V (3.3V +/- 10%).

C (400 kbits/s) and two SPIs™.

Introduction 16 May 03, 2004

Page 17

Philips Semiconductors Preliminary User Manual

LPC2119/2129/2194/2292/2294ARM-based Mic rocontroller

APPLICATIONS

• Industrial control

• Medical systems

• Access control

• Point-of-sale

• Communication gateway

• Embedded soft modem

• general purpose applicatio ns

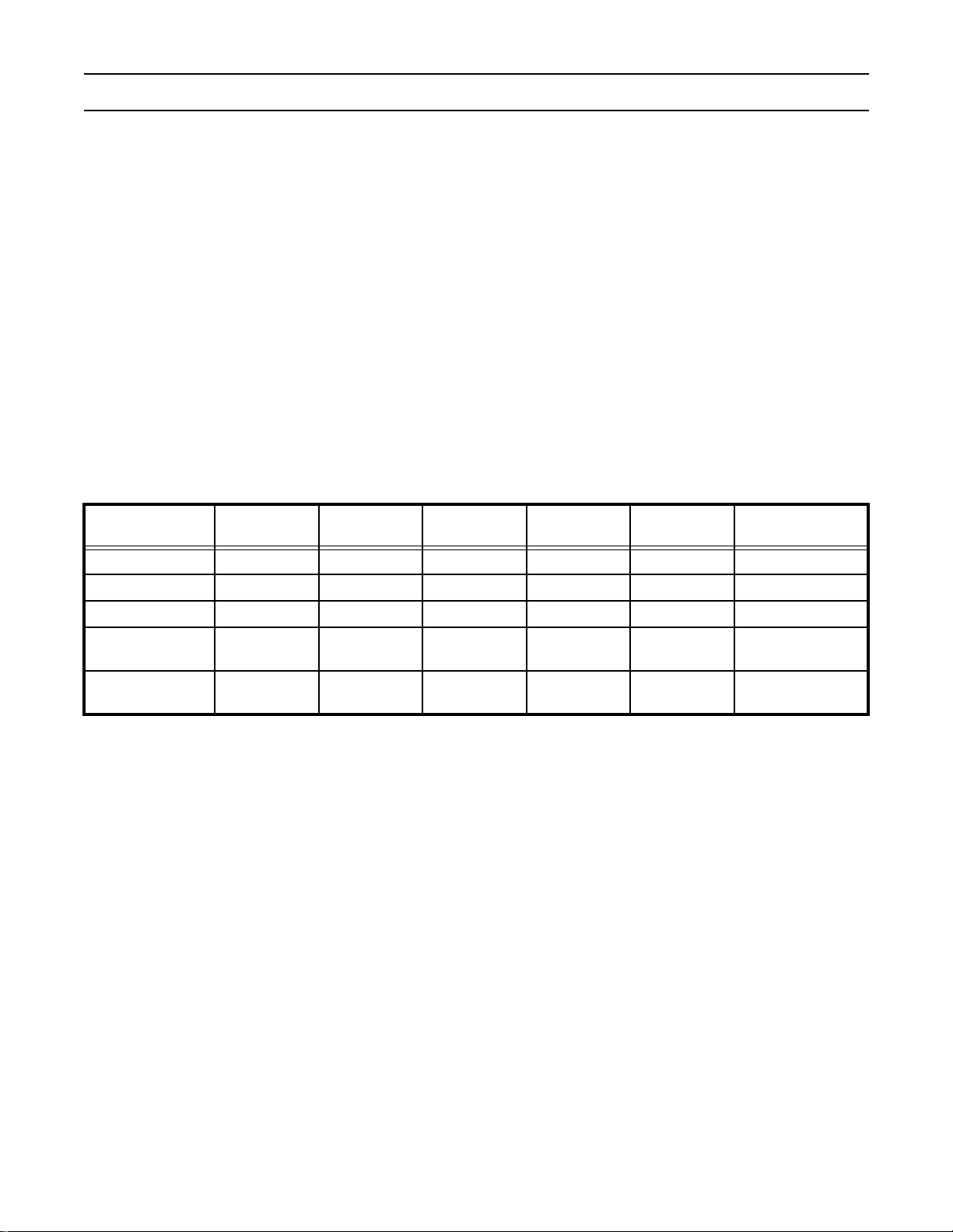

DEVICE INFORMATION

Table 1: LPC2119/2129/2194/2292/2294 device information

Device No. of pins On-chip RAM

LPC2119 64 16 kB 128 kB 2 4 LPC2129 64 16 kB 256 kB 2 4 LPC2194 64 16 kB 256 kB 4 4 -

LPC2292 144 16 kB 256 kB 2 8

LPC2294 144 16 kB 256 kB 4 8

On-chip

FLASH

No. of CAN

channels

No. of 10-bit

AD Channels

Note

with external

memory interface

with external

memory interface

Introduction 17 May 03, 2004

Page 18

Philips Semiconductors Preliminary User Manual

LPC2119/2129/2194/2292/2294ARM-based Mic rocontroller

ARCHITECTURAL OVERVIEW

The LPC2119/2129/2194 /2292/2294 consist s of an ARM7TDMI-S CPU with emulati on support, the ARM7 Local Bus for interface

to on-chip memory contro llers, the AMBA Ad vanced High-performanc e Bus (AHB) for interf ace to the inte rrupt controller, a nd the

VLSI Peripheral Bus (VPB, a comp atible superset of ARM’s AMBA Advanced Peripheral Bu s) for connection to on-c hip peripheral

functions. The LPC2119/2129/2194/2292/2294 configures the ARM7TDMI-S processor in little-endian byte order.

AHB peripherals are allocated a 2 megabyte range of addresses at the very top of the 4 gigabyte ARM memory space. Each

AHB peripheral is allocated a 16 kilobyte address space within the AHB address space. LPC2119/2129/2194/2292/2294

peripheral functions (other than the interrupt controller) are connected to the VPB bus. The AHB to VPB bridge interfaces the

VPB bus to the AHB bus. VPB peripherals are also allocated a 2 megabyte range of addresses, beginning at the 3.5 gigabyte

address point. Each VPB peripheral is allocated a 16 kilobyte address space within the VPB address space.

The connection of on-chip pe ripherals to d evice pins i s controlled by a Pin Conne ction Block. This must be configured by software

to fit specific application requirements for the use of peripheral functions and pins.

ARM7TDMI-S PROCESSOR

The ARM7TDMI-S is a general purpose 32-bit microproce ssor, which offers high perfo rmance and very low pow er consumption .

The ARM architecture is based on Reduced Instruction Set Computer (RISC) principles, and the instruction set and related

decode mechanism are much simpler than those of microprogrammed Complex Instruction Set Computers. This simplicity

results in a high instruction throughput and impressive real-time interrupt response from a small and cost-effective processor

core.

Pipeline techniques are em plo ye d so tha t all parts of the processing and memory sy stems can operate continuou sly. Typically,

while one instruction is being executed, its successor is being decoded, and a third instruction is being fetched from memory.

The ARM7TDMI-S processor also employs a unique architectural strategy known as THUMB, which makes it ideally suited to

high-volume applications with memory restrictions, or applications where code density is an issue.

The key idea behind THUMB is that of a super-reduced instruction set. Essentially, the ARM7TDMI-S processor has two

instruction sets:

• The standard 32-bit ARM instruction set.

• A 16-bit THUMB instruction se t.

The THUMB set’s 16-bit ins truc tio n l eng th al lo ws it to ap proa ch tw ic e th e de ns ity of s tan dard AR M c ode while retaining most of

the ARM’s performance advantage over a traditional 16-bit processor using 16-bit registers. This is possible because THUMB

code operates on the same 32-bit register set as ARM code.

THUMB code is able to provide up to 65% of the code size of ARM, and 160% of the performance of an equivalent ARM

processor connected to a 16-bit memory system.

The ARM7TDMI-S processor is described in detail in the ARM7TDMI-S Datasheet that can be found on official ARM website.

ON-CHIP FLASH MEMORY SYSTEM

The LPC2219 incorporat e a 128 kB Flash m emory system, while LPC2129/ 2194/2292 /2294 incorpo rate a 256 kB Flash memory

system. This mem ory ma y be u sed fo r both c ode an d data storage . Program ming of the Flash memo ry may be ac comp lishe d in

several ways: over the serial built-in JTAG interface, using In System Programming (ISP) and UART0, or by means of In

Application Programmi ng (IAP) capabilities. Th e application pro gram, using the In Appli cation Programmin g (IAP) functions, may

also erase and/or program the Flash while the application is running, allowing a great degree of flexibility for data storage field

firmware up grades, etc.

Introduction 18 May 03, 2004

Page 19

Philips Semiconductors Preliminary User Manual

LPC2119/2129/2194/2292/2294ARM-based Mic rocontroller

ON-CHIP STATIC RAM

The LPC2119/2129/2194/2292/2294 provide a 16 kB static RAM memory that may be used for code and/or data storage. The

SRAM supports 8-bit, 16-bit, and 32-bit accesses.

The SRAM controller inc orpo rate s a wri te-b ac k bu ffer i n ord er to p rev ent CPU stalls during back-to-back writes. The write-back

buffer always holds the last data sent by software to the SRAM. This data is only written to the SRAM when another write is