Page 1

INTEGRATED CIRCUITS

LPC2106/2105/2104 USER MANUAL

Preliminary

Supersedes data of 2003 Sep 17

2003 Oct 02

Page 2

Philips Semiconductors Preliminary User Manual

LPC2106/2105//2104ARM-based Microc ontroller

2 October 02, 2003

Page 3

Philips Semiconductors Preliminary User Manual

LPC2106/2105/2104ARM-based Microcontroller

Table of Contents

List of Figures . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

List of Tables . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Document Revision History . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

Applications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

Architectural Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

ARM7TDMI-S Processor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

On-Chip Flash Memory System . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

On-Chip Static RAM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

LPC2106/2105/2104 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

LPC2106/2105/2104 Memory Addressing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

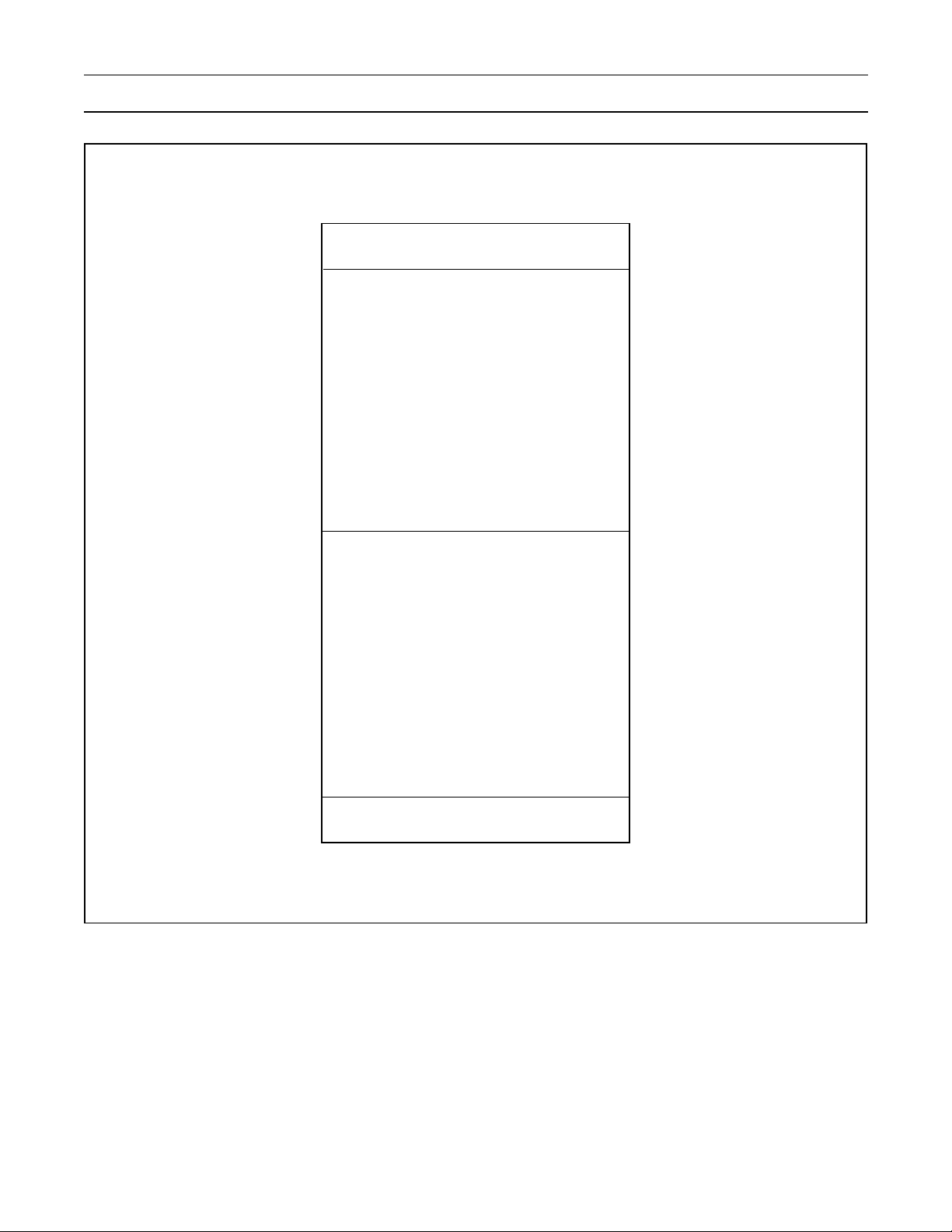

Memory Maps . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

LPC2106/2105/2104 Memory Re-mapping and Boot Block . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

Prefetch Abort and Data Abort Exceptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

System Control Block . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

Summary of System Control Block Functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

Pin Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

Register Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

Crystal Oscillator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

External Interrupt Inputs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

Memory Mapping Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

PLL (Phase Locked Loop) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

Power Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

VPB Divider . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

Wakeup Timer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

Memory Accelerator Module (MAM) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

Memory Accelerator Module Operating Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

MAM Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

Register Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

MAM Usage Notes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

Vectored Interrupt Controller (VIC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

Register Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

VIC Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

Interrupt Sources . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

VIC Usage Notes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70

Pin Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

LPC2106/2105/2104 Pinout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

LPC2106/2105/2104 Pin functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 72

Pin Description for LPC2106/2105/2104 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

3 October 02, 2003

Page 4

Philips Semiconductors Preliminary User Manual

LPC2106/2105/2104ARM-based Microcontroller

Pin Connect Block . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

Applications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

Register Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

GPIO . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 81

Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 81

Applications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 81

Pin Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 81

Register Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 81

GPIO Usage Notes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83

UART 0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 85

Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 85

Pin Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 85

Register Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 86

Architecture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 94

UART 1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 97

Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 97

Pin Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 97

Register Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98

Architecture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 109

I2C Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 111

Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 111

Applications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 111

Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 111

Pin Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 115

Register Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 116

Architecture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 122

SPI Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 123

Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 123

Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 123

Pin Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 127

Register Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 128

Architecture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 131

Timer 0 and Timer 1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 133

Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 133

Applications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 133

Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 134

Pin Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 134

Register Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 135

Example Timer Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 140

Architecture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 141

Pulse Width Modulator (PWM) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 143

Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 143

Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 143

Pin Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 148

Register Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 149

4 October 02, 2003

Page 5

Philips Semiconductors Preliminary User Manual

LPC2106/2105/2104ARM-based Microcontroller

Real Time Clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 157

Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 157

Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 157

Architecture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 158

Register Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 158

RTC Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 160

Miscellaneous Register Group . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 161

Consolidated Time Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 164

Time Counter Group . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 166

Alarm Register Group . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 167

RTC Usage Notes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 167

Reference Clock Divider (Prescaler) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 168

Watchdog . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 171

Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 171

Applications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 171

Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 171

Register Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 172

Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 175

Flash Memory System and Programming . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 177

Flash Memory System . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 177

Flash boot Loader . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 177

Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 177

Applications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 177

Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 177

Boot process FlowChart . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 182

Sector Numbers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 183

JTAG FLASH Programming interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 199

EmbeddedICE Logic . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 201

Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 201

Applications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 201

Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 201

Pin Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 202

Register Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 203

Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 204

Debug Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 205

Embedded Trace Macrocell . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 207

Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 207

Applications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 207

Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 207

Pin Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 208

Register Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 209

Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 210

RealMonitor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 211

Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 211

Applications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 211

Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 211

How to Enable RealMonitor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 215

RealMonitor build options . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 221

5 October 02, 2003

Page 6

Philips Semiconductors Preliminary User Manual

LPC2106/2105/2104ARM-based Microcontroller

6 October 02, 2003

Page 7

Philips Semiconductors Preliminary User Manual

LPC2106/2105/2104ARM-based Microcontroller

List of Figures

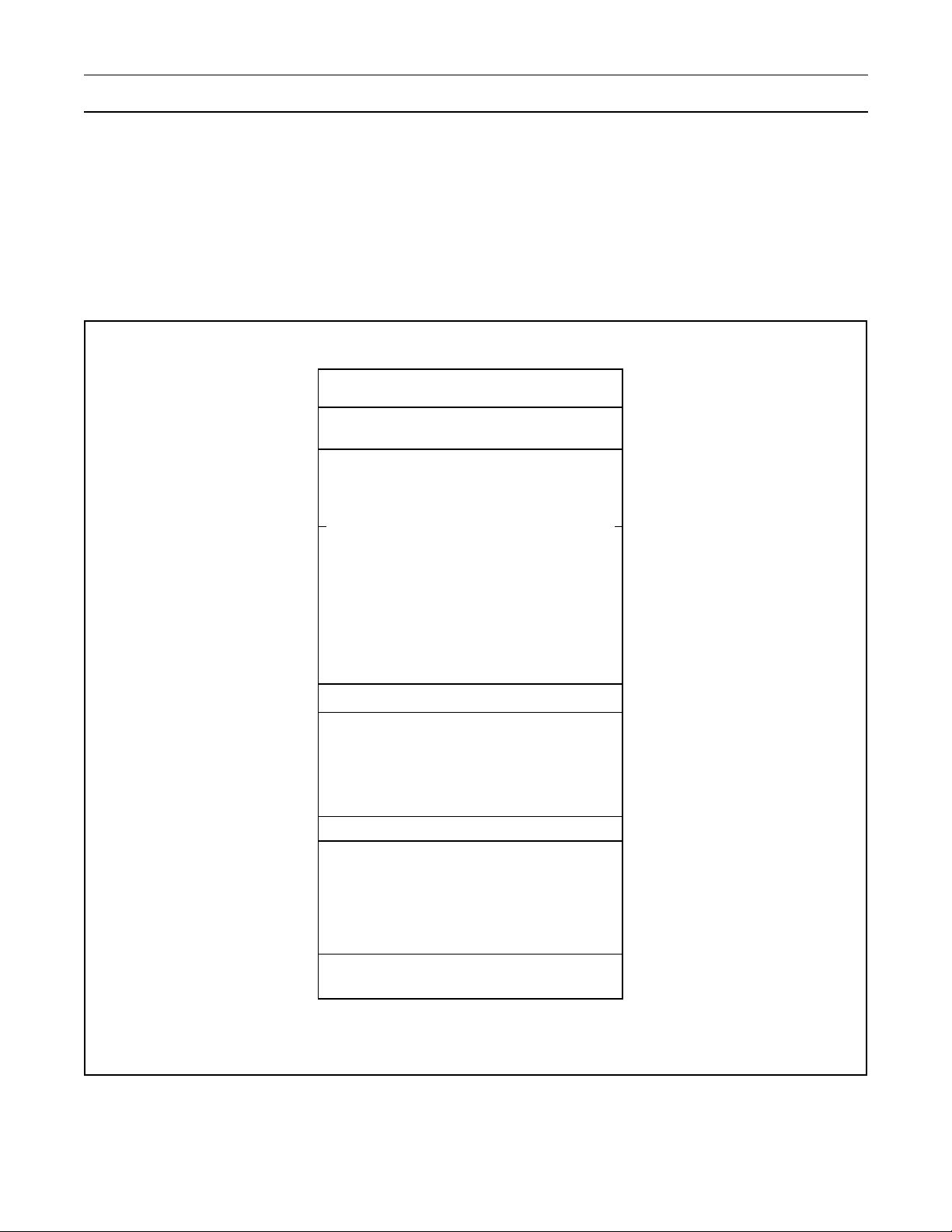

Figure 1: LPC2106/2105/2104 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

Figure 2: System Memory Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

Figure 3: Peripheral Memory Map. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

Figure 4: AHB Peripheral Map. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

Figure 5: VPB Peripheral Map. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

Figure 6: Map of lower memory is showing re-mapped and re-mappable areas. . . . . . . . . . . . . . . . . . . . 35

Figure 7: Oscillator modes and models: a) slave mode of operation, b) oscillation mode of operation,

c) external crystal model used for CX1/X2 evaluation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

Figure 8: External Interrupt Logic. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

Figure 9: PLL Block Diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

Figure 10: Reset Block Diagram including Wakeup Timer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

Figure 11: VPB Divider Connections . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

Figure 12: Simplified Block Diagram of the Memory Accelerator Module . . . . . . . . . . . . . . . . . . . . . . . . . . 56

Figure 13: Block Diagram of the Vectored Interrupt Controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

Figure 14: LPC2106/2105/2104 48-pin package (LQFP48) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

Figure 15: UART0 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 95

Figure 16: UART1 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 110

Figure 17: I2C Bus Configuration. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 112

Figure 18: Slave Mode Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 112

Figure 19: Format in the master transmitter mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 113

Figure 20: Format of master receiver mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 113

Figure 21: A master receiver switch to master transmitter after sending repeated START. . . . . . . . . . . . 114

Figure 22: Slave Mode Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 114

Figure 23: Format of slave receiver mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 115

Figure 24: Format of slave transmitter mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 115

Figure 25: I2C Architecture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 122

Figure 26: SPI Data Transfer Format (CPHA = 0 and CPHA = 1). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 124

Figure 27: SPI Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 131

Figure 28: A timer cycle in which PR=2, MRx=6, and both interrupt and reset on match are enabled.. . . 140

Figure 29: A timer cycle in which PR=2, MRx=6, and both interrupt and stop on match are enabled. . . . 140

Figure 30: Timer block diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 141

Figure 31: PWM block diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 145

Figure 32: Sample PWM waveforms . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 146

Figure 33: RTC block diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 158

Figure 34: RTC Prescaler block diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 169

Figure 35: Watchdog Block Diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 175

Figure 36: Flash Sector Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 178

Figure 37: Map of lower memory after any reset. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 179

Figure 38: Boot Process flowchart. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 182

Figure 39: IAP Parameter passing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 195

Figure 40: EmbeddedICE Debug Environment Block Diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 204

Figure 41: Waveforms for normal operation (not in debug mode). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 205

Figure 42: Waveforms for Debug mode using the primary JTAG pins. . . . . . . . . . . . . . . . . . . . . . . . . . . . 206

Figure 43: ETM Debug Environment Block Diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 210

Figure 44: RealMonitor components . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 212

Figure 45: RealMonitor as a state machine. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 213

Figure 46: Exception Handlers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 216

7 October 02, 2003

Page 8

Philips Semiconductors Preliminary User Manual

LPC2106/2105/2104ARM-based Microcontroller

8 October 02, 2003

Page 9

Philips Semiconductors Preliminary User Manual

LPC2106/2105/2104ARM-based Microcontroller

List of Tables

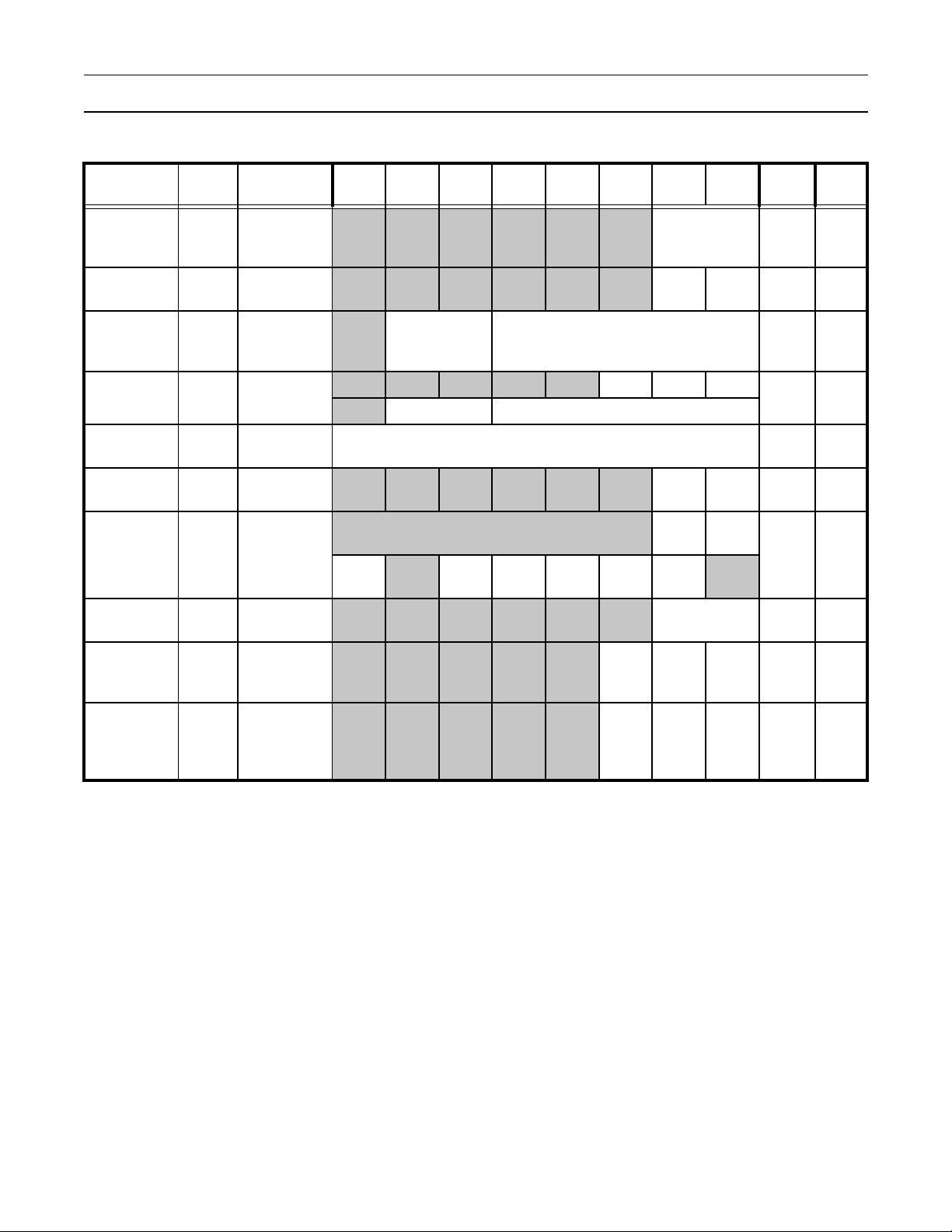

Table 1: LPC2106/2105/2104 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Table 2: ARM Exception Vector Locations. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

Table 3: LPC2106/2105/2104 Memory Mapping Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

Table 4: Pin summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

Table 5: Summary of System Control Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

Table 6: Recommended values for CX1/X2 when oscillation mode is used . . . . . . . . . . . . . . . . . . . . . . . 39

Table 7: External Interrupt Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

Table 8: External Interrupt Flag Register (EXTINT - 0xE01FC140). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

Table 9: External Interrupt Wakeup Register (EXTWAKE - 0xE01FC144) . . . . . . . . . . . . . . . . . . . . . . . . 41

Table 10: MEMMAP Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

Table 11: Memory Mapping Control Register (MEMMAP - 0xE01FC040). . . . . . . . . . . . . . . . . . . . . . . . . . 42

Table 12: PLL Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

Table 13: PLL Control Register (PLLCON - 0xE01FC080) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

Table 14: PLL Configuration Register (PLLCFG - 0xE01FC084) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

Table 15: PLL Status Register (PLLSTAT - 0xE01FC088) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

Table 16: PLL Control Bit Combinations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

Table 17: PLL Feed Register (PLLFEED - 0xE01FC08C). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

Table 18: PLL Divider Values. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

Table 19: PLL Multiplier Values. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

Table 20: Power Control Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

Table 21: Power Control Register (PCON - 0xE01FC0C0) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

Table 22: Power Control for Peripherals Register (PCONP - 0xE01FC0C4). . . . . . . . . . . . . . . . . . . . . . . . 50

Table 23: VPBDIV Register Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

Table 24: VPB Divider Register (VPBDIV - 0xE01FC100). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

Table 25: MAM Responses to Program Accesses of Various Types. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

Table 26: MAM Responses to Data and DMA Accesses of Various Types. . . . . . . . . . . . . . . . . . . . . . . . . 57

Table 27: Summary of System Control Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

Table 28: MAM Control Register (MAMCR - 0xE01FC000). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

Table 29: MAM Timing Register (MAMTIM - 0xE01FC004) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

Table 30: VIC Register Map. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

Table 31: Software Interrupt Register (VICSoftInt - 0xFFFFF018, Read/Write) . . . . . . . . . . . . . . . . . . . . . 64

Table 32: Software Interrupt Clear Register (VICSoftIntClear - 0xFFFFF01C, Write Only). . . . . . . . . . . . . 64

Table 33: Raw Interrupt Status Register (VICRawIntr - 0xFFFFF008, Read-Only). . . . . . . . . . . . . . . . . . . 64

Table 34: Interrupt Enable Register (VICINtEnable - 0xFFFFF010, Read/Write) . . . . . . . . . . . . . . . . . . . . 65

Table 35: Software Interrupt Clear Register (VICIntEnClear - 0xFFFFF014, Write Only) . . . . . . . . . . . . . . 65

Table 36: Interrupt Select Register (VICIntSelect - 0xFFFFF00C, Read/Write) . . . . . . . . . . . . . . . . . . . . . 65

Table 37: IRQ Status Register (VICIRQStatus - 0xFFFFF000, Read-Only) . . . . . . . . . . . . . . . . . . . . . . . . 65

Table 38: IRQ Status Register (VICFIQStatus - 0xFFFFF004, Read-Only) . . . . . . . . . . . . . . . . . . . . . . . . 66

Table 39: Vector Control Registers (VICVectCntl0-15 - 0xFFFFF200-23C, Read/Write) . . . . . . . . . . . . . . 66

Table 40: Vector Address Registers (VICVectAddr0-15 - 0xFFFFF100-13C, Read/Write) . . . . . . . . . . . . . 66

Table 41: Default Vector Address Register (VICDefVectAddr - 0xFFFFF034, Read/Write) . . . . . . . . . . . . 66

Table 42: Vector Address Register (VICVectAddr - 0xFFFFF030, Read/Write). . . . . . . . . . . . . . . . . . . . . 67

Table 43: Protection Enable Register (VICProtection - 0xFFFFF020, Read/Write). . . . . . . . . . . . . . . . . . . 67

Table 44: Connection of Interrupt Sources to the Vectored Interrupt Controller . . . . . . . . . . . . . . . . . . . . . 68

Table 45: Pin description for LPC2106/2105/2104 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 72

Table 46: Pin description and corresponding functions for LPC2106/2105/2104 . . . . . . . . . . . . . . . . . . . . 73

Table 47: Pin Connect Block Register Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

Table 48: Pin Function Select Register 0 (PINSEL0 - 0xE002C000). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 78

Table 49: Pin Function Select Register 1 (PINSEL1 - 0xE002C004). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 79

Table 50: Pin Function Select Register Bits. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 79

Table 51: GPIO Pin Description. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 81

Table 52: GPIO Register Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 81

Table 53: GPIO Pin Value Register (IOPIN - 0xE0028000). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 82

Table 54: GPIO Output Set Register (IOSET - 0xE0028004) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 82

Table 55: GPIO Output Clear Register (IOCLR - 0xE002800C) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 82

9 October 02, 2003

Page 10

Philips Semiconductors Preliminary User Manual

LPC2106/2105/2104ARM-based Microcontroller

Table 56: GPIO Direction Register (IODIR - 0xE0028008) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 82

Table 57: UART 0 Pin Description. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 85

Table 58: UART 0 Register Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 86

Table 59: UART0 Receiver Buffer Register (U0RBR - 0xE000C000 when DLAB = 0, Read Only). . . . . . . 87

Table 60: UART0 Transmit Holding Register (U0THR - 0xE000C000 when DLAB = 0, Write Only). . . . . . 87

Table 61: UART0 Divisor Latch LSB Register (U0DLL - 0xE000C000 when DLAB = 1). . . . . . . . . . . . . . . 87

Table 62: UART0 Divisor Latch MSB Register (U0DLM - 0xE000C004 when DLAB = 1). . . . . . . . . . . . . . 87

Table 63: UART0 Interrupt Enable Register Bit Descriptions (U0IER - 0xE000C004 when DLAB = 0) . . . 88

Table 64: UART0 Interrupt Identification Register Bit Descriptions (U0IIR - 0xE000C008, Read Only) . . . 88

Table 65: UART0 Interrupt Handling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 89

Table 66: UART0 FIFO Control Register Bit Descriptions (U0FCR - 0xE000C008) . . . . . . . . . . . . . . . . . . 90

Table 67: UART0 Line Control Register Bit Descriptions (U0LCR - 0xE000C00C). . . . . . . . . . . . . . . . . . . 91

Table 68: UART0 Line Status Register Bit Descriptions (U0LSR - 0xE000C014, Read Only) . . . . . . . . . . 92

Table 69: UART0 Scratchpad Register (U0SCR - 0xE000C01C) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 93

Table 70: UART1 Pin Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 97

Table 71: UART 1 Register Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98

Table 72: UART1 Receiver Buffer Register (U1RBR - 0xE0010000 when DLAB = 0, Read Only). . . . . . . 99

Table 73: UART1 Transmit Holding Register (U1THR - 0xE0010000 when DLAB = 0, Write Only). . . . . . 99

Table 74: UART1 Divisor Latch LSB Register (U1DLL - 0xE0010000 when DLAB = 1). . . . . . . . . . . . . . . 99

Table 75: UART1 Divisor Latch MSB Register (U1DLM - 0xE0010004 when DLAB = 1). . . . . . . . . . . . . 100

Table 76: UART1 Interrupt Enable Register Bit Descriptions (U1IER - 0xE0010004 when DLAB = 0). . . 100

Table 77: UART1 Interrupt Identification Register Bit Descriptions (IIR - 0xE0010008, Read Only). . . . . 101

Table 78: UART1 Interrupt Handling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 102

Table 79: UART1 FCR Bit Descriptions (U1FCR - 0xE0010008) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 103

Table 80: UART1 Line Control Register Bit Descriptions (U1LCR - 0xE001000C). . . . . . . . . . . . . . . . . . 104

Table 81: UART1 Modem Control Register Bit Descriptions (U1MCR - 0xE0010010) . . . . . . . . . . . . . . . 105

Table 82: UART1 Line Status Register Bit Descriptions (U1LSR - 0xE0010014, Read Only). . . . . . . . . . 106

Table 83: UART1 Modem Status Register Bit Descriptions (U1MSR - 0x0xE0010018) . . . . . . . . . . . . . . 107

Table 84: UART1 Scratchpad Register (U1SCR - 0xE001001C) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 108

Table 85: I2C Pin Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 115

Table 86: I2C Register Map. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 116

Table 87: I2C Control Set Register (I2CONSET - 0xE001C000) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 118

Table 88: I2C Control Clear Register (I2CONCLR - 0xE001C018) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 118

Table 89: I2C Status Register (I2STAT - 0xE001C004) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 119

Table 90: I2C Data Register (I2DAT - 0xE001C008). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 119

Table 91: I2C Slave Address Register (I2ADR - 0xE001C00C) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 119

Table 92: I2C SCL High Duty Cycle Register (I2SCLH - 0xE001C010) . . . . . . . . . . . . . . . . . . . . . . . . . . 120

Table 93: I2C SCL Low Duty Cycle Register (I2SCLL - 0xE001C014) . . . . . . . . . . . . . . . . . . . . . . . . . . . 120

Table 94: I2C Clock Rate Selections for VPB Clock Divider = 1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 120

Table 95: I2C Clock Rate Selections for VPB Clock Divider = 2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 121

Table 96: I2C Clock Rate Selections for VPB Clock Divider = 4 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 121

Table 97: SPI Data To Clock Phase Relationship . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 124

Table 98: SPI Pin Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 127

Table 99: SPI Register Map. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 128

Table 100: SPI Control Register (SPCR - 0xE0020000). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 128

Table 101: SPI Status Register (SPSR - 0xE0020004). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 129

Table 102: SPI Data Register (SPDR - 0xE0020008). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 129

Table 103: SPI Clock Counter Register (SPCCR - 0xE002000C). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 129

Table 104: SPI Interrupt Register (SPINT - 0xE002001C) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 130

Table 105: Pin summary. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 134

Table 106: Timer 0 and Timer 1 Register Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 135

Table 107: Interrupt Register

(IR: Timer 0 - T0IR: 0xE0004000; Timer 1 - T1IR: 0xE0008000) . . . . . . . . . . . . . . . . . . . . . . . 136

Table 108: Timer Control Register

(TCR: Timer 0 - T0TCR: 0xE0004004; Timer 1 - T1TCR: 0xE0008004). . . . . . . . . . . . . . . . . . 136

Table 109: Match Control Register

(MCR: Timer 0 - T0MCR: 0xE0004014; Timer 1 - T1MCR: 0xE0008014). . . . . . . . . . . . . . . . . 137

10 October 02, 2003

Page 11

Philips Semiconductors Preliminary User Manual

LPC2106/2105/2104ARM-based Microcontroller

Table 110: Capture Control Register

(CCR: Timer 0 - T0CCR: 0xE0004028; Timer 1 - T1CCR: 0xE0008028) . . . . . . . . . . . . . . . . . 138

Table 111: External Match Register

(EMR: Timer 0 - T0EMR: 0xE000403C; Timer 1 - T1EMR: 0xE000803C) . . . . . . . . . . . . . . . . 139

Table 112: External Match Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 139

Table 113: Set and Reset inputs for PWM Flip-Flops. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 146

Table 114: Pin summary. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 148

Table 115: Pulse Width Modulator Register Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 149

Table 116: PWM Interrupt Register (PWMIR - 0xE0014000) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 151

Table 117: PWM Timer Control Register (PWMTCR - 0xE0014004) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 152

Table 118: PWM Match Control Register (PWMMCR - 0xE0014014) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 153

Table 119: PWM Control Register (PWMPCR - 0xE001404C). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 154

Table 120: PWM Latch Enable Register (PWMLER - 0xE0014050). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 155

Table 121: Real Time Clock Register Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 159

Table 122: Miscellaneous Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 161

Table 123: Interrupt Location Register Bits (ILR - 0xE0024000). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 161

Table 124: Clock Tick Counter Bits (CTC - 0xE0024004). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 161

Table 125: Clock Control Register Bits (CCR - 0xE0024008). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 162

Table 126: Counter Increment Interrupt Register Bits (CIIR - 0xE002400C) . . . . . . . . . . . . . . . . . . . . . . . 162

Table 127: Alarm Mask Register Bits (AMR - 0xE0024010). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 163

Table 128: Consolidated Time Register 0 Bits (CTIME0 - 0xE0024014) . . . . . . . . . . . . . . . . . . . . . . . . . . 164

Table 129: Consolidated Time Register 1 Bits (CTIME1 - 0xE0024018) . . . . . . . . . . . . . . . . . . . . . . . . . . 164

Table 130: Consolidated Time Register 2 Bits (CTIME2 - 0xE002401C) . . . . . . . . . . . . . . . . . . . . . . . . . . 165

Table 131: Time Counter Relationships and Values. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 166

Table 132: Time Counter registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 166

Table 133: Alarm Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 167

Table 134: Reference Clock Divider registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 168

Table 135: Prescaler Integer Register (PREINT - 0xE0024080). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 168

Table 136: Prescaler Fraction Register (PREFRAC - 0xE0024084). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 168

Table 137: Watchdog Register Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 172

Table 138: Watchdog Mode Register (WDMOD - 0xE0000000). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 173

Table 139: Watchdog Feed Register (WDFEED - 0xE0000008) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 174

Table 140: Watchdog Timer Value Register (WDTV - 0xE000000C) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 174

Table 141: Sectors in a device with 128K bytes of Flash . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 183

Table 142: ISP Command Summary. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 184

Table 143: ISP Unlock command description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 184

Table 144: ISP Set Baud Rate command description. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 185

Table 145: Correlation between possible ISP baudrates and external crystal frequency (in MHz). . . . . . . 185

Table 146: ISP Echo command description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 186

Table 147: ISP Write to RAM command description. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 187

Table 148: ISP Read Memory command description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 187

Table 149: ISP Prepare sector(s) for write operation command description. . . . . . . . . . . . . . . . . . . . . . . . 188

Table 150: ISP Copy RAM to Flash command description. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 188

Table 151: ISP Go command description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 189

Table 152: ISP Erase sector command description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 189

Table 153: ISP Blank check sector(s) command description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 190

Table 154: ISP Read Part ID command description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 190

Table 155: ISP Read Boot Code version command description. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 190

Table 156: ISP Compare command description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 191

Table 157: ISP Return Codes Summary. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 192

Table 158: IAP Command Summary. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 194

Table 159: IAP Prepare sector(s) for write operation command description. . . . . . . . . . . . . . . . . . . . . . . . 195

Table 160: IAP Copy RAM to Flash command description. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 196

Table 161: IAP Erase Sector(s) command description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 196

Table 162: IAP Blank check sector(s) command description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 197

Table 163: IAP Read Part ID command description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 197

Table 164: IAP Read Boot Code version command description. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 197

11 October 02, 2003

Page 12

Philips Semiconductors Preliminary User Manual

LPC2106/2105/2104ARM-based Microcontroller

Table 165: IAP Compare command description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 198

Table 166: IAP Status Codes Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 198

Table 167: EmbeddedICE Pin Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 202

Table 168: EmbeddedICE Logic Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 203

Table 169: JTAG Pins Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 206

Table 170: ETM Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 207

Table 171: ETM Pin Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 208

Table 172: ETM Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 209

Table 173: RealMonitor stack requirement . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 215

12 October 02, 2003

Page 13

Philips Semiconductors Preliminary User Manual

LPC2106/2105/2104ARM-based Microcontroller

DOCUMENT REVISION HISTORY

May, 2003:

• Prototype LPC2106/2105/2104 User Manual created from the design specification.

July, 2003:

• Flash Programming chapter added.

• Memory Accelerator Module chapter added.

• Register names in UARTs and timers updated.

• List of all registers added in the Introduction chapter.

• Pin Configuration chapter added.

August, 2003:

• MAM, VIC, GPIO, and RTC Usage Notes added.

• EmbeddedICE chapter updated.

September, 2003:

• Details on JTAG ports added in the EmbeddedICE chapter.

• Details on crystal oscillator added in the System Control Block chapter.

• List of possible baudrates when ISP is used added in the Flash Memory System and Programming chapter.

• Details on reset timing requirem en ts add ed in the Sys tem Control Block, Reset chapter.

October, 2003:

• Number of Flash erase and write cycel is added in the Introduction chapter.

13 October 02, 2003

Page 14

Philips Semiconductors Preliminary User Manual

LPC2106/2105/2104ARM-based Microcontroller

14 October 02, 2003

Page 15

Philips Semiconductors Preliminary User Manual

LPC2106/2105/2104ARM-based Microcontroller

1. INTRODUCTION

FEATURES

• ARM7TDMI-S processor.

• 128 kilobyte on-chip Flash Program Memory with In-System Programming (ISP) and In-Application Programming (IAP)

capability. Flash programming time is 1 ms for up to a 512 byte line. 10,000 erase and write cycles are guaranteed per 512

byte line. Single sector erase (8 kB) or the whole chip erase is done in 400 ms.

• 64/32/16 kilobyte Static RAM (LPC2106/2105/2104).

• Vectored Interrupt Controller.

• Emulation Trace Module supports real-time trace.

• RealMonitor module enables real time debugging.

• Standard ARM Test/Debug interface for compatibility with existing tools.

2

• Very small package LQFP48 (7x7mm

• Two UARTs, one with full modem interface.

•I2C serial interface.

• SPI serial interface.

• Two timers, each with 4 capture/compare channels.

• PWM unit with up to 6 PWM outputs.

• Real Time C lock.

• Watchdog Timer.

• General purpose I/O pins.

• CPU operating range up to 60 MHz.

• Dual power supply.

- CPU operating voltage range of 1.65V to 1.95V (1.8V +/- 8.3%).

- I/O power supply range of 3.0V to 3.6V (3.3V +/- 10%).

).

• Two low power modes, Idle and Power Down.

• Processor wakeup from Power Down mode via external interrupt.

• Individual enable/disable of peripheral functions for power optimization.

• On-chip crystal oscillator with an operating range of 10 MHz to 25 MHz.

• On-chip PLL allows CPU operation up to the maximum CPU rate. May be used over the entire crystal operating range.

APPLICATIONS

• Internet gateway.

• Serial communications protocol converter.

• Access control.

• Industrial Control.

• Medical equipment.

Introduction 15 October 02, 2003

Page 16

Philips Semiconductors Preliminary User Manual

LPC2106/2105/2104ARM-based Microcontroller

ARCHITECTURAL OVERVIEW

The LPC2106/2105/2104 consists of an ARM7TDM I-S CPU with emulatio n support, the ARM7 Lo cal Bus for interface to on -chip

memory controllers, the AMBA Advanced High-performance Bus (AHB) for interface to the interrupt controller, and the VLSI

Peripheral Bus (VPB, a compatible superset of ARM’s AMBA Advanced Peripheral Bus) for connection to on-chip peripheral

functions. The LPC2106/2105/2104 configures the ARM7TDMI-S processor in little-endian byte order.

AHB peripherals are allocated a 2 megabyte range of addresses at the very top of the 4 gigabyte ARM memory space. Each

AHB peripheral is allocated a 16 kilobyte address space within the AHB address space. LPC2106/05/04 peripheral functions

(other than the interrupt controller) are connected to the VPB bus. The AHB to VPB bridge interfaces the VPB bus to the AHB

bus. VPB peripherals are also allocated a 2 megabyte range of addresses, beginning at the 3.5 gigabyte address point. Each

VPB peripheral is allocated a 16 kilobyte address space within the VPB address space.

The connection of on-chip pe ripherals to d evice pins i s controlled by a Pin Conne ction Block. This must be configured by software

to fit specific application requirements for the use of peripheral functions and pins.

ARM7TDMI-S PROCESSOR

The ARM7TDMI-S is a general purpose 32-bit microproce ssor, which offers high perfo rmance and very low pow er consumption .

The ARM architecture is based on Reduced Instruction Set Computer (RISC) principles, and the instruction set and related

decode mechanism are much simpler than those of microprogrammed Complex Instruction Set Computers. This simplicity

results in a high instruction throughput and impressive real-time interrupt response from a small and cost-effective processor

core.

Pipeline techniques are em plo ye d so tha t all parts of the processing and memory systems can operat e con tinuously. Typically,

while one instruction is being executed, its successor is being decoded, and a third instruction is being fetched from memory.

The ARM7TDMI-S processor also employs a unique architectural strategy known as THUMB, which makes it ideally suited to

high-volume applications with memory restrictions, or applications where code density is an issue.

The key idea behind THUMB is that of a super-reduced instruction set. Essentially, the ARM7TDMI-S processor has two

instruction sets:

• The standard 32-bit ARM instruction set.

• A 16-bit TH UMB instruction set.

The THUMB set’s 16-bit ins truc tion length allows it to approach twic e th e de ns ity of s tan dard ARM code while retaining most of

the ARM’s performance advantage over a traditional 16-bit processor using 16-bit registers. This is possible because THUMB

code operates on the same 32-bit register set as ARM code.

THUMB code is able to provide up to 65% of the code size of ARM, and 160% of the performance of an equivalent ARM

processor connected to a 16-bit memory system.

The ARM7TDMI-S processor is described in detail in the ARM7TDMI-S Datasheet that can be found on official ARM website.

ON-CHIP FLASH MEMORY SYSTEM

The LPC2106/2105/2104 incorporates a 128K byte Flash memory system. This memory may be used for both code and data

storage. Programming o f the Fl ash m emory ma y be a ccom plish ed in sev eral w ays: over t he seri al bui lt-in JT AG interfa ce, us ing

In System Programming (ISP) and UART0, or by means of In Application Programming (IAP) capabilities. The application

program, using the In Application Programming (IAP) functions, may also erase and/or program the Flash while the application

is running, allowing a great degree of flexibility for data storage field firmware upgrades, etc.

Introduction 16 October 02, 2003

Page 17

Philips Semiconductors Preliminary User Manual

LPC2106/2105/2104ARM-based Microcontroller

ON-CHIP STATIC RAM

The LPC2106, LPC210 5 and LPC 2104 prov ide a 64K byte, 32K b yte and 16 K byte sta tic RAM me mory r espectivel y that may be

used for code and/or data storage. The SRAM supports 8-bit, 16-bit, and 32-bit accesses.

The SRAM controller incorpo r ate s a wri te-b ac k bu ffer i n ord er to p rev ent CPU s tal ls d urin g ba ck -to-back writes. The write-back

buffer always holds the last data sent by software to the SRAM. This data is only written to the SRAM when another write is

requested by software. If a ch ip res et occurs , actu al SRAM cont ent s w ill not refl ec t the mo st recen t wr ite req ue st. Any sof tw are

that checks SRAM contents after reset must take this into account. A dummy write to an unused location may be appended to

any operation in order to guarantee that all data has really been written into the SRAM.

Introduction 17 October 02, 2003

Page 18

Philips Semiconductors Preliminary User Manual

LPC2106/2105/2104ARM-based Microcontroller

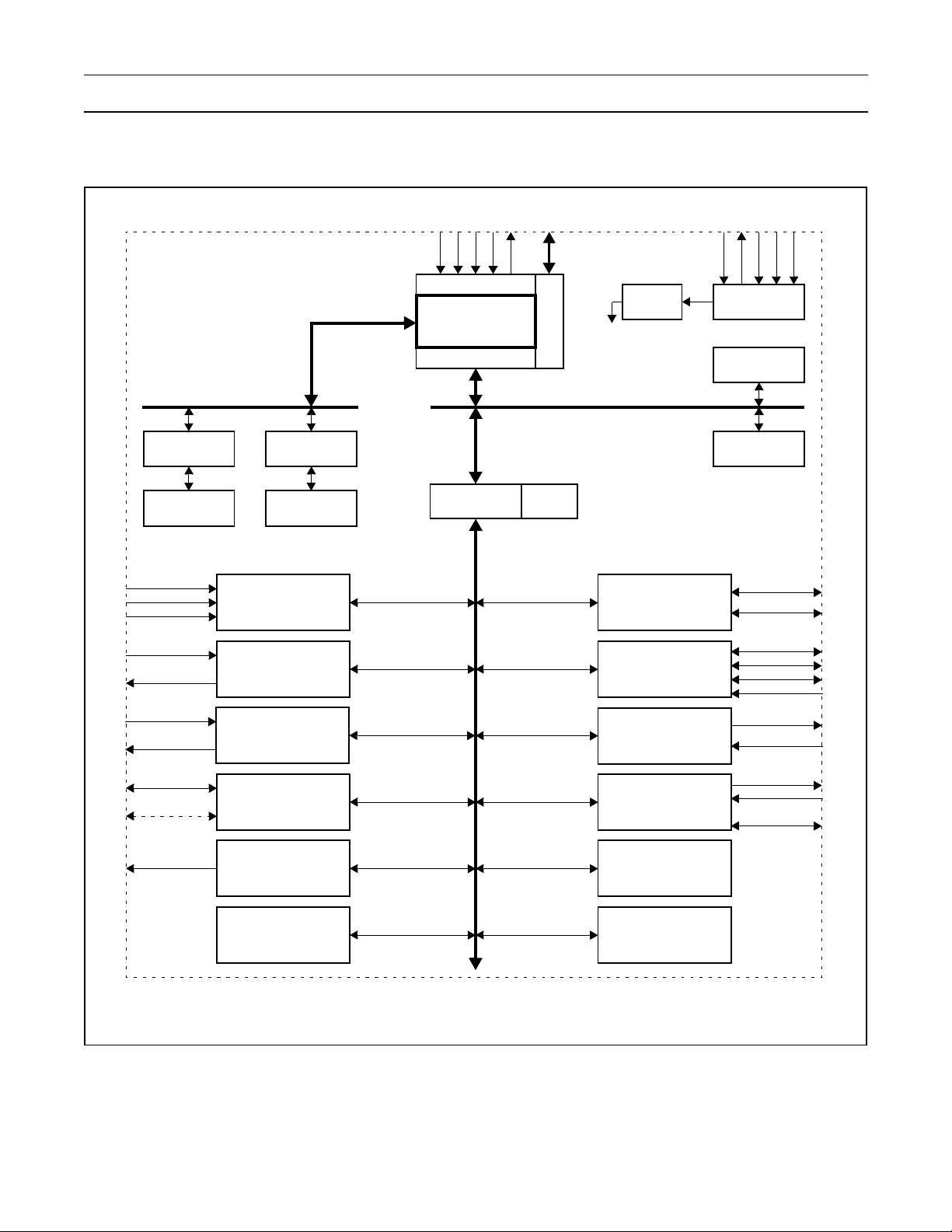

BLOCK DIAGRAM

Internal SRAM

Controller

64/32/16 kB

SRAM

EINT0 *

EINT1 *

EINT2 *

CAP0..2 *

MAT0..2 *

ARM7 Local Bus

Internal Flash

External

Interrupts

Capture /

Compare

Timer 0

Controller

128 kB

FLASH

1

1

TMS

TRST

Test/Debug Interface

1

1

1

TDI

TCK

TDO

ARM7TDMI-S

AHB Bridg e

AHB to VPB

Bridge

VPB (VLSI

Peripheral Bus)

PLL

System

Module

Emulation Trace

(Advanced High-performance Bus)

Clock

AMBA AHB

VPB

Divider

I2C Serial

Interface

SPI Serial

Interface

Vss

Vdd

RST

Xtal2

Xtal1

System

Functions

Vectored Interrupt

Controller

AHB

Decoder

SCL *

SDA *

SCK *

MOSI *

MISO *

SSEL *

CAP0..3 *

MAT0..3 *

GPIO (22 pins)

Capture /

Compare

Timer 1

General

GPIO (10 pins)

PWM1..6 *

Purpose I/O

PWM0

Real Time

Clock

* Shared with GPIO

1

When Test/Debug Interface is used, GPIO/other functions sharing these pins are not available

Figure 1: LPC2106/2105/2104 Block Diagram

UART0

UART1

Watchdog

Timer

System

Control

TxD *

RxD *

TxD *

RxD *

Modem Control

(6 pins) *

Introduction 18 October 02, 2003

Page 19

Philips Semiconductors Preliminary User Manual

LPC2106/2105/2104ARM-based Microcontroller

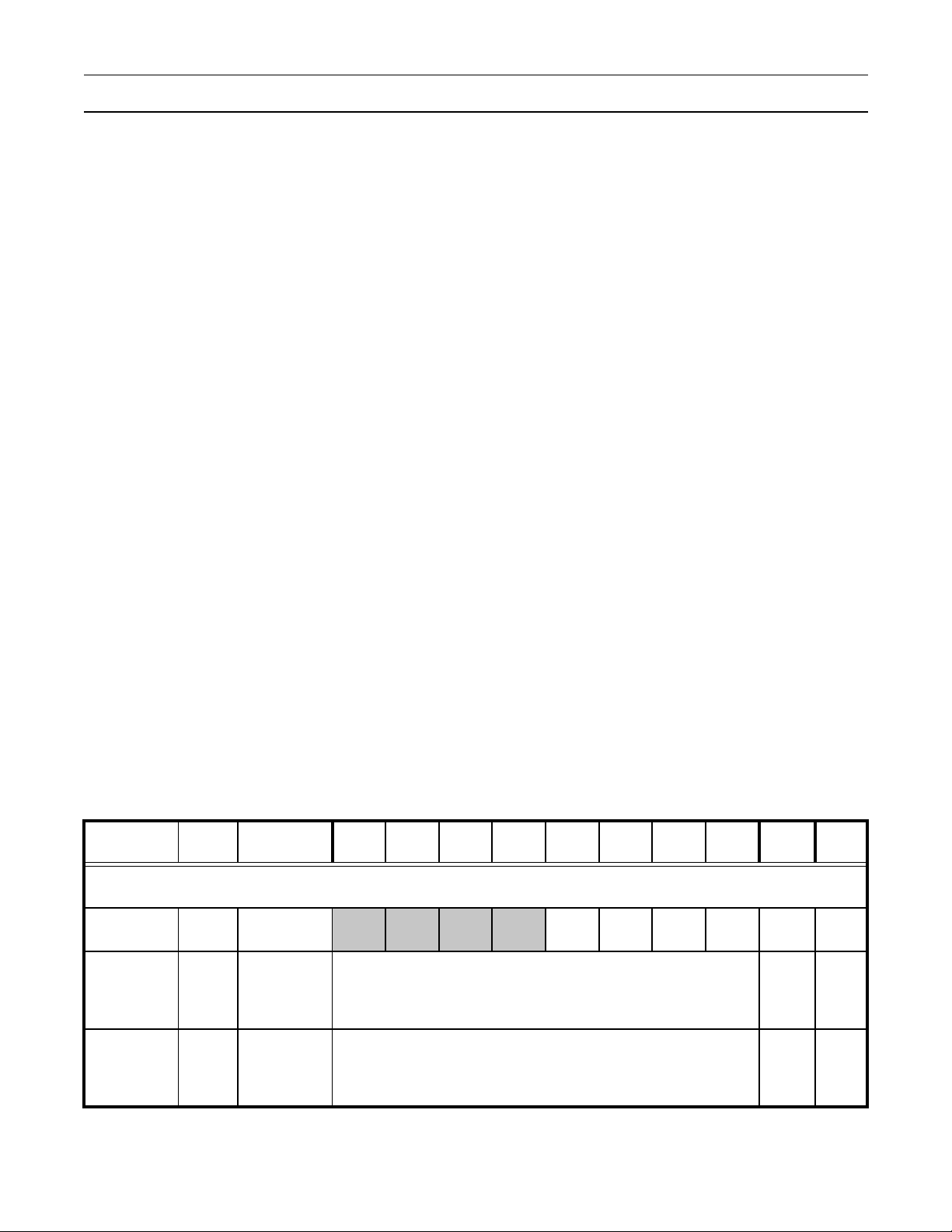

LPC2106/2105/2104 REGISTERS

Accesses to registers in LPC2106/2105/2104 is restricted in the following ways:

1) user must NOT attempt to access any register locations not defined.

2) Access to any defined register locations must be stri ctly for the functions for the registers.

3) Register bits labeled ’-’, ’0’ or ’1’ can ONLY be written and read as follows:

- ’-’ MUST be written with ’0’, but can return any value when read (even if it was written with ’0’). It is a reserved bit and may

be used in future derivatives.

- ’0’ MUST be written with ’0’, and will return a ’0’ when read.

- ’1’ MUST be written with ’1’, and will return a ’1’ when read.

The following table shows all registers available in LPC2106/2105/2104 microcontroller sorted according to the address.

Access to the specific one can be categorized as either read/write, read only or write only (R/W, RO and WO respectively).

"Reset Value" field refe rs to the data stored in us ed/accessible bit s only. It does not inc lude reserved bits cont ent. Some registers

may contain undeterm ined data up on reset. In thi s case, reset value is ca tegorized as "un defined". Classificati on as "NA" is u sed

in case reset value is not applicable. Some registers in RTC are not affected by the chip reset. Their reset value is marked as *

and these registers must be initialized by software if the RTC is enabled.

Registers in LPC210 6/2105/2104 are 8, 16 or 3 2 bits wi de. For 8 bit registers show n in Table 1, bit resi ding in the MSB (The Most

Significant Bit) col umn corresponds to the bit 7 o f that register, while bit in t he LSB (The Leas t Significant B it) column corr esponds

to the bit 0 of the same register.

If a register is 1 6/3 2 bit wide, the b it res iding in t he top left corne r of i ts d escrip tion, is th e bit corre spond ing to the bit 1 5/31 o f the

register, while the bit in the bottom right corner corresponds to bit 0 of this register.

Examples: bit "EN A6" in PWM P CR reg ist er ( add res s 0 xE0 014 04 C) rep res ents t he bit at pos iti on 14 in this register; bits 15, 8, 7

and 0 in the same register are reserved. Bit "Stop on MR6" in PWMMCR register (0xE001 4014) corresponds to the bit at positi on

20; bits 31 to 21 of the same register are reserved.

Unused (reserved) bits are marked with "-" and represented as gray fields. Access to them is restricted as already described.

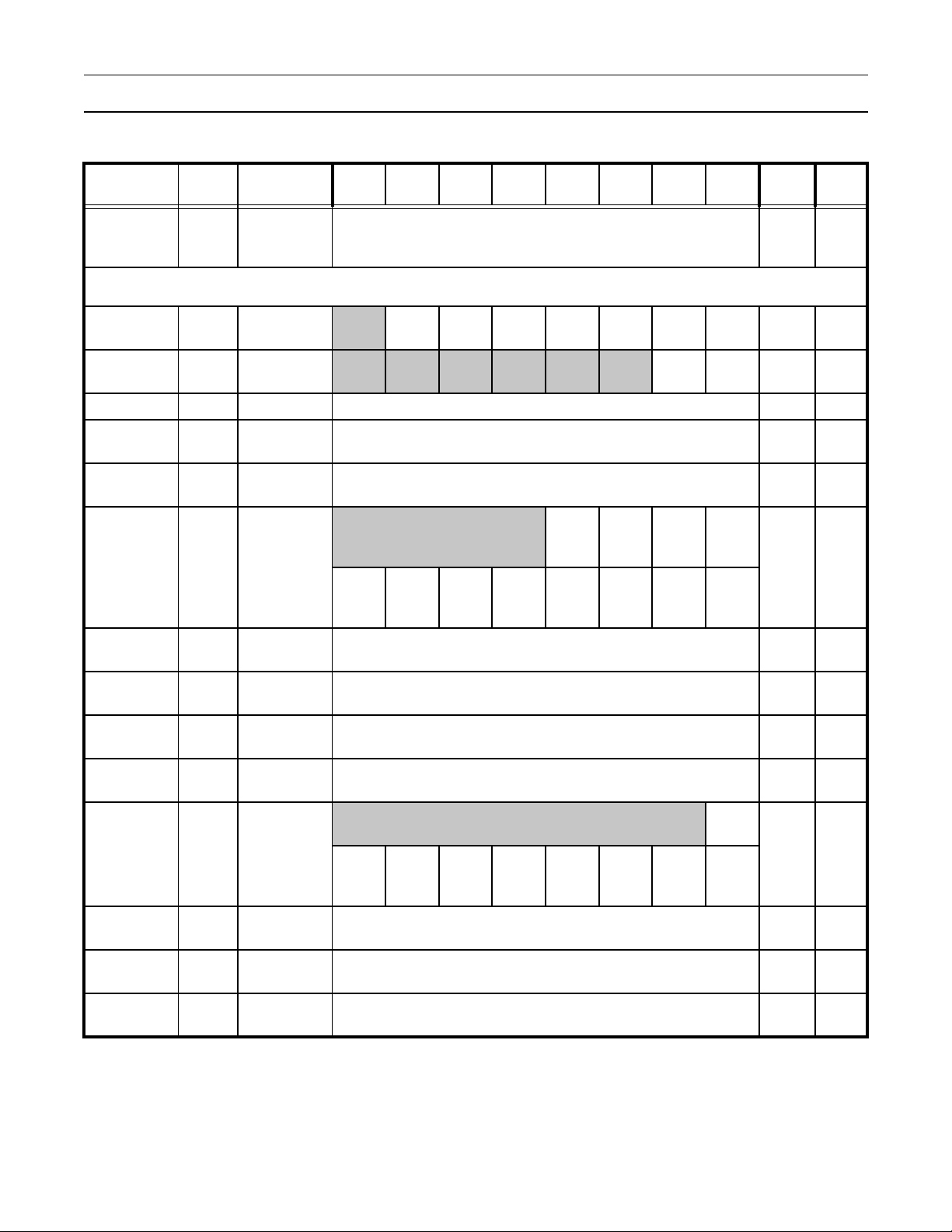

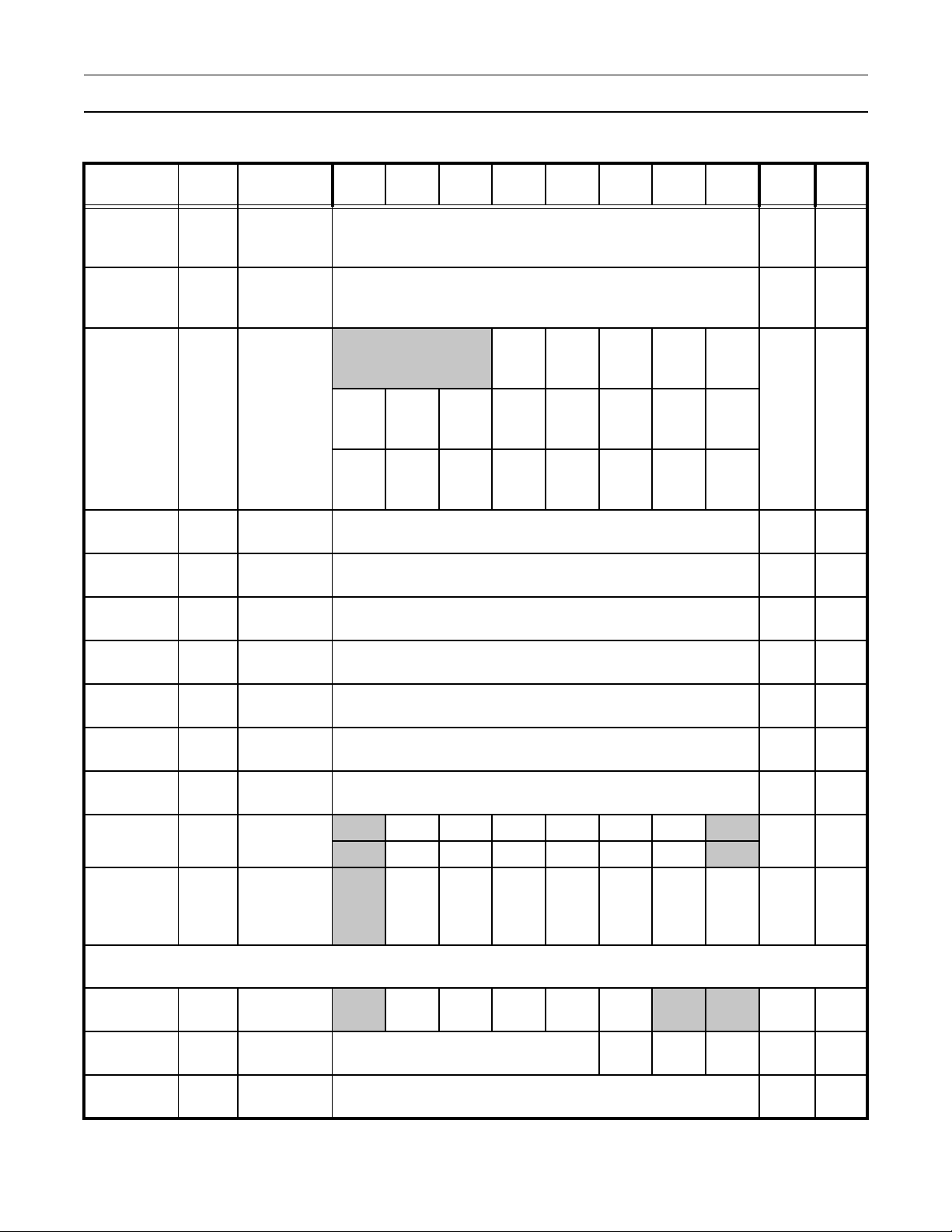

Table 1: LPC2106/2105/2104 Registers

Address

Offset

WD

0xE0000000

0xE0000004 WDTC

Name Description MSB LSB Access

WD

MOD

Watchdog

mode register

Watchdog

timer

constant

register

- - - -

WD

INTWDTOF

32 bit data R/W 0xFF

WDRE

SET

WDEN R/W 0

Reset

Value

Watchdog

WD

0xE0000008

FEED

feed

sequence

register

8 bit data (0xAA fallowed by 0x55) WO NA

Introduction 19 October 02, 2003

Page 20

Philips Semiconductors Preliminary User Manual

LPC2106/2105/2104ARM-based Microcontroller

Table 1: LPC2106/2105/2104 Registers

Address

Offset

0xE000000C WDTV

Timer 0

0xE0004000 T0IR

0xE0004004 T0TCR

0xE0004008 T0TC T0 Counter 32 bit data RW 0

0xE000400C T0PR

0xE0004010 T0PC

0xE0004014 T0MCR

Name Description MSB LSB Access

Watchdog

timer value

register

T0 Interrupt

Register

T0 Control

Register

T0 Prescale

Register

T0 Prescale

Counter

T0 Match

Control

Register

CR2

Int.

- - - - - -

4 reserved (-) bits

Reset

MR2

on

Int. on

MR2

CR1

Int.

Stop

on

MR1

32 bit data RO 0xFF

CR0

Int.

Reset

MR1

MR3

Int.

32 bit data R/W 0

32 bit data R/W 0

Stop

on

MR3

Int. on

on

MR1

MR2

Int.

Reset

on

MR3

Stop

on

MR0

MR1

Int.

CTR

Enable

Int. on

MR3

Reset

on

MR0

MR0

Int.

CTR

Reset

Stop

on

MR2

Int. on

MR0

R/W 0

R/W 0

R/W 0

Reset

Value

0xE0004018 T0MR0

0xE000401C T0MR1

0xE0004020 T0MR2

0xE0004024 T0MR3

0xE0004028 T0CCR

0xE000402C T0CR0

0xE0004030 T0CR1

0xE0004034 T0CR2

T0 Match

Register 0

T0 Match

Register 1

T0 Match

Register 2

T0 Match

Register 3

T0 Capture

Control

Register

T0 Capture

Register 0

T0 Capture

Register 1

T0 Capture

Register 2

Int. on

Cpt.2

falling

Int. on

Cpt.2

rising

32 bit data R/W 0

32 bit data R/W 0

32 bit data R/W 0

32 bit data R/W 0

7 reserved (-) bits

Int. on

Cpt.1

Int. on

Cpt.1

falling

32 bit data RO 0

32 bit data RO 0

32 bit data RO 0

Int. on

Cpt.1

rising

Int. on

Cpt.0

Int. on

Cpt.0

falling

Int. on

Cpt.2

Int. on

Cpt.0

rising

R/W 0

Introduction 20 October 02, 2003

Page 21

Philips Semiconductors Preliminary User Manual

LPC2106/2105/2104ARM-based Microcontroller

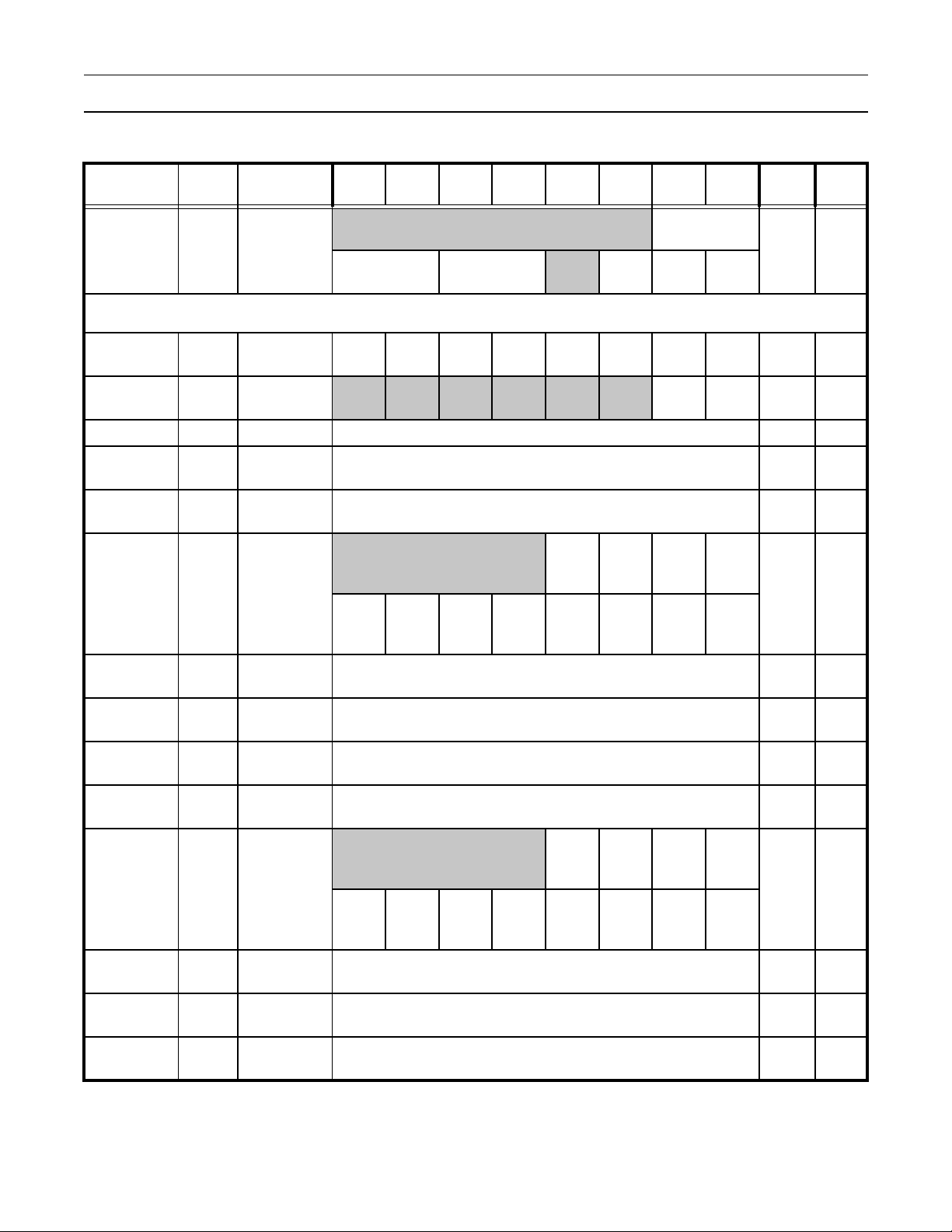

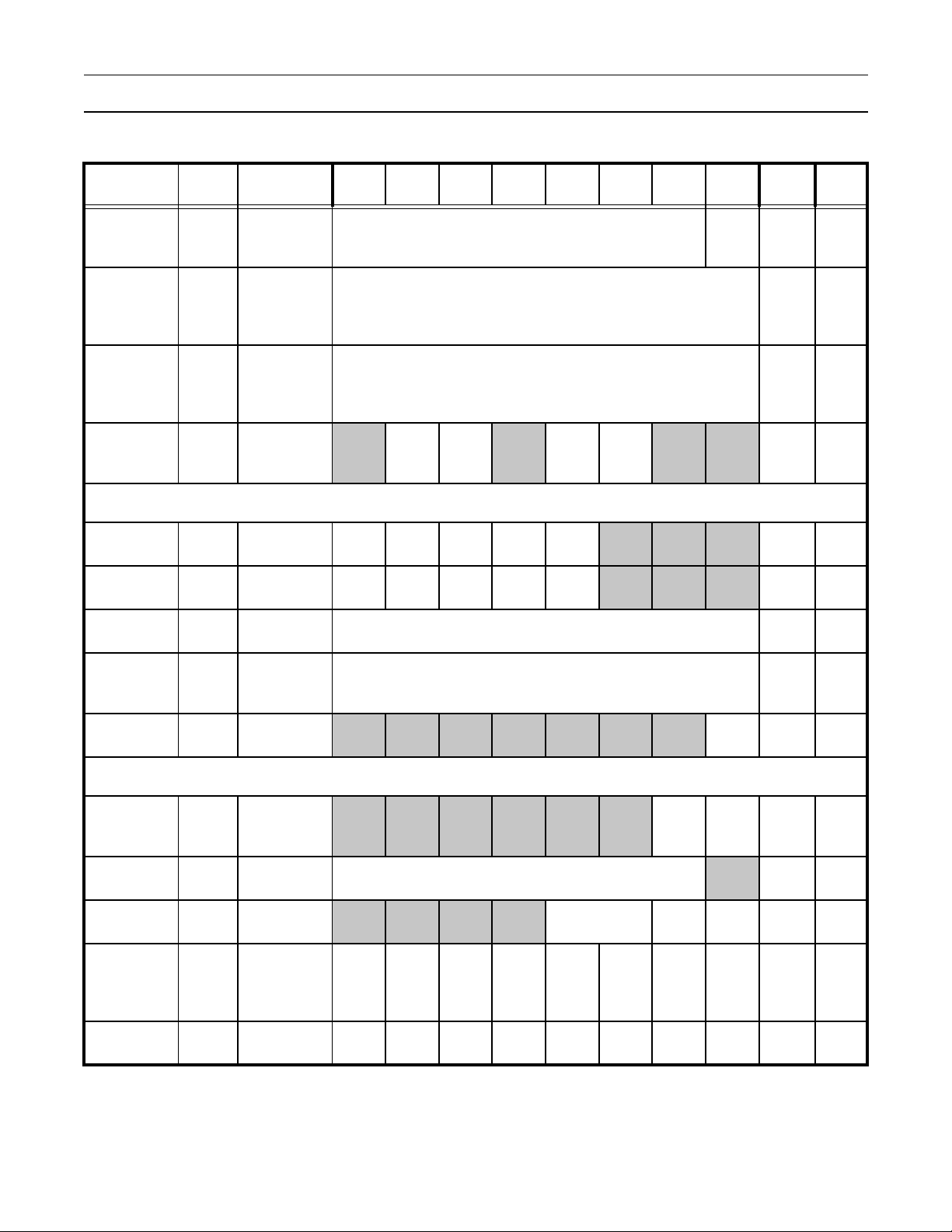

Table 1: LPC2106/2105/2104 Registers

Address

Offset

0xE000403C T0EMR

Timer 1

0xE0008000 T1IR

0xE0008004 T1TCR

0xE0008008 T1TC T1 Counter 32 bit data RW 0

0xE000800C T1PR

0xE0008010 T1PC

0xE0008014 T1MCR

Name Description MSB LSB Access

Ext.

Int.

on

on

External Match

Control 2

Ext.

Mtch.1

MR1

Int.

CTR

Enable

Int. on

MR3

Reset

on

MR0

Ext.

Mtch.0

MR0

Int.

CTR

Reset

Stop

on

MR2

Int. on

MR0

R/W 0

R/W 0

R/W 0

R/W 0

T0 External

Match

Register

T1 Interrupt

Register

T1 Control

Register

T1 Prescale

Register

T1 Prescale

Counter

T1 Match

Control

Register

6 reserved (-) bits

External Match

Control 1

CR3

Int.

Reset

on

MR2

CR2

- - - - - -

4 reserved (-) bits

Int. on

MR2

Int.

External Match

Control 0

CR1

Int.

Stop

on

MR1

CR0

Int.

32 bit data R/W 0

32 bit data R/W 0

Reset

on

MR1

-

MR3

Int.

Stop

on

MR3

Int. on

MR1

Mtch2.

MR2

Reset

MR3

Stop

MR0

Reset

Value

0xE0008018 T1MR0

0xE000801C T1MR1

0xE0008020 T1MR2

0xE0008024 T1MR3

0xE0008028 T1CCR

0xE000802C T1CR0

0xE0008030 T1CR1

0xE0008034 T1CR2

T1 Match

Register 0

T1 Match

Register 1

T1 Match

Register 2

T1 Match

Register 3

T1 Capture

Control

Register

T1 Capture

Register 0

T1 Capture

Register 1

T1 Capture

Register 2

4 reserved (-) bits

Int. on

Cpt.2

falling

Int. on

Cpt.2

rising

Int. on

Cpt.1

32 bit data R/W 0

32 bit data R/W 0

32 bit data R/W 0

32 bit data R/W 0

Int. on

Cpt.3

Int. on

Cpt.1

falling

Int. on

Cpt.1

rising

32 bit data RO 0

32 bit data RO 0

32 bit data RO 0

Int. on

Cpt.3

falling

Int. on

Cpt.0

Int. on

Cpt.3

rising

Int. on

Cpt.0

falling

Int. on

Cpt.2

R/W 0

Int. on

Cpt.0

rising

Introduction 21 October 02, 2003

Page 22

Philips Semiconductors Preliminary User Manual

LPC2106/2105/2104ARM-based Microcontroller

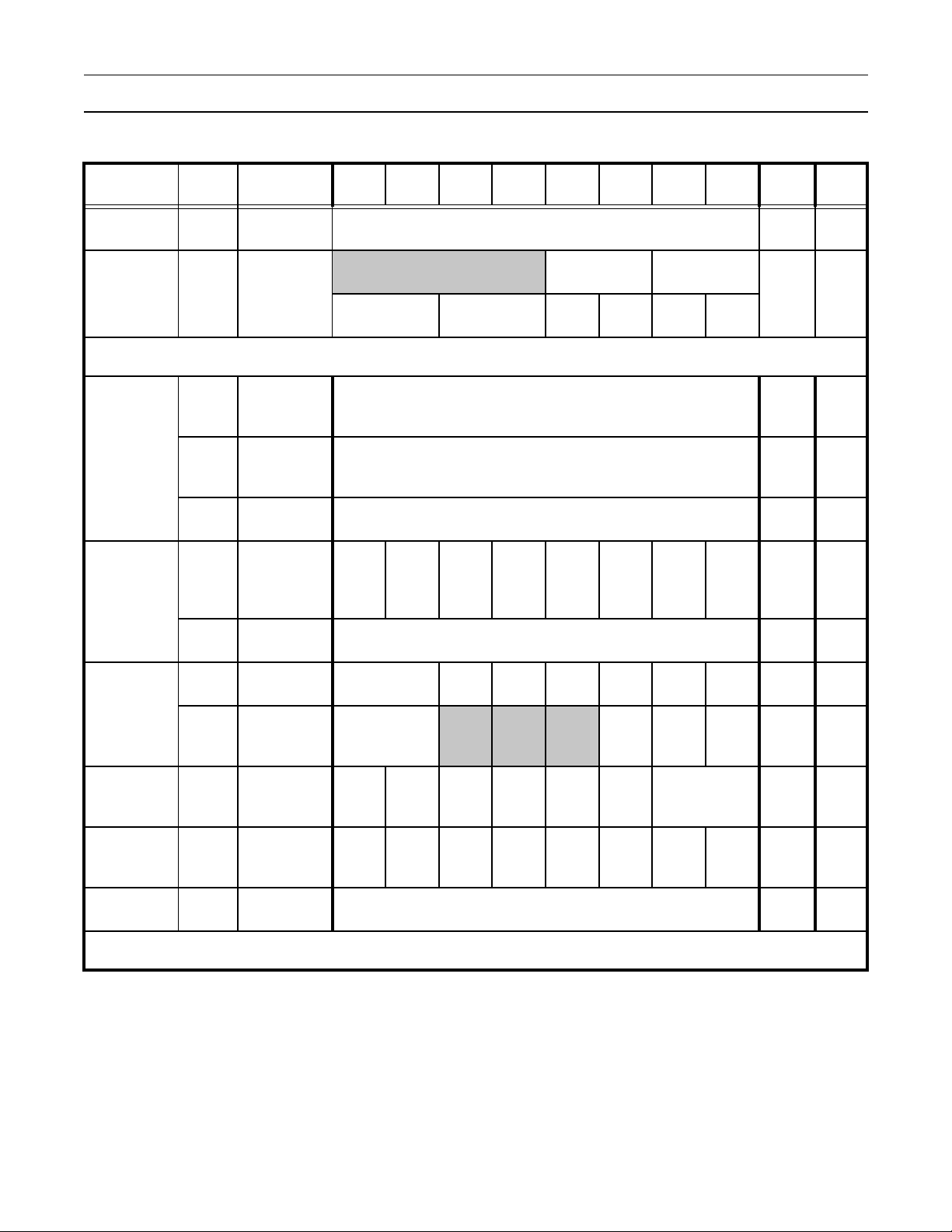

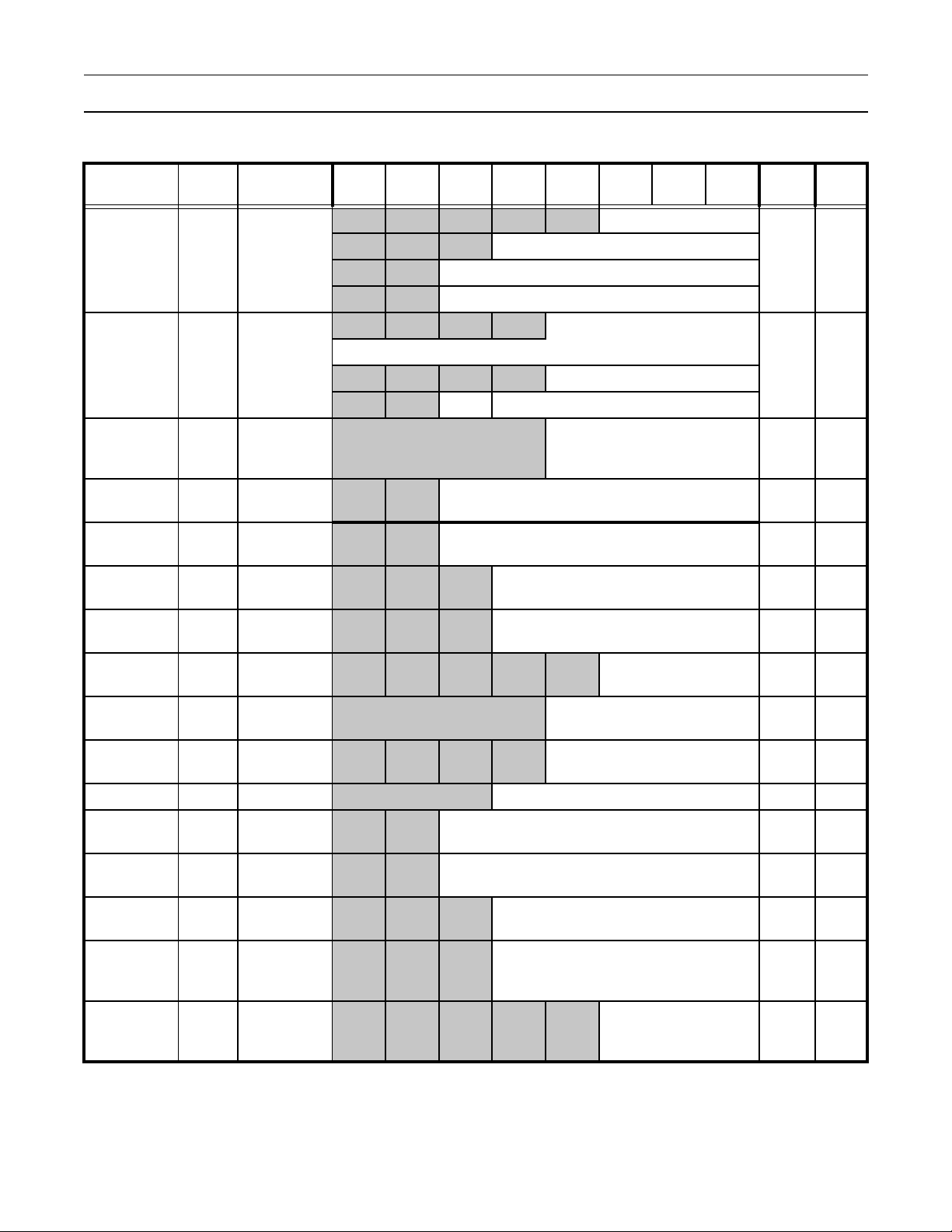

Table 1: LPC2106/2105/2104 Registers

Address

Offset

Name Description MSB LSB Access

0xE0008038 T1CR3

0xE000803C T1EMR

UART 0

U0RBR

(DLAB=0)

0xE000C000

U0THR

(DLAB=0)

U0DLL

(DLAB=1)

U0IER

0xE000C004

(DLAB=0)

T1 Capture

Register 3

T1 External

Match

Register

U0 Receiver

Buffer

Register

U0 Transmit

Holding

Register

U0 Divisor

Latch LSB

U0 Interrupt

Enable

Register

32 bit data RO 0

4 reserved (-) bits

External Match

Control 1

External Match

Control 0

External Match

Control 3

Ext.

Mtch.3

8 bit data RO

8 bit data WO NA

8 bit data R/W 0x01

00000

Ext.

Mtch2.

En. Rx

Line

Status

Int.

External Match

Control 2

Ext.

Mtch.1

Enable

THRE

Int.

Ext.

Mtch.0

En. Rx

Data

Av.Int.

Reset

Value

R/W 0

un-

defined

R/W 0

U0DLM

(DLAB=1)

U0IIR

0xE000C008

U0FCR

0xE000C00C U0LCR

0xE000C014 U0LSR

0xE000C01C U0SCR

UART 1

U0 Divisor

Latch MSB

U0 Interrupt

ID Register

U0 FIFO

Control

Register

U0 Line

Control

Register

U0 Line

Status

Register

U0 Scratch

Pad Register

8 bit data R/W 0

FIFOs Enabled 0 0 IIR3 IIR2 IIR1 IIR0 RO 0x01

Rx Trigger

DLAB

Set

Break

- - -

Stick

Parity

Even

Parity

Select

Parity

Enable

U0 Tx

FIFO

Reset

Nm. of

Stop

Bits

U0 Rx

FIFO

Reset

U0

FIFO

Enable

Word Length

Select

WO 0

R/W 0

Rx

FIFO

TEMT THRE BI FE PE OE DR RO 0x60

Error

8 bit data R/W 0

Introduction 22 October 02, 2003

Page 23

Philips Semiconductors Preliminary User Manual

LPC2106/2105/2104ARM-based Microcontroller

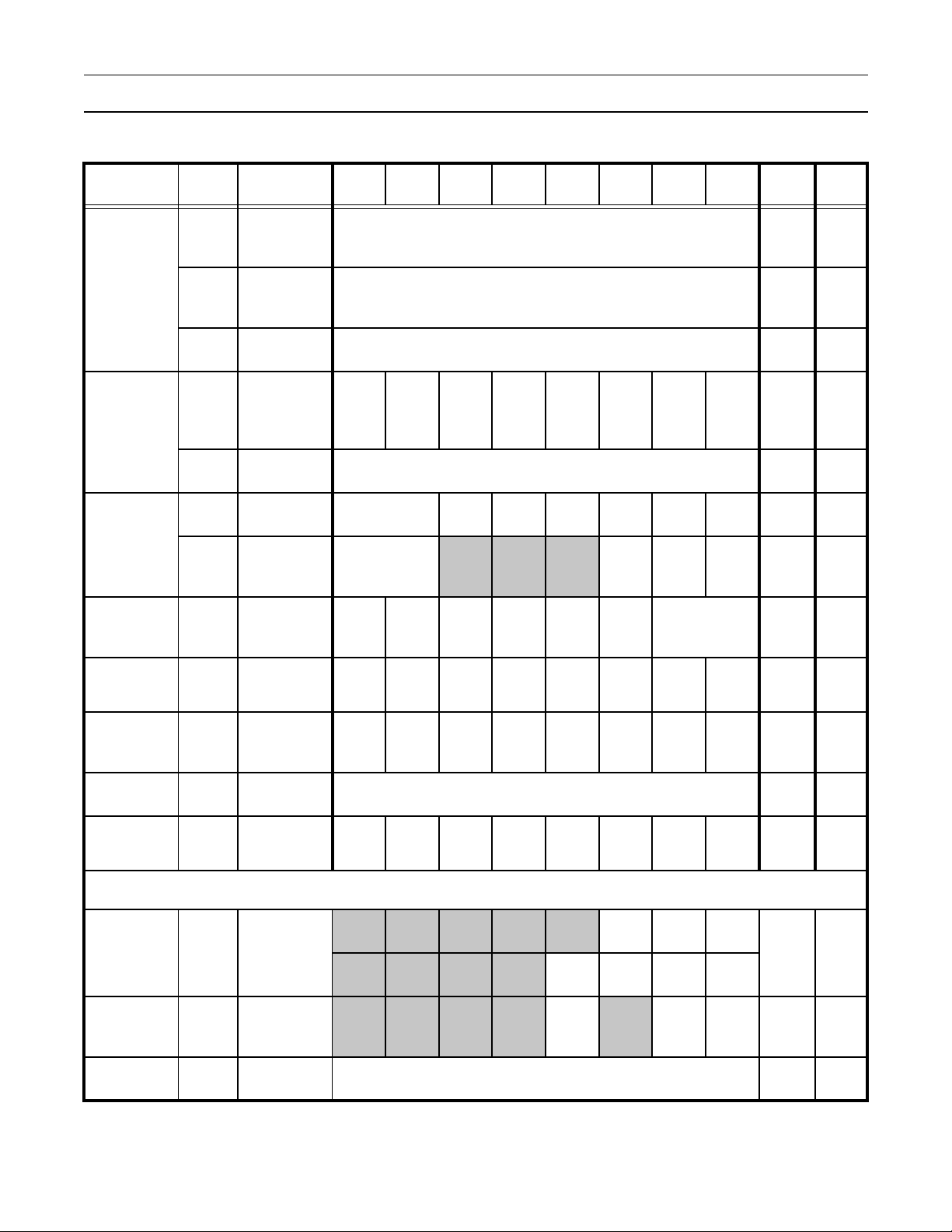

Table 1: LPC2106/2105/2104 Registers

Address

Offset

Name Description MSB LSB Access

U1RBR

(DLAB=0)

0xE0010000

U1THR

(DLAB=0)

U1DLL

(DLAB=1)

U1IER

0xE0010004

(DLAB=0)

U1DLM

(DLAB=1)

U1IIR

0xE0010008

U1FCR

0xE001000C U1LCR

0xE0010010

U1

MCR

0xE0010014 U1LSR

U1 Receiver

Buffer

Register

U1 Transmit

Holding

Register

U1 Divisor

Latch LSB

U1 Interrupt

Enable

Register

U1 Divisor

Latch MSB

U1 Interrupt

ID Register

U1 FIFO

Control

Register

U1 Line

Control

Register

U1 Modem

Control

Register

U1 Line

Status

Register

Reset

Value

8 bit data RO

un-

defined

8 bit data WO NA

8 bit data R/W 0x01

En.

0000

Mdem

Satus

En. Rx

Status

Int.

Line

Int.

Enable

THRE

Int.

En. Rx

Data

Av.Int.

R/W 0

8 bit data R/W 0

FIFOs Enabled 0 0 IIR3 IIR2 IIR1 IIR0 RO 0x01

Rx Trigger

DLAB

Set

Break

- - -

Stick

Parity

000

Even

Parity

Select

Loop

Back

U0 Tx

FIFO

Reset

Parity

Enable

Nm. of

Stop

0 0 RTS DTR R/W 0

Bits

U0 Rx

FIFO

Reset

U0

FIFO

Enable

Word Length

Select

WO 0

R/W 0

Rx

FIFO

TEMT THRE BI FE PE OE DR RO 0x60

Error

U1

U1 Scratch

Pad Register

U1 Modem

Status

Register

8 bit data R/W 0

DCD RI DSR CTS

Delta

DCD

Trailing

Edge

RI

Delta

DSR

Delta

CTS

RO 0

0xE001001C U1SCR

0xE0010018

MSR

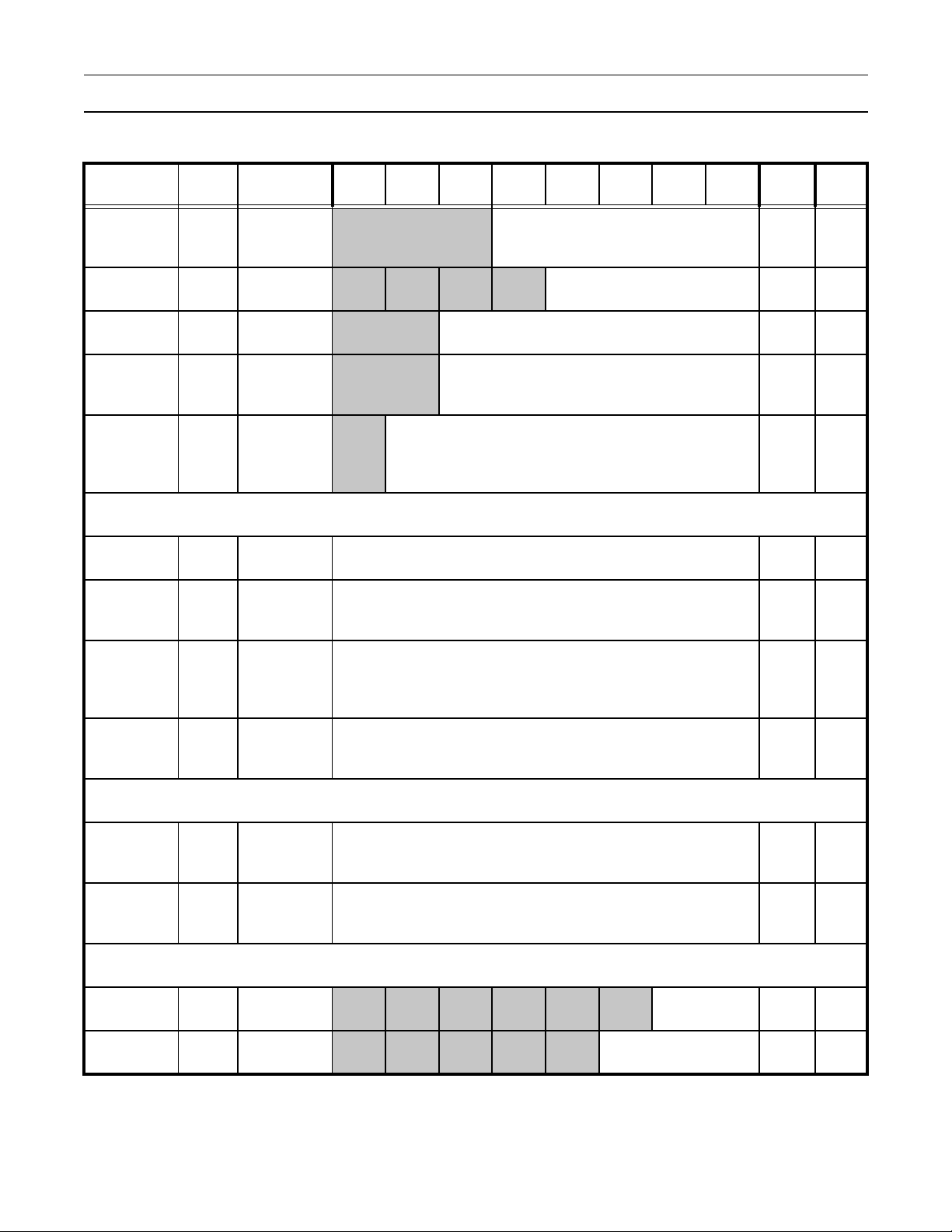

PWM

0xE0014000

0xE0014004

0xE0014008

IR

PWM

Interrupt

Register

PWM Timer

Control

Register

PWM

PWM

TCR

PWMTCPWM Timer

Counter

- - - - -

- - - -

- - - -

MR3

PWM

Enable

32 bit data RW 0

Int.

MR6

Int.

MR2

Int.

MR5

Int.

MR4

Int.

R/W 0

MR1

Int.

CTR

Reset

MR0

Int.

CTR

Enable

R/W 0

Introduction 23 October 02, 2003

Page 24

Philips Semiconductors Preliminary User Manual

LPC2106/2105/2104ARM-based Microcontroller

Table 1: LPC2106/2105/2104 Registers

Address

Offset

0xE001400C

0xE0014010

0xE0014014

0xE0014018

0xE001401C

0xE0014020

Name Description MSB LSB Access

PR

PC

PWM

Prescale

Register

PWM

Prescale

Counter

PWM Match

Control

Register

PWM Match

Register 0

PWM Match

Register 1

PWM Match

Register 2

11 reserved (-) bits

Int. on

MR5

Reset

on

MR2

Stop

on

MR4

Int. on

MR2

Reset

on

MR4

Stop

on

MR1

32 bit data R/W 0

32 bit data R/W 0

Stop

MR6

Int. on

MR4

Reset

MR1

on

on

Reset

on

MR6

Stop

on

MR3

Int. on

MR1

Int. on

MR6

Reset

on

MR3

Stop

on

MR0

Stop

on

MR5

Int. on

MR3

Reset

on

MR0

Reset

on

MR5

Stop

on

MR2

Int. on

MR0

R/W 0

32 bit data R/W 0

32 bit data R/W 0

32 bit data R/W 0

PWM

PWM

PWM

MCR

PWM

MR0

PWM

MR1

PWM

MR2

Reset

Value

0xE0014024

0xE0014040

0xE0014044

0xE0014048

0xE001404C

0xE0014050

2

C

I

0xE001C000

PWM

MR3

PWM

MR4

PWM

MR5

PWM

MR6

PWM

PCR

PWM

LER

I2CON

SET

0xE001C004 I2STAT

0xE001C008 I2DAT

PWM Match

Register 3

PWM Match

Register 4

PWM Match

Register 5

PWM Match

Register 6

PWM Control

Register

PWM Latch

Enable

Register

2

C Control

I

Set Register

2

C Status

I

Register

2

C Data

I

Register

32 bit data R/W 0

32 bit data R/W 0

32 bit data R/W 0

32 bit data R/W 0

- ENA6 ENA5 ENA4 ENA3 ENA2 ENA1 R/W 0

- SEL6 SEL5 SEL4 SEL3 SEL2 SEL1 -

Ena.

PWM

-

M6

Latch

Ena.

PWM

M5

Latch

Ena.

PWM

M4

Latch

Ena.

PWM

M3

Latch

Ena.

PWM

M2

Latch

Ena.

PWM

M1

Latch

Ena.

PWM

M0

Latch

R/W 0

-I2ENSTASTOSIAA - -R/W0

5 bit Status 0 0 0 RO 0xF8

8 bit data R/W 0

Introduction 24 October 02, 2003

Page 25

Philips Semiconductors Preliminary User Manual

LPC2106/2105/2104ARM-based Microcontroller

Table 1: LPC2106/2105/2104 Registers

Address

Offset

0xE001C00C

0xE001C010

0xE001C014

0xE001C018

Name Description MSB LSB Access

I2

ADR

I2

SCLH

I2

SCLL

I2CON

CLR

SPI

0xE0020000 SPCR

0xE0020004 SPSR

0xE0020008 SPDR

0xE002000C

SP

CCR

0xE002001C SPINT

2

C Slave

I

Address

Register

SCL Duty

Cycle

Register High

Half Word

SCL Duty

Cycle

Register Low

Half Word

2

C Control

I

Clear

Register

SPI Control

Register