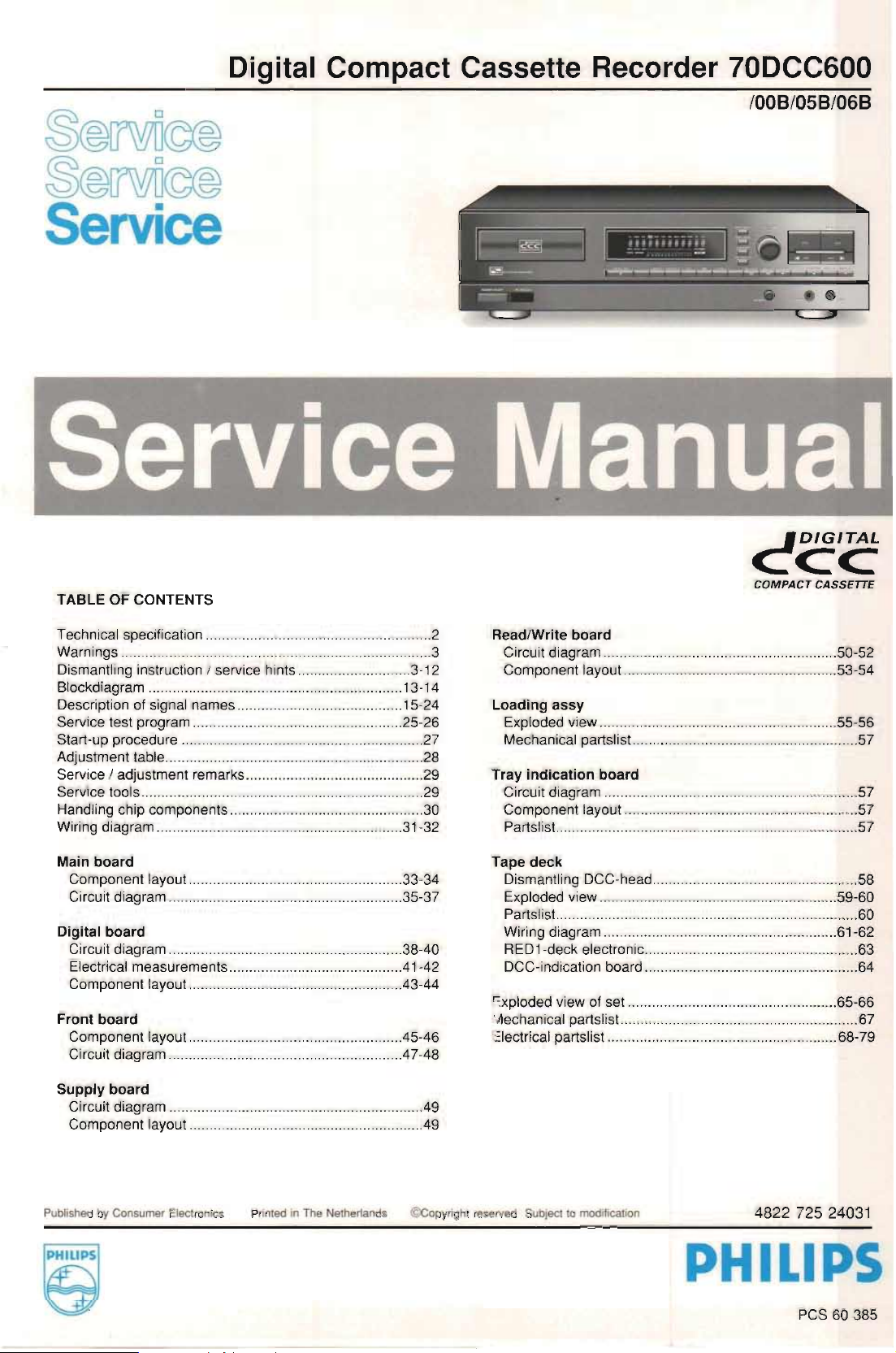

Philips DCC-600 Service Manual

Digital Compact Cassette Recorder 70DCC600

~@NOO

~@NOO

Service

1008/058/068

TABLE

Technical specification 2

W~~

Dismantling instruction I service hints 3-12

Blockdiagram 13-14

Description of signal names 15-24

Service test program 25-26

Start-up procedure 27

Adjustment table 28

Service

Service tools 29

Handling chip components 30

Wiring diagram 31-32

Main

Digital

Front

OF CONTENTS

I adjustment remarks 29

board

Component layout 33-34

Circuit diagram 35-37

board

Circuit diagram 38-40

Electrical measurements .41-42

Component layout .43-44

board

Component layout .45-46

Circuit diagram .47-48

CCC

COMPACT CASSETTE

ReadlWrite

~

Circuit diagram 50-52

Component layout 53-54

Loading

Exploded view 55-56

Mechanical partslist 57

Tray

Circuit diagram 57

Component layout 57

Partslist. 57

Tape

Dismantling DCC-head 58

Exploded view 59-60

Partslist. 60

Wiring diagram 61-62

RED1-deck electronic 63

DCC-indication board 64

Exploded view of set 65-66

\,1echanical parts list 67

:::Iectrical partslist 68-79

board

assy

indication

deck

board

Supply

PublishedbyConsumer Electronics PrintedinThe Netherlands ©Copyright reserved Subjecttomodification

board

Circuit diagram .49

Component layout .49

4822 725

24031

PHILIPS

PCS 60 385

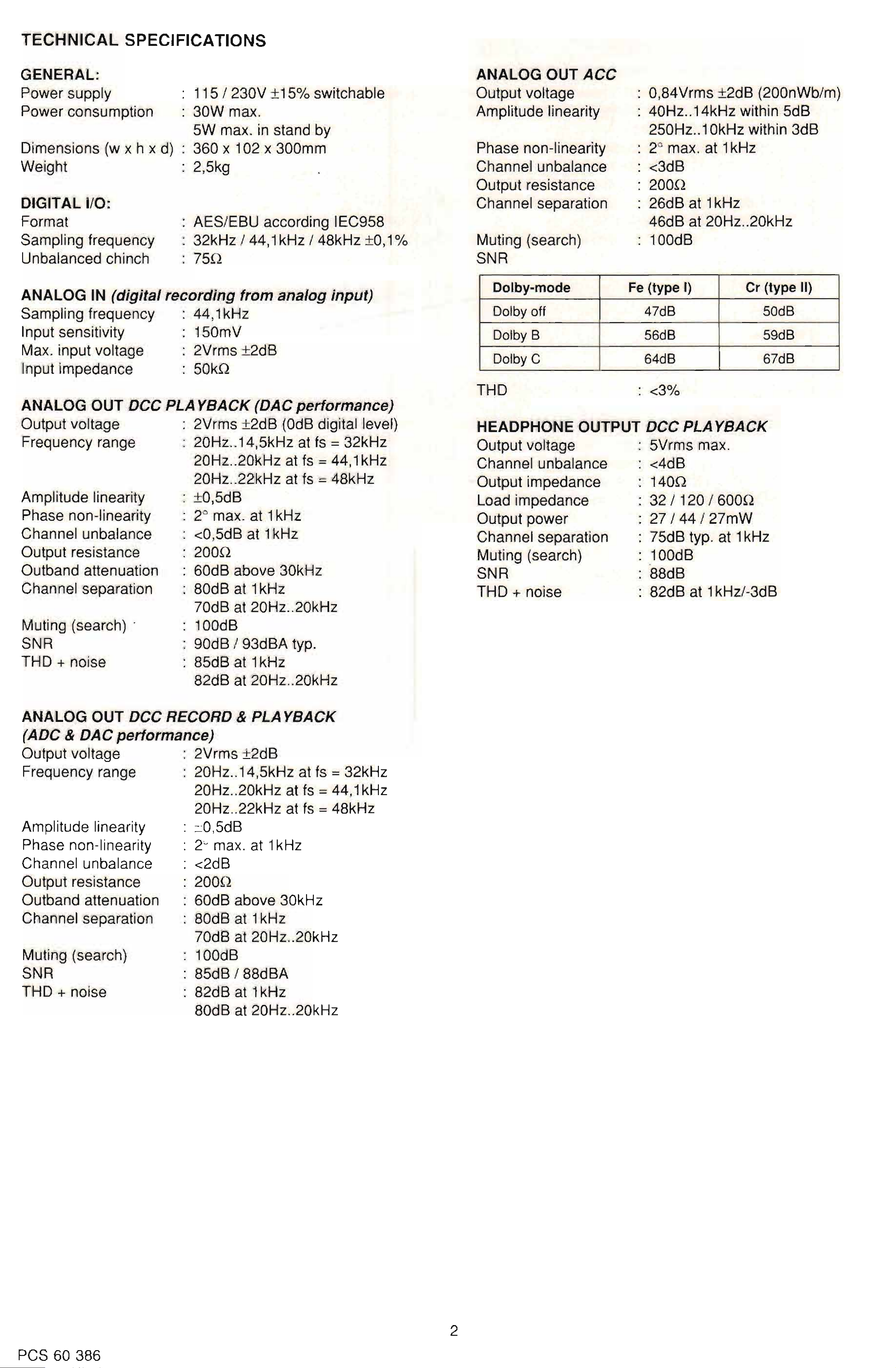

TECHNICAL

SPECIFICATIONS

GENERAL:

Power supply

Power consumption

Dimensions

(w

x h x

Weight

DIGITAL 1/0:

Format

Sampling frequency

Unbalanced chinch

d)

115

I 230V +15% switchable

30W max.

5W

max.

in

stand by

: 360 x 102 x 300mm

: 2,5kg

: AES/EBU according IEC958

: 32kHz

144,1 kHz 148kHz

+0,1

: 75Q

%

ANALOG OUT

ACC

Output voltage

Amplitude linearity

Phase non-linearity

Channel unbalance

Output resistance

Channel separation

Muting (search)

SNR

: 0,84Vrms ±2dB

(200nWb/m)

: 40Hz..14kHz within 5dB

250Hz

:

2°

max.

..1OkHz

at

1

kHz

within 3dB

: <3dB

: 200Q

: 26dB at 1kHz

46dB at 20Hz

..

20kHz

: 100dB

ANALOG

IN

Sampling frequency :

(digital

recording

44,1

kHz

from

Input sensitivity . 150mV

Max. input voltage 2Vrms +2dB

Input impedance 50kQ

ANALOG OUT DCC

Output voltage

Frequency range

PLA

YBACK

: 2Vrms +2dB

: 20Hz

20Hz

..

..

(DAC

14,5kHz

20kHz at

analog

performance)

(OdB

at

fs

input)

digital level)

fs

= 32kHz

=

44,1

kHz

Dolby-mode

Dolby

Dolby

Dolby

off

B

C

Fe

THO

HEADPHONE OUTPUT

Output voltage

Channel unbalance

(type

47dB

56dB

I)

Cr

(type

50dB

59dB

64dB 67dB

: <3%

DCC PLAYBACK

: 5Vrms max.

: <4dB

II)

Amplitude linearity

Phase non-linearity

Channel unbalance

Output resistance

Outband attenuation

Channel separation

Muting (search) .

SNR

THO

+ noise

20Hz

22kHz

at

fs

..

: +0,5dB

: 2°

max.

<0,5dB

at

at

1

kHz

1kHz

: 200Q

: 60dB above 30kHz

: 80dB

70dB

at

1kHz

at

20Hz..20kHz

100dB

90dB

85dB

I 93dBA

at

1kHz

typo

= 48kHz

Output impedance

Load impedance

Output power

Channel separation

Muting (search)

SNR

THO

+ noise

: 140Q

:

32

:

27

I 120 I 600Q

I 44 I 27mW

: 75dB

: 100dB

: 88dB

: 82dB

typo

at

at

1kHzI·3dB

1kHz

ANALOG OUT

(ADC &

DAC

DCC

performance)

Output voltage

Frequency range

Amplitude linearity

Phase non-linearity

Channel unbalance

at

82dB

RECORD & PLAYBACK

20Hz..20kHz

: 2Vrms +2dB

: 20Hz

20Hz

20Hz

..

14,5kHz

..

20kHz

..

22kHz

at

at

at

fs

fs

fs

= 32kHz

=

= 48kHz

: +0,5dB

: 2° max.

at

1

kHz

: <2dB

44,1

kHz

Output resistance

Outband attenuation

Channel separation

Muting (search)

SNR

THO + noise

: 200Q

: 60dB above 30kHz

: 80dB

70dB

at

1

kHz

at

20Hz..20kHz

: 100dB

: 85dB

: 82dB

80dB

I 88dBA

at

1kHz

at

20Hz..20kHz

PCS

2

60 386

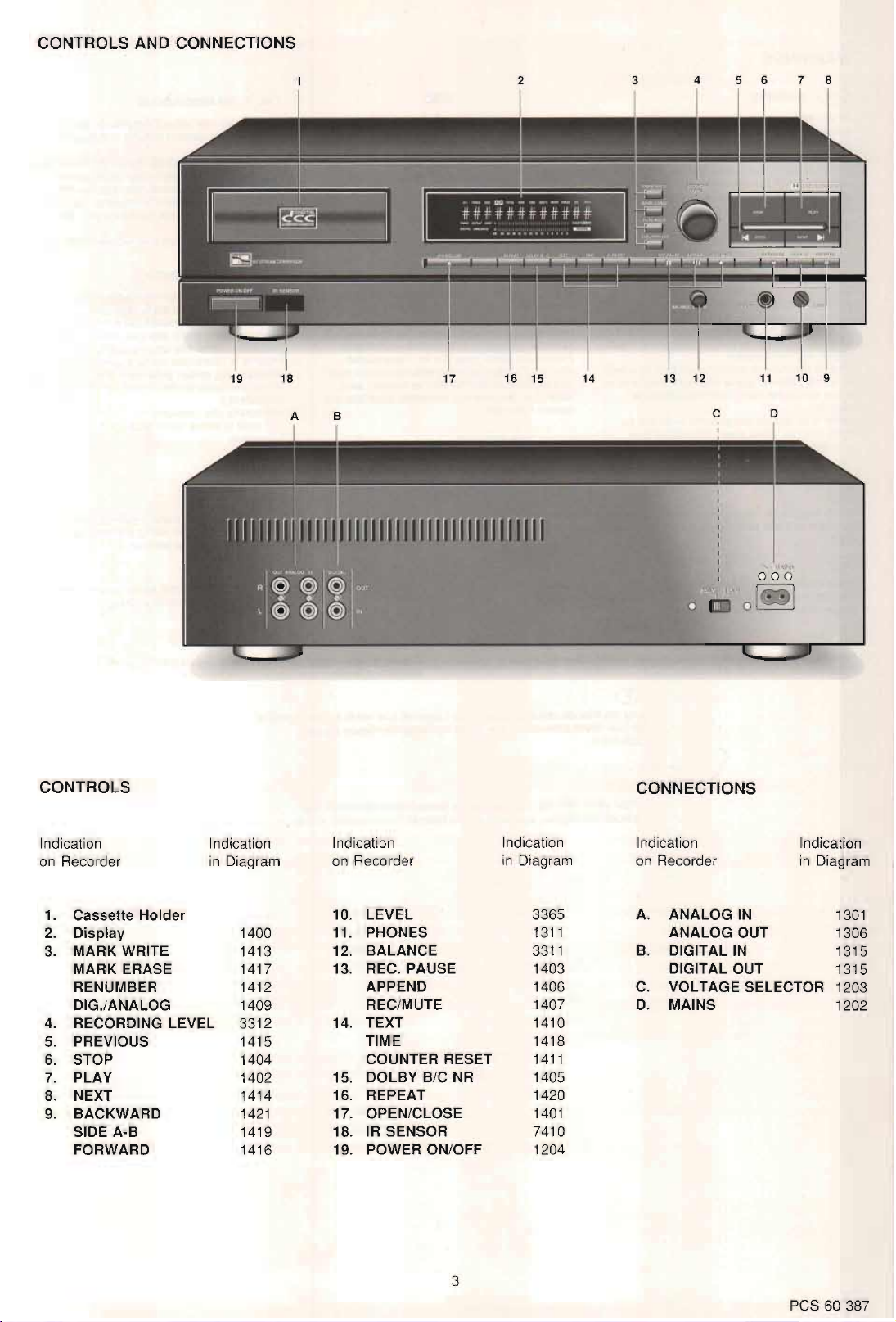

CONTROLS AND CONNECTIONS

2

19

18

A B

17

16 15

14

3

4 5 6 7 8

13

12

c

11

10 9

o

CONTROLS

Indication Indication

in

on

Recorder

1. Cassette

2.

Display 1400

Holder

Diagram

3. MARK WRITE 1413

MARK ERASE 1417

RENUMBER 1412

DIG.lANALOG 1409

RECORDING LEVEL

4.

PREVIOUS 1415

5.

6. STOP

PLAY

7.

8.

NEXT

9.

BACKWARD 1421 17.

SIDE A-B

FORWARD 1416

3312

1404

1402

1414

1419

CONNECTIONS

Indication

on

Recorder

Indication

in

Diagram

Indication

on

Recorder

10. LEVEL 3365 A. ANALOG

11.

PHONES 1311

BALANCE 3311 B.

12.

13.

REC.PAUSE

APPEND 1406

REC/MUTE 1407

TEXT 1410

14.

TIME 1418

COUNTER RESET 1411

15.

DOLBY B/C NR 1405

1403 DIGITAL OUT

ANALOG

DIGITAL

C.

VOLTAGE SELECTOR

D.

MAINS

16. REPEAT 1420

OPEN/CLOSE 1401

18. IR SENSOR 7410

19.

POWER ON/OFF

1204

"",

1-1\1>1;\

000

'org

IN

OUT

IN

Indication

in

Diagram

1301

1306

1315

1315

1203

1202

3

pes

60

387

WARNINGS

® WARNING

All

les

and

many

other

susceptible to electrostatic discharges (ESD).

Careless

handling

drastically.

When

repairing. make

connected

of

Keep components and tools also at this

potential.

CD

Taus les IC

semi-conducteurs

dacharges statiques (ESD).

Leur

ecourtee par

prise

Lors

au

anfiler

securite.

Veilleraco

cUlils

potentiel.

with

the

set

via

a wrist wrap with resistance.

ATTENTION

et

longevite

Ie

aleur manipulation.

de

reparations. g'assurer

meme

potential

Ie

bracelet

que

que

I'on

@

Safety regulations require that the set be restoredtoits original

condition

used.

and

®

Veiligheidsbepalingen vereisen, dat het apparaatinzijn

toestand

wordt

gespeciliceerde worden toegepasl.

@Varo!

Avattaessajasuojalukitus ohitettaessa olet alttiina nakymattomalle

lasersiiteilylle. Alii katso sateeseen.

semi-conductors are

during

repair

can

reduce

sure

that

you

the

same potentialasthe mass

beaucoup

pourrait etre considerablement

utilise

that parts

d'autres

sont

sensibles

fait

qu'aucune precaution n'est

quelamasse de I'appareil at

sarti

d'une resistance de

les composants

soient egalement ace

which

teruggebracht en

are

aux

de

bien

atre falie

ainsi

que les

are identical

dat

onderdelen, identiek aan de

life

with

those specified

® WARNUNG

Aile ICs und viele andere Halbleiter sind

emplindlich gegen elektrostatische Entladungen

(ESD).

Unsorgtiiltige

kann die Lebensdauer drastisch vermindern.

Sorgen sie datur,

l.iber

ein

Pulsarmband

Massepotential des Gerates verbunden

halten Sie Bauteile und Hillsminel ebenlalls auf

diesem Potential.

oorspronkelijke

Behandlung bei

dass

be

ESD

@ WAARSCHUWING

Aile IC's en vele andere haltgeleiders zijn

gevoelig voor electrostatische ontladingen

(ESD).

Onzorgvuldig behandelen tijdens reparatie kan

de levensduur drastisch doen verminderen.

Zorg erYoor dat u tijdens reparatie

polsband

hetzeltde potentiaal als de

apparaal.

Houd

ditzeltde potentiaal.

CJ) AVVERTIMENTO

TuttiIee parecchi semi-conduttori sono

sensibili aile scariche statiche (ESD).

La

der

Reparatur

Sie im Reparaturfall

mit

Widerstand

mit

dem

sind.

loro longevita potrebbe essere fortemente

ridatta

grande cauzione alia loro manipolazione.

Durante

collegato alia

massa dell'apparecchio tramiteunbraceialetta

a resistenza.

Assicurarsi

con

qualisilavara siano anche a questa

potenziale.

CD

Bei

jeder Reparatur

beachten. Der Originalzustand des Gerats dart

fUr

Reparaturen

sind

die

geltenden Sicherheitsvorschriften

sind

Original-Ersatzteilezuverwenden.

CD

Le

normedisicurezza esigona

condizioni originali e

quelli

specificati.

che

siano utilizzati pezzidirtcambiago identici a

® Varning!

Osynlig laserstnllning

Betrakta ej stnllen.

niir

denna del

met

weerstand verbonden bent

componenten

in

casodinon

Ie

riparazioni occorre quindi essere

stesso

che

i componenti e anche

che

I'apparecchio venga rimesso nelle

iir

oppnad

massa

en hulpmiddelen

osservazione della piu

potenziale che quello della

nicht

verandert werden

och sparren

via

een

van het

oak

gli

zu

iir

urkopplad.

met

op

utensili

CD

Les

normesdesecurite exigent que I'appareil

et

que soient utili

specifiees.

-Pour votre securite, ces documents doivent etre utilises par des

specialistes agrees, seuls habilites a reparer votre appareil

sees

les pieces de rechange identiques a celles

soit

remis a "etat d'arigine

en

panne-.

pes

4

60 388

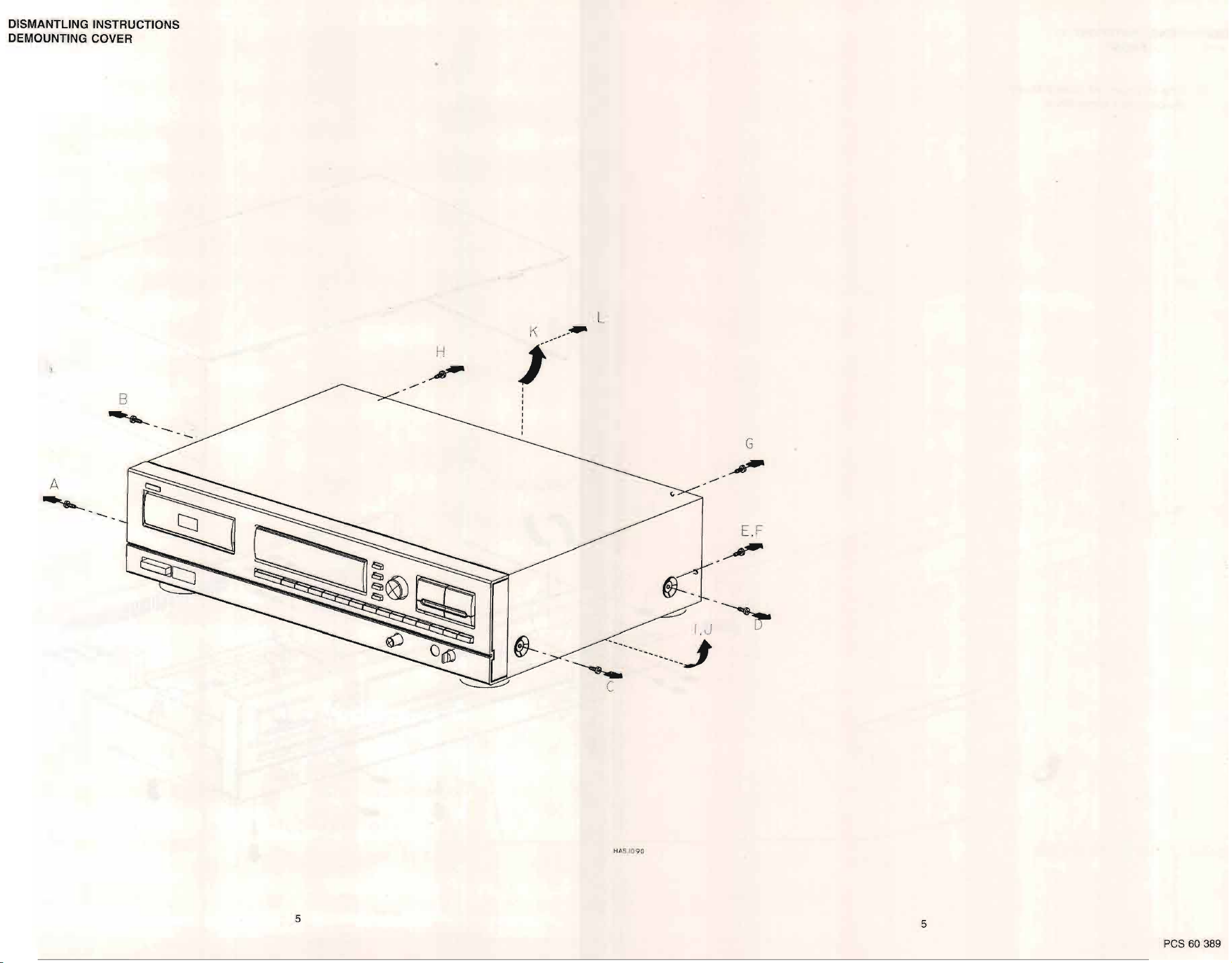

DISMANTLING INSTRUCTIONS

DEMOUNTING COVER

L

B

~-

A

~----

G

~

E,F

~

HAS.109Q

5

5

pes

60 389

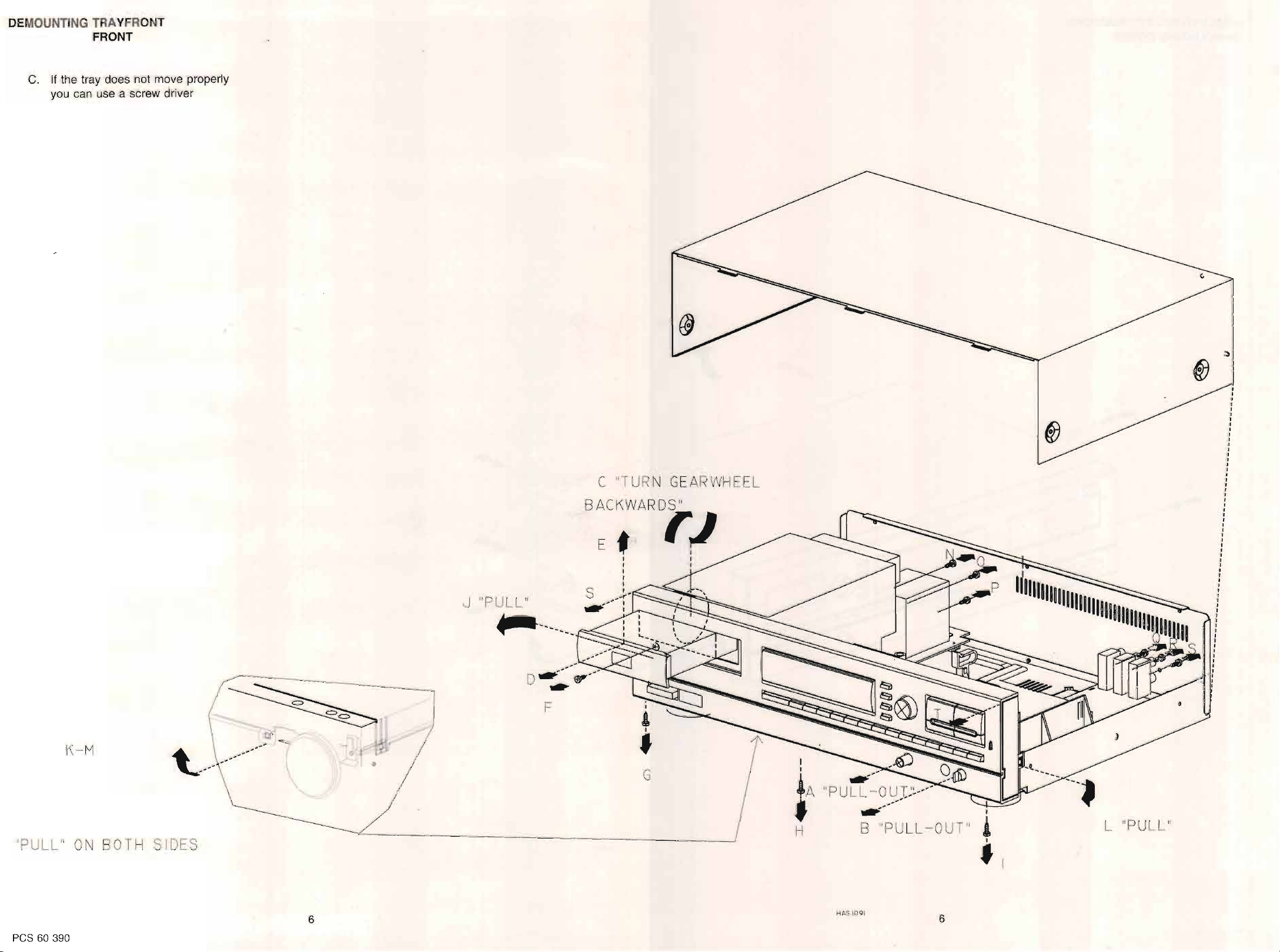

DEMOUNTING TRAYFRONT

FRONT

C.Ifthe tray does not move properly

you can use a screw driver

BACKWARDS"

J "PULL"

~-------

F

C "TURN GEARWHEEL

Et

rJ

I

I

I

,

,

I

,

I

,

I

I

I

I

,

I

I

I

I

,

I

,

I

I

,

I

,

,

,

,

,

,

•

,

I

I

I

,

I

I

I

,

I

,

I

,

I

I

,

I

,

,

,

,

I

,

I

,

I

I

'PULL"

pes

60 390

K-M

ON

BOTH SIDES

G

L "PULL"

6

HAS.I091

6

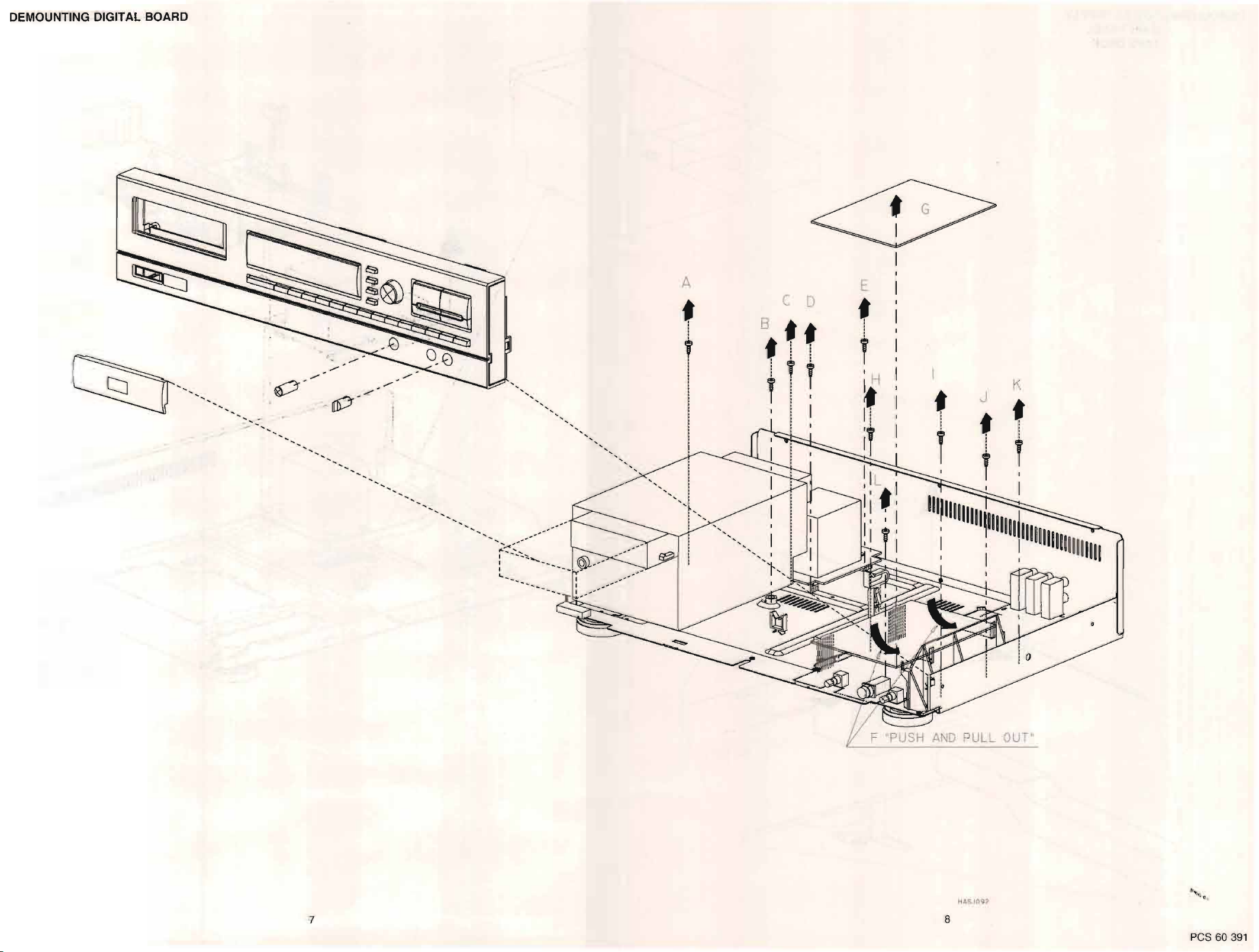

DEMOUNTING DIGITAL BOARD

A

f

t

!

l

!

!

i

C D

B.ff

! , .

Ti r

I i I

: I

:

K

• t f

t i ,

F "PUSH

AND

T I

I

PULL

I

OUT"

HAS.I09?

7

8

pes

60

391

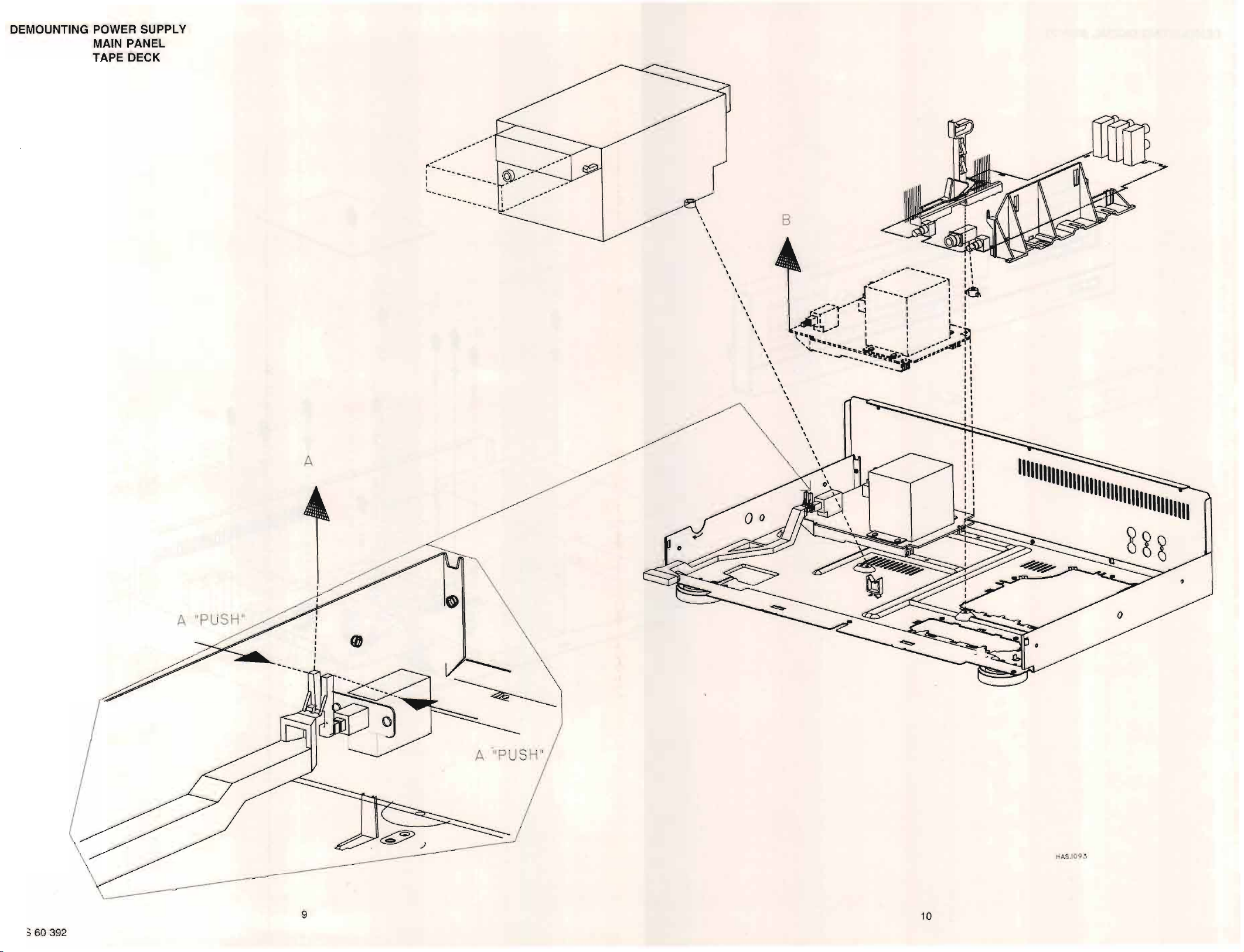

DEMOUNTING POWER SUPPLY

MAIN PANEL

TAPE DECK

A

--

--

---

--

...

_-

: ------

I

'-.

-.

'-.

---

--

..

".

\

\

\

\

\

\

\

\

\

\

\

\

\

\

\

\

\

B

;"..--

.....

",;

__

1---- ----- :

_~_

/~

--

_--,..

I'

__

-..J

, ,

~~

- .......

"'--..

\

\

\

\

\

\

\

\

\

\

\

\

\

"

'J'

~

-

-'1--

~

..

, ' :

,1

....'

'4... -

.....__...

\

\

\

\

\

\

\

\

\

\

\

\

...

_ I

-

...

__

T

' "

I

, ,

...j.." _

-1:1"-

~

;,'

...

"

I '

"

..

:-:.,

I

~

~

':

I,

r---~'

-'

_-

.,.-

....

·~II

,.-

I I

I I

It

"

"

"

"

I'

"

,'

I:

11111111111111111111111111111111111111111

888

pes

60 392

HAS.I093

9

10

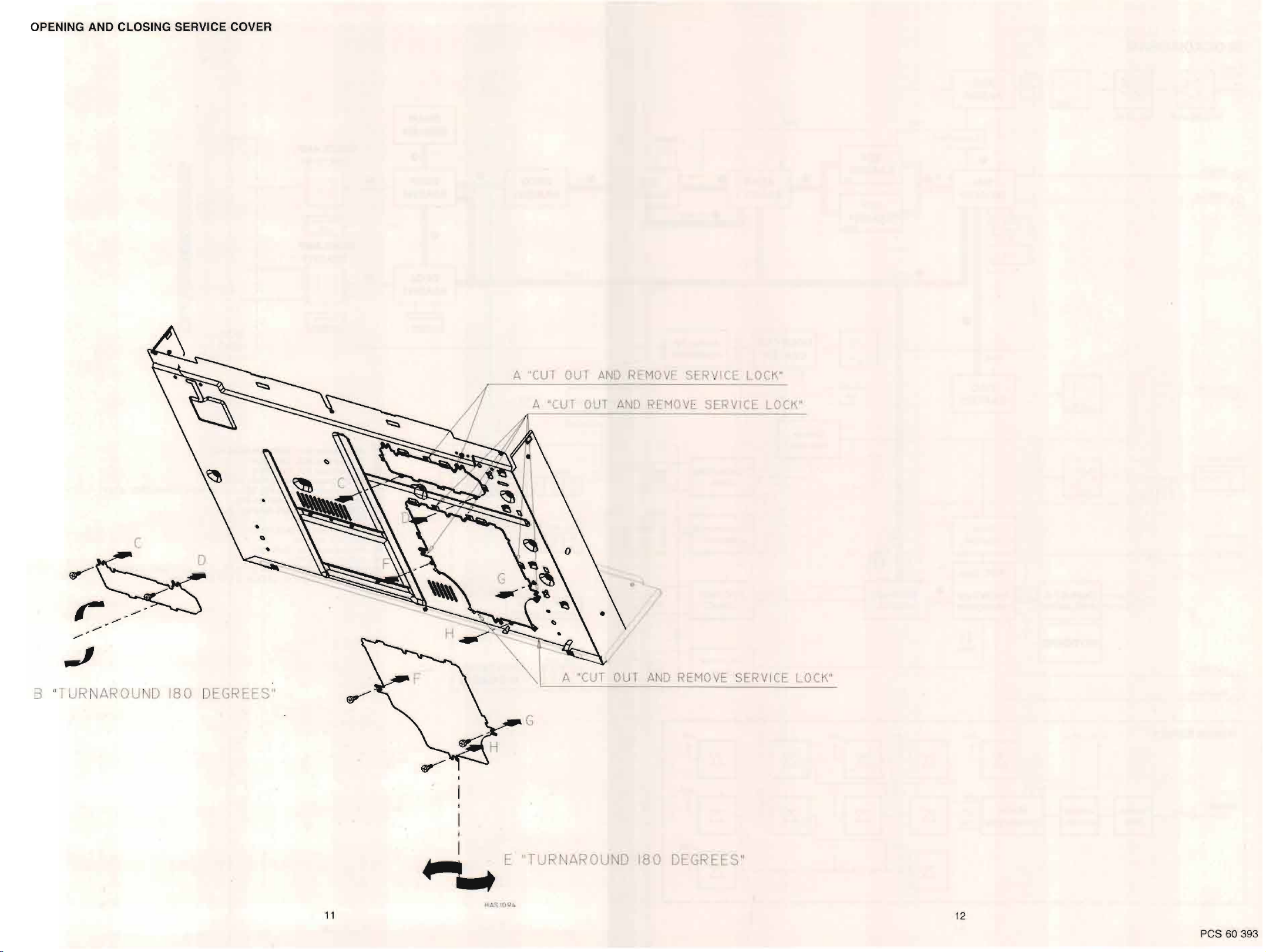

OPENING AND CLOSING SERVICE COVER

c

B "TURNAROUND 180 DEGREES"

A "CUT

A "CUT

OUT

A

OUT

"CUT

AND

REMOVE

AND

OUT

REMOVE

)

AND

REMOVE

SERVICE LOCK"

SERVICE LOCK"

SERVICE LOCK"

11

HAS

G

"TURNAROUND 180 DEGREES"

1094

12

pes

60

393

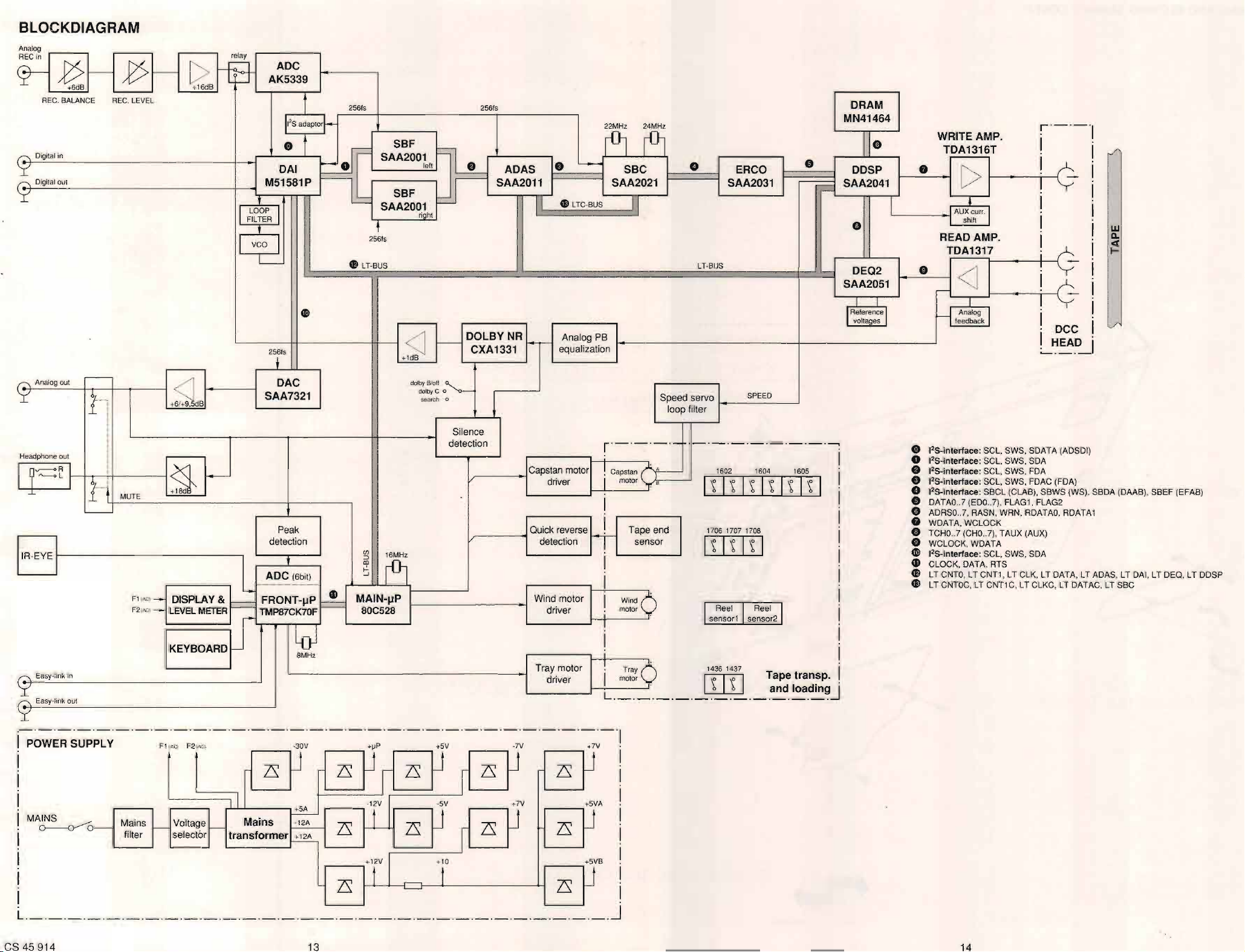

BLOCKDIAGRAM

A log

n.

REC

in

-

7-

Digital

Digital out

p

+6dB

REC.BALANCE

in

p

REC.

LEVEL

relay

-

[>

S

+16dB

Ir

Ir

ADC

AK5339

T

IlS

adaPtor~

G f

DAI

M51581P

256'5

dJF

IlL

LOOP

FILTER

t t

vco

l-

~

2sts

lfJ

SBF

SAA2001 h

SBF r

SAA2001

25615

LT·BUS

<J

+1dB

left e

~nht

f---

256ls

'--

f---

e

Gl

LTC·BUS

Analog

equalization

ADAS

SAA2011 SAA2021

DOLBY NR

CXA1331

fDl

PB

SBC

N

fDl

•

LT·BUS

ERCO

SAA2031

•

;::;::

L

DRAM

MN41464

10

DDSP

SAA2041

0

DEQ2

SAA2051

I

Reference

vol1aoes

WRITE AMP.

TDA1316T

•

I

READ AMP.

0

~

I H

[>

I

I AUXcurr.

I

shift

TDA1317

<J

Analog

feedback

1

r'-'

1

1

!

1

1

1

i

!

1

1

1

~.-

DC

HEA

w

a.

~

C

D

out

L I

in

out

-

A.

I--

A.

L--

MUTE

F1

IAC)-

;,~-

+~B

I--

S}

DISPLAY &

""'-

.....

KEYBOARD

f---

~

L.

DAC

SAA7321

Peak

detection detection

dolbyBloll

dolby

search

o~

c 0

0

detection

Silence

Capstan

Quick

•

ADC (6bit)

1---------

FRONT-IJP I

TMP87CK70F

loJ

8M

Gl

Hz

fDl

MAIN-IJP

80C528

Wind

Tray

driver

reverse

motor

driver

motor

driver

~

Analog out

'i'

Headphone

~~RI

"---<>

-= l-l

IR-EYE

Easy-link

Easy-link

_._._._._._._._._._.-.-._._._._._._._._._._._._._._._.-'-'-'-'1

POWER SUPPLY

F1

lAC)

F2

(ACj

30V

+~P

sv

7V

motor

Speed

servo

loop

filter

r'-'-'-'-

I

.

i

J:.

CaPSta~

(

motor

yB

r--

'-'-'-'-'-'-'-'-'

1602

u::IIIIIillIIl

1

Tape

If-

end

sensor

I

I

Wj~¢

1

motor

;

~

_

I

i

!

Tray 1436 1437

;0

motor _ [Iill Tape

I

L.

+7V·

'-'-'-'-'-'-'-'-'-'

1706

[illJIJ

rReel 1Reel

sensor1

1707

SPEED

1604

1708

sensor2

and loadingJ

1605

I

1

I

1

1

1

1

1

1

1

1

tran~p.

.

!

G

I'S-interlace:

"S-interlace:

•

e

"S-interlace:

e

"S-interlace:

0

"S-interlace:

DATAO..7

•

ADRSO..7,

•

WDATA, WCLOCK

•

0

TCHO..7

0 WCLOCK, WDATA

~

"S-interlace:

Gl

CLOCK, DATA,

lfJ

LT

CNTO,LTCNT1, LT CLK,LTOAT

Gl

LT

CNTOC,

SCL, SWS, SDATA (AD

SCL, SWS, SDA

SCL, SWS,

SCL, SWS, FDAC (FDA

SBCL (CLAB), SBWS (

(EDO..7), FLAGt, FLAG2

RASN, WRN,

(CHO..7), TAUX

SCL, SWS, SDA

RTS

LT CNTtC,LT CLKC, LT

FDA

RDATAO,

(AU

X)

SOl)

)

WS), SBDA (DAAB), SBEF (EFAB)

ATA1

RD

A,

LT ADAS, LT DAI, LT DEQ, LT DDSP

DATAC,LTSBC

ZS

0

ZS

J

ZS ZS

J I

J

ZSJ

i

I

MA~

>-

Mains

filter

I--

Voltage

selector

I--

transformer

Mains

L._._._._._._._._._._._._._._._._._._._._._._._._._._._._._._.J

CS 45 914

~

~

·12A

13

ZS

ZS

11

+f

I

E J I

T

ZS

,:r

0

ZS

zsO

VA

VB

14

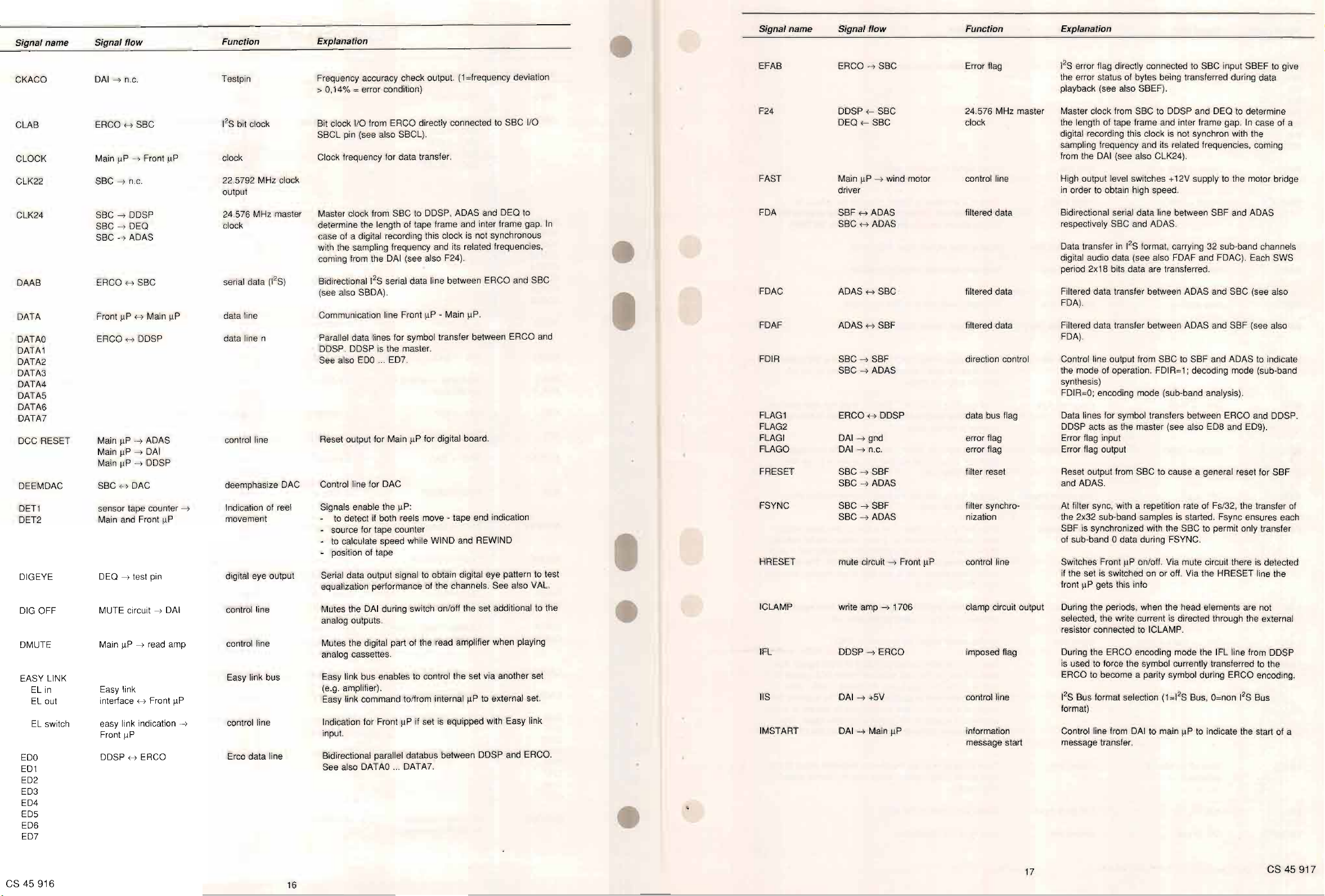

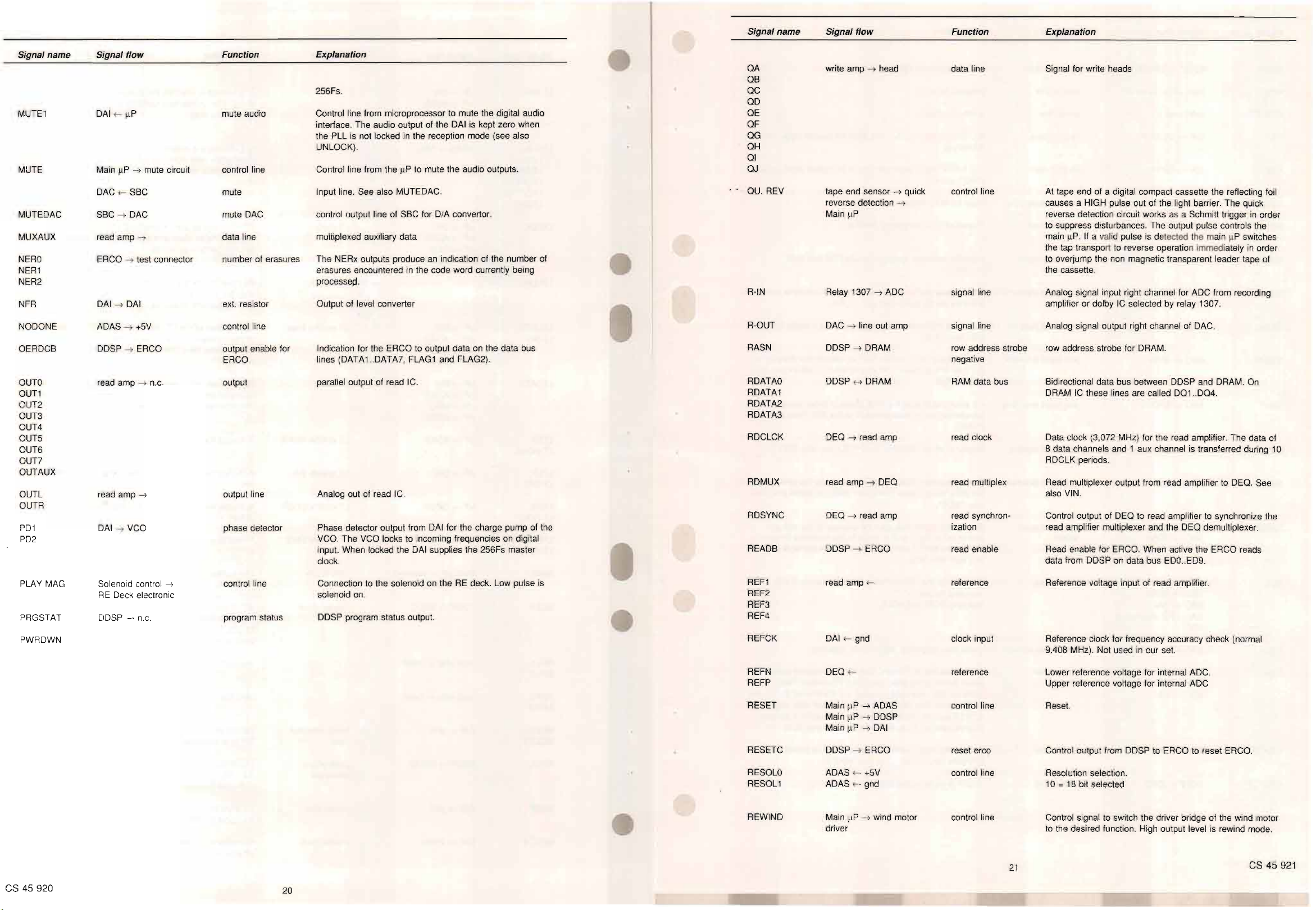

Description

of

signal

names

Signal name Signal flow Function

128Fs SBC

256Fs SBC

ADRSO

ADRS1

ADRS2

ADRS3

ADRS4

ADRS5

ADRS6

ADRS7

ADSDI

ADSEL

ANA L

ANA R

-->

n.C.

.....

DAI system clock

-->

SBF

SBC

-->

ADC

SBC

-->

DAC

SBC

-->

ADAS

SBC

-->

-->

-->

DAI

gnd

DRAM

-->

analog Pb

DDSP

ADC

DAI

read amp

equalization

clock

address lines

analog/digital serial

data input

control line

signal line

Explanation

Clock output from SBC, 128 x sampling frequency.

Master clock signal (256 x sampling frequency) for SBF,

DAI, ADC, DAC and ADAS.

exception of the mode Digital Record.

is the MASTER and supplies 256Fs on MSTCK pin. See

also MSTCK.

Fs=32 kHz for DAB, DSR or

Fs=44.1

Fs=48 kHz for professional recording and OAT.

8 address lines

data into or reading data from memory.

DAI input for serial data from AD convertor (see also S-

DATA).

Serial data output source selection

Analog signal left (right) channel playback analog compact

cassette.

kHz forCDand DCC.

to

DRAM to locateanaddress for writing

Is

generated by SBC with

In

that case the

BS

(digital audio broadcast).

DAI

ASL

An

AnDAC

AUX

AUXENV

AZCHK

BIASA

BIASD

CAP A

CAP B

CAPSTAN

CASN

CHO

CH1

CH2

CH3

CH4

CH5

CH6

CH7

DAI

-->

+5V

SBC

-->

DAC

-->

DAC

SBC

DEQ

-->

DDSP

-->

-->

-->

-->

-->

-->

Main IlP

test pin

high

low

-->

7359

DRAM

DDSP

DEQ

DDSP

DEQ

DEQ

Capstan motor

control

Main IlP

DDSP

DEQ

-->

speed

control line

attenuation

attenuate DAC

auxiliary channel

output

auxiliary envelope

azimuth check

control line

control line

control line

control line

control line

channel n

Audio sample length selection

Data input for DAC to set his attenuation register.

Control line (output from SBG) connected to DAC

attenuation input.

Sliced output from DEQ of auxiliary channel data (bit rate

12 kb/s) routed to DDSP input TAUX.

_Digital representation of the AUX signal and monitors

during DCC search mode the start of a track.

Monitors the azimuth of channels 0 and 7 (output of

DDSP).

Bias current for internal AID converter of DEQ2

Bias current for internal AID converter of DEQ2

Via connection points A and B of capstan motor the

reference of the integrated speed control is controlled by

the additional external speed control.

Low output level switches the capstan motor on.

Column address strobe for DRAM

to

DEQ channel n output

DDSP inputs

TCHO

..TCH7.

CHROME

RE

Deck electronic

AnalogPbequalization

-->

control line

15

Indication if a chrome analog cassette

Cassette is high level.

is

inserted. Chrome

CS45915

Signal name

CKACO

CLAB

Signal flow

DAI

ERCO H SBC

CLOCK Main

CLK22

SBC

-->

~P

-->

n.C.

n.C.

-->

Front

~P

Function

Testpin

2

S bit clock

1

clock

22.5792 MHz clock

output

Explanation

(1

Frequency accuracy check output.

> 0,14% = error condition)

=frequency deviation

Bit clock I/O from ERCO directly connected to SBC I/O

SBCL pin (see also SBCL).

Clock frequency for data transfer.

Signal name Signal flow Function Explanation

2

S error flag directly connectedtoSBC input SBEFtogive

EFAB ERCO

-->

SBC Error flag

1

the error status of bytes being transferred during data

playback (see also SBEF).

F24 DDSP

DEQ

<- SBC 24.576 MHz master

<- SBC clock the length of tape frame and inter frame gap.

Master clock from SBC

digital recording this clock

sampling frequency and its related frequencies, coming

DAI

ordertoobtain high speed.

FAST

Main

driver

~P

-->

wind motor

from the

control line High output level switches +12V supply

in

to

DDSP and DEQtodetermine

is

not synchron with the

(see also CLK24).

In

case of a

to

the motor bridge

CLK24

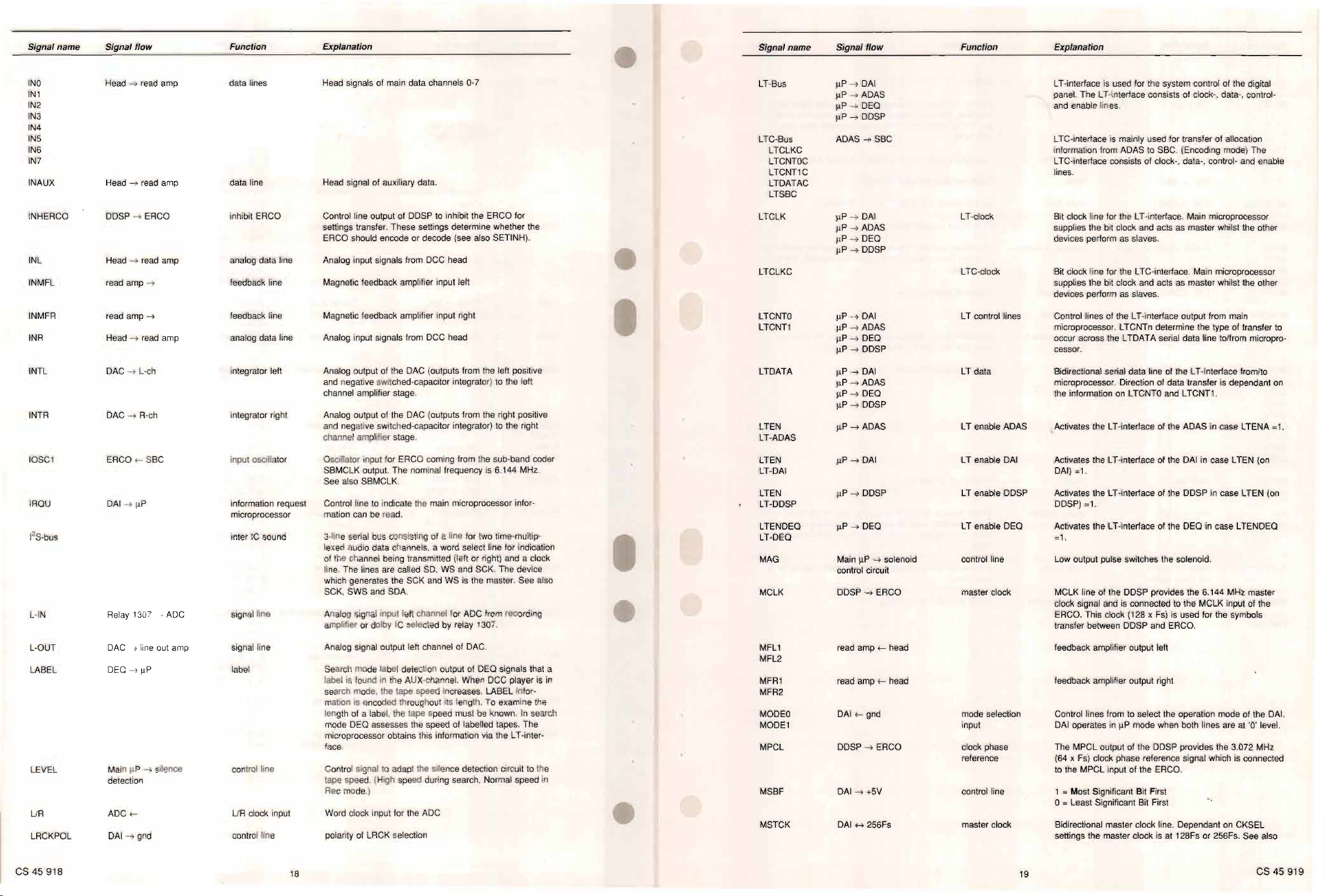

SBC

SBC

SBC

DAAB

DATA

DATAO

ERCO

Front

ERCO H DDSP

DATA1

DATA2

DATA3

DATA4

DATA5

DATA6

DATA7

DCC RESET

Main

Main

Main

DEEMDAC

DEn

DET2

SBC

sensor tape counter

Main and Front

DIGEYE DEQ

-->

DDSP

-->

DEQ

-->

ADAS

H SBC

~P

H Main

~P

-->

~P

-->

~

P

-->

H DAC

-->

test pin

ADAS

DAI

DDSP

~P

~P

-->

24.576 MHz master

clock

serial data

(12S)

data line

data line n

control line

deemphasize DAC

Indication of reel

movement

digital eye output

Master clock from SBC to DDSP, ADAS and DEQ to

determine the length of tape frame and inter frame gap.

is

case of a digital recording this clock

not synchronous

with the sampling frequency and its related frequencies,

coming from the DAI (see also F24).

Bidirectional 12S serial data line between ERCO and SBC

(see also SBDA).

~P

- Main

Communication line Front

~P.

Parallel data lines for symbol transfer between ERCO and

is

DDSP. DDSP

See also

Reset output for Main

the master.

EDO..ED7.

~P

for digital board.

Control line for DAC

Signals enable the

to

detect if both reels move - tape end indication

~P:

source for tape counter

to calculate speed while WIND and REWIND

position of tape

to

Serial data output signal

obtain digital eye pattern to test

equalization performance of the channels. See also VAL.

FDA SBF

In

H ADAS filtered data Bidirectional serial data line between SBF and ADAS

SBC H ADAS respectively SBC and ADAS.

in

Data transfer

12S format, carrying32sub-band channels

digital audio data (see also FDAF and FDAC). Each SWS

period 2x18 bits data are transferred.

FDAC

H SBC filtered data Filtered data transfer between ADAS and SBC (see also

ADAS

FDA).

FDAF ADAS H SBF filtered data Filtered data transfer between ADAS and SBF (see also

FDA).

FDIR

-->

SBC

SBC

SBF direction control Control line output from SBC to SBF and ADAStoindicate

-->

ADAS the mode of operation. FDIR=1; decoding mode (sub-band

synthesis)

FLAG1

ERCO H DDSP data bus flag Data lines for symbol transfers between ERCO and DDSP.

FLAG2

FLAGI

FLAGO

DAI

DAI

FRESET SBC

SBC

FSYNC SBC

SBC

FDIR=O;

DDSP acts as the master (see also ED8 and ED9).

-->

gnd error flag Error flag input

-->

n.c. error flag Error flag output

-->

SBF filter reset Reset output from SBCtocause a general reset for SBF

-->

ADAS and ADAS.

-->

SBF filter synchro- At filter sync, with a repetition rate of Fs/32, the transfer of

-->

ADAS nization the 2x32 sub-band samplesisstarted. Fsync ensures each

SBF

encoding mode (sub-band analysis).

is

synchronized with the SBC to permit only transfer

of sub-band 0 data during FSYNC.

HRESET

mute circuit

-->

Front

~P

control line

Switches Front

is

if the set

front

switchedonor off. Via the HRESET line the

~P

gets this info

~P

on/off. Via mute circuit thereisdetected

DIG OFF

DMUTE

EASY LINK

in

EL

EL out

EL switch

EDO

ED1

ED2

ED3

ED4

ED5

ED6

ED7

CS45916

~P

-->

read amp

-->

MUTE circuit

Main

Easy link

interface

H Front

easy link indication

~P

Front

DDSP H ERCO

DAI

~P

-->

control line

control line

Easy link bus

control line

Erco data line

16

DAI

Mutes the

during switch on/off the set additional to the

analog outputs.

Mutes the digital part of the read amplifier when playing

analog cassettes.

Easy link bus enables to control the set via another set

(e.g. amplifier).

Easy link command to/from internal~Pto

~P

Indication for Front

if setisequipped with Easy link

ex1ernal

set.

input.

Bidirectional parallel databus between DDSP and ERCO.

See also

DATAO

...

DATA7.

ICLAMP

IFL

liS

IMSTART

write amp

-->

DDSP

-->

DAI

DAI

-->

-->

1706 clamp circuit output During the periods, when the head elements are not

is

selected, the write current

directed through the external

resistor connected to ICLAMP.

ERCO imposed flag During the ERCO encoding mode the IFL line from DDSP

is

used to force the symbol currently transferred to the

ERCO to become a parity symbol during ERCO encoding.

+5V

control line

12S Bus format selection(1=12S Bus,

O=non

12S Bus

format)

Main

~P

information

Control line from

DAI

to main~Pto

indicate the start of a

message start message transfer.

17

CS45917

Signal name Signal flow Function

Explanation

Signal name

Signal flow Function Explanation

INO

IN1

IN2

IN3

IN4

IN5

IN6

IN7

INAUX

INHERCO DDSP

INL Head

INMFL read amp

INMFR read amp

INR Head

INTL DAC

INTR DAC

Head~read amp data lines

~

Head

~

~

~

~

~

read amp data line

ERCO

read amp

~

~

read amp analog data line

L-ch

R-ch

inhibit ERCO

analog data line

feedback line

feedback line

integrator left

integrator right

Head signals of main data channels 0-7

Head signal of auxiliary data.

Control line output of DDSP to inhibit the ERCO for

settings transfer. These settings determine whether the

ERCO should encode or decode (see also SETINH).

Analog input signals from DCC head

Magnetic feedback amplifier input left

Magnetic feedback amplifier input right

Analog input signals from DCC head

Analog output of the DAC

and negative switched-capacitor integrator) to the left

channel amplifier stage.

Analog output of the DAC (outputs from the right positive

and negative switched-capacitor integrator) to the right

channel amplifier stage.

(ou1puts

from the left positive

LT-Bus

LTC-Bus ADAS

LTCLKC

LTCNTOC

LTCNT1C lines.

LTDATAC

LTSBC

LTCLK

LTCLKC

LTCNTO

LTCNT1

LTDATA

LTEN

LT-ADAS

).lP~DAI

).lP~ADAS panel. The LT-interface consists of clock-, data-, control-

).lP~DEQ and enable lines.

).lP~DDSP

~

SBC

).lP~DAI

).lP~ADAS supplies the bit clock and acts as master whilst the other

).lP~DEQ devices perform as slaves.

).lP~DDSP

).lP~

DAI

).lP~ADAS

).lP~DEQ occur across the LTDATA serial data line tolfrom micropro-

).lP~DDSP cessor.

).lP~DAI

).lP

~ADAS

).lP~DEQ the information on L

).lP~DDSP

).lP~ADAS L

LT-c1ock

LTC-clock

LT control lines Control lines of the LT-interface output from main

LT data Bidirectional serial data line of the LT-interface fromlto

Tenable

ADAS Activates the LT-interface of the ADAS in case LTENA =1.

LT-interface is used for the system control of the digital

is

LTC-interface

information from ADAS to SBC. (Encoding mode) The

LTC-interface consists of

Bit clock line for the LT-interface. Main microprocessor

Bit clock line for the LTC-interface. Main microprocessor

supplies the bit clock and acts as master whilst the other

devices perform as slaves.

microprocessor. LTCNTn determine the type of transfer to

microprocessor. Direction of data transferisdependant on

mainly used for transfer of allocation

c1ock-,

data-, control- and enable

TCNTO

and LTCNT1.

IOSC1

IRQU

2

1

S-bus

L-IN Relay 1307

L-OUT DAC~line out amp

LABEL

LEVEL Main

UR

LRCKPOL DAI

ERCO <- SBC

~).lP

DAI

~

DEQ~

).lP

).lP~silence

detection

ADC <-

~

gnd

ADC

input oscillator

information request

microprocessor

IC

sound

inter

signal line

signal line

label

control line

UR

clock input Word clock input for the ADC

control line

Oscillator input for ERCO coming from the sub-band coder

SBMCLK output. The nominal frequency is 6.144 MHz.

See also SBMCLK.

Control line to indicate the main microprocessor infor-

be

mation can

3-line serial bus consisting of a line for two time-multip-

lexed audio data channels, a word select line for indication

of the channel being transmitted (left or right) and a clock

line. The lines are called SD,

which generates the SCK and WS is the master. See also

SCK, SWS and SDA.

Analog signal input left channel for ADC from recording

amplifier or dolby

Analog signal output left channel of DAC.

Search mode label detection output of DEQ signals that a

label is found in the AUX-channel. When DCC player

search mode, the tape speed increases. LABEL infor-

mation is encoded throughout its length. To examine the

length of a label, the tape speed must

mode DEQ assesses the speed of labelled tapes. The

microprocessor obtains this information via the LT-inter-

face.

Control signal

tape speed. (High speed during search, Normal speed in

Rec mode.)

polarity of LRCK selection

read.

to

adapt the silence detection circuit to the

WS

and SCK. The device

IC

selected by relay 1307.

be

known.Insearch

).lP~

LTEN

LT-DAI DAI) =1.

LTEN

LT-DDSP DDSP) =1.

LTENDEQ

LT-DEQ

MAG Main

•

is

in

MCLK DDSP

MFL1

MFL2

MFR1

MFR2

MODEO

MODE1

MPCL DDSP

MSBF DAI

DAI

).lP~DDSP

).lP~DEQ L

).lP~solenoid control line Low output pulse switches the solenoid.

control circuit

~

ERCO master clock MCLK line of the DDSP provides the 6.144 MHz master

read amp <- head feedback amplifier output left

read amp <- head

DAI <- gnd mode selection Control lines from to select the operation mode of the DAI.

~

ERCO clock phase The MPCL output of the DDSP provides the 3.072 MHz

~

+5V

L

Tenable

Tenable

L

Tenable

input

reference (64 x Fs) clock phase reference signal which is connected

control line

DAI Activates the LT-interface of the DAI in case LTEN (on

DDSP Activates the LT-interface of the DDSP in case LTEN

DEQ Activates the LT-interface of the DEQ in case LTENDEQ

=1

.

clock signal and is connected

ERCO. This clock (128 x Fs) is used for the symbols

transfer between DDSP and ERCO.

feedback amplifier output right

DAI

operatesin).lP

to the MPCL input of the ERCO.

1 = Most Significant Bit First

mode when both lines are at '0' level.

to

the MCLK input of the

(on

o= Least Significant Bit First

DAI

.....

MSTCK

256Fs master clock Bidirectional master clock line. DependantonCKSEL

is

settings the master clock

at 128Fs or 256Fs. See also

CS45918

18

19

CS45919

Loading...

Loading...