Philips 74HCT164PW, 74HCT164N, 74HCT164DB, 74HCT164D, 74HC164U Datasheet

...

DATA SH EET

Product specification

File under Integrated Circuits, IC06

December 1990

INTEGRATED CIRCUITS

74HC/HCT164

8-bit serial-in/parallel-out shift

register

For a complete data sheet, please also download:

•The IC06 74HC/HCT/HCU/HCMOS Logic Family Specifications

•The IC06 74HC/HCT/HCU/HCMOS Logic Package Information

•The IC06 74HC/HCT/HCU/HCMOS Logic Package Outlines

December 1990 2

Philips Semiconductors Product specification

8-bit serial-in/parallel-out shift register 74HC/HCT164

FEATURES

• Gated serial data inputs

• Asynchronous master reset

• Output capability: standard

• ICC category: MSI

GENERAL DESCRIPTION

The 74HC/HCT164 are high-speed Si-gate CMOS devices

and are pin compatible with low power Schottky TTL

(LSTTL). They are specified in compliance with JEDEC

standard no. 7A.

The 74HC/HCT164 are 8-bit edge-triggered shift registers

with serial data entry and an output from each of the eight

stages.

Data is entered serially through one of two inputs (D

sa

or

Dsb); either input can be used as an active HIGH enable for

data entry through the other input.

Both inputs must be connected together or an unused

input must be tied HIGH.

Data shifts one place to the right on each LOW-to-HIGH

transition of the clock (CP) input and enters into Q0, which

is the logical AND of the two data inputs (Dsa,Dsb) that

existed one set-up time prior to the rising clock edge.

A LOW level on the master reset (MR) input overrides all

other inputs and clears the register asynchronously,

forcing all outputs LOW.

QUICK REFERENCE DATA

GND = 0 V; T

amb

= 25 °C; tr= tf= 6 ns

Notes

1. C

PD

is used to determine the dynamic power dissipation (PDin µW):

PD= CPD× V

CC

2

× fi+∑(CL× V

CC

2

× fo) where:

fi= input frequency in MHz

fo= output frequency in MHz

∑ (CL× V

CC

2

× fo) = sum of outputs

CL= output load capacitance in pF

VCC= supply voltage in V

2. For HC the condition is VI= GND to V

CC

For HCT the condition is VI= GND to VCC− 1.5 V

ORDERING INFORMATION

See

“74HC/HCT/HCU/HCMOS Logic Package Information”

.

SYMBOL PARAMETER CONDITIONS

TYPICAL

UNIT

HC HCT

t

PHL

/ t

PLH

propagation delay

CP to Q

n

MR to Q

n

CL= 15 pF; VCC= 5 V

12

11

14

16

ns

ns

f

max

maximum clock frequency 78 61 MHz

C

I

input capacitance 3.5 3.5 pF

C

PD

power dissipation capacitance per

package

notes 1 and 2

40 40 pF

December 1990 3

Philips Semiconductors Product specification

8-bit serial-in/parallel-out shift register 74HC/HCT164

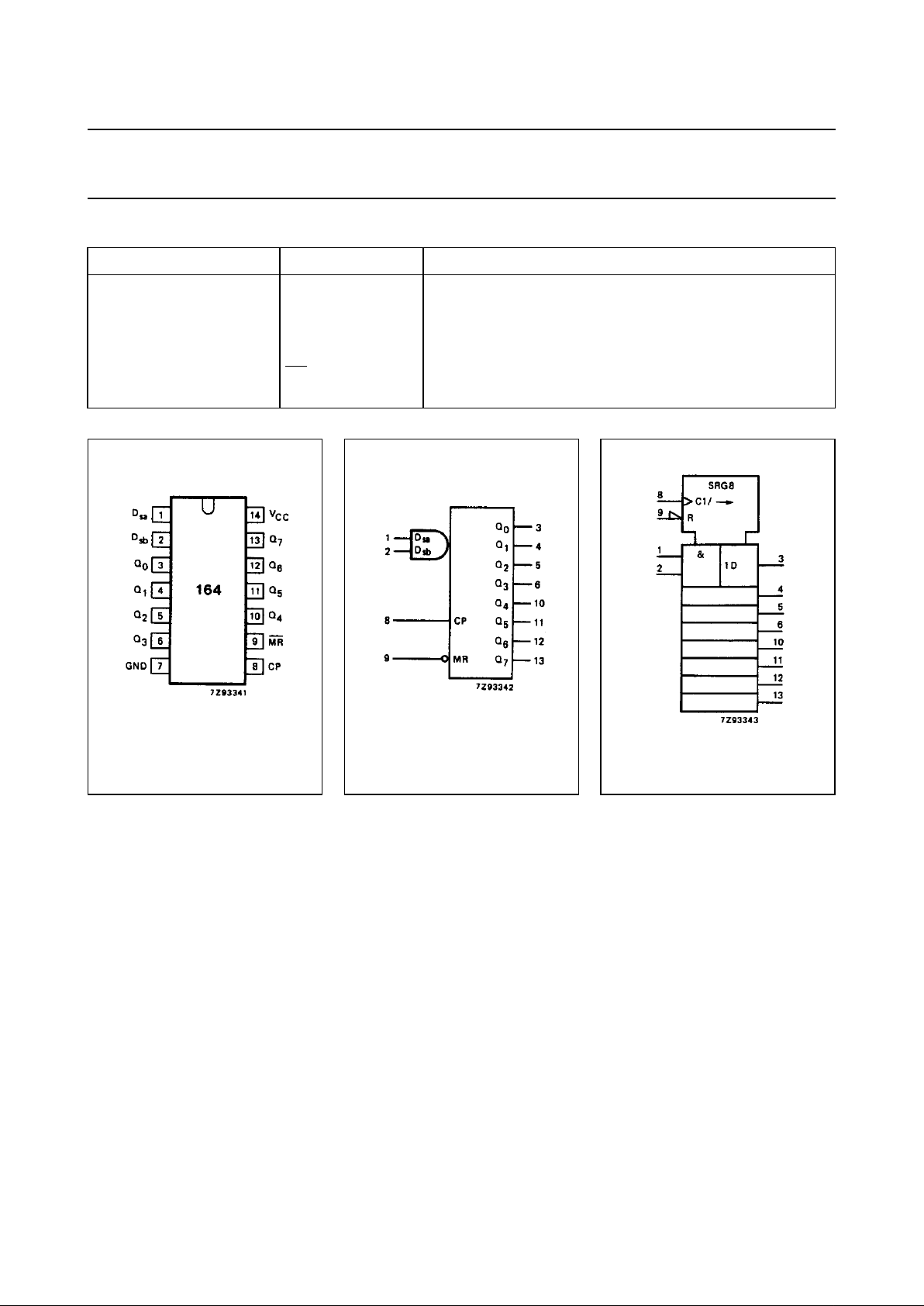

PIN DESCRIPTION

PIN NO. SYMBOL NAME AND FUNCTION

1, 2 D

sa,Dsb

data inputs

3, 4, 5, 6, 10, 11, 12, 13 Q

0

to Q

7

outputs

7 GND ground (0 V)

8 CP clock input (LOW-to-HIGH, edge-triggered)

9

MR master reset input (active LOW)

14 V

CC

positive supply voltage

Fig.1 Pin configuration. Fig.2 Logic symbol.

Fig.3 IEC logic symbol.

Loading...

Loading...