Philips 74HC_HCT258 Datasheet

DATA SH EET

Product specification

File under Integrated Circuits, IC06

1999 Sep 02

INTEGRATED CIRCUITS

74HC/HCT258

Quad 2-input multiplexer; 3-state;

inverting

1999 Sep 02 2

Philips Semiconductors Product specification

Quad 2-input multiplexer; 3-state; inverting 74HC/HCT258

FEATURES

• Inverting data path

• 3-state outputs interface directly with system bus

• Output capability: bus driver

• ICC category: MSI.

GENERAL DESCRIPTION

The74HC/HCT258arehigh-speedSi-gateCMOSdevices

and are pin compatible with Low power Schottky TTL

(LSTTL). They are specified in compliance with JEDEC

standard no. 7A.

The74HC/HCT258havefouridentical2-inputmultiplexers

with 3-state outputs, which select 4 bits of data from two

sources and are controlled by a common data select

input (S).

The data inputs from source 0 (1I0to 4I0) are selected

when input S is LOW and the data inputs from source 1

(1I1to 4I1) are selected when S is HIGH.

Data appears at the outputs (1Yto4Y) in inverted form

from the select inputs.

The‘258’is the logic implementation ofa4-pole,2-position

switch, where the position of the switch is determined by

the logic levels applied to S. The outputs are forced to a

high impedance OFF-state when OE is HIGH.

The logic equations for the outputs are:

The ‘258’ is identical to the ‘257’ but has inverting outputs.

1Y OE 1I

1

S× 1I0S×+()×=

2Y OE 2I1S× 2I0S×+()×=

3Y OE 3I1S× 3I0S×+()×=

4Y OE 4I1S× 4I0S×+()×=

QUICK REFERENCE DATA

GND = 0 V; T

amb

=25°C; tr=tf= 6 ns.

Notes

1. C

PD

is used to determine the dynamic power dissipation (PDin µW):

PD=CPD× V

CC

2

× fi+ ∑ (CL× V

CC

2

× fo) where:

f

i

= input frequency in MHz;

fo= output frequency in MHz;

∑ (CL× V

CC

2

× fo) = sum of outputs;

CL= output load capacitance in pF;

VCC= supply voltage in Volts.

2. For HC the condition is VI= GND to VCC;

For HCT the condition is VI= GND to VCC− 1.5 V.

SYMBOL PARAMETER CONDITIONS

TYPICAL

UNIT

HC HCT

t

PHL/tPLH

propagation delay CL= 15 pF;

VCC=5V

nI

0

,nI1to nY 9 13 ns

Ston

Y 1416ns

C

I

input capacitance 3.5 3.5 pF

C

PD

power dissipation capacitance per multiplexer notes 1 and 2 55 38 pF

1999 Sep 02 3

Philips Semiconductors Product specification

Quad 2-input multiplexer; 3-state; inverting 74HC/HCT258

ORDERING INFORMATION

PIN DESCRIPTION

TYPE NUMBER

PACKAGE

NAME DESCRIPTION VERSION

74HC258N;

74HCT258N

DIP16 plastic dual in-line package; 16 leads (300 mil); long body SOT38-1

74HC258D;

74HCT258D

SO16 plastic small outline package; 16 leads; body width 3.9 mm SOT109-1

74HC258DB SSOP16 plastic shrink small outline package; 16 leads; body width 5.3 mm SOT338-1

PIN NO. SYMBOL NAME AND FUNCTION

1 S common data select input

2, 5, 11 and 14 1I

0

to 4I

0

data inputs from source 0

3, 6, 10 and 13 1I

1

to 4I

1

data inputs from source 1

4, 7, 9 and 12 1

Yto4Y 3-state multiplexer outputs

8 GND ground (0 V)

15

OE 3-state output enable input (active LOW)

16 V

CC

positive supply voltage

page

MGA830

1

2

3

4

5

6

7

8

16

15

14

13

12

11

10

9

258

S

1I

0

1Y

2I

0

2I

1

2Y

GND

1I

1

V

CC

OE

3I

1

4Y

4I

0

4I

1

3Y

3I

0

Fig.1 Pin configuration.

page

MGA832

S

OE

1Y

2Y

3Y

4Y

2

3

5

6

14

13

11

10

15

1

4

7

9

12

1I

0

1I

1

2I

0

3I

1

4I

0

4I

1

3I

0

2I

1

Fig.2 Logic symbol.

page

MGA831

4

3

2

5

6

11

10

14

13

1

15

G1

EN

MUX

1

1

7

9

12

Fig.3 IEC logic symbol.

1999 Sep 02 4

Philips Semiconductors Product specification

Quad 2-input multiplexer; 3-state; inverting 74HC/HCT258

handbook, full pagewidth

MBL095

3-STATE MULTIPLEXER OUTPUTS

SELECTOR

1I

0

OE

S151

23

1I

1

1Y

4

2I

0

5

2I

1

6

14

3I

1

3I

0

13

11

4I

1

4I

0

10

2Y

7

3Y

12

4Y

9

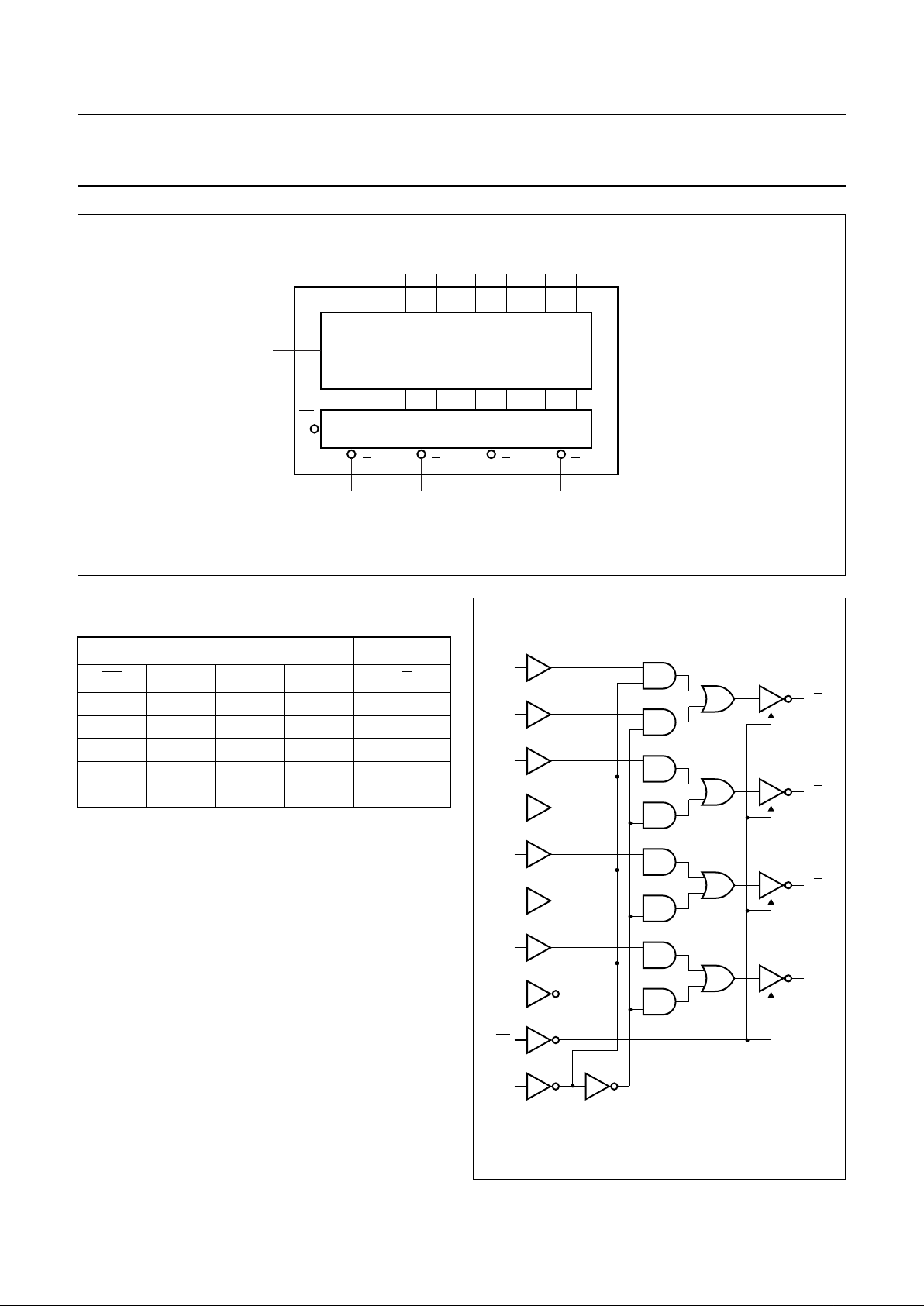

Fig.4 Functional diagram.

FUNCTION TABLE

See note 1

Note

1. H = HIGH voltage level;

L = LOW voltage level;

X = don’t care;

Z = high impedance OFF-state.

INPUTS OUTPUT

OE S nI

0

nI

1

nY

HXXXZ

LHXLH

LHXHL

LLLXH

LLHXL

MBL096

1I

0

1I

1

2I

0

2I

1

3I

0

3I

1

4I

0

4I

1

OE

S

1Y

2Y

3Y

4Y

Fig.5 Logic diagram.

1999 Sep 02 5

Philips Semiconductors Product specification

Quad 2-input multiplexer; 3-state; inverting 74HC/HCT258

DC CHARACTERISTICS FOR 74HC

For the DC characteristics see chapter

“HCMOS family characteristics”

, section “Family specifications”.

Output capability: bus driver.

ICC category: MSI.

AC CHARACTERISTICS FOR 74HC

GND = 0 V; tr=tf= 6 ns; CL=50pF.

SYMBOL PARAMETER

T

amb

(°C)

UNIT

TEST CONDITIONS

25 −40 to +85 −40 to +125

V

CC

(V)

WAVEFORMS

MIN. TYP. MAX. MIN. MAX. MIN. MAX.

t

PHL/tPLH

propagation delay;

nI

0

to nY; nI1to nY

− 30 95 − 120 − 145 ns 2.0 see Fig.6

− 11 19 − 24 − 29 4.5

− 916−20 − 25 6.0

propagation delay;

Ston

Y

− 47 140 − 175 − 210 ns 2.0 see Fig.6

− 17 28 − 35 − 42 4.5

− 14 24 − 30 − 36 6.0

t

PZH/tPZL

3-state output

enable time

OE to nY

− 39 140 − 175 − 210 ns 2.0 see Fig.7

− 14 28 − 35 − 42 4.5

− 11 24 − 30 − 36 6.0

t

PHZ/tPLZ

3-state output

disable time

OE to nY

− 55 150 − 190 − 225 ns 2.0 see Fig.7

− 20 30 − 38 − 45 4.5

− 16 26 − 33 − 38 6.0

t

THL/tTLH

output transition

time

− 14 60 − 75 − 90 ns 2.0 see Fig.6

− 512−15 − 18 4.5

− 410−13 − 15 6.0

Loading...

Loading...