Panjit PJDLC05C-02 Schematic [ru]

PJDLC05C-02

Fig.21

VOLTAGE

5.0 V olts

POWER

200 Watts

ULTRA LOW CAPACIT ANCE DUAL TRANSIET VOL TAGE

SUPPRESSOR FOR HIGH SPEED DA T A LINES

This transient overvoltage suppressor is intended to protect sensitive

equipment against electrostatic discharge events as well to offer a

minimum insertion loss in data transmission lines in communications ports

used in portable consumer, computing and networking applications. This

dual transient voltage suppressor comes in a single SOT-23, offering board

space reduction, where the application requires it.

This device comes with two pairs of high speed switching diodes

connected in series, where both pairs are electrically isolated, offering a

very low capacitance, minimizing the insertion losses in data transmission

lines.

FEA TURES

• Maximum capacitance @ 0 Vdc Bias of 1.0 pF between terminals 1-3 or

terminals 2-3

• IEC61000-4-2 esd 15kV Air, 8kV contact compliance

• Lead free in comply with EU RoHS 2002/95/EC directives.

• Green molding compound as per IEC61249 Std. . (Halogen Free)

MECHANICAL

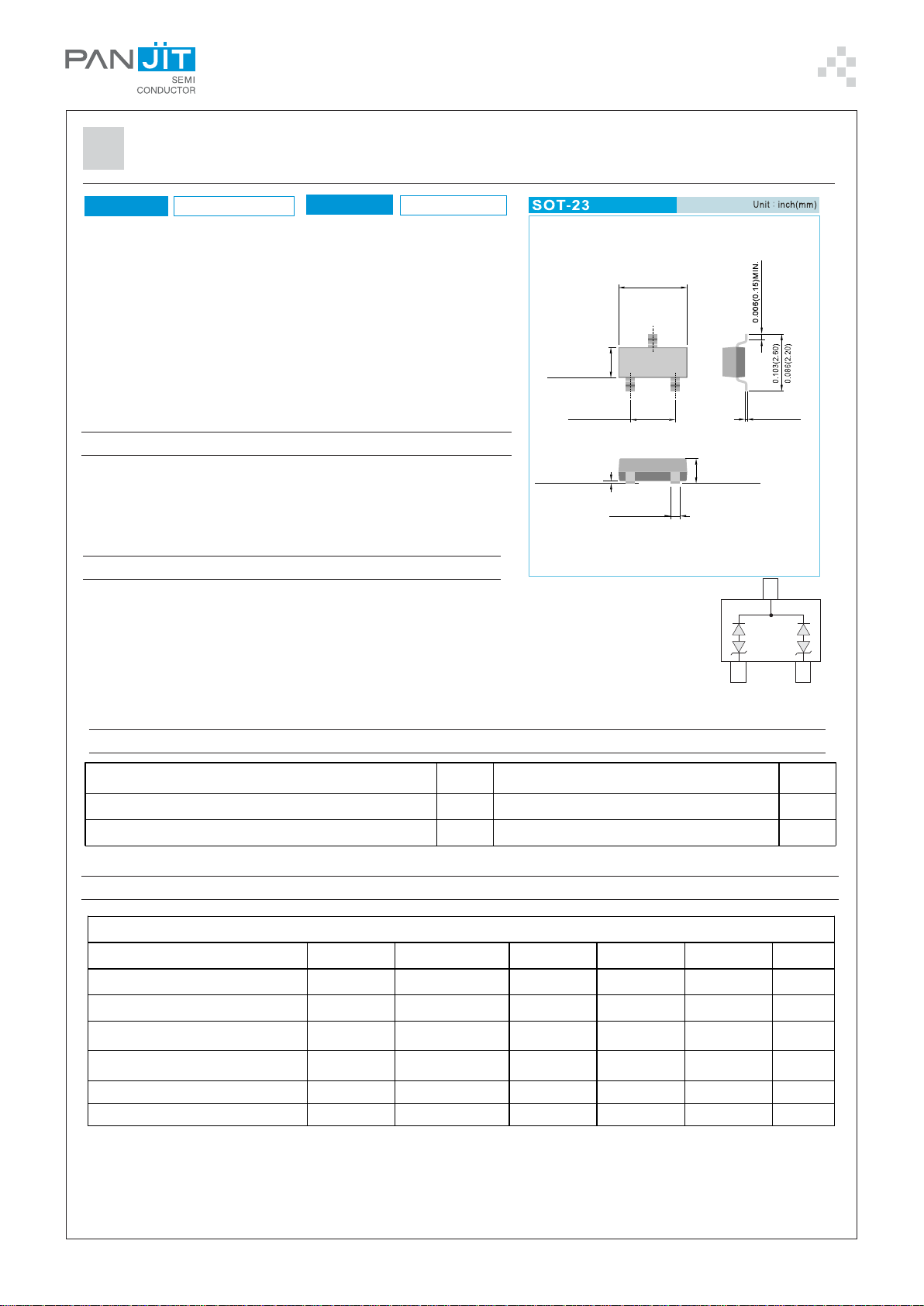

• Case: SOT-23, plastic

• Terminals: solderable per MIL-STD-750, Method 2026

• Approx. Weight: 0.0003 ounce, 0.0084 gram

• Marking : DAA

DAT A

0.0 56 (1. 40 )

0.0 47 (1. 20 )

0.0 79 (2. 00 )

0.0 04 (0. 10 )

0.0 00 (0. 00 )

0.0 70 (1. 80 )

0.0 20 (0. 50 )

0.0 13 (0. 35 )

0.1 20 (3. 04 )

0.11 0(2 .8 0)

0.0 44 (1. 10 )

0.0 35 (0. 90 )

0.0 08 (0. 20 )

0.0 03 (0. 08 )

MAXIMUM RA TINGS

PARAMETER SYMBOL VALUE UNITS

Operating Junction T

Storage Temperature Range T

STG

J

-55 to +150

-55 to +150

O

C

O

C

ELECTRICAL CHARACTERISTICS

PJDLC05C-02

PARAME TER SYMBOL CONDITIONS Min. Typ. Max. UNITS

Reverse Stand-Off Voltage V

Reverse Breakdown Voltage V

Reverse Leakage Current I

Junction Capacitance C

Peak Pulse Current I

Max Clamping Voltage V

RWM

BR

R

J

PP

C

PAN JIT RESER VES THE RIGHT TO CHANGE THE SPECIFICATION ANY TIME WITHOUT NOTICE IN ORDER TO IMPROVE THE

DESIGN AND SUPPLY THE BEST POSSIBLE PRODUCT .

---5V

I T=1mA 6 - - V

V

= 5V,

RWM

O

T = 25

C

Between pin1.2 to 3

V

=0V,f=1MHz

R

--20μA

--1.0pF

t P=8/20 μsec - - 10 A

t P=8/20 μsec - - 20.5 V

February 16,2010-REV.02

PAGE . 1

PJDLC05C-02

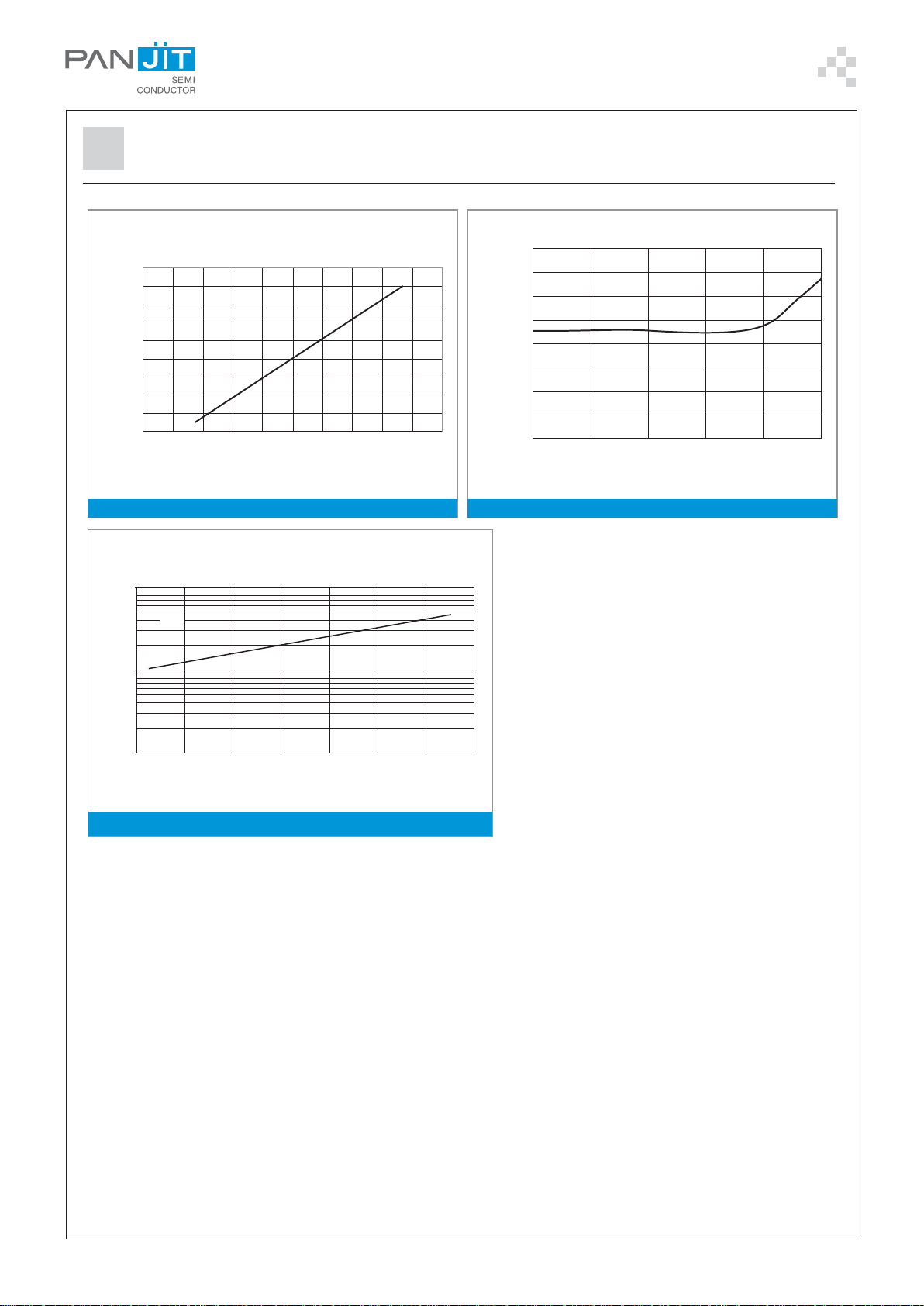

FIG.3- TYPICAL LEAKAGE CURRENT JUNCTION TEMPERATURE

FIG.1- TYPICAL CLAMPING VOLTAGE

FIG.2- TYPICAL JUNCTION CAPACITANCE UNDER BIAS

18

16

14

12

10

8

6

4

2

0

Peak Pulse Cu rren t Ipp , A

5 7 9 1113 151719212325

Clamping Voltage V , V

FIG.1- TYPICAL CLAMPING VOLTAGE

m

1

C

0.7

0.65

0.6

,pF

J

0.55

0.5

0.45

0.4

0.35

Capacitance C

0.3

012345

Reverse Bias Voltage, V

FIG.2- TYPICAL JUNCTION CAPACITANCE UNDER BIAS

VR =5V

0.1

0.01

R

I , Reverse Leakage Current( A)

20 40 60 80 100 120 140 160

TJ, Junction Temperature (°C)

FIG.3- TYPICAL LEAKAGE CURRENT JUNCTION TEMPERATURE

February 16,2010-REV.02

PAGE . 2

Loading...

Loading...