Panasonic SAAK-188 Schematic

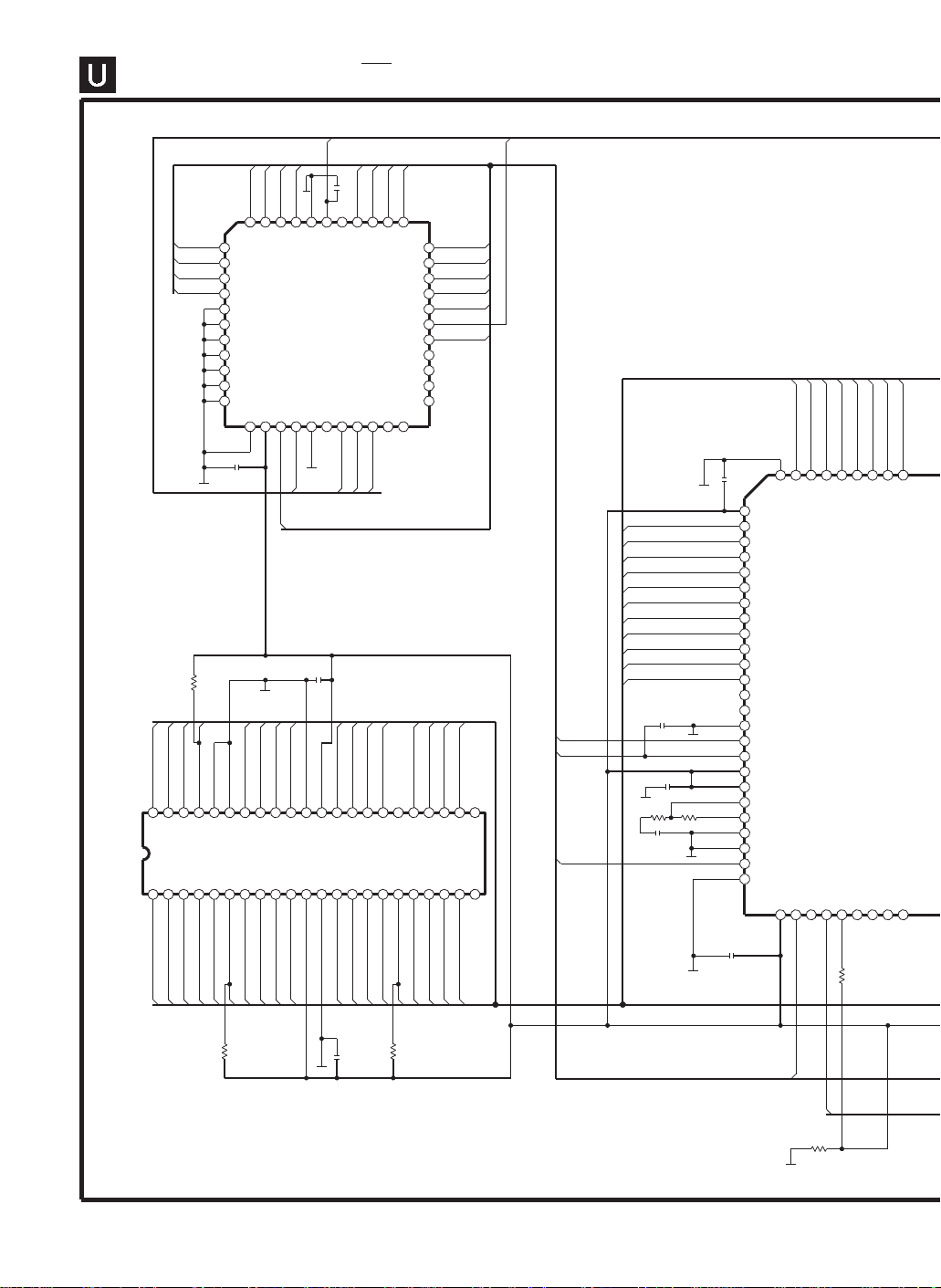

SCHEMATIC DIAGRAM -1

: +B SIGNAL LINE

CD SERVO CIRCUIT

: CD-DA SIGNAL LINE

OPTICAL PICKUP CIRCUIT

LASER DIODE

6

8

11

C

12

10

5

4

9

2

3

C

C

NBOUT

1

8

GND

GND

2

7

VCC

NAOUT

6

3

BIN

VREF

4

5

AIN

C

R701

4.7

C701

R750

5.6

C713

C750

0.1

C751

0.1

6.3V33

0.1

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

VCC

PDF

PDE

LD

LD GND

GND

NB

GND

NA

VREF

LPD

GND

TT+

FF+

Q701

CN701

1

2

3

4

5

6

C

7

8

9

10

11

12

13

14

15

16

Q701

2SA1037AKSTX

LASER POWER DRIVE

C714

6.3V100

AN8885SBE1

IC701

SERVO AMP

C712

0.1

C711

0.1

1

C770

0.1

PDE

FBAL

29

30

C703

6.3V100

C704

0.1

0.1

2700P

C707

C702

0.027

C706

14

1312

LPD

IC701

TEOUT

23 2228

C710

120P

R702

10K

LD

TEN

C742

0.027

876

21

RF

NC

R705

150K

10

11

9

CEA

BDO

RFIN

NC

19

20

GND

LDON

CSBRT

NC

ENV

OFTR

PDOWN

/RFDET

17

15

16

18

3

2

4

5

PDB

PDF

PDA

VCC

FEOUT

TBAL

FEN

VREF

24

25

26

27

C747

180P

R744

120K

C749

1800P

313941 34

R708

22K

R707

39K

33

R706

1K

324042

R704

1K

C735

0.1

C734

10V220

14 13 12 11 10

36

38

D4-

D3-

D3+

D2+

D2-

D1+

C737

0.1

M

M702

SP MOTOR

C736

0.1

M

M701

TRV MOTOR

IC703

AN8739SBE2

FOCUS COIL/

TRACKING COIL/

TRAVERSE MOTOR/

SPINDLE MOTOR DRIVE

22 28272625

23 24

29

2120

1915 16 17 18

GND

PVCC2

IC703

PVCC1

GND

NC

NC

7 6 5 4 3 2 1

30

VCC

IN1NCPC2NCIN2

R735

100

NC

D4+

PGND2

PGND1

NC

D1-

9 8

35

VREF

NC

IN3

IN4

RSTIN

R724

18K

R725

390

R715

1K

/RST

C715

2700P

R727

6.8K

R736

10

C752

1500P

R749

4.7K

C738

0.01

R729

3.9K

28

C739

1500P

R728

3.9K

37

R723

6.8K

R731

6.8K

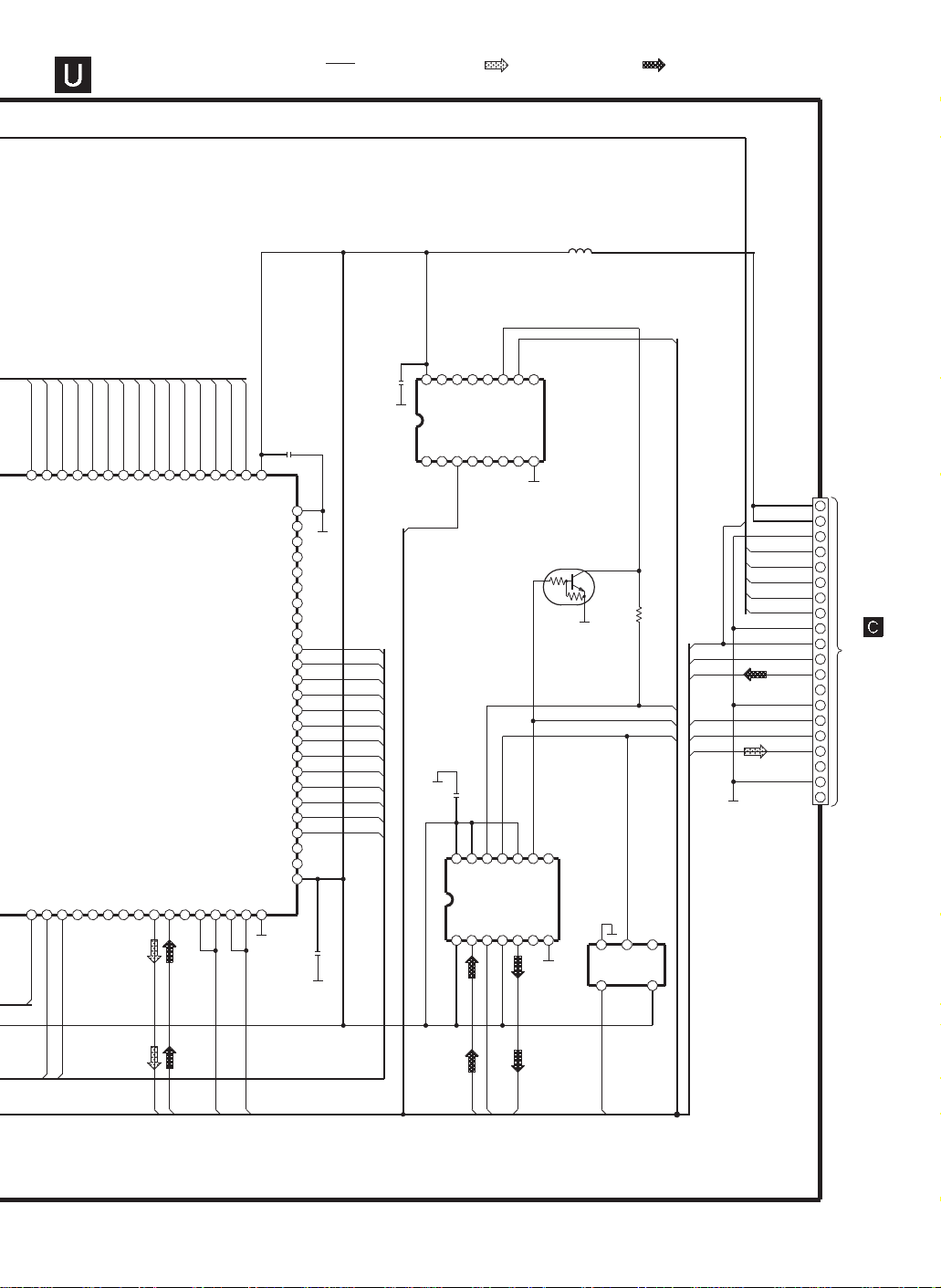

SCHEMATIC DIAGRAM - 2

X701

RSXB16M9J02T

C722

10P

R711

C717

120K

0.1

C716

1200P

CD SERVO CIRCUIT

C723

10V220

C724

0.1

R714

120

C721

10P

R712

C718

C744

0.022

R709

33K

0.47

470

R741

R742

220K

47K

: +B SIGNAL LINE

R721

100

C731

6.3V220

C730

0.1

25

27

61 62 63 64 65 66 67 68 69 70 71 72 73 74 75 76 77 78

BYTCK

/CLDCK

60

VDD

59

X2 OUT

58

X1 IN

57

VSS

56

SBCK

55

SUBC

54

VCOF2

53

PCK

52

EFM

51

AVSS2

50

AVDD2

49

VCOF

48

PLLF

DSLF

47

46

DRF

45

IREF

44

ARF

43

WVEL

42

DSLF2

41

PLLF2

LDON

BDO

40

39 38 37 36 35 34 33 32 31 30 29 28 27 26 25 24 23 22 21

CRC

CLVS

FCLK

FLAG

IPFLAG

DEMPH

MN662790RSC

SERVO PROCESSOR/

DIGITAL SIGNAL PROCESSOR/

DIGITAL FILTER/

D/A CONVERTER

VDET

OFT

TRCRS

/RFDET

RESY

IOSEL

IC702

TBAL

FETERFENV

/TEST

FBAL

AVDD1

VREF

OUTL

FOD

: CD-DA SIGNAL LINE

R717

100

R718

100

46

PSEL

RSEL

OUTR

AVSS1

IOVDD

PC

ECM

ECS

TRD

KICK

C732

6.3V220

80

79

MSEL

BCLK

LRCK

SRDATA

DVDD1

DVSS1

MCLK

MDATA

SENSE

/FLOCK

/TLOCK

BLKCK

SQCK

SUBQ

DMUTE

SMCK

CSEL

TVD

STAT

/RST

TRV

SSEL

MLD

: CD SIGNAL LINE

20

21

C725

1000P

C726

1000P

C733

0.1

L701

RLBN102V-Y

4847

R716

10

L702-L704

RLBN102V-Y

1

2

3

4

5

TX

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

17

C745

1000P

L702

L703

L704

R713

100

1314

24

23

30

LCH OUT

29

1

49

RCH OUT

R753

10

RESET SW

A.GND

LDVDD

DIDATA

DILRCK

DISCK

+3.3V

BCLK

SRDATA

LRCK

D.GND

IPFLAG

+7.5V

EFM

P.GND

MCLK

MDATA

MLD

BLKCK

SQCK

SUBQ

SBCK

STAT

/RST

SUBC

VCOF

TX

28

27

26

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

CN702

TO

VCD CIRCUIT

(CN802) ON

SCHEMATIC

DIAGRAM-6

C753

470P

18

C743

0.1

444345

22

12

4

678

3

TJ702

S701

RESET

SW

2

5

15

16

2

4

3

GND

IC1004

7

INVERTER

6

5

IC1004

TC7W14FUTE1L

2

4

3

GND

INVERTER

IC1003

7

6

5

IC1003

TC7WU04FUT2L

R1021

R1020

0.1µ

C1008

10K

R1008

0.1µ

C1006

100P

C1021

4.7K

2.2K

1

VCC

8

1

VCC

8

0.1µ

C1011

HDI0

HINT

HCK

HDI0

EMPH

DILRCK

DIDATA

DISCK

HRDY

SBCK

100P

C1019

HSEL

SUBC

CLOCK

BLKCK

0.1µ

C1017

R1000

5.6K

100

R1001

X1000

RSXC27M0S02T

10P

C1000

96

NCNCNC

97

NC

NC

98

VSS

99

NC

100

PIO3

101

VDD3

102

103104

VSS

GCK

105

VCK

106

107

108

109

110

111

112

113

HINT

114

115

VSS

116

HCK

117

VDD3

118

HD-IN

119

VDD3

120

HSEL

121122

123

124

NC

125

NC

126127

NC

NC

128

CDSCK1

CDSCK0

MPEGHCK

10P

C1001

95

VCKPIO1

DA-EMP

DA-LRCK

DA-DATA

DA-BCK

HDO-OUT

HRDY

CDG-SCK

CDG-VFSY

CDG-SOS1

NC

VSS

1

2

93

94

PIO2

VDDMAX-OUT

CDG-SDATA

CD BCK

CD DATA

4

3

1

A+3.3V

92

RESERVED

CD LRCK

5

2

CVOUT

91

PIO0

CD C2PO

6

3

COUT

90

RESERVED

NCNCNC

7

89

RESERVED

4

YOUT

8

5

VGND

RESERVED

9

6

AVDD

7

VGND

XCK

868788

DAXCK

MD0

10

8

R.+5V

AGND

MD1

11

9

D.+3.3V

D.+3.3V

RESERVED

MD2

MD3

13

12

11

12

13

10

XCK

D.GND

D.GND

0.1µ

C1010

10K

R1006

838485

808182

VSS

VDD3

RESERVED

CLK SEL(3)

IC1000

MPEG VIDEO

AUDIO DECODER

MN89103M2

MD4

MD5

VSS

15

14

16

TO

VCD CIRCUIT

(CN801) ON

SCHEMATIC

16

14

15

HRDY

EMPH

DISCK

DILRCK

10K

R1010

10K

R1011

R1004 10K

79

77

78

CLK SEL(2)

CLK SEL(0)

CLK SEL(1)

MD6

VDD3

MD7

I/O VSS

19

17

20

18

DIAGRAM-6

20

17

19

18

HINT

VRST

SBCK

DIDATA

COUT

75

R1013

5.6K

R1007

73

75

74

76

VREF

AVDD

AGND

C-OUT

MD8

VDD3

MD9

MD10

23

21

24

22

21

HCK

72

VGAIN

MD11

25

22

HDIO

C1020

3.3K

R1012

0.1µ

C1016

9.1K

R1009

71

AGND

MD12

23

0.1µ

70

AVDD

24

CDSCK

CDDATA

69

Y-OUT

MD13

MD14

25

YOUT

68

AGND

MD15NCNC

26

27

IPFLG

CDLRCK

CVOUT

L1000

L1002

66

67

AVDD

CVOUT

3029282726

HSEL

R1005

31

SUBC

150P

C1014

75

65

NC

NC

NC

NC

VDDMAX-IN

RESET

RESERVED

MA0

MA1

MA2

VDD3

MA3

VSS

MA4

MA5

MA6

VDD3

MA7

VSS

MA8

MA9

MA10

RAS1

RAS0

VDD3

CAS

VSS

MWE

MCE

NC

NC

NC

NC

NC

32

302928

CLOCK

100P

C1013

R1014

64

63

62

6160

59

58

57

56

55

54

53

5251

50

4948

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

CN1000

BLKCK

C1018

C1015

75

330P

270P

L1000

L1002

RLQP1R8KT2-Y

0.1µ

C1012

C1009

RLQP2R7KT2-Y

0.1µ

VRST

MA0

MA1

MA2

MA3

MA4

MA5

MA6

MA7

MA8

MA9

MA10

R1003 100

RAS0

R1002 100

CAS

MWE

MCE

0.1µ

C1007

: CD-DA SIGNAL LINE : VCD VIDEO SIGNAL LINE : VCD AUDIO SIGNAL LINE

: +B SIGNAL LINE

MD3

MD4

MD5

MD6

MD7

MCE

MA10

MD00

MA9

MA8

MD02

MD03

MD08

C1002 0.1µ

VIDEO MODULE CIRCUIT

SCHEMATIC DIAGRAM - 3

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

D3

D4

D5

D6

D7

CE

A10

OE

A11

A9

A8

A13

A14

A17

NC

VCC

IC 1001

IC 1001

CDDATA

CDSCK

2M ROM

LH532KU1

GND

16

D2

15

D1

14

D0

13

A0

12

A1

11

A2

A3

9 10

A4

8

A5

7

A6

A7

5 6

A12

A15

A16

NC

1 2 3 4

IPFLG

CDLRCK

MD2

MD1

MD0

MA0

MA1

MA2

MA3

MA4

MA5

MA6

MA7

MD01

MD04

MD05

MD1

MD3

MD6

MD4

MD2

MD0

MD5

IC 1002

3

11512

4M DRAM

24

27

M44260CTP7

6

18

19

17

25

23

29

13

MD7

MA4

MA5

MA6

MA7

MA8

CAS

RAS0

MD00

MD01

MD02

MD03

MD04

MD05

MD06

MD07

MD00

MD01

MD02

C1005

MD03

0.1µ

MD04

MD05

MD06

23

24

25

26

27

28

29

30

31

32

35

36

37

38

39

40

41

42

43

44

MD07

A4

A5

A6

A7

A8

VSS

OE

NC

DQ9

VSS

VSS

/UCAS

/LCAS

IC 1002

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

VCC

A3

A2

A1

A0

NC

/RAS

/WE

NC

NC

D8Q

DQ7

DQ6

DQ5

VCC

DQ4

DQ3

DQ2

DQ1

VCC

0.1µ

C1004

22

21

20

19

18

17

16

15

14

13

9 10

8

7

5 6

1 2 3 4

22

0.1µ

C1003

MA3

MA2

MA1

MA0

RAS

MWE

MD7

MD6

MD5

MD4

MD3

MD2

MD1

MD0

1

9

2

10

26

28

21

16

15

20

8

47

14

SCHEMATIC DIAGRAM - 4

MP3 MODULE CIRCUIT

: +B SIGNAL LINE

RST

P4P5P6

P7

42

44

43

P3 /PWE

P2 /STOP

P1 ACK

P0 DSPRST

R1005

4.7K

A5A6A7

44

43

42

A5

A6

LED4

1

LED3

2

LED2

3

LED1

4

LED0

AN0

5

6

AN1

7

AN2

8

AN3

AN4

9

10

AN5

11

AN6

12

C1006

0.1

/DR

40

41

39

A7

/OE

/BLE

/BHE

I/O16

LED7

LED6

LED5

MN101C427MA2

MP3 MICROPROCESSOR

OSC1

OSC2

VDD

AN7

14

13

BCLK

OSCF0

D15

D14

D13

D12

3435

363738

I/O15

I/O13

I/O14

401541

MMOD

IC1001

VSS

173916

C1007

0.1

33

VSS

VCC

0.022

C1011

ERROR

38

36

37

P27

P70

P67

P66

P00

P01

P02

NC

20

19

18

HDOUT

HDIN

HCLK

C3BBHG000048

D9

D11

D10

313029

32

I/O11

I/O10

I/O12

PIBE

/PCS

/PRE

34

35

P65

P64

P63

P62

P61

P60

P22

P21

P20

P14

P13

P12

P11

P06

P10

22

21

IC1002

64K x 16 SRAM

D8

28 272625

NC

IC1002

I/O3

I/O4

A2

A3

A4

1

2

I/O1

/CE

A1

A0

76543

I/O2

VCC

98

11

10

I/O7

I/O8 /IO9

I/O5

VSS

12

13

/WE

I/O6

14

15

16

17

A8

A15

HCS

33

32

31

30

POBF

29

28

NEXT

27

26

25

24

23

C1001

0.1

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14

C1012

A8

A9

A10

A11

24

23

A9

NC

A11

A10

NC

A12

A13

A14

1918

22

20

21

/STOP

DSPRST

OSCF0

0.022

C1002

R1001

680

C1000

0.47

0.1

R1000

10K

1009998 979695

1

VDD

AMD4

2

AMD5

3

4

AMD6

AMD7

5

AMD8

6

7

AMD9

AMD10

8

AMD11

9

10

AMD12

11

AMD13

12

AMD14

13

AMD15

PLLSLEEP

14

15

VSS

16

/STOP

/RST

17

18

VDD

19

AVDD

VCOIN

20

21

PCOUT

AVSS

22

23

VSS

OSCF0

24

OSCS0

25

A3A2A1

VSS

VDD

2726

AMD3

GI0

28

AMD2

GI1

29

A0

AMD1

GI2

30

/CS

AMD0

GI3

31

/DW

94

/CS

MODE0

32

/DR

93

/DW

MODE1

33

D15

92

/DR

MODE2

34

DMD15

MODE3

A4A3A2

A1

R1006

4.7K

C1003

0.1

D0D1D2

A0

/CS

D3

D4D5D6

D7

A15

A14

A13

A12

C1008

0.1

R1004

4.7K

/DW

ACK

R1008

4.7K

LRCK

R1050

10

SCHEMATIC DIAGRAM - 5

MP3 MODULE CIRCUIT

D14

91 90

DMD14

GO0

35

A15

D13

36

D9D8D7D6D5D4D3D2D1

D12

D11

D10

DMD10

GO4

40

DMD9

DMD8

IC1000

SRDY1

SRDY0

41

42

8384

DMD7

TXD0

43

878685

89 88

DMD11

DMD12

DMD13

MN1933222MD1

MP3 DIGITAL SIGNAL PROCESSOR

GO3

GO2

GO1

38

39

37

82

81

DMD5

DMD4

DMD6

RXD1

RXD0

TXD1

444546 47

80

DMD3

SCLK0

7879

DMD2

SCLK1

48

D0

77

DMD1

/SINH0

49

76

DMD0

/SINH1

50

VDD

VSS

C1005

VSS

P15

P14

P13

P12

P11

P10

POBF

PIBE

/PRE

/PWE

/PCS

TCLK

TOUT

VDD

: +B SIGNAL LINE

14

16

VCC

15

Q11

C1009

0.1

IC1003

0.1

75

74

73

72

71

70

69

68

P9

67

P8

66

P7

65

P6

64

P5

63

P4

62

P3

61

P2

P1

60

59

P0

58

57

56

55

54

53

52

51

P7

P6

P5

P4

P3

P2

P1

P0

POBF

PIBE

/PRE

/PWE

/PCS

1

SINH

Q6

Q12

UN5211TX

TURN ON

IC1003 RESET

C1010

14

VCC

: MP3 SIGNAL LINE

12

13

11

10

9

Q1

Q9

Q8

Q10

RESET

CLOCK

Q3

GND

Q2

Q4

Q7

Q5

432

C0JBAK000133

RIPPLE-CARRY BINARY

Q1000

0.1

13

2CLR

IC1003

COUNTER

11

12

2D

2CK

8

765

9

10

2Q

2PR

VLP0157-T

8

/2Q

L1001

Q1000

: CD-DA SIGNAL LINE

BCLK

R1002

4.7K

BCLK

LRCK

SRDATA

LRCK

BCLK

IBCLK

LRCK_1D

TXD1

LRCK_1D

BCLK

HCS

HDIN

HDOUT

HCLK

RST

D+3.3V

D+3.3V

DGND

HCS

HDIN

HDOUT

HCLK

RST

DGND

CDSCK

CDLRCK

CDDATA

IPFLG

DGND

DISCK

DILRCK

DIDATA

FCLK

DGND

OSCF0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

CN1000

TO

VCD CIRCUIT

(CN800) ON

SCHEMATIC

DIAGRAM-6

IC1004

C1004

0.1

1CLR

1D

1CK

GND

/1Q

1PR

1Q

76

4321

5

3 2 1

IC1005

OUT Y

4

VCC

NCIN AGND

5

ERROR

NEXT

TXD1

RXD0

BCLK

SINH

SRDATA

BCLK

RXD0

IC1004

C0BAF000184

DUAL D FLIP FLOP

IBCLK

IC1005

C0BAB000007

INVERTER

CN803

CD5V2

30

DGND

2928272625242322212019181716151413121110

POSITION

BOTTOMSW

CLAMP

OPEN

CHG_SW2

CHG_SW1

MM_CS

MM_IO

MM_CLK

MM_REQ

MM_RST

PGND

CD7.5V

VGND

CVOUT

NCD

TO

MAIN CIRCUIT (CN305)

SW5V

ON SCHEMATIC DIAGRAM-9

CHG_CW

VMODE

VMUTE

CD3.3V

CDL

A.GND

2 4 6 8 9753

CDR

1

47K

R848

CHG_CCW

CHG_PLGR

CHG_HALF

Q804

: VCD VIDEO SIGNAL LINE

22K

R843

SW5V

: CD SIGNAL LINE

: CD-DA SIGNAL LINE

: MP3 SIGNAL LINE : VCD AUDIO SIGNAL LINE

: +B SIGNAL LINE

SCHEMATIC DIAGRAM - 6

MRST

L800

RLL500050T-Y

MHCLK

MHCS

MHDIN

L800

C801

C800

IC800

VCD CIRCUIT

TC74HC4050EL

HEX NON-INVERTING BUFFER/

LEVEL SHIFTER (GATE BUFFER)

D+3.3V

2

1

+3.3V

D801

D800

100

R824

16

NC

VDD

100

1

R818

100

R817

100

R816

1000P

6.3V100

D+3.3V

DGND

3

0.01

0.01

C851

10K

R845

Q802

MM_IO

15

6Y

IY

2

MHCS

HCS

5

4

EEDA

OPEN

CLAMP

CSQCK

CSUBQ

C850

R835

C807

MHDIN

R800

HDIN

6

330P

C822

CHG_SW1

CHG_SW2

BOTTOMSW

POSITION

D800-D801

1SS355TE17

4.7K

R844

47K

14

6A

IA

3

0.1

MHCLK

10K

HDOUT

HCLK

7

8

13

NC

2Y

4

MRST

RST

47K

R890

R839

12

5Y

IC800

2A

5

DGND

9

10

47K

R882

1K

MM_CLK

11

5A

3Y

6

CDLRCK

CDSCK

CDLRCK

11

4.7K

4.7K

R884

R883

Q803

10P

10

4Y

3A

7

CDDATA

CDDATA

12

13

4.7K

R885

10P

C818

100P

C817

R847

MP3RST

9

8

IPFLG

R801 100

IPFLG

DGND

14

4.7K

4.7K

R886

R887

C819 10P

4.7K

C814

MP3DIN

4A

VSS

MP3SCK

R802 100

DISCK

16

15

EECLK

100

100

100

100

100

100

MM_CS

SW5V

MP3HCS

10K

R819

MP3DATA

MP3LRCK

100

R803

DILRCK

DIDATA

FCLK

18

17

22K

R892

EECS

SW5V

MM_REQ

MP3CLK

MP3DOT

R794

DGND

19

22K

R889

0.022

C823

47K

47K

R880

R772

R771

R879

R878

R877

R875

R873

1K

100

100

1K

R859

SWITCH

Q802-Q804

2SC2712GRT5T

R840

CBLKCK

MM_RST

Q800

KRC101STA

Q800

82P

C830

1K

R795

1.8K

OSCFO

20

CN800

47K

47K

R797

R865

R863 4.7K

R861 4.7K

R860

R856

1K

SWITCH

1

3 2

4

5

6

7

8

9

10

11

12

16 15 14 13

S-REQ

47K

CVOUT

1

R774

R773

64

NC

OPEN

NC

NC

SOUT

SUBQ

S-CS

S-CLK

BLKCK

17

R779

L801

A+3.3V

CDRST

63

CHG_SW1

CDRST

CHG_SW2

CLAMP

POSITION

CSQCK

SDATA_O

SDATA_I

CNVSS

18

0

C815

L801-L802

CVOUT

2

Q805-Q808

33P

33P

C824

C825

CRESTSW

61

60

62

NC

DACSEL

CRESTSW

BOTTOMSW

RST

20

21

19

47K

47K

R769

IN

0.01

X800

OUT

RSXY6M00D01T

3

4

GND

6

5

1K

R820

0

R766

BCLK

RLL500050T-Y

L802

1000P

C805

6.3V100

C802

C804

COUT

YOUT

VGND

3

5

6

4

SWITCH

KRC101STA

22K

R893

0.1

CMCLK

CMDATA

58

57

59

56

VCC

AVSS

VREF

CMCLK

IC802

MICROPROCESSOR

C2BBGF000281

CDPCNT

VSS

XOUT

XINNCNC

22

23

25

24

R770

1K

R855

GND

2

1

VDD

8

7

0

47

R762

R821

R767

C810

0.47

C809

C808

6.3V100

220

R804

C806

6.3V100

C803

1000P

1000P

D.+3.3V

D.+3.3V

VGND

R.+5V

8

7

9

10

10K

R787

10K

R785

10K

R899

10V220

CMLD

54

CMLD

CHG_PLGR

27

100

R851

CBLKCK

CCDSTAT

52

53

MP3DIN

CCDSTAT

CHG_CW

29

28

100

R853 100

R852

R799

100

R854

R777

1K

51

MP3DOT

30

47K

R833

10K

R841

0

Q805

CSUBQ

0

50

MP3CLK

SEL(H : PM141/L :111)NCCHG_CCW

31

10K

R782

C827

C826

55

CMDATA

CHG_HALF

26

IC801

IC803

INVERTER

0

R778

TC7W14FTE12L

0

R760

0

0.1

1K

1K

1K

R807

R805

R806

XCK

DILRCK

D.GND

11

HRDY

EMPH

14

12

13

15

D.GND

Q807

Q806

CCDSTAT

R793

47K

R891

10K

49

MP3HCS

NC

32

TC74HC157AFT

16

48

MP3RST

MP3ERR

47

HSEL

46

HDO

45

HDI

44

HCLK

VRST

42 43

HINT

41

HRDY

40

EMPHA

39

VMODE

38

VMUTE

NC

36 37

EEDA

35

EECLK

34

EECS

33

47K

R768

1K

R837

10K

R834

0.1

C812

MULTIPLEXOR/

QUAD 2 CHANNEL

15

16

G

VCC

L:A/H:B

IA

3

2

1

1K

1K1K1K

R811

R808

R809

R810

HINT

DIDATA

SBCK

DISCK

20

18

17

19

14

4A

IB

1K

R812

VRST

R868

21

Q801

R827

13

4B

IY

4

R825

1K

R813

HCK

22

47K

R765

R831

1.8K

100

R814 1K

HDIO

Q808

470P

C828

CRESTSW

100K

R888

10K

R776

L803

SWITCH (PCONT)

KRC102STA

Q801

1.5K

R828

11

10

12

3B

3A

4Y

IC801

2A

2Y

2B

7

6

5

R826

0

R763

CDLRCK

CDDATA

CDSCK

IPFLG

24

26

23

25

10K

10K

10K

R894 4.7K

R895 4.7K

CDRST

CSQCK

MP3DIN

MP3DOT

MP3CLK

MP3HCS

DACSEL

SW5V

MP3RST

HSEL

HDIO

HCLK

VRST

HINT

HRDY

EMPHA

VMODE

VMUTE

EEDA

EECLK

EECS

68

RLL500050T-Y

CHG_CCW

CHG_CW

CDR

CHG_PLGR

CHG_HALF

CDL

MP3DATA

1.8K

9

3Y

C811

GND

8

1.8K

1.8K

100

0

1K

R815

SUBC

HSEL

CLOCK

27

28

29

30

CMLD

1K

2.2K

1K

1K

1K

1K

CD7.5V

100

1K

CDDATA

R846

100

100

100

0.1

R830

R829

0.1

BLKCK

CN801

R791

R790 10K

R789

R881

4.7K

4.7K

R897

R896

CMDATA

C816

MP3SCK

1K

100

R822

R823

R761

4.7K

R898

CMCLK

R788

C821

1000P

R876

R874

R872

R871 1K

R870

R869

R867 1K

R866

R864 1K

R862 1K

C820

R858

R857

R850 100

100

R849

L803

R842

R838

R836

C813

6.3V100

MP3LRCK

10K

10K

10K

10K

10K

C829

220

10V100

NCD

SBCK

DIDATA

DACSEL

DILRCK

DISCK

BLKCK

SUBQ

STAT

RESTSW

/RST

SQCK

MLD

MDATA

MCLK

R786

R784

R783

R781

R780

50V0.47

DGND

CN802

VCOF

RESET SW

24689 7 5 3 1

SUBC

/RST

STAT

SBCK

SUBQ

SQCK

BLKCK

MLD

MDATA

MCLK

P.GND

EFM

+7.5V

IPFLAG

CLOCK

TX

D.GND

LRCK

SRDATA

BCLK

+3.3V

DISCK

DILRCK

DIDATA

+3.3V

RCH OUT

A. GND

LCH OUT

30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10

TO

CD SERVO CIRCUIT (CN702)

ON SCHEMATIC DIAGRAM-2

TO

MP3

MODULE

CIRCUIT

(CN1000) ON

SCHEMATIC

DIAGRAM-5

TO

VIDEO

MODULE

CIRCUIT

(CN1000) ON

SCHEMATIC

DIAGRAM-3

Loading...

Loading...