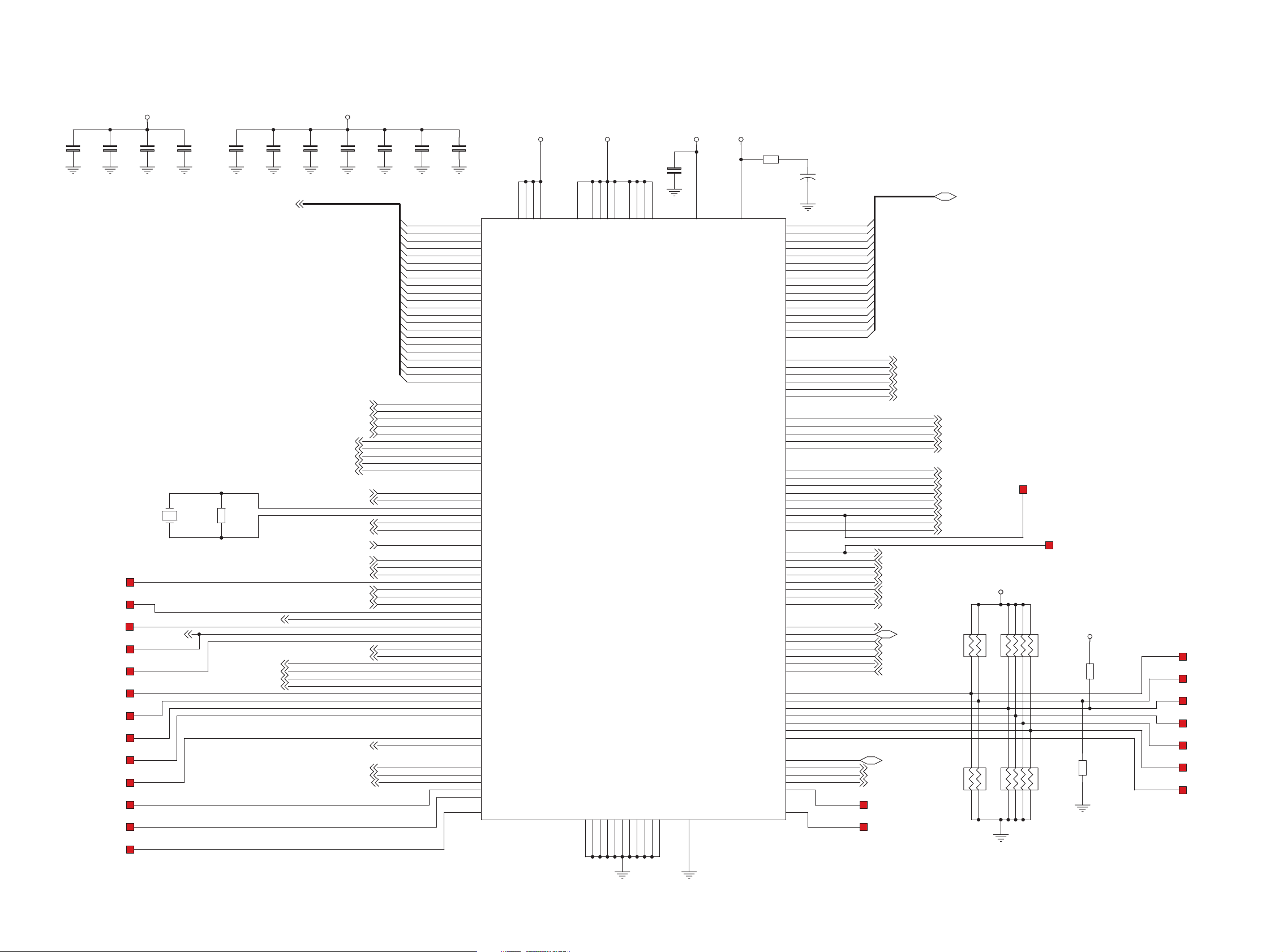

Page 1

– 3-1 –

D[0..15]

ADD[0..21]

ADD1

ADD10

ADD15

ADD4

ADD20

D1

D3

D14

D15

ADD6

D13

ADD3

D2

D8

D11

ADD2

ADD13

ADD5

ADD11

USC3

USC6

D10

ADD17

ADD16

ADD7

ADD21

ADD9

USC1

USC2

ADD12

ADD14

ADD19

USC0

D0

D4

D7

ADD8

D5

D6

ADD0

ADD18

D9

D12

USC5

USC4

NRESET_LCD[7]

YMU_AVCC_ON[5]

AUDIO_ON[6]

BACKLIGHT[7]

VIBRATOR_ON[7]

YMU_IRQ[5]

HANDFREE_IN[6]

PT T

CHARGER_DET[3]

CHARGER_EN[3]

NRESET[3,4,5]

SYS_POWERON[3]

KEYROW_0[7]

KEYROW_2[7]

KEYROW_3[7]

KEYROW_4[3]

KEYROW_1[7]

KEYCOL_0[7]

KEYCOL_1[7]

KEYCOL_2[7]

KEYCOL_3[7]

KEYCOL_4[7]

BBCLK[3]

RD [4]

HWR [4]

LWR [4]

WE [4,7]

ROMCS [4]

RAMCS [4]

TRSW1 [9]

TRSW2 [9]

LE [8]

TRSW3 [9]

DCSEN [8]

RFEN [9]

GSMEN [8,9]

SXEN [8]

DATA [8]

BSDI [2]

BSIFS [2]

ASDI [2]

CLKOUT_GATE [2]

BSDO [2]

VSDO [2]

ASDO [2]

ASFS [2]

ARSM [2]

AT SM [2]

CLK_OUT [2,5]

VBC_RESET [2]

VSFS [2]

VSDI [2]

ADD[0..21][4,7]

YMU_SYNC[5]

LCDCTL[7]

YMU_SCLK[5]

LCDCS[7]

POWER_ON[3]

CHARGER_GATEIN[3]

CLKON[3]

YMU_SDIN[5]

CLK [8]

END_OF_CHARGE[3]

SIM_ON [3]

SIM_CLK [4]

SIM_RESET [4]

RXEN1 [8]

TXEN [2,8,9]

RXEN [2]

PA_EN [9]

HPOUT_ON[6]

VRTCVMEM VCORE

VCORE VMEM

VMEM

VMEM

VCORE

C103

0.1U

C102

0.1U

C101

0.1U

C107

0.1U

C108

0.1U

C109

0.1U

C110

0.1U

C105

0.1U

X101

MC-146

+

BAT101

ML414R-F9A

C111

0.1U

R107

TBD

1 2

3 4

R103

TBD

1 2

3 4

R108

TBD

123

4 5

678

R104

TBD

123

4 5

678

TP124

RXEN

U101

AD6522

H4

J3

J2

J4

K3

K2

K4

L4

L1

L3

L5

M1

M2

N1

P1

N2

P2

N3

M3

P4

N4

M4

P5

A6

F4

D4

B5

A5

C4

E4

B4

A4

C3

L12

G14

B3

A3

B2

N14

C14

D12

A14

A13

E11

C12

B13

D11

D10

B12

C11

D9

B11

A11

C10

D8

A10

C9

C7

B9

A9

B8

A8

D6

B7

H14

H13

J12

J11

K11

N6

P6

M6

N7

M7

L7

P8

N8

M8

P9

M9

P10

N10

M10

P11

N11

M11

N12

P13

P14

M13

M14

M12

L13

G13

H12

F14

F13

H11

F12

E14

E13

G11

E12

D14

D13

F11

B1

C2

G12

D1

D2

E1

A1

C1

E2

F1

F2

F3

G4

G2

G1

G3

H3

H2

M5

J13

K12

L10

K13

J14

A7

C5

L14

J1K1P3L6L8

P12

L11

C1 3

A12D7B6

D3

H1P7K14

C8

L9L2N5N9N1 3

B14

B10C6D5

E3

A2

ADD0

ADD1

ADD2

ADD3

ADD4

ADD5

ADD6

ADD7

ADD8

ADD9

ADD10

ADD11

ADD12

ADD13

ADD14

ADD15

ADD16

ADD17

ADD18

ADD19

ADD20

ADD21

nDISPLAYCS (ADD22)

KEYPADROW0

KEYPADROW1

KEYPADROW2

KEYPADROW3

KEYPADROW4

KEYPADCOL0

KEYPADCOL1

KEYPADCOL2

KEYPADCOL3

KEYPADCOL4

CLKIN

CLKON

OSCOUT

OSCIN

PWRON

RESET

USC0

USC1

USC2

USC3

USC4

USC5

USC6

GPIO_0

GPIO_1

GPIO_2

GPIO_3

GPIO_4

GPIO_5

GPIO_6

GPIO_7

GPIO_8

GPIO_9

GPIO_10

GPIO_11

GPIO_12

GPIO_13

GPIO_14

GPIO_15

GPIO_16

GPIO_17

GPIO_18

GPIO_19

GPIO_20

GPIO_21

JTAGEN

DATA0

DATA1

DATA2

DATA3

DATA4

DATA5

DATA6

DATA7

DATA8

DATA9

DATA10

DATA11

DATA12

DATA13

DATA14

DATA15

RD

HWR

LWR

WE

ROMCS

RAMCS

GPCS0

GPCS1

TXPA (GPO_2)

PA_NEGBIAS (GPO_4)

TXPHASE (GPO_7)

DCS_SW_SYNC (GPO_8)

DCS_SW_DRV (GPO_9)

SM_SW_SYNC (GPO_10)

GSM_SW_DRV (GPO_11)

TX_GSM (GPO_16)

ADD23(TX_DCS)GPO_17

(OTH_EN)GPO_18

(OTH_VLO_EN)GPO_19

(OTH_DATA)GPO_20

(OTH_CLK)GPO_21

(RXON)GPO_0

(TXON)GPO_1

GPO_3

CLKOUT

CLKOUT_GATE

(VBCRESET)GPO_24

(ARSM)GPO_5

(ATSM)GPO_6

ASDI

ASDO

ASFS

BSDO

BSOFS

BSDI

BSIFS

VSDI

VSDO

VSFS

LCDCTL (nDISPLAYCS)

SIMDATAOP

SIMCLK

SIMRESET (GPIO_23)

SIMSUPPLY (GPIO_24)

SIMVPROG (GPIO_22)

BACKLIGHT0 (GPO_22)

BACKLIGHT1 (GPO_23)

GPIO_32(WAIT)

GND1

GND2

GND3

GND4

GND5

GND6

GND7

GND8

GND9

GND1 0

GND1 1

VSSRTC

VCC1

VCC2

VCC3

VCC4

VSIM

VMEM1

VMEM2

VMEM3

VMEM4

VEXT1

VEXT2

VEXT3

VEXT4

VPEG1

VDDRTC

R101 33K

TP106

TP_USC0

TP110

TP_USC2

TP101

TP_CLKOUT

TP108

TP_USC1

TP116

TP_USC5

TP112

TP_USC3

TP103

TP_GPIO7

TP114

TP_USC4

TP118

TP_USC6

TP102

TP_GPIO3

R102

10M

TP107

TP_GPIO11

TP113

TP_GPIO20

TP111

TP_GPIO19

TP115

TP_GPIO21

TP109

TP_GPIO18

T117

TP_GPO23

C106

0.1U

C104

0.1U

C112

0.1U

T123

TP_GPIO32

TP105

TP_GPIO9

TP120

TP_GPIO22

1

TP122

TP_JTAGEN

1

TP104

TP_GPIO9

TP119

TP_GPCS1

TP121

TP_GPCS0

R105

100K

R106

100K

BSOFS

D[0..15] [4,7]

SIM_IO [4]

3. CIRCUIT DIAGRAMS

3.1. Circuit Diagram-1

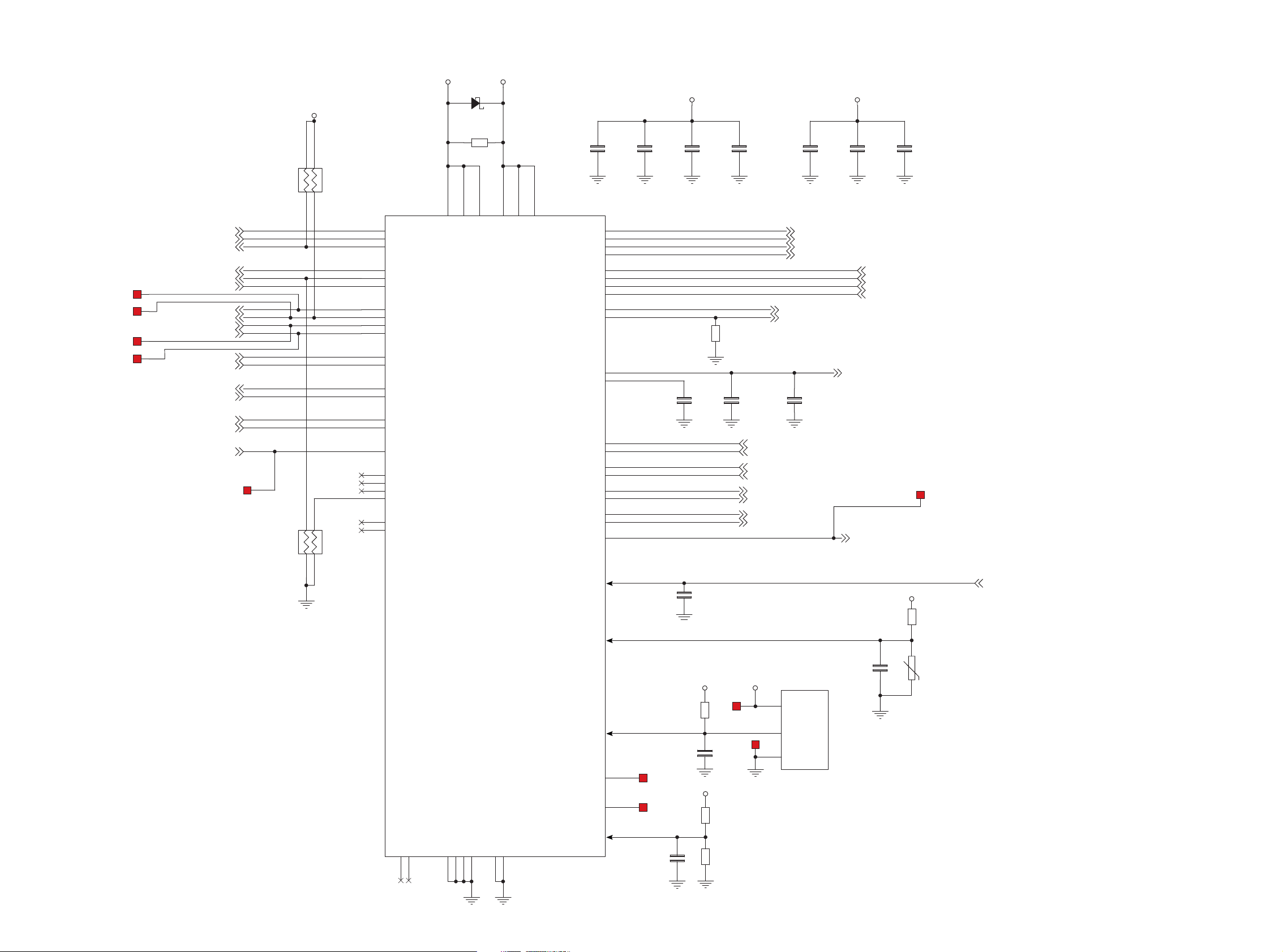

Page 2

– 3-2 –

PCB_ID

TXIP [8]

TXIN [8]

TXQN [8]

TXQP [8]

RXIP [8]

RXIN [8]

RXQP [8]

RXQN [8]

VOUTNORP [5]

VOUTNORN [5]

VOUTAUXP [5]

VOUTAUXN [5]

VSDI[1]

ASDI[1]

VSFS[1]

ASDO[1]

ASFS[1]

VSDO[1]

BSDO[1]

ATSM[1]

ARSM[1]

CLK_OUT[1,5]

VBC_RESET[1]

CLKOUT_GATE[1]

AFC [3]

RAMP [9]

VREFOUT

VINNORP [6]

VINAUXP [6]

VINAUXN [6]

VINNORN [6]

BAT_TEMP

BSDI[1]

BSIFS[1]

BSOFS

BUZZER [6,7]

TXEN[1,8,9]

RXEN[1]

BAT_VIOLTAGE

[3]

VANA VCORE

VMEM

VCORE

VANA

VANA

VANA

VANA

C214

0.1U

R201

100K

1 2

3 4

TP205

BSDI

R210

100K/1%

R207

100K

1 2

3 4

TP208

BSOFS

C217 TBD

R212 TBD R211 TBD

C201

2.2U

TP206

BSDO

R206

100K

C202

0.1U

R211

TBD

NTC

R209

100K

C216

0.1U

C207

0.1U

U201

AD6521

F9

E9

C9

D9

E10

D10

C10

B10

A10

H9

A7

A8

A6

B5

A4

H10

G10

J10

K10

J6

K8

K7

K9

K6

H1

H2

J1

D2

D1

E1

E2

F1

F2

G2

K1

K2

J2

K3

J3

K4

J4

B4

A3

B2

B1

C2

C1

F10A9J8

A1G1K5

G9

B8

J7

B3

A2

J5

J9

B9

B6

B7

ITXP

ITXN

QTXN

QTXP

IRXP

IRXN

QRXP

QRXN

AFCDAC

RAMPDAC

REFOUT

REFCAP

AUXADC1

A5

AUXADC2

AUXADC3

AUXADC4

VINAUXP

VINAUXN

VINNORP

VINNORN

BUZZER

VOUTNORP

VOUTNORN

VOUTAUXP

VOUTAUXN

ASDI

ASFS

ASDO

VSFS

VSDO

VSDI

BSOFS

BSDO

BSIFS

BSDI

RESET

MCLKEN

MCLK

ATSM

ARSM

TXON

RXON

IDACOUT

IDACREF

TDI

TDO

TMS

TCK

AVDD1

AVDD2

AVDD3

DVDD1

DVDD2

DVDD3

AGND1

AGND2

AGND3

AGND4

DGND1

DGND3

NC(MICCAP)

NC(REFCAP20)

AUXADC5

AUXADC6

C213

0.1U

C212

0.1U

C204

0.1U

C203

0.1U

R213

100K

D201

TBD

C218

2.2U

R208

200K/1%

TP201

TP_VBCRST

C205

0.1U

C206

0.1U

TP202

TP_BUZZER

TP203

ADC5

TP204

ADC6

C215

0.1U

TP207

BSIFS

VBAT

TP302

TP_GND

TP301

TP_VBAT

CON301

BAT_CON

1

2

3

VBAT

BAT_TEMP

GND

3.2. Circuit Diagram-2

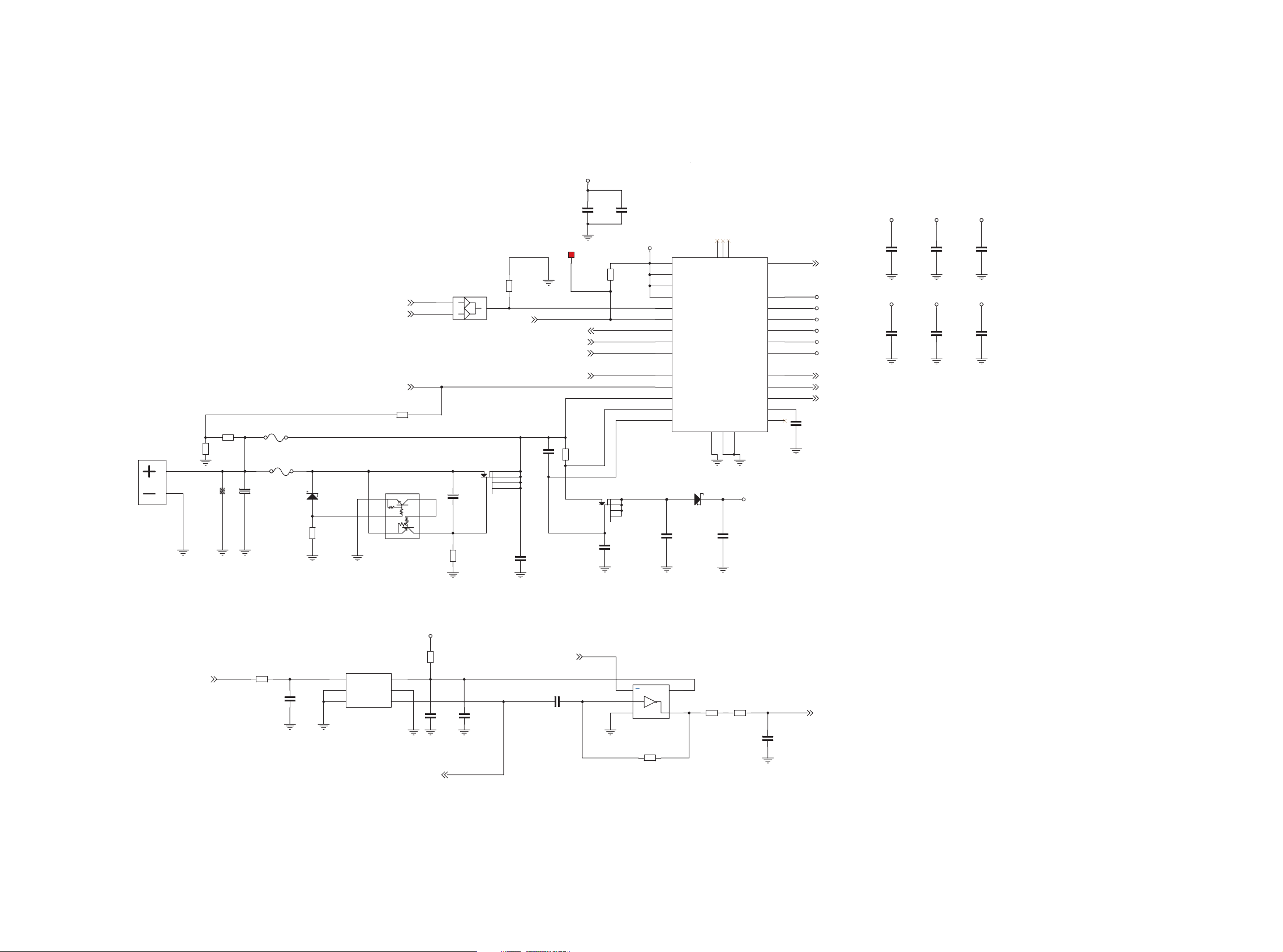

Page 3

– 3-3 –

TO RF BLOCK

22K

22K

POWERON_IN

AFC[2]

13 MH z[8]

BBCLK [1]

CLKON[1]

POWER_KEY[7]

POWER_ON[1]

CHARGER_EN[1]

KEYROW_4[1]

SYS_POWERON[1]

END_OF_CHARGE [1]

CHARGER_GATEIN[1]

CLKON[1]

BAT_VOLTAGGE [2]

NRESET [1,4,5]

SIM_ON[1]

CHARGER_DET [1]

VTCXO

VANA

SIMVCC

VANA

VCORE

VRTC VCORE

VRTC

VMEM SIMVCC

VTCXO

VTCXO

VBAT

VMEM

VBAT

VBAT

TP303

POWERON_KEY

C301

4.7U

C311 0.1U

R307 1M

C304

4.7U

R311

TBD

C305

4.7U

U301

ADP3408

29

30

31

1

2 3

4

5

6

7

8

9

10

12

1314

15

16

18

19

20

21

22

23

25

26

272811

172432

PWRONIN

PWRONKEY

ROWX

SIMEN

VRTCIN VRTC

BATSNS

MVBAT

CHRDET

CHRIN

GATEIN

GATEDIR

DGND

ISENSE

EOCCHGEN

RESCAP

RESET

VSIM

VBAT2

VMEM

VCORE

VBAT

VANA

VTCXO

REFOUT

AGND

TCXOEN

DGND

NCNCNC

C306

4.7U

R301

100K/0402R

C307

2.2U

U310

RB491D

1 2

R312

TBD

R313 TBD

R303

0.3

U306

BLM55C9V1 - B

1 2

C308

1U

R308 0R

F302 FULSE

C312

10N

C310

2.2U/25V

CON302

P_JACK

1

2

1

2

C321

0.1U

T301

1 2

C309

10N

R306 100R

C318

TBD

R309

10K - B

U302

DAN222

3

1

2

R302

100K

C319

0.01U - B

U305 NC7SZU00P5X

1

2

3 4

5

D

A

GND

Y

VCC

C322

0.1U

U304

TG-2820CB

1

2

3 4

5

6

AFC

GND

GND OUT

GND

VCC

U307

FDC640P - B

3

4 1

2

5

6

R304

0

C323

0.1U

C316

1U

C317 10N

C303

0.1U

R305 27K

C313 10N

R310

10K - B

C302

0.1U

U309

SI3443DV

3

4 1

2

5

6

U308

EMD2 - B

34

5

61

2

C314 10P

F301 TBD

3.3. Circuit Diagram-3

Page 4

– 3-4 –

D8

D6

D5

D2

D1

D12

D9

D7

D0

D4

D3

D11

D10

D14

D13

D15

ADD19

ADD3

ADD21

ADD10

ADD1

ADD18

ADD4

ADD14

ADD2

ADD16

ADD12

ADD20

ADD13

ADD11

ADD5

ADD15

ADD9

ADD6

ADD7

ADD17

ADD8

D[0..15]

ADD[0..21]

CE2s

WP-ACC

CIOs

CIOf

ADD[0..21] [1,7]

RD[1]

HWR[1]

LWR[1]

WE[1,7]

ROMCS[1]

RAMCS[1]

NRESET[1,3,5]

SIM_CLK[1]

SIM_RESET[1]

VMEM

VMEM

SIMVCC

C404

33pF

C401

0.1U

U401

MC-222243AF9-B85XBT3(FBGA)

C1

F1

G1

B10

E9

F10

D9

G10

F8

L10

E8

M10

D8

C8

F7

E7

C7

C3

D3

E3

F3

D2

E2

F2

G2

C6

D6

H2

D4

J3

K3

G4

J2

C4

K4

D5

H5

D7

H4

F9

E4

F4

C5

H3

G9

H6

E5

J4

K7

K6

G8

H9

E6

G7

J5

A1

J8

J6

B1

K5

G3

J7

H7

K8

H8

L1

M1

B5

L5

B6

A10

L6

J9

MB2

MB3

MB4

MB12

NC0

MB13

A15

MB14

A14

MB15

A13

MB16

A12

A11

A10

A9

A8

A7

A6

A5

A4

A3

A2

A1

A0

WE

CE2s

CEf

UB

DQ0

DQ8

DQ1

CE1s

LB

DQ2

RESET

DQ3

A19

DQ9

NC1

A18

A17

WP/ACC

OE

A16

DQ4

RY/BY

DQ10

DQ5

CIOs

SA

CIOf

A20

DQ6

VCCf

MB0

DQ7

VCCs

MB1

DQ11

VSS

DQ12

DQ13

DQ14

DQ15/A-1

MB5

MB6

MB7

MB8

MB9

MB11

MB10

VSS

R404

150R/1%

R401

100K

123

4 5

678

R403

10K

R405

100K

TP404

TP_SIMIO

TP401

TP_SIMVCC

TP403

TP_SIMCLK

TP402

TP_SIMRST

J401

SIM SOCKET

6

4

21

3

5

GND

VPP

I/OCLK

RST

VCC

C403

0.1U

C402

TBD

D[0..15][1,7]

SIM_IO [1]

3.4. Circuit Diagram-4

Page 5

– 3-5 –

YMU_SCLK[1]

YMU_SDIN[1]

YMU_SYNC[1]

VOUTNORN[2]

VOUTNORP[2]

CLK_OUT[1,2]

NRESET[1,3,4]

YMU_IRQ[1]

HPOUT [6]

VOICEOUT [6]

BUZZER [2,6]

VOUTAUXN[2]

YMU_AVCC_ON[1]

VOUTA U XP[2]

VM EM

YMU_AVCC

VBAT

YMU_AVCC

R522

0R

C527

TBD

C511 TBD

LS501

SPEAKER

C516

33P

T501

1 2

C515

33P

T502

1 2

R521 100K

C522

TBD

LS502

RECEIVER - B

T503 - B

1 2

T504 - B

1 2

C521 0.1U

C513

0.1U

C512

0.1U

R514 20K

TP501

TP_SPK-P

C520

TBD

C519

0.1U

R504

0R

R503

0R

C525

2.2U

C526

4.7U

C523

33P

U505

SC1563ISK-3.0

1

2

34

5

N

I

CG

O

C524

33P

R510

TBD

U504

YMU757B

1

2

3

4

5

6

7

8

9

10

15

1413

12

11

20

19

18

17

16

SYNC

SCLK

AVSS

VREF

HPOUT

EQ1

ER2

EQ3

AVDD

SPVSS

IRQ

DVDDDVSS

SPOUT2

SPOUT1

SDIN

CLK_I

TESTO

RST

/TESTI

R508

22K

R520

0R

R509

82K

C517

22N

TP502

TP_SPK-N

C518 120P

3.5. Circuit Diagram-5

Page 6

– 3-6 –

MIC_PWR

EXT_SPK

EXT_MIC

AUDIO_ON[1]

VINAUXP[2]

VINAUXN[2]

HANDFREE_IN[1]

VINNORP[2]

VINNORN[2]

HPOUT[5]

VOICEOUT[5]

MIC_PWR

VBAT

MIC_PWR

YMU_AVCC

VMEM

VANA MIC_PWR

R603

0

R628

TBD

R602

4.7K

C605

TBD

MIC601

MICROPHONE

1

2

R629

TBD

C622

0.1U

R615

47K

C612

TBD

T602

1 2

R623

0R

T603

1 2

C616

10uF

R621

0R

J601

PHONEJACK-B

2

3

6

5

4

1

T606 -B

1 2

R624

0R

T605 - B

1 2

C626

10U

R633

0R

TP601

TP_MIC

C623

100P

T604 -B

1 2

R608

TBD

C628

10uF

R625

0R

C620

0.1U

R634

0R

C603

0.1U

C615

33P

R626 2.4K

C630

2.2uF

C624

100P

R610

1M

R609

1M

C614

0.1uF

R630

0R

R611

0R

R620

0R

C629

2.2U

C606

TBD

C627

0.1U

C602

10U

C601

10N

C621

0.1U

U601

LP2985AIMX5-2.5

1

2

34

5

N

I

CG

O

R606

4.7K

C611

33P

C610

33P

R631

TBD

C608

33P

R632

100K

C607

33P

3.6. Circuit Diagram-6

Page 7

– 3-7 –

Connect to LCM

ADD[0..21]

ADD0

D13

D15

D10

D12

D8

D[0..15]

D14

D9

D11

KEYCOL_1 [1]

KEYCOL_2 [1]

KEYCOL_3 [1]

KEYCOL_4 [1]

KEYCOL_0 [1]

VIBRATOR_ON [1]BACKLIGHT[1]

KEYROW_0 [1]

KEYROW_1 [1]

KEYROW_2 [1]

KEYROW_3 [1]

POWER_KEY [3]

WE[1,4]

LCDCTL[1]

ADD[0..21][1,4]

NRESET_LCD[1]

LCDCS[4]

VBAT VBAT

VM EM

VM EM

C729

TBD

C730

TBD

C731

0.1UF

SW7 02

KEY [7]

1 2

SW71 6

SOFTKEY_RIGHT

1 2

SW71 1

KEY [#]

1 2

SW70 6

KEY [0]

1 2

SW70 1

KEY [*]

1 2

C732

TBD

SW70 3

KEY [4]

1 2

SW7 17

KEY [SEND]

1 2

SW7 12

KEY [9]

1 2

SW7 07

KEY [8]

1 2

SW7 04

KEY [1]

1 2

SW71 3

KEY [6]

1 2

R706

100R

SW70 8

KEY [5]

1 2

C733

0.1U

R705

1K

SW7 05

KEY_[UP]

1 2

C709

1U

SW7 14

KEY [3]

1 2

C706

1U

SW7 09

KEY [2]

1

2

U701

LCD interface

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

C86

VSS

V5

V4

V3

V2

V1

CAP2+

CAP2CAP1CAP1+

CAP3VOUT

VSS

VDD

D7

D6

D5

D4

D3

D2

D1

D0

RD/E

WR/R/W

A0

RES

CS1

SW71 8

POWERKEY

&

END

1 2

C734 0.1U

R701

1M

SW7 15

SOFTKEY_LEFT

1 2

C707

1U

SW7 10

KEY_[DOWN]

1 2

C702

0.47U

C701

4.7U

C708

0.47U

A

-

+

M701

Samsung(AY010300035)

12

C703

0.47U

C705

0.47U

C704

0.47U

C710

1U/0805 -B

D705

LED - B

D703

LED - B

D704

LED - B

D706

LED - B

D701

LED - B

D702

LED - B

D709

HT-110NB5CT - B

R707

10K

33pF

D710

HT-110NB5CT - B

TBD

TBD

R704

0R

R702

150

123

4 5

678

C727

TBD

C725

33pF

C722

C723

33pF

C726

C721

TBD

C720

TBD

C724

33pF

D713

1SS355

R703

33R

1 2

3 4

R708

100K

U702

FFB2222A

1

2

3

4

5

6

E1

B1

C2

E2

B2

C1

C728

TBD

D[0..15][1,4]

3.7. Circuit Diagram-7

Page 8

– 3-8 –

LE [1]

DCSEN[1]

DCSTX[9]

RXQP [2]

GSMTX[9]

DATA [1]

TXEN[1,2,9]

TXIP [2]

TXQP [2]

TXIN [2]

CLK [1]

GSMRX[9]

RXIN [2]

GSMEN[1,9]

TXQN [2]

RXQN [2]

VRF

VTX[9]

[9]

[9]

VRF

13MHz [3]

DCSRX[9]

PCSRX[9]

VSYN [9]

[9]

VRF

RXIP [2]

VRF

RXEN1[1]

VTCXO

SXEN

[1]

C1234 15p

C1281

100p

C1283

33p

U1233

SRF1960NMC31K

1

2 3

4

G

IN G

OUT

L1262

12n

U1231

EPCOS B7707

1

2 3

4

IN

G OUT

G

TP6

L1261

12n

U1234

CX74017

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

181920212223242526272829303132

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

Tx/D

TXTUNE

RXEN

TXEN

PCO1

PCO2

VTXCP

VCC1

TXCP

TXFB

LNA/G

GNDLNA/G

LNA/D

FEEN

LNA/P

NC

NC

FILTN

FILTP

TXIP

TXIN

TXQP

TXQN

TXIFP

TXIFN

VCC2

CAPIP

CAPIN

CAPQP

CAPQN

LPFADJ

T/H

NC

NC

GNDD

VCCD

VCCF

FREF

GNDFN

GNDCP

LOCP

VCCFN_CP

SXEN

LD_MUX

DATA

CLK

LE

VDD

BYP

LOTUNE

VCCLO

VCC3

LOP

LON

RXQN

RXQP

RXIN

RXIP

VCC4

VCCTXVCO

NC

NC

NC

TX/G

C1273

0.1U

TP2

R1276

JP

C1267

8n2

R1202

510/1%

TP5

C1203 33p

R1266

10

C1271

22p

C1269 100n

R1232

39k/1%

L1202 27n

C1279

22p

R1268 10

C1262 10P

C1266

680p

C1213

0p5

R1267 10

R1264 2K

TP3

C1201

100p

R1275

JP

L1235

3n3

C1290

5p

C1278

100n

C1268

220p

B1262

BEAD

TP7

R1203

220/1%

B1263

BEAD

TP8

TP4

R1265

5k6

C1208

2.2n

B1261

BEAD

R1204

510/1%

C1277

22p

C1210

2.7p

C1238

470p

TP9 TP10

R1281

JP

C1276

100n

C1215 18p

C1288

33p

C1211

15p

C1204 22p

C1212

0p5

C1237

470p

R1290

10k

C1286

22p

R1231 JP

C1272 10u

L1237

2n2

TP1

L1266 82n

C1209

39p

R1279

51

R1271 JP

C1280

100n

U1232

SRF1842NHC31K

1

2 3

4

G

IN G

OUT

L1201

180n/0603

R1269 10

C1207

39p

C1202

100p

R1277 JP

R1201 JP

1

2

3

45

6

7

8

R1-1

R2-1

R3-1

R4-1R4-2

R3-2

R2-2

R1-2

C1285

100n

R1291

NM

C1235

18p

R1205

390

C1274

100n

L1234

8n2

C1284

10p

3.8. Circuit Diagram-8

Page 9

– 3-9 –

RFEN[1]

DCSRX[8]

GSMRX[8]

VTX[8]

PCSRX[8]

VSYN[8]

RAMP

[2]

GSMTX [8]

VRF [8]

TRSW2 [1]

TXEN [1,2,8]

TRSW1 [1]

TRSW3 [1]

DCSTX [ 8 ]

GSMEN [1,8]

PA_EN [1]

VBAT

C1141 33p

4.7K

4.7K

U1131EM B 3

4

5

26

3

1

C1174

1U

U1133

SHS-L090TL

1

2

3

4

5

11

10

9

8

7

6

12

13

14

15

16

GND

ANT

GND

VC3

GND

VC1

D_RX

P_RX

GND

D/P_TX

GND

GND

G_TX

VC2

GND

G_TX

R1112

49.9K

C1173

10U

L1101 JP

U1101

RF3110

1

2

3

4

5

12

11

10

9

6

7

8

DCS IN

BAND SELECT

PA ENABLE

VBATT

VREG

VCC2

DCS OUT

VCC OUT

GSM OUT

VRAMP

GSM IN

VCC2

C1142 12p

L1131

6.8nH

C1177

4.7U

R1101

2 1

4

3

L1133

DNI

C1178

DNI

C1138

10p

C1176

0.1U

C1144 33p

R1114

180

C1146 0

C1136

33p

C1145

6.8p

AN1131

L1140

DNI

C1105

2.7p

TP13

R1113

180

C1107

DNI

C1175

1U

C1111

220U

4.7K

4.7K

U1132

EM B 3

4

5

26

3

1

C1179

1pF

C1109

33p

C1172

10n

C1112 1u

C1113

10n

C1132

39p

L1139 JP

C1147 1n8

L1136

DNI

R1115

100K

U1103

LDO/MAX8878EUK-2.9

1

2

34

5

VCC

GND

CTLBYP

OUT

L1132 8n2

L1143

DNI

L1144 1.8nH

R1111

110K

L1135

DNI

C1106

DNI

C1120 18p

R1102

2 1

3

4

C1140

1nF

C1110

100n

U1173

M AS9122

1

4

3

8

2

5

7

6

OUTA

ENA

ENBC

OUTB

OUTC

VREF

VCC

GND

J1131 MM8430-2600

12

453

6

INOUT

GND

GND

GND

GND

C1137

10p

3.9. Circuit Diagram-9

Page 10

– 4-1 –

5

AD6521ACA

U1234

CX74017

AD6522N

MC-222243AF9

-B85X-BT3

U601

LAUA

U301

ADP3408

6330

ACBM

U1173

9122

U304

E13.000

U1101

RF3110

U309

43FCX

U504

Y757B

U505

4. LAYOUT DIAGRAMS

Loading...

Loading...