Panasonic EB-G50 Schematics

– 11–1 –

E3D

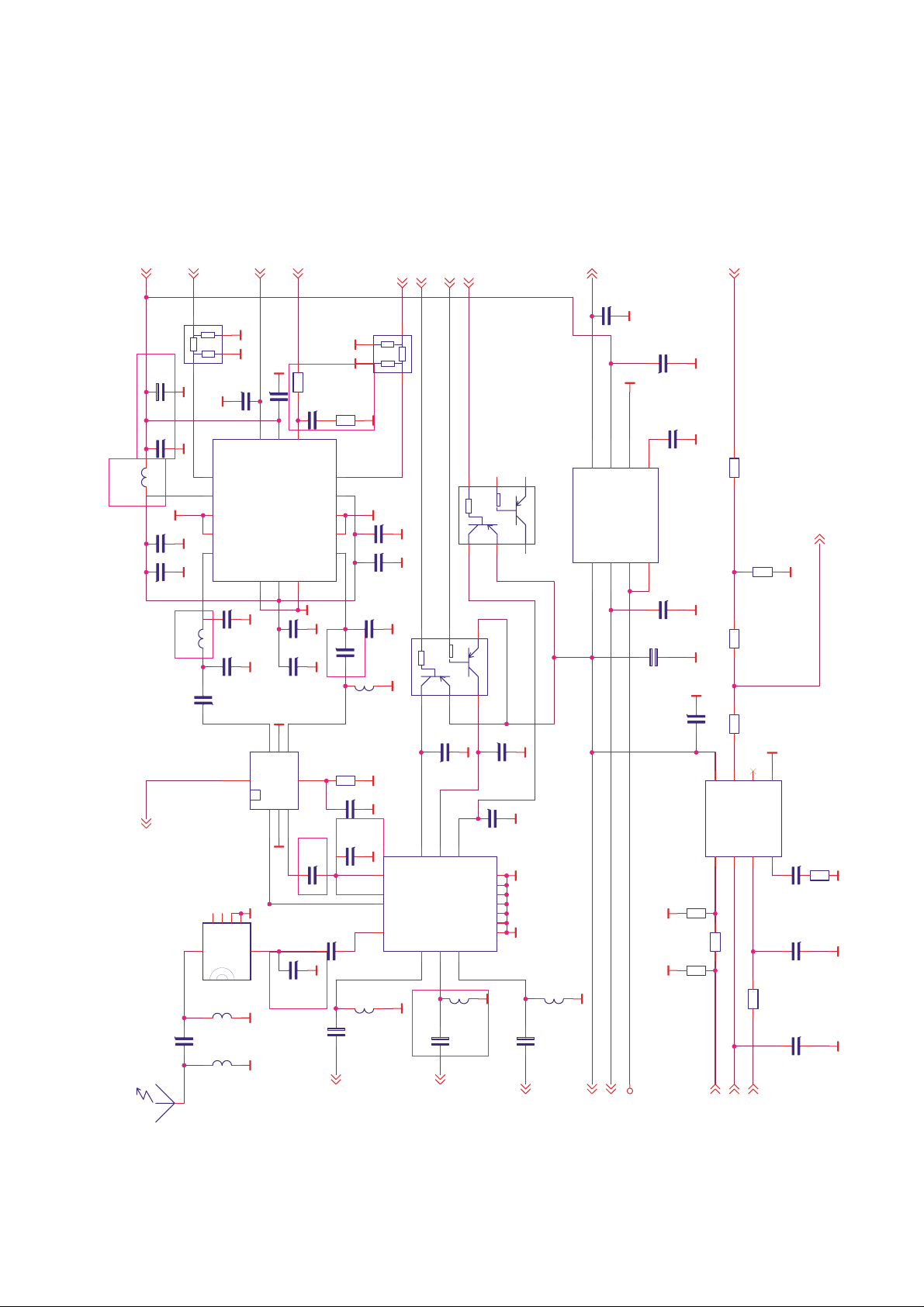

11. CIRCUIT DIAGRAM

11.1. Circuit Diagram of RF Band-1

E3B

B1100

modify0512

VBAT

+

BEAD

CPL

C1101

220uF

-

C1156

12p

C1102

33p

C1103

E3D

C1161

21

R1103

10n

L1101

C1155

AN1161

DCSTX [8]

J1161

2

JP

U1101

5

6

7

8

9

JP

6

GND

3

4

NM

33p

L1161

L1162

C1115

VCC

GND

GND

C1105

NM

C1106

NM

U1131

4

3

GND4GND5GND

IN1OUT

15nH

15nH

BS [8]

C1116

33p

4

3

BS

Vcmos

DCS/PCS IN

GSM OUT

GND10VCC11GND

5

7

6

G

D/I

G/I

ISO

CPL

G/O1G2D/O

3

MM8430-2600

modify0512

VAPC

220

2

VAPC

12

C1107

C1108

LDC15D19

8

E3D

C1154

NM

C1185

R1101

R1142

C1114

JP

CX77314

GSM IN

VCC

GND

GND

DCS/PCS OUT

100p

C1111

10n

R1131

C1131

NM

modify0512

22p

C1141

C1143

GSMRX[8]

P_RX 0 0 1

NM

L1152

U1173

VTX[ 8]

8

OUTB

OUTA

1

VRF[8]

C1176

1u/0603

7

VCC

OUTC

2

VSYN[8]

6

GND

ENBC

3

VTCXO

5

VREF

ENA

4

C1178

C1174

C1175

10u/0805

C1177

MAS9122

1u/0603

C1184

33p

Mode Vc1 Vc2 Vc3

G_TX 1 0 0

D/P_TX 0 1 0

4.7K

10p

C1172

10p

15

12

8

6

5

3

1

C1145

G/D_RX 0 0 0

4

PEMB3

3

SHS-L090TL

12p

PCSRX[8]

TRSW_DT [1]

TRSW_GT [1]

GSMTX [8]

4

3

2 1

C1110

E3D E3D

4.7nH

NM

7

13

2

U1141

L1141

NM

C1113

33p

10n

C1112

NM

R1102

26

U1171

11

D/P_TX

VC1

G_TX

ANT

G_RX

16

modify0529

1k

1

16

15

14

13

6.8p

L1102

51

C1157

39p

33p

4.7K

14

VC2

D_RX10P_RX

C1144

DCSRX[8]

U1172

5

1

33p

C1171

4

9

L1142

3n9

4.7K

VC3

26

0.5p

TRSW_PR [1]

5

4.7K

1

4

PEMB3

3

C1173

GND

GND

GND

GND

GND

GND

GND

10n/X7R

R1199

1u/0603

R1197

R1196

8

VCC

RFIN1ENBL2VSET3FLTR

51.1

R1192

910

R1191

51.1

R1190

CPL

PA_EN [1]

7

VAPC

R1193

RF_TXEN[1]

1k2

JP

JP

6

NC

RAMP[2]

R1198

1k

5

4

51k

G

AD8315

U1103

C1182

68p

C1181

15P

C1180

150p

VAPC

R1195

JP

– 11–2 –

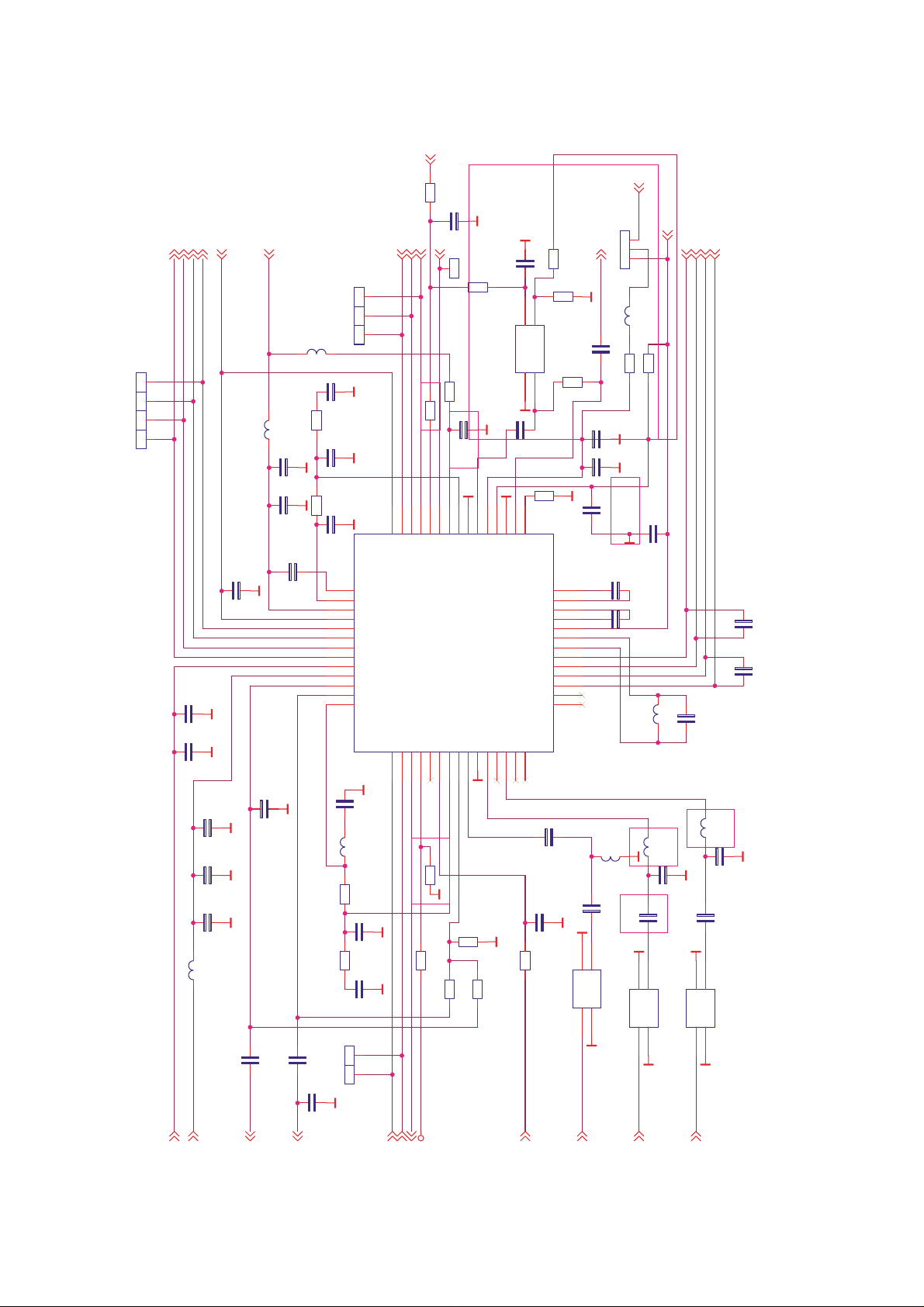

11.2. Circuit Diagram of RF Band-2

AFC

VTX

10k

R1232

C1230

100n

VRF

LE

680p

U1201

43

42

VDDBB

UHFBYP

UHFTUNE

VCCUHF

VCC3

RXQN

RXQP

RXIN

RXIP

VCC4

TX900

RXENA1TXENA2PCO3VCXO_EN

CLK

DATA

R1296

40

41

39

LE

CLK

DATA

XTALTUNE

VCCTXVCO

TX1800/TX1900

TXVCOTUNE

PDETVCC

4

5

NM

38

SXEN

TP8

1

E3D

37

36

SXENA

VCCFN_CP

VCC16TXCPO7TXINP8LNA900IN9GNDLNA900

R1294

JP

E3B

modify0522

10

R1224

10p

C1226

33

34

35

XTAL

VCCF

GNDFN

UHFCPO

LNA1800IN

10

11

C1291

U1291

R4

30

32

31

VCCD

GNDD

PDET12LNA1900IN

13NC14NC15

NM

1

4

Vc

Vcc

GND2o/p

3

100n

29

R1221

LPFADJ

XTALBUF

BEAD

R1293

R1292

100nF

R1291

VTCXO

39k/1%

CX74063

CAPQN

28

CAPQP

27

CAPIN

26

CAPIP

25

VCC2

24

TXIFN

23

TXIFP

22

TXQN

21

TXQP

20

TXIN

19

TXIP

18

BBVAPC

17

PAVAPC

16

NM

RXIN

RXQN

RXIP

VRF

RXQP

1

TP4

1

TP3

1

TP2

1

TP1

C1245

22p

C1246

100n

C1244

100n

VSYN

B1241

BEAD

C1243

C1242

B1222

22p

10u

0.1u

C1241

BEAD

R1226

R1225

C1229

7

TP

6

TP

5

TP

2k

5k6

220p

44

45

46

47

48

49

50

51

52

53

54

55

56

1

1

1

C1228

8n2/PC

C1227

13MHz_BB

C1225

1n

C1224

C1223

C1221

R1297 JP

B1221

10

R1223

100n

22p

E3B

22p

del C1222

C1215

C1214

1

2

3

BEAD

R1222

470p

470p

L1211

82n

10

C1216

100n

TXQN

TXQP

C1211

TXIN

TXIP

NM

C1213

NM

C1212

22p

C1250

2p7

C1247

10p

C1248

33p

C1249

33n

L1241

27n

C1253

33p

VTX

VRF

GSMTX

DCSTX

R1202

C1254

18p

C1252

510/1%

C1203

2.2n/X7R

TP10

TP9

180R

C1204

L1201

180n/0603

R1203

1

1

39p/NPO

220/1%

C1202

39p/NPO

E3B

modify0522

RXEN1

RF_TXEN

R1295

R1231

VTCXO

BS

NM

JP

R1204

390

R1205

51

R1206

510

R1207

VRF

C1262

C1205

10

15p

100p

C1265

4

U1261

3

G

IN1G

2

GSMRX

L1261

OUT

SAFSE942

15p

8n2

C1266

4

U1271

L1271

3

G

OUT

IN1G

2

DCSRX

E3C

modify 0529

3n9

0p5

C1271

E3C

JP

C1267

modify 0529

B7744

U1272

3

4

G

OUT

IN1G

2

PCSRX

L1272

3n9

C1272

B7740

0p5

12p

– 11–3 –

D[0..15]

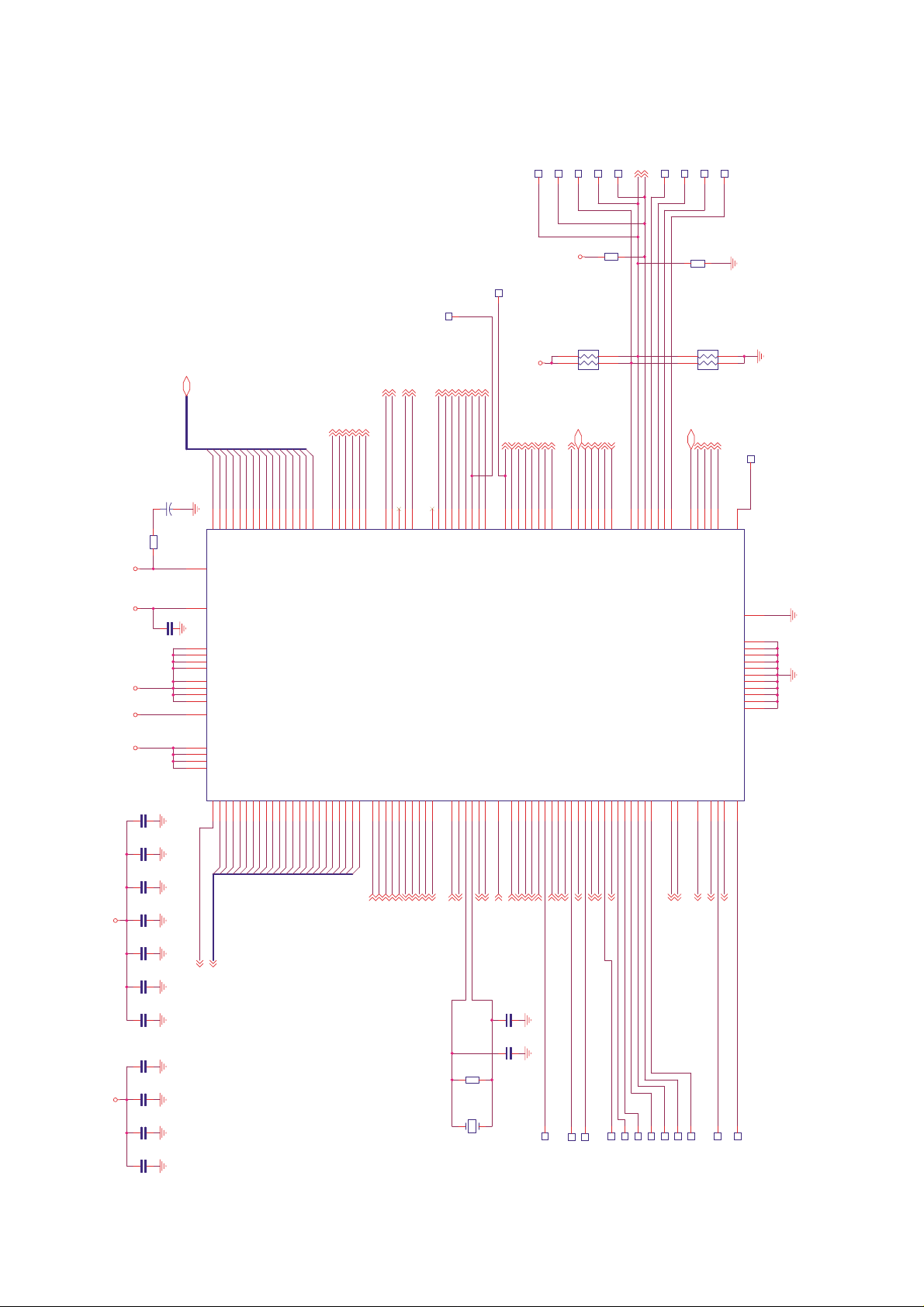

11.3. Circuit Diagram of GSM Processor

RX

TX

TP130

TP129

TP106

TP_USC01TP115

1

1

VMEM

TP101

TP_CLKOUT

TP124

TRSW_PR

TRSW_DTLETRSW_GT

RF_TXEN

RXEN1

SXEN

1

RXEN

1

R103

VMEM

PA_EN

DATA

CLK

TXEN

RXEN

TP113

1

TP_USC1

R105

100K/0402R

TBD

3 4

1 2

TP_USC2

1

USC1

USC2

TP116

TP_USC5

TP112

TP_USC31TP114

TP_USC41TP118

TP_USC6

1

1

R106

100K/0402R

R107

TBD

3 4

1 2

D[0..15]

D1

D3

D2

D0

SEIKO XH414H

BAT101

+

R101

0R/0402R

VRTCVMEM VMEM

C112

0.1U/0402C

DATA0N6DATA1P6DATA2M6DATA3N7DATA4M7DATA5L7DATA6P8DATA7N8DATA8M8DATA9

A2

E3

D5

C6

B10

B14

N13

N9

N5

L2

L9

VCORE SIMVCC

C111

0.1U/0402C

C110

0.1U/0402C

C109

0.1U/0402C

C8

K14

P7

H1

U101

ADD0H4ADD1J3ADD2J2ADD3J4ADD4K3ADD5K2ADD6K4ADD7L4ADD8L1ADD9L3ADD10L5ADD11M1ADD12M2ADD13N1ADD14P1ADD15N2ADD16P2ADD17N3ADD18M3ADD19P4ADD20N4ADD21M4ADD22(nDISPLAYCS)

D8

D4

D7

D5

D6

D9

D14

D15

D13

D11

D10

D12

P9

P10

N10

M10

P11

N11

DATA10M9DATA11

DATA12

DATA13

DATA14

VDDRTC

DATA15

VPEG1

VEXT4

VEXT3

VEXT2

VEXT1

VMEM4

VMEM3

VMEM2

VMEM1

VSIM

VCC4

VCC3

VCC2

VCC1

ADD1

ADD3

ADD2

ADD10

ADD4

ADD6

ADD5

ADD7

ADD15

ADD13

ADD11

ADD9

ADD12

ADD14

ADD8

ROMCS

RAMCS

RD

HWR

LWR

WE

CLKOUT_GATE

CLK_OUT

ARSM

VBC_RESET

BSOFS

BSDO

ASDO

ASDI

ASFS

ATSM

VSDO

USC2

USC0

BSDI

USC1

BSIFS

VSFS

VSDI

SIM_IO

USC3

USC5

USC4

USC6

SIM_ON

SIM_CLK

SIM_RESET

SIM_PROG

TP122

TP_JTAGEN

1

F13

M14

G13

P14

M13

N12

M11

P13

RD

WE

LWR

HWR

RAMCS

ROMCS

TXPA (GPO_2)

KEYPADROW0

KEYPADROW1

KEYPADROW2

F4

P5

A6

D4

ADD20

ADD17

ADD16

ADD21

ADD19

ADD18

ADD22

G11

F14

E13

H11

H12

TX_GSM (GPO_16)

TXPHASE (GPO_7)

PA_NEGBIAS (GPO_4)

DCS_SW_DRV (GPO_9)

ADD23(TX_DCS)GPO_17

DCS_SW_SYNC (GPO_8)

KEYPADROW3

KEYPADROW4

KEYPADCOL0

KEYPADCOL1

KEYPADCOL2

KEYPADCOL3

KEYPADCOL4C3CLKIN

B5

A5

E4

B4

A4

C4

E12

D14

B1

G12

C2

F11

D13

GPO_3

(TXON)GPO_1

(RXON)GPO_0

(OTH_EN)GPO_18

(OTH_CLK)GPO_21

(OTH_DATA)GPO_20

(OTH_VLO_EN)GPO_19

CLKON

OSCOUTB3OSCINA3PWRONB2RESET

GSM_SW_DRV (GPO_11)

L12

E14

G14

D2

E1

D1

CLKOUT

CLKOUT_GATE

(VBCRESET)GPO_24

GPIO_0

GPIO_1

N14

D11

D10

F1

A1

E2

F2

C1

ASDI

ASDO

(ATSM)GPO_6

(ARSM)GPO_5

GPIO_2

GPIO_3

GPIO_4D9GPIO_5

B12

B11

A11

C11

F3

G2

G4

G1

BSDI

ASFS

BSDO

BSIFS

BSOFS

GPIO_6

GPIO_7

GPIO_8D8GPIO_9

GPIO_10C9GPIO_11C7GPIO_12B9GPIO_13A9GPIO_14B8GPIO_15A8GPIO_16D6GPIO_17B7GPIO_18

A10

C10

H3

G3

C14

D12

A14

A13

E11

C12

USC0

H14

USC1

USC2

GPIO_19

GPIO_20

J12

H13

USC3

USC4

GPIO_21

J11

B13

USC5

VSDI

H2

VSDO

VSFS

J14

K13

L10

K12

J13

K11

USC6

SIMCLK

SIMDATAOP

BACKLIGHT0 (GPO_22)

BACKLIGHT1 (GPO_23)C5GPIO_32(WAIT)

A7

JTAGEN

SIMRESET (GPIO_23)

SIMVPROG (GPIO_22)

SIMSUPPLY (GPIO_24)

VSSRTC

GND11

GND10

GND9

GND8

GND7

GND6

GND5

GND4

GND3

GND2

GND1

GPCS0

GPCS1

SM_SW_SYNC (GPO_10)

nDISPLAYCS(LCDCTL)

M5

L13

L14

F12

M12

AD6525

D3

B6

D7

A12

C13

L11

P12

L8

L6

P3

K1

J1

C108

0.1U/0402C

C107

0.1U/0402C

C106

0.1U/0402C

C105

0.1U/0402C

0.1U/0402C

C104

C103

0.1U/0402C

VCORE VMEM

C102

0.1U/0402C

C101

0.1U/0402C

ADD[1..22]

LCD_CTL

ADD[1..22]

BBCLK

KEYCOL_0

KEYCOL_1

KEYROW_0

KEYROW_2

KEYROW_3

KEYROW_4

KEYROW_1

CLKON

KEYCOL_2

KEYCOL_3

KEYCOL_4

EOC

NRESET

LCD_ID

CHG_EN

POWER_O N

SYS_PWR_ON

R102

10M/0603R

CHG_DET

CHG_GATE_IN

C114

TBD

C113

TBD

1

X101

MC-146

TP126

TP_GPIO5

VIB_ON

YMU_IRQ

MIC_ON

GPIO10

PJ_ACC_IN

PJ_FUNC_SEL

YMU_AVCC _ON

1

1

1

1

TP102

TP105

TP125

TP104

TP_GPIO14

TP_GPIO16

TP_GPIO11

TP_GPIO9

BL_LCD

BL_KEY

TDI

TMS

TCK

1

1

1

1

TP107

TP109

TMS

TP110

TP108

TCK

TP_GPIO17

YMU_CS

LCD_CS

LCD_NRST

TDO

1

1

1

TDI

TP128

TP111

TDO

TP123

GPCS1

TP_GPIO32

– 11–4 –

VANA

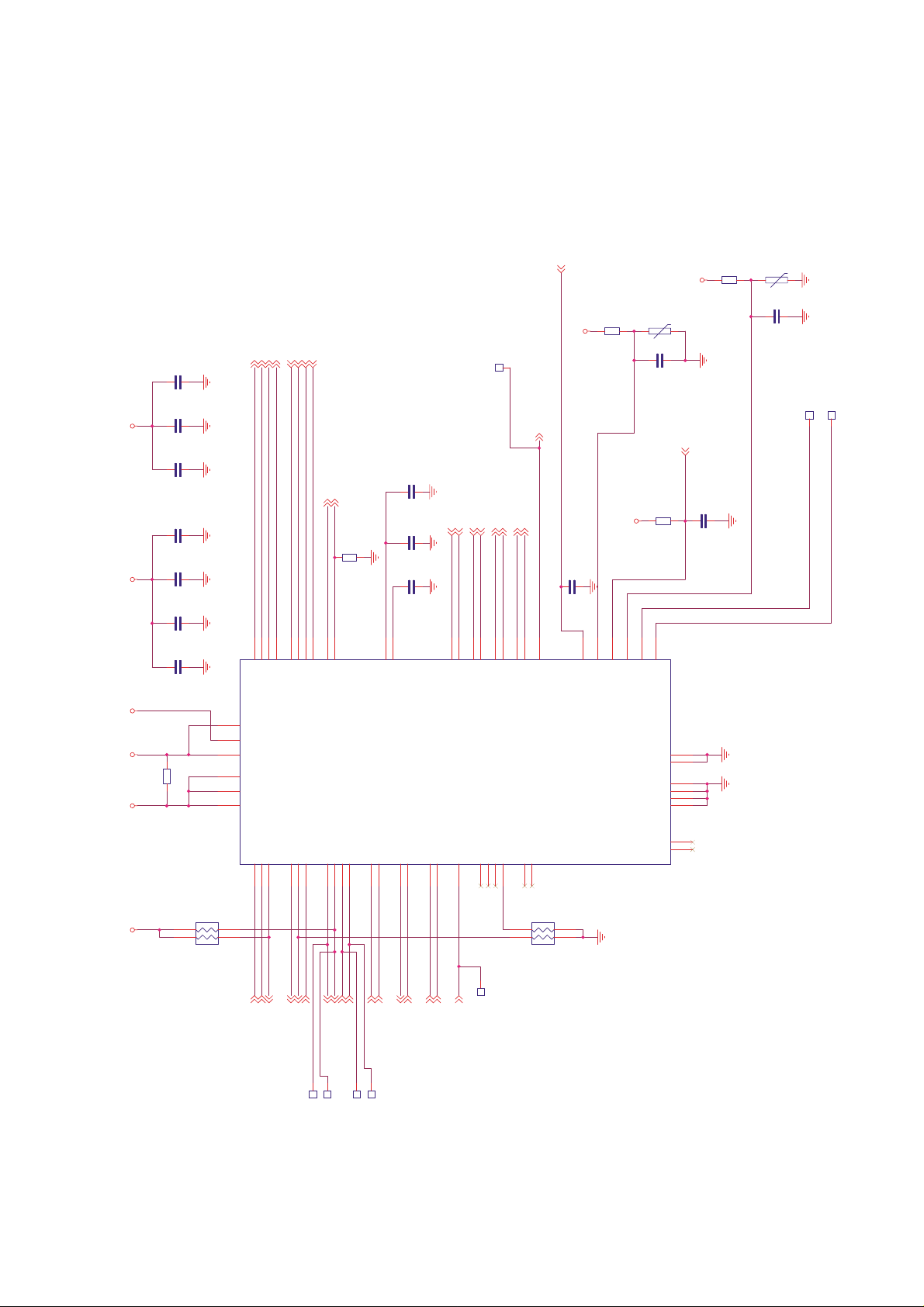

11.4. Circuit Diagram of Voiceband, Baseband and Codec

BAT_VOLTAGE

VANA

100K/NTC/0402R

R209

R208

200K/0402R/1%

VANA

TXIN

TXQN

RXIP

RXQP

RXQN

RXIN

TXIP

TXQP

C207

0.1U/0402C

C206

0.1U/0402C

C205

0.1U/0402C

AFC

RAMP

C204

0.1U/0402C

0.1U/0402C

C203

R206

100K/0402R

2.2U/0603C

C218

VINNORP

0.1U/0402C

C212

VINAUXP

VINNORN

VINAUXN

TP202

TP_BUZZER

1

VOUTNORP

VOUTNORN

VOUTAUXP

VOUTAUXN

BUZZ ER

Charging Temp

C214

10nF/0402C

VANA

NTC

C215

0.1U/0402C

BATTEMP

R210

100K/0402R/1%

C216

0.1U/0402C

R212

R211

100K/NTC/0402R

200K/0402R/1%

NTC

C217

0.1U/0402C

TP203

TP204

ADC5

PCB_Temp

1

ADC5

ADC6

1

ADC6

C202

0.1U/0402C

H9

D10

E10

E9

ITXN

DVDD3

DVDD2

DVDD1

AVDD3

AVDD2

AVDD1

ASFS

C9

QTXN

ASDI

D9

QTXP

IRXP

VSFS

IRXN

VSDI

C10

QRXP

VSDO

B10

QRXN

A10

AFCDAC

RAMPDAC

BSDI

BSIFS

G2

BSDO

BSOFS

R201

F9

ITXP

K5

G1

A1

J8

A9

F10

U201

ASDIH1ASFSH2ASDOJ1VSFSD2VSDOD1VSDIE1BSOFSE2BSDOF1BSIFSF2BSDI

3 4

1 2

100K/4P2R

ASDO

C201

2.2U/0603C

VMEM

R213

VANA VCOREVMEM VCORE

100K/0402R

A7

ATSMK3ARSM

J3

ATSM

ARSM

A8

REFCAP

REFOUT

C213

MCLKENK2MCLK

J2

CLK_OUT

CLKOUT_GATE

0.1U/0402C

TXONK4RXON

J4

TXEN

RXEN

K10

J10

VINNORP

VINNORN

RESET

K1

VBC_RESET

G10

H10

VINAUXP

1

TP201

K8

K7

VINAUXN

VOUTNORP

VOUTNORN

TDIB2TDOB1TMSC2TCK

C1

TP_VBCRST

K9

J6

K6

VOUTAUXP

VOUTAUXN

IDACOUTB4IDACREF

A3

R207

BUZZER

100K/4P2R

3 4

1 2

A4

AUXADC1A6AUXADC2A5AUXADC3B5AUXADC4

AUXADC5B6AUXADC6

B7

AD6521

DGND3

DGND1

AGND1

AGND2

AGND3

AGND4

NC(REFCAP2)

NC(MICCAP)

J5

A2

G9

B8

J7

B3

B9

J9

1

1

1

TP207

BSIFS

1

TP205

BSDI

BSDO

TP208

BSOFS

TP206

Loading...

Loading...