Panasonic DP 130, DP 150 Schematics

ORDER NO. MGCS010501G0

Technical Guide

Digital Copier

DP-130/150

Please file and use this manual together with the service manual for Model No. DP-130/150, Order No.

MGCS010207C0.

© 2001 Matsushita Graphic Communication Systems, Inc.

All rights reserved. Unauthorized copying and distribution is

a violation of law.

Table of Contents

1 System Description .................................................................................................. 4

1.1. Electrical Circuit Explanation .................................................................................................. 4

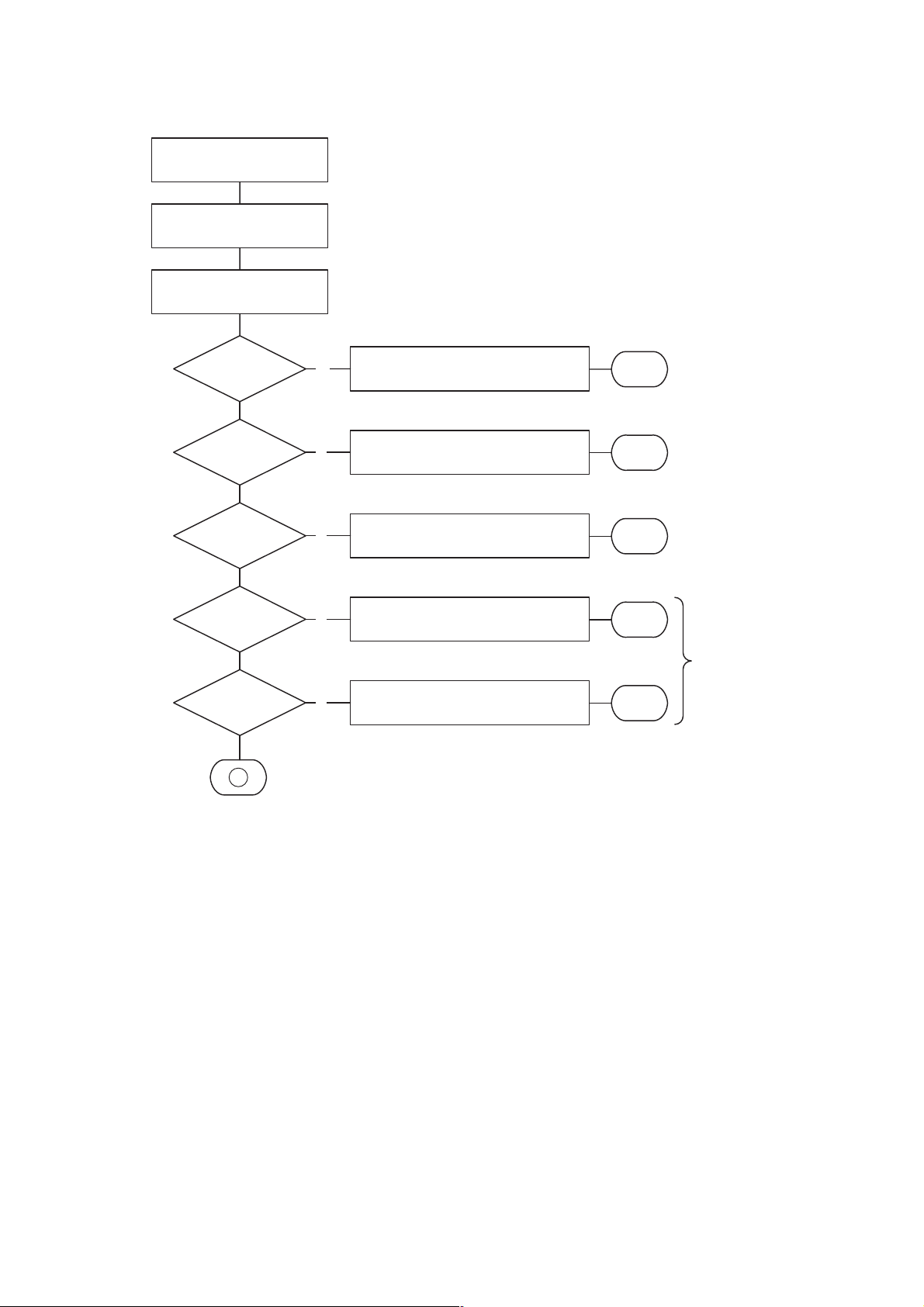

1.2. Power On Initial Flow Chart .................................................................................................... 21

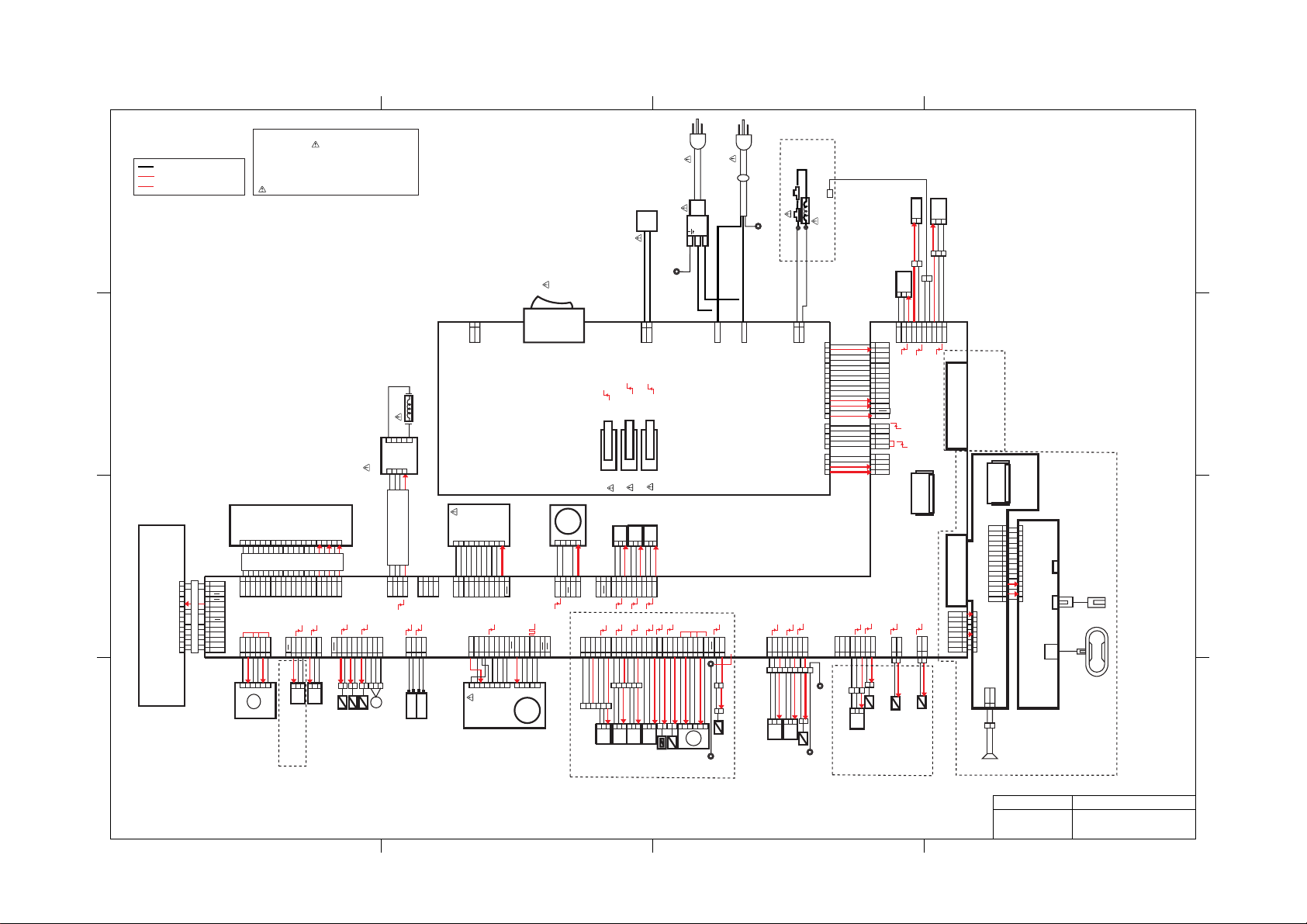

2 Schematic Diagram................................................................................................. 26

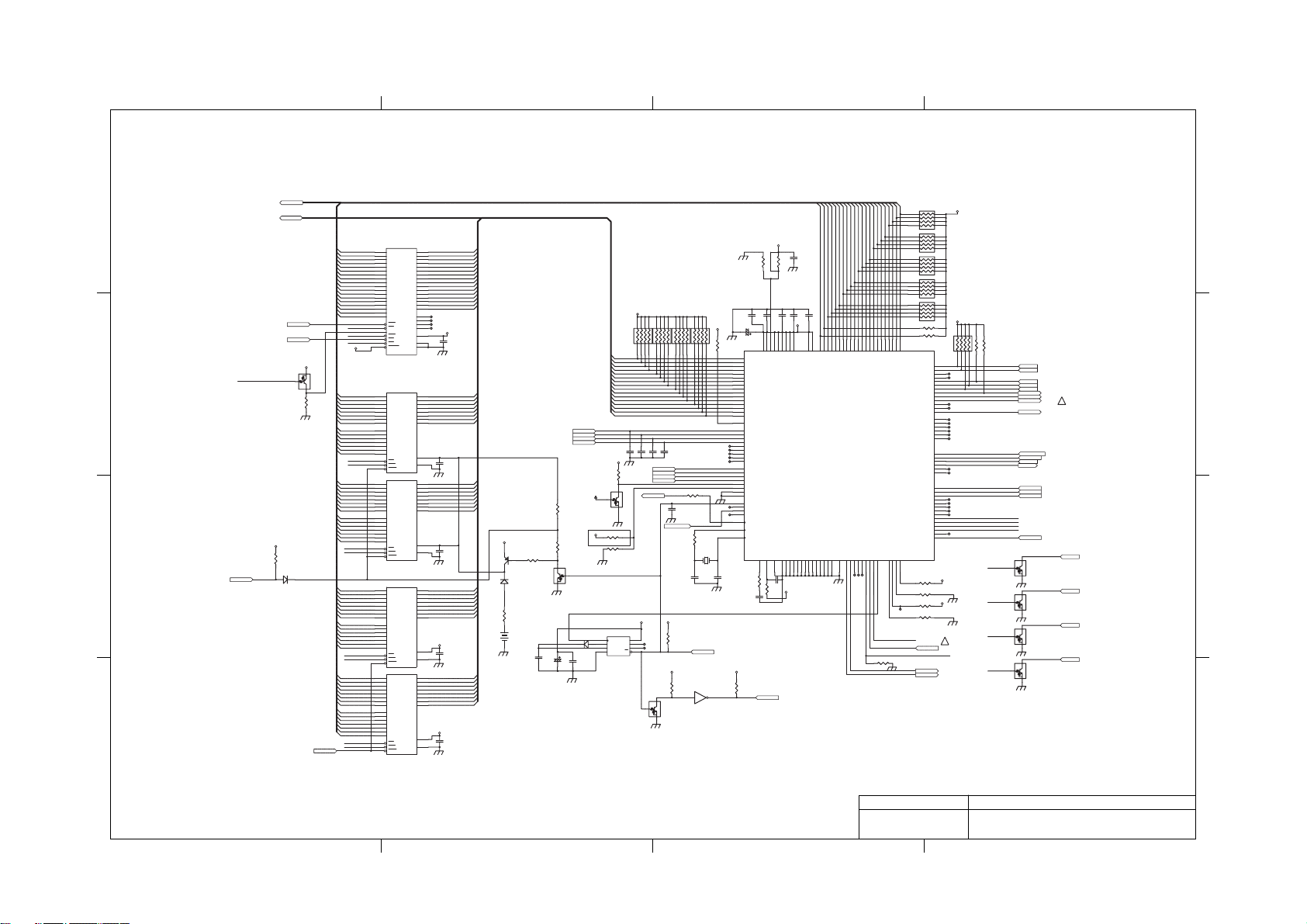

2.1. General Circuit Diagram System Circuit ................................................................................. 26

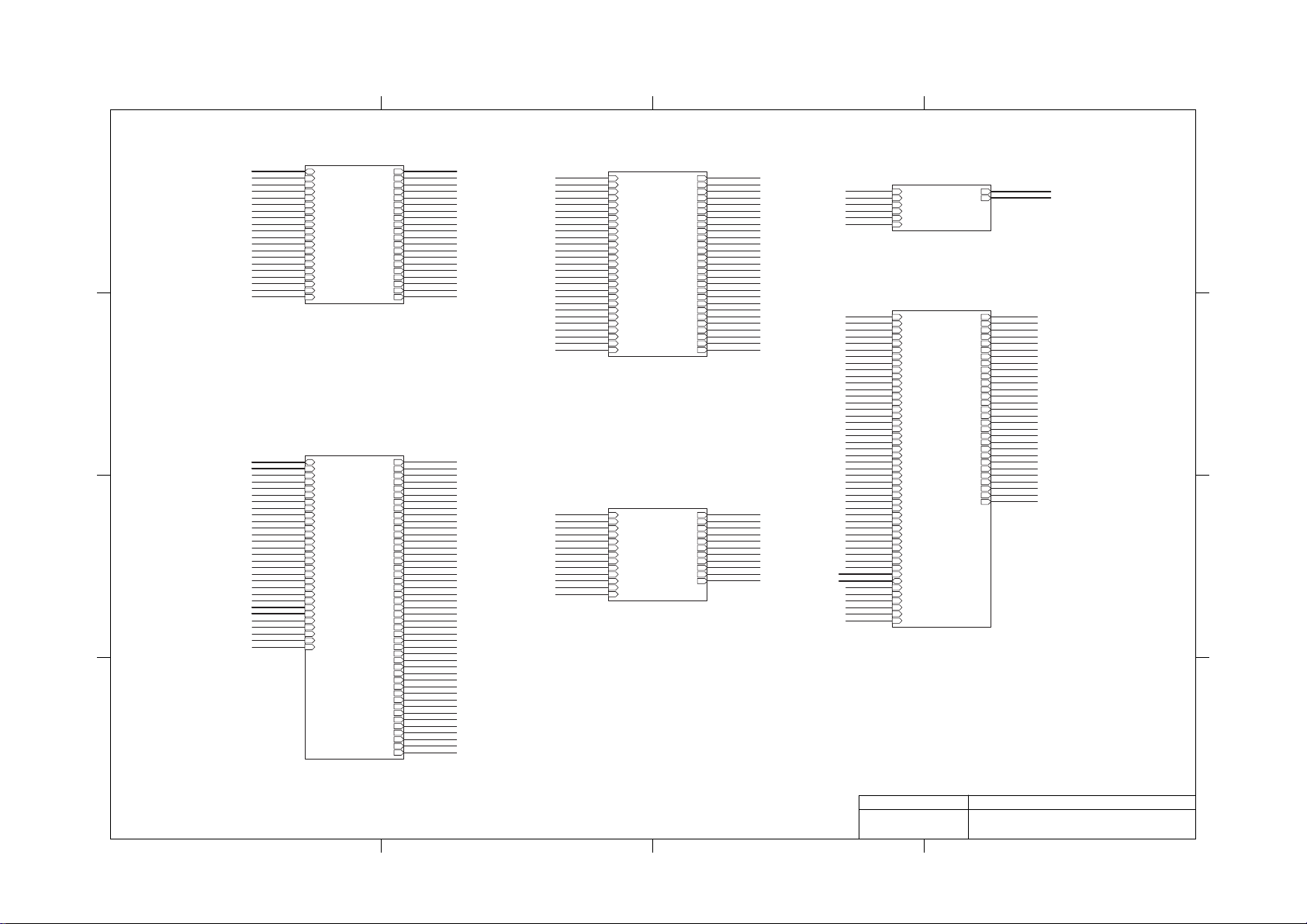

2.2. CPU PC Board (V Model) ....................................................................................................... 27

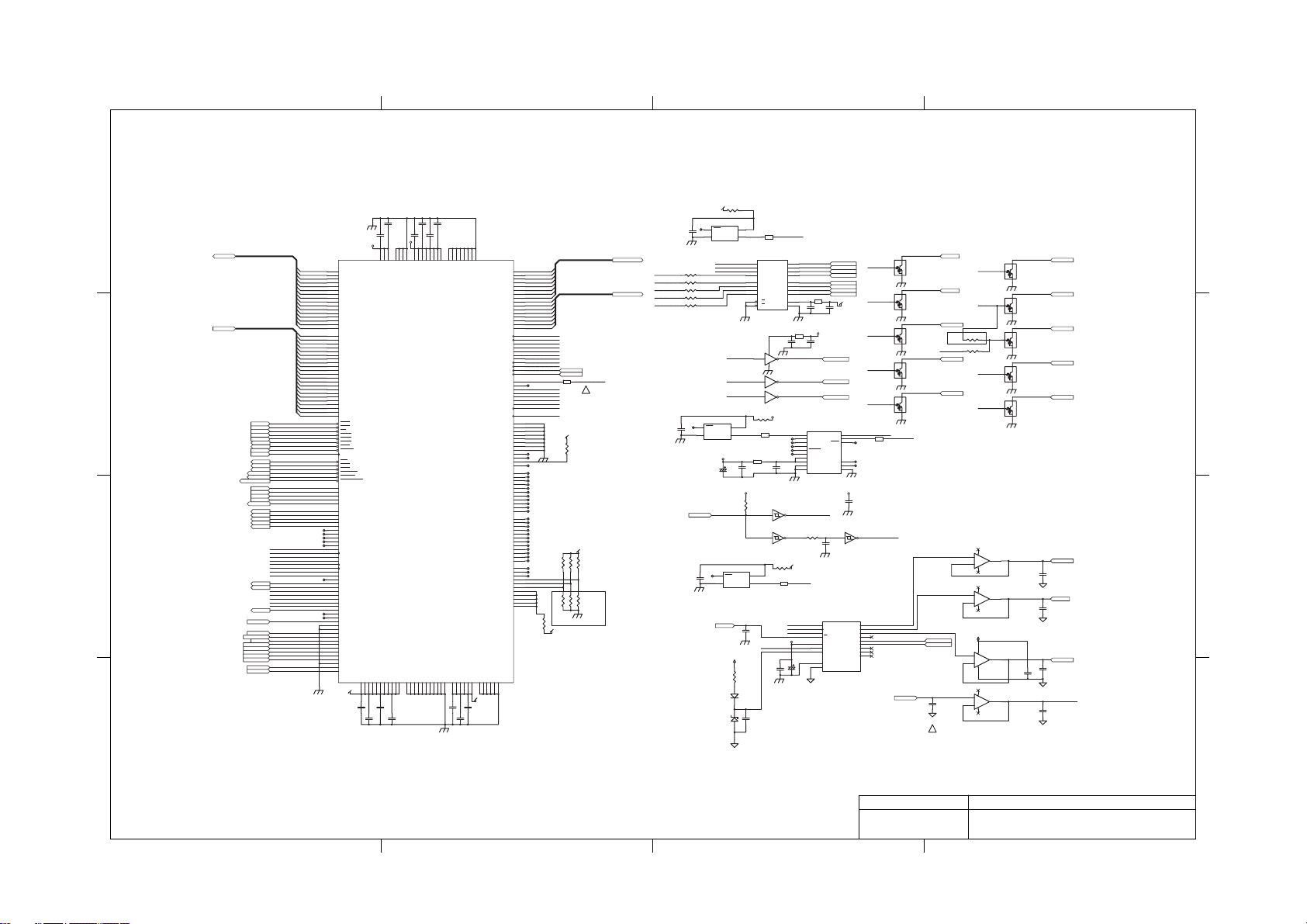

2.3. CPU PC Board (P/A/PA/PP/FX Model)................................................................................... 34

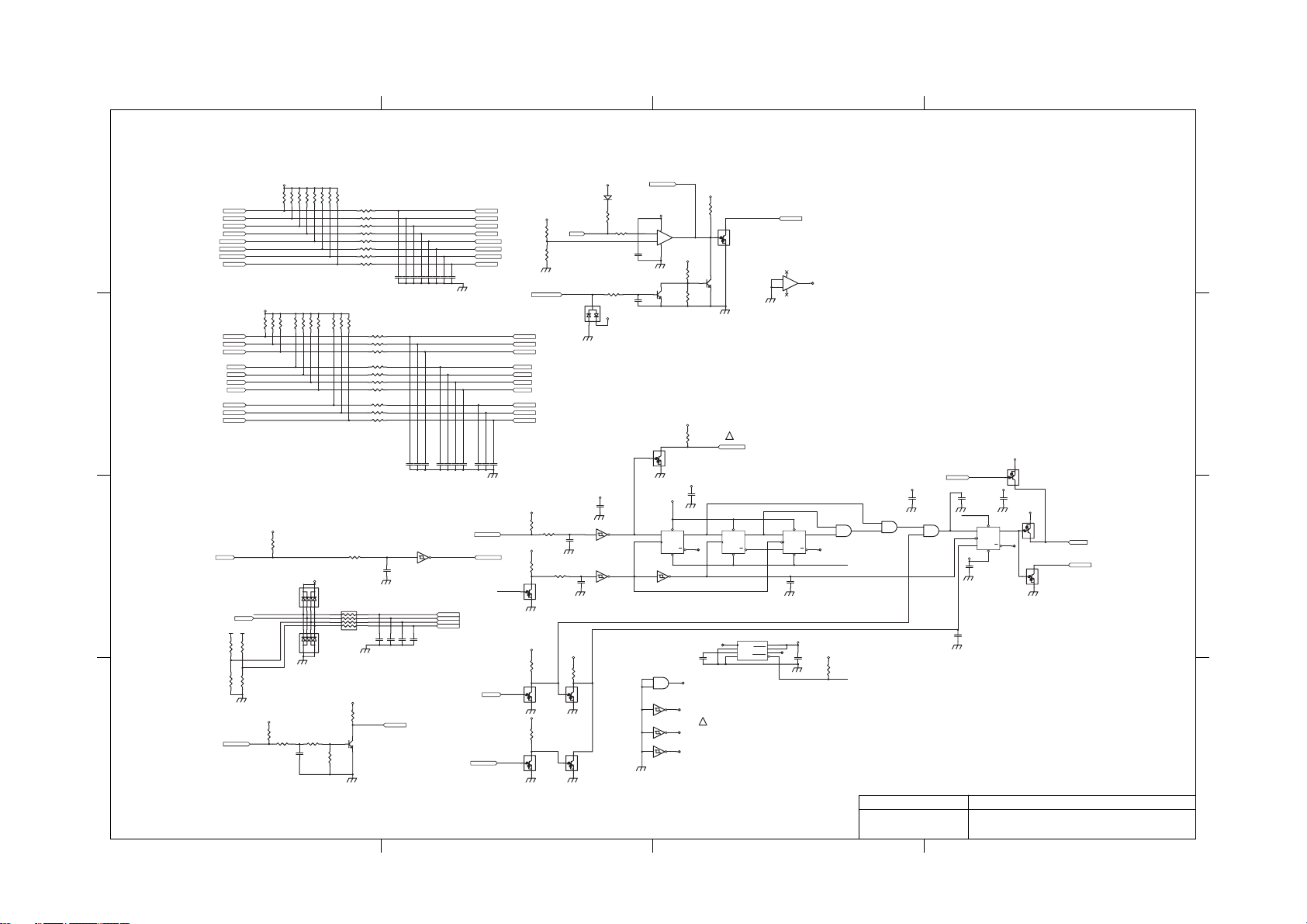

2.4. CCD PC Board ....................................................................................................................... 45

2.5. PNL PC Board (V/P Model) .................................................................................................... 48

2.6. PNL PC Board (A/PA Model) .................................................................................................. 49

2.7. PNL PC Board (FP/FX Model) ................................................................................................ 50

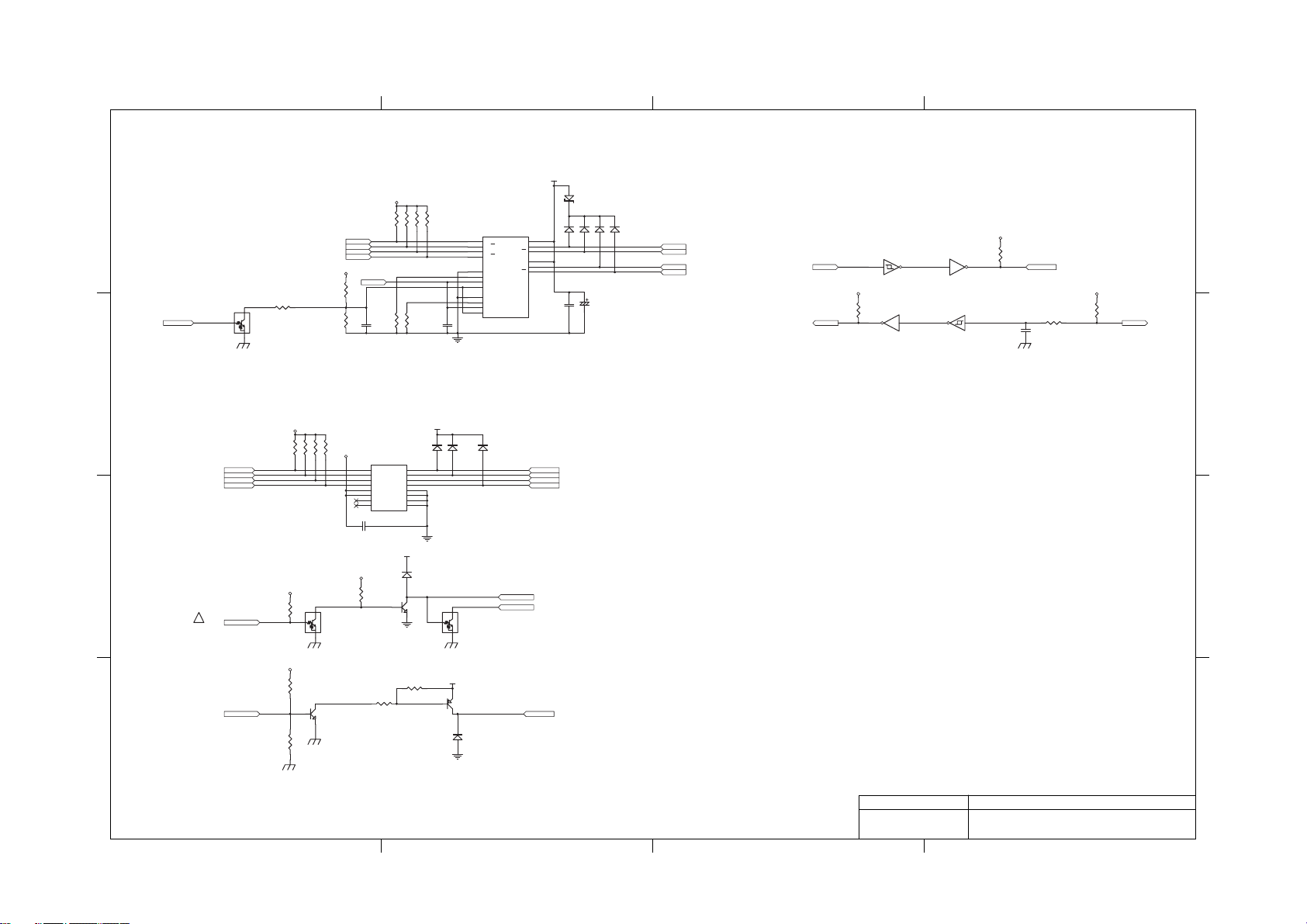

2.8. G3B PC Board. ....................................................................................................................... 51

2.9. LCE PC Board ........................................................................................................................ 56

2.10. LVPS PC Board (North America) ............................................................................................ 57

2.11. LVPS PC Board ...................................................................................................................... 59

(V Model except North America)

2.12. LVPS PC Board ...................................................................................................................... 61

(P/FP Model except North America)

2.13. LVPS PC Board (Taiwan)........................................................................................................ 63

3

Electrical Circuit Diagram & Parts List...........................................................................

3.1. Country Codes........................................................................................................................ 65

3.2. Main CPU PC Board (FFPWB0665 for DP-150FX/FP) .......................................................... 66

Main CPU PC Board (FFPWB06651 for DP-150A)

Main CPU PC Board (FFPWB06652 for DP-130P/150P)

Main CPU PC Board (FFPWB06653 for DP-150PA)

3.3. Main CPU PC Board (FFPWB06641 for DP-150/130) ........................................................... 87

3.4. Control Panel PC Board (FFPWB0667 for DP-150/130) ........................................................ 96

Control Panel PC Board (FFPWB06671 for DP-150A/150P/150PA/130P)

3.5. Control Panel PC Board (FFPWB0668 for DP-150FP/FX)................................................... 100

3.6. CCD PC Board (FFPWB0666) ............................................................................................. 104

3.7. LCE PC Board (DZEP000441) ............................................................................................. 107

3.8. Main LVPS PC Board (FFPWB06691 for North America)..................................................... 109

3.9. Main LVPS PC Board (FFPWB06692, DP-150 except North America).................................114

3.10. Main LVPS PC Board (FFPWB06694, DP-150A/P/FP except North America)......................119

3.11. Main LVPS PC Board (FFPWB06695 for Taiwan) ................................................................ 124

3.12. G3B PC Board (FFPWB06711) ............................................................................................ 129

Note:

V model : DP-130/150 P model : DP-130P/150P A model : DP-150A

PA model : DP-150PA FP model : DP-150FP FX model : DP-150FX

65

3

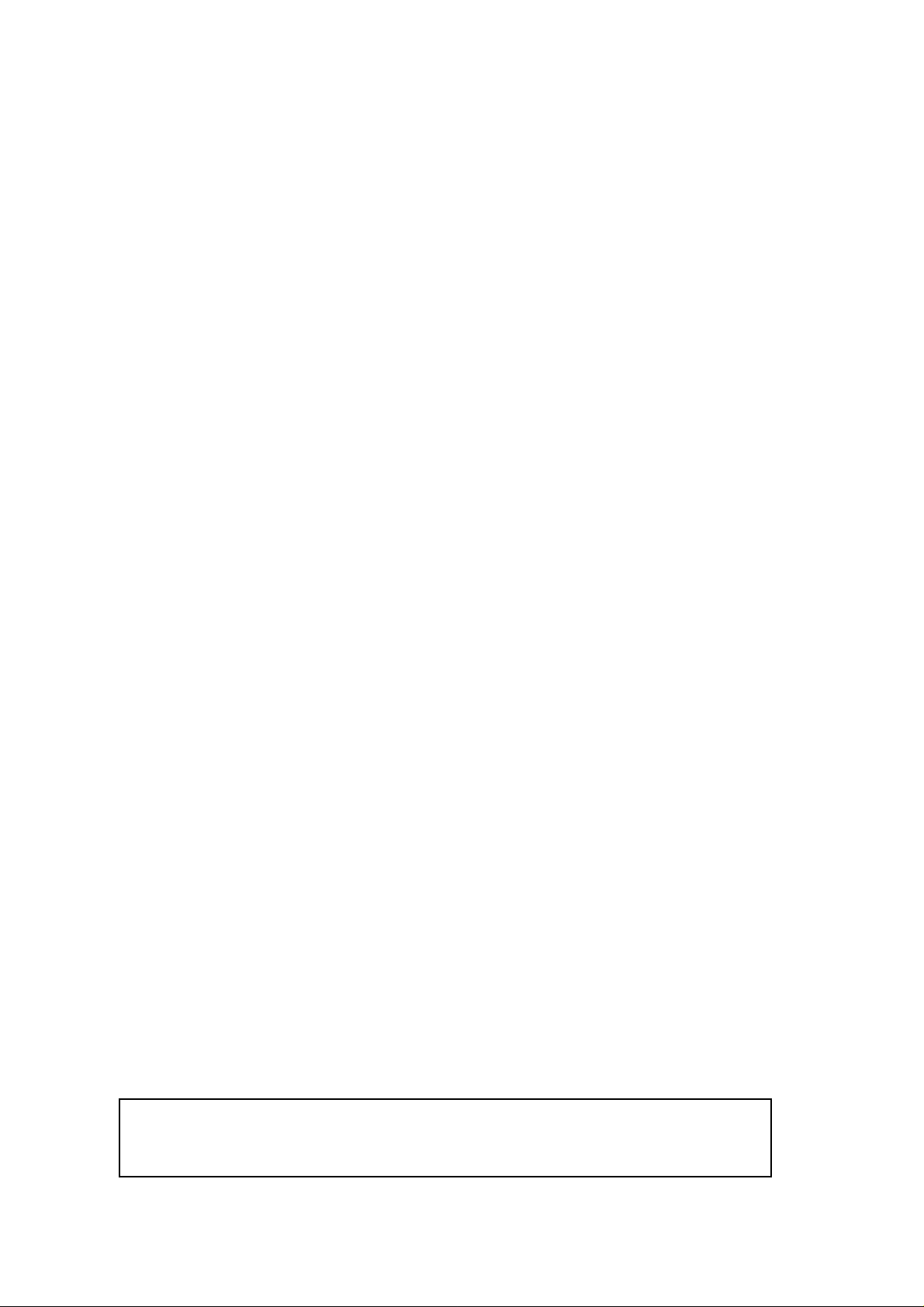

1 System Description

1.1. Electrical Circuit Explanation

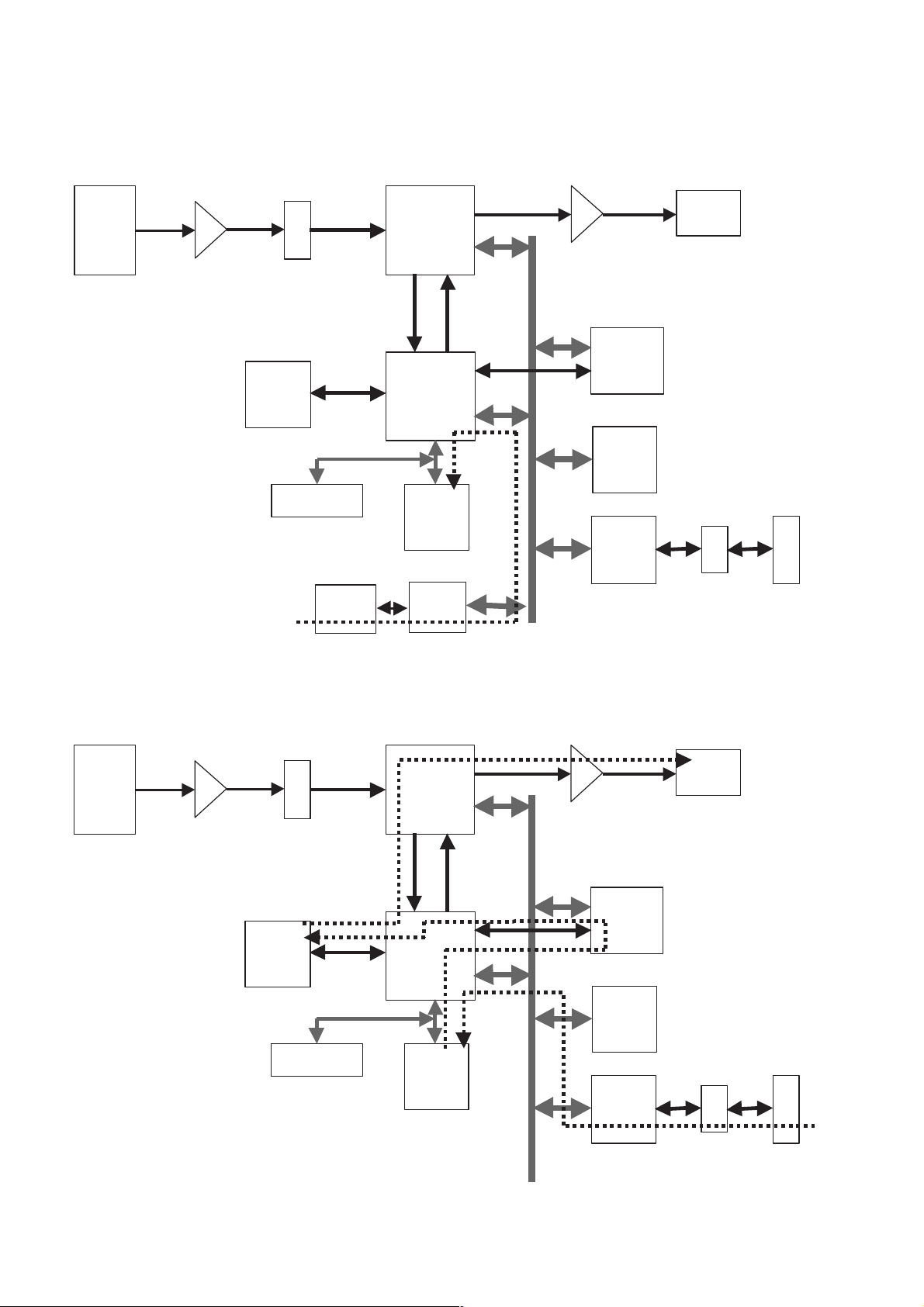

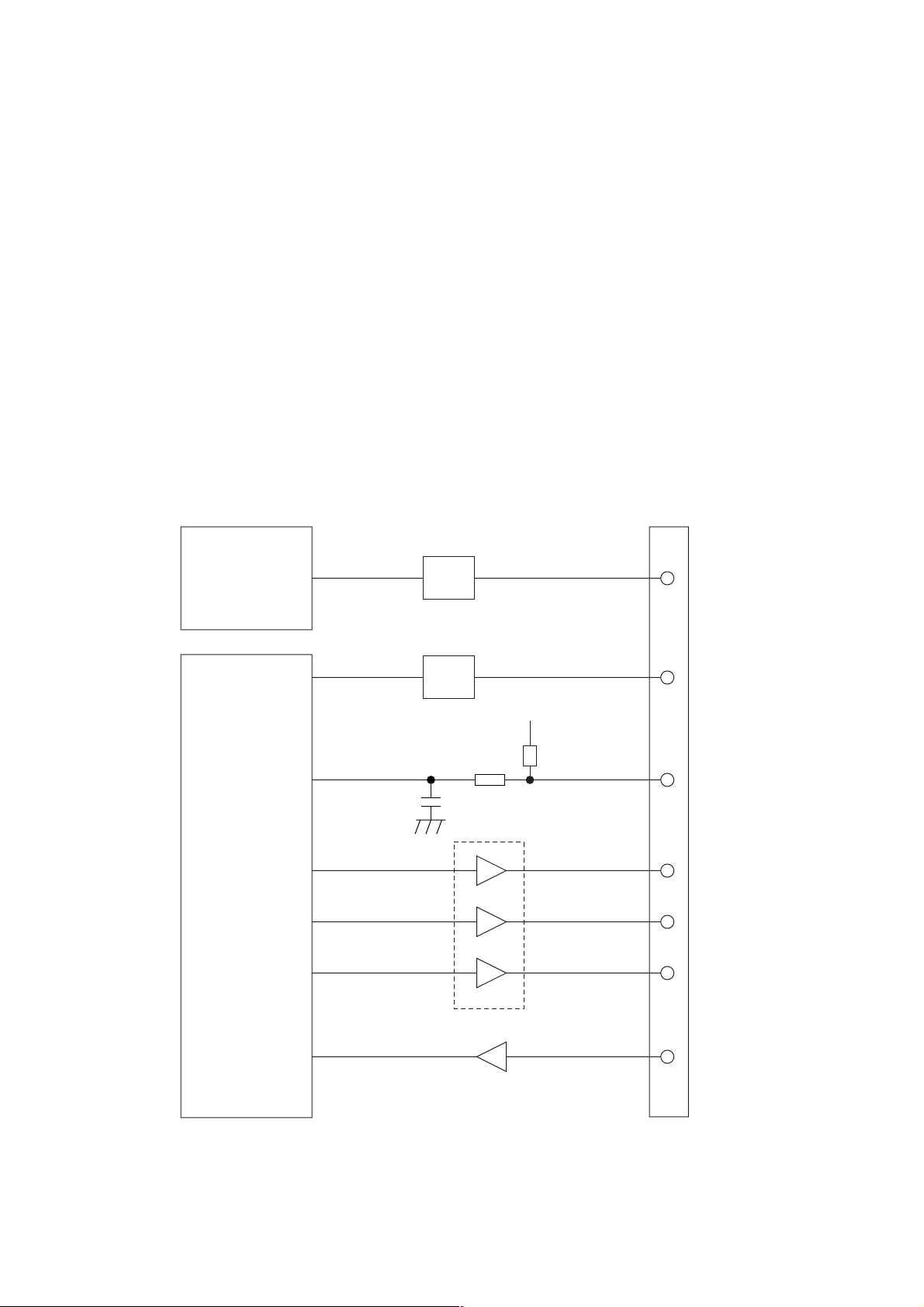

1.1.1. Block Diagram

Scanner

Lamp

Inverter

LM

DRAM8MB DRAM8MB

5V2

3.3V

DRAM BOARD

1284

IF

CCD

CCD PC Board

HPSN

GA1

GA2

DRAM16MB

PCSN

3.3V

3.3V

Sort

Amp

12V

5V2

ADC

3.3V

IEEE1284

5V1

RST

-12V5V2

5V1

GA3

12V

SRAM

128KB

Printer

5V2

CODEC

PM2

5V2

Program

2MB FROM

5V2

Program

2MB FROM

5V2

SRAM

32KB

5V2

SRAM

32KB

5V2

CPU

SH2

SH7041

Processor

28 MHz

Control Panel

5V2 5V1

Control Panel

5V2

RST

Energy Saving SW

24V 12V

5V2

D/A

Print

5V1

CPU

TMP86CH06U

LCD

5V2

ADF

(for DP-150A/PA/FP/FX)

AFOSN

SOL

Laser Safety

SW

HVPS

MM

Paper Feed Unit

PFOSN

FUOSN

TH

Fuser Lamp

ADF

PESNRRSN PFSN PFOSN

APC

TESN

NDSN

FM

TS

SOL

5VLD

LSU

LD

PESNRRSN PFSN

HPESN

DOSN

LVPS&ACD

• +5V1

• +5V2

• 3.3V

• +12V

• -12V

• +24V (SVP)

• +24V(PVP)

PM

SM

Drum

Discharge

Lamp

SOL

SOL

SOL

SP

5V2

FAX

2MB FROM

Program

512KB FROM

MODEM

TR88017

Analog

Transformer

(for DP-150FP/FX)

DP Signal

NCU

DSP

MN195004

SRAM

32KB

PC

FAX

16Hz Detected

5V1

FAX MEMORY IF

5V2

CODEC

MN86064

Telephone Line

5V2

FAX Memory

2 or 4 FROM

4

ADU (for DP-150FX)

SOL

SOL

DXISN

2nd Paper Feed Module

SOL

PESN PFSN

SOL

DXOSN

PFOSN

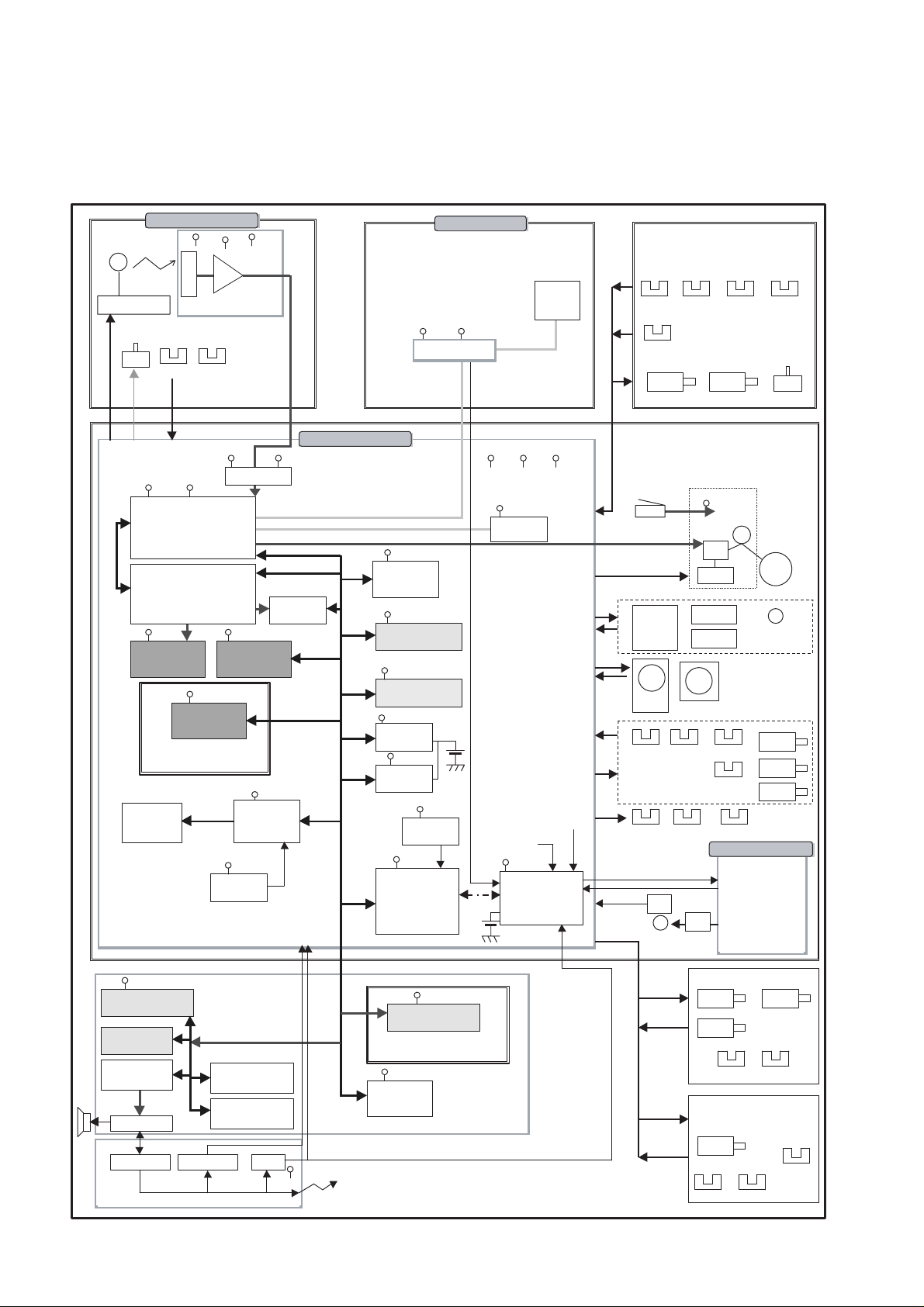

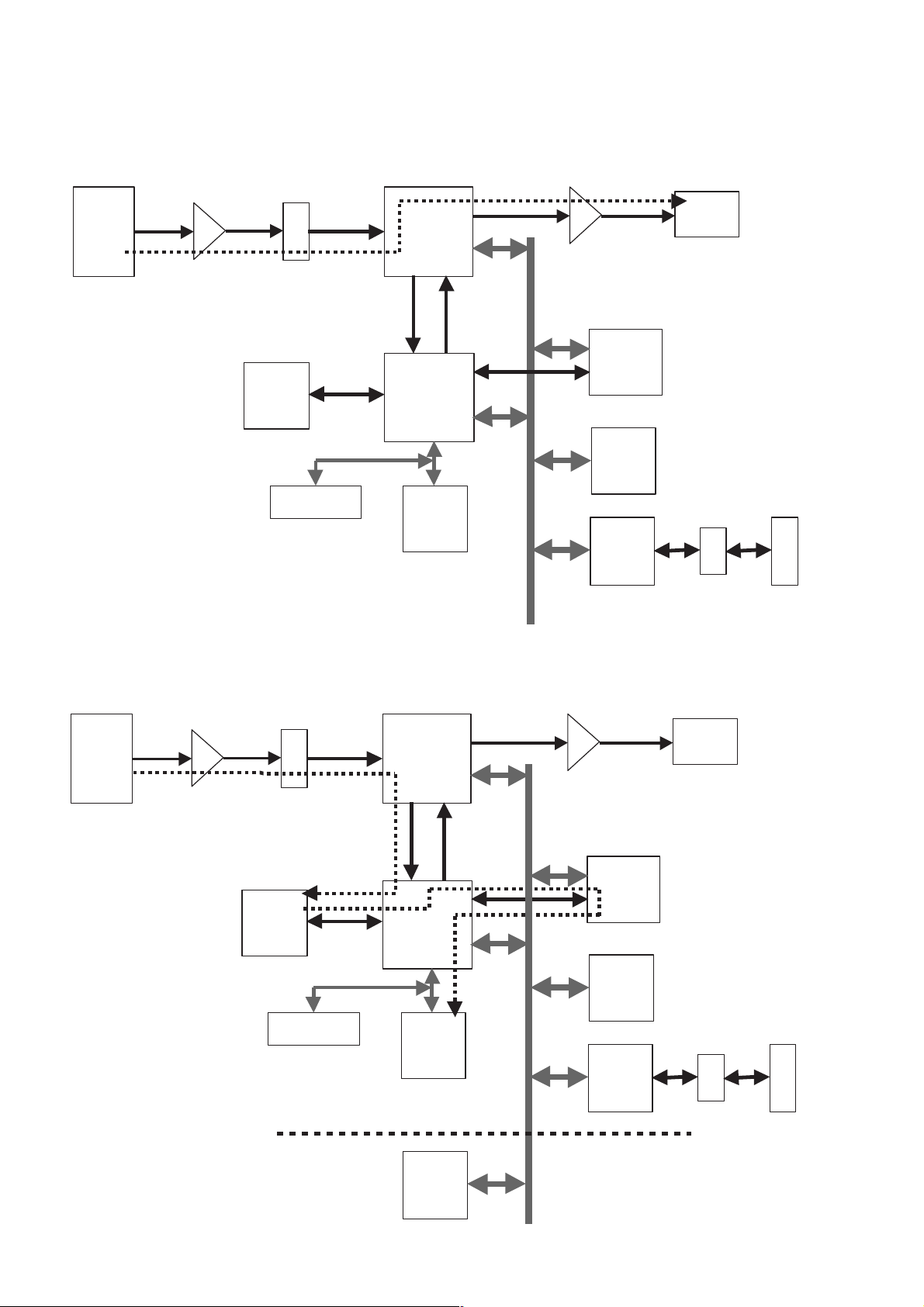

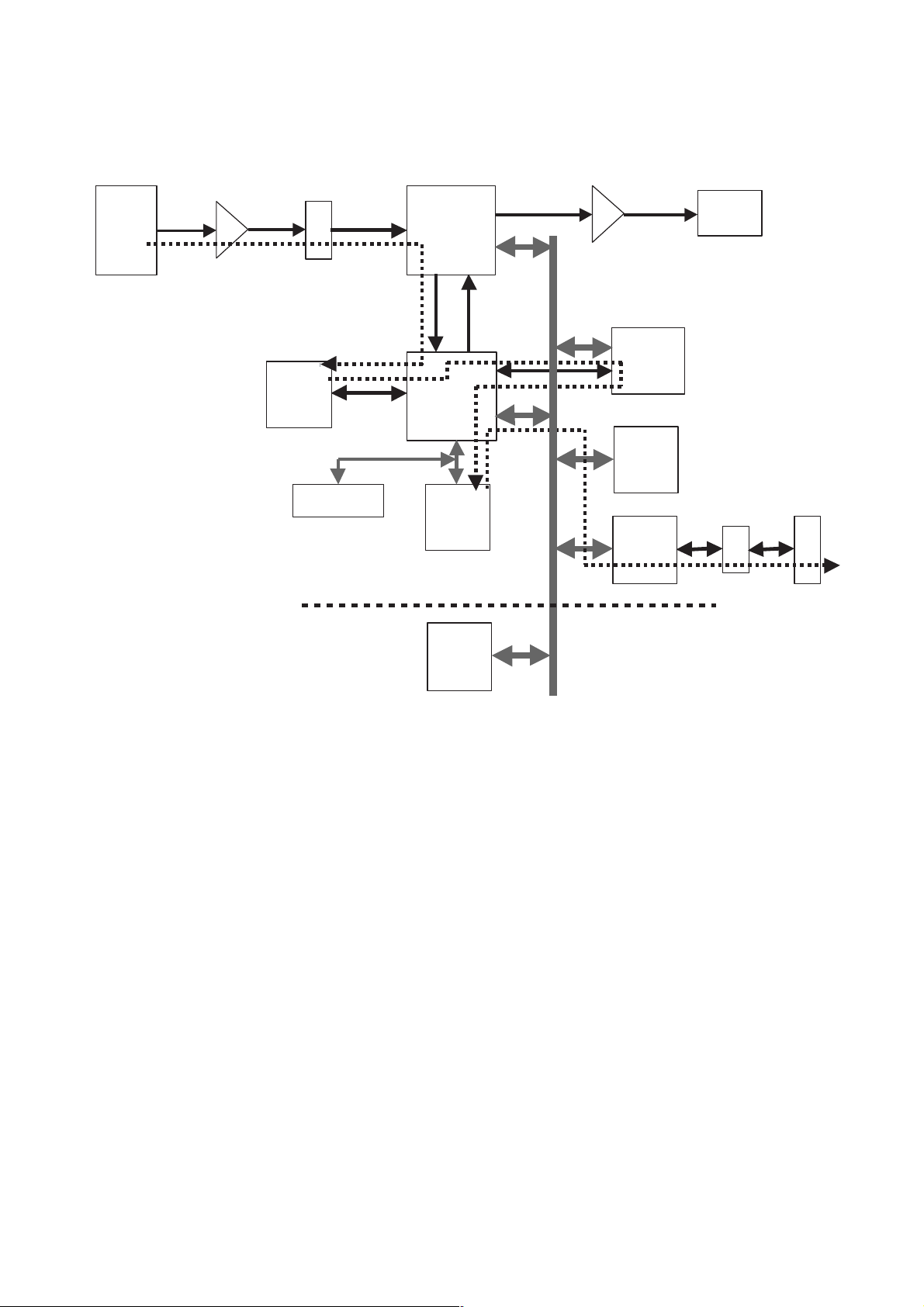

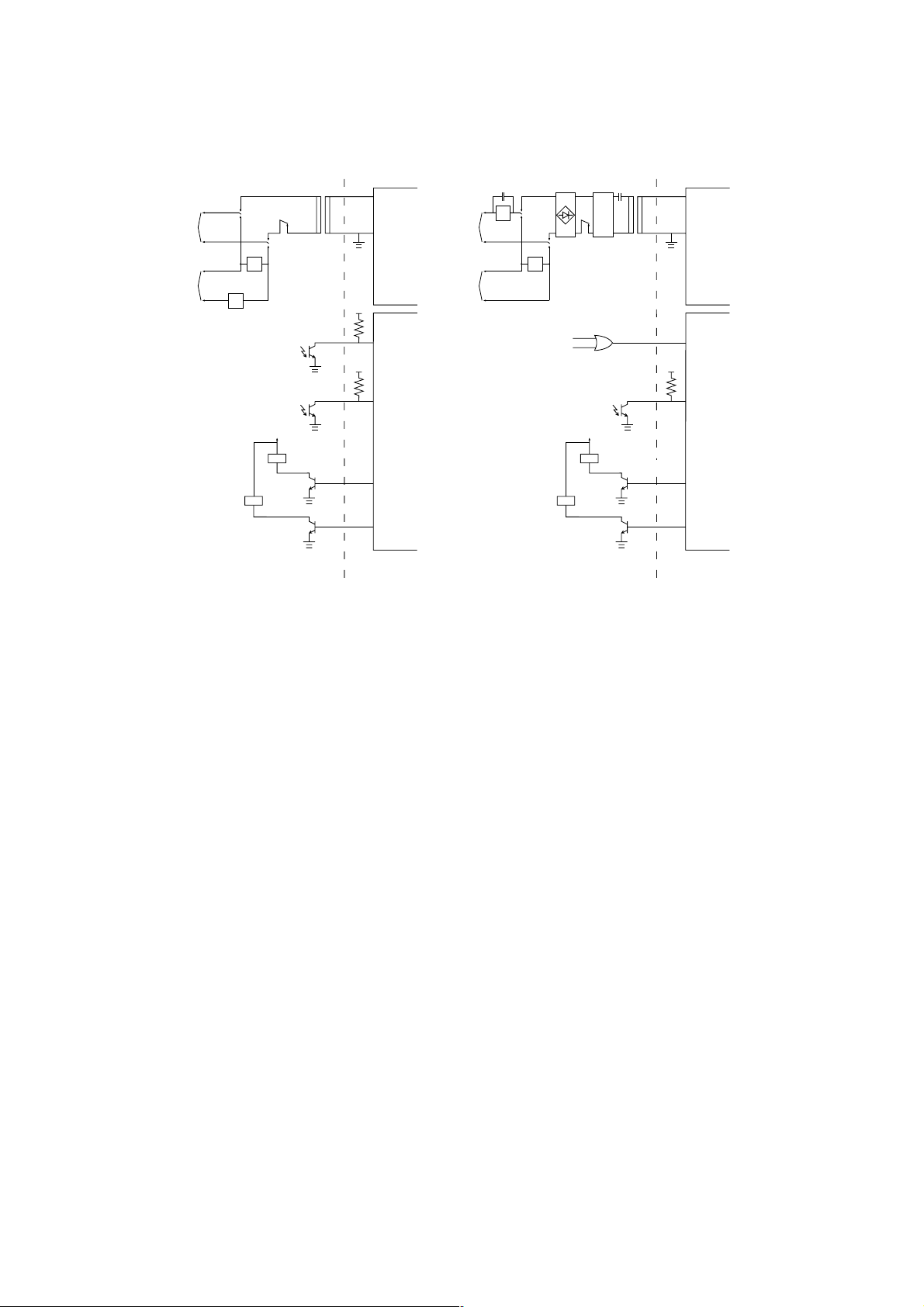

1.1.2. Image Data Circuit

The Image Data Circuit is independent of System circuit from Page Memory / Sort Memory circuit due

to high speed scanning and printing. As a result of this, all image data is managed by the Image Data

circuit and only coded data is transferred to the System Data BUS.

CCD

Amp

ADC

(IC20 ,21)

Page Memory

SDRAM

8MB

(IC27)

DRAM BORD

(CN27)

8MB

GA1

(IC7)

GA2

(IC30)

SDRAM

8MB

(IC28)

Work Memory

BUF

(IC11)

Control &

SYSTEM DMA BUS

CODEC

PM22/33

(IC32)

CPU

SH-2

(IC1)

GA3

(IC34)

LSU

BUF

(IC35)

IEEE1284 I/F

CONECTER

(CN26)

F-ROM

2 or 4 MB

5

1.Memory Control Gate Array

GA2 (IC30) is a Memory Controlling Gate Array.

•DMA Control

It is used to transfer data between the following devices.

Scanning Control LSI (GA1)

Page Memory (S-DRAM)

CODEC (PM22)

Page Memory (S-DRAM)

System Memory (S-DRAM)

Page Memory (S-DRAM) : Scanning Route

CODEC (PM22) : Coding Route

Page Memory (S-DRAM) : Decoding Route

LSU Unit : Recording Route

Page Memory (S-DRAM) : Report Route

•Rotation Management

The rotation is carried out by the hardware when transferring the route.

•S-DRAM Control

It generates S-DRAM Control Signal for Page memory and Refresh Control when the power is ON.

It does not backup the Page Memory.

•Picture Quality Correction Circuit (Smoothing)

When the receiving data (8 dot/mm x 3.85, 7.7, 15.4 line/mm) is converted to 600 dpi x 600 dpi

resolution, the current printed data and 15 surrounding printed data are sent to the Smoothing ROM

through 16 bit line and the ROM sends smoothed dot data. As a result of this operation, the distorted

curved lines are smoothed.

•Gray-Level Enhancement

This control function allows expressing higher-level scales than using a recorded signal, by reducing

line density into 1/2 or 1/3 on the original after binary-to-multiple value conversion. This capability

increases reproduction of grayscale images such as photographs.

•Reduction / Enlargement Control Circuit

This circuit is used to process the received data so that it fits on the recording paper, according to

the Fax Parameter Settings.

•Synchronization Control Circuit

This circuit is used to synchronize the output of the recorded data with the horizontal synchronizing

output signal from the printer for each line. It controls the resolution of the printer as follows.

16 dot/mm x 15.4 line/mm : Report data

600 dpi x 600 dpi : Copy & Printer Interface

6

•FIFO/S-RAM Control

Picture Edit Coding Gate Array uses FIFO for Smoothing & Laser pulse width control, and S-RAM

for Smoothing Data and interface controls.

•S-DRAM Control

It generates S-DRAM Control Signal for SORT Memory and Refresh Control when the power is ON.

It does not backup the Page Memory.

2.Optional Memory for Image Side

The Optional Memories are:

•Memory PC Board (SODIMM) → DRAM Card (16 MB) for Sort memory

Install the DRAM Card for Sort memory to CN11 (FX/FP Model)/CN27 (A/PA Model) on the SORT

PCB.

7

1.1.3. Fax System Control Circuit

The System Control Block consists of the following IC that control the general Fax functions.

1.System CPU

The System CPU (SH7041) is a 32-bit RISC (Reduced Instruction Set Computer) type of CPU and

DMA Control, Serial Communication Port, Timer Control, Interrupt Control, DRAM Control, and I/O

Port are integrated into 1 chip. Mask ROM (64k byte) is already installed and it controls the Monitor ,

High Speed managing Task and Boot Programming.

•DMA Control

It has a 4ch DMA Control and is used to transfer data between the following devices.

Communication CODEC (PM22) ←→ Image Data Memory (DRAM)

•Serial Communication Port

It has a 2ch Serial Communication Port and is used to interface the following devices.

CPU ←→ Sub-CPU (Energy Saving Microprocessor)

•Timer Control

It is used to program the standard timer.

•Interrupt Control

It controls receipt & transfer to CPU the interrupt from Modem, LSI, Option, etc.

•DRAM Control

It generates DRAM Control Signal and Refresh Control when the power is ON.

•I/O Port

It is used to control lines and reset control around LSI.

2.System Memory

This system consists of the following memory.

•F-ROM (IC) → F-ROM (2MB) for programming

•F-ROM (IC) → F-ROM (2MB) for programming

The program is booted from F-ROM Card.

•F-ROM (IC) → Image Data Memory (2MB)

During a blackout, the image data is backed up.

•DRAM (IC) → Work RAM, buffer (8MB) for transfer and reception

3.Optional Memory for System Side

The Option Memories are:

•F-ROM Card (2/4MB) → Image Data Memory for expansion

During a blackout, the image data is backed up.

It is possible to rewrite the program by rebooting the main program from this card.

8

1.1.4. Scanning Circuit

1.Scanning LSI

GA1 (IC7) is a Scanning LSI and generates Shading Correction, MTF Correction, Reduction/

Enlargement, and Gray Scale Error Diffusion. The Image Signal is converted to binary signal and

transported.

2.TX Motor Drive Circuit

TX Motor Drive Circuit is controlled by SLA7032M and SCN PCB IC19, ADF PCB IC15.

1.1.5. Coding

Coding and decoding (MH/MR/MMR/JBIG conversion) is carried out by the hardware codec device.

There are 2 codecs, Image Codec and Communication Codec.

•PM-22 (IC32) : for Image Codec

It codes or decodes the data transferred from Sort memory. When copying, this codec codes from

the Image data to JBIG data. When communicating, this codec codes from Image data to MMR

data.

1.1.6. Sleep Mode

This function reduces the power consumption in standby mode. During Sleep Mode, power is supplied

only to the Energy Saver Lamp to keep it at a steady ON condition, to the circuit that monitors incoming

Ringing signals and to circuits that maintain Deferred communications. The power is recovered only

when an incoming Ringing signal is detected, the time to perform a Deferred communication has

lapsed or the Energy Saver key is pressed.

Recovers from Sleep Mode

No. Item Recovers from Remark

Sleep Mode

1 When Energy Saver key is pressed Yes

2 Deferred Communication time is lapsed Yes

3 Time for Deferred Communication Yes

4 Original Sensor is actuated Yes

5 Ringing signal detected Yes Not 1300Hz detection

6 Off-Hook (External telephone or Handset) Yes

7 When printing from a PC Yes

Not Document Sensor with Flatbed

9

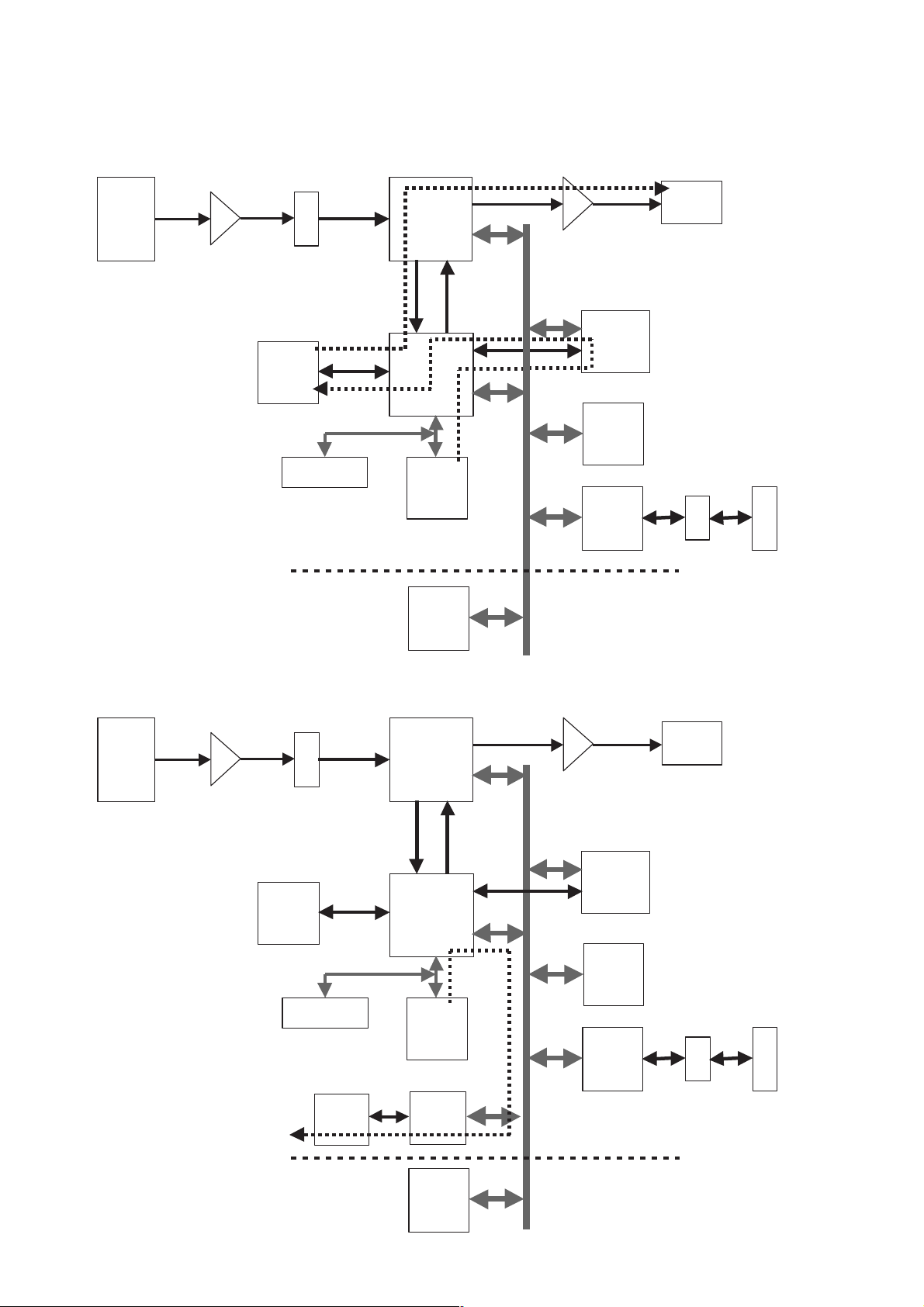

1.1.7. Signal Routing

1.Copy

Amp

CCD

(IC20,21)

ADC

GA1

(IC7)

BUF

(IC11)

LSU

Control &

SYSTEM DMA BUS

CODEC

Page Memory

SDRAM

8MB

(IC27)

2.Scan into Memory (FAX)

Amp

CCD

DRAM BORD

8MB

(CN27)

ADC

(IC20 ,21)

GA2

(IC30)

SDRAM

8MB

(IC28)

Work Memory

GA1

(IC7)

PM22/33

(IC32)

CPU

SH-2

(IC1)

GA3

(IC34)

BUF

(IC11)

Control &

SYSTEM DMA BUS

BUF

(IC35)

IEEE1284 I/F

LSU

CONECTER

(CN26)

Page Memory

SDRAM

8MB

(IC27)

DRAM BORD

8MB

(CN27)

GA2

(IC30)

SDRAM

8MB

(IC28)

Work Memory

F-ROM

2 or 4 MB

10

CODEC

PM22/33

(IC32)

CPU

SH-2

(IC1)

GA3

(IC34)

BUF

(IC35)

IEEE1284 I/F

CONECTER

(CN26)

3.File Print from Memory (FAX)

ADC

Amp

CCD

(IC20,21)

GA1

(IC7)

BUF

(IC11)

LSU

Control &

SYSTEM DMA BUS

CODEC

Page Memory

SDRAM

4.Memory Transmission

Amp

CCD

8MB

(IC27)

DRAM BORD

8MB

(CN27)

ADC

(IC20,21)

GA2

(IC30)

SDRAM

8MB

(IC28)

Work Memory

F-ROM

2 or 4 MB

GA1

(IC7)

BUF

(IC11)

PM22/33

(IC32)

CPU

SH-2

(IC1)

GA3

(IC34)

BUF

(IC35)

IEEE1284 I/F

LSU

CONECTER

(CN26)

Page Memory

SDRAM

8MB

(IC27)

DRAM BORD

(CN27)

8MB

NCU

GA2

(IC30)

SDRAM

8MB

(IC28)

Work Memory

MODEM

F-ROM

2 or 4 MB

Control &

SYSTEM DMA BUS

CODEC

PM22/33

(IC32)

CPU

SH-2

(IC1)

GA3

(IC34)

BUF

(IC35)

IEEE1284 I/F

CONECTER

(CN26)

11

5.Memory Preception

Amp

CCD

ADC

(IC20 ,21)

GA1

(IC7)

BUF

(IC11)

LSU

Control &

SYSTEM DMA BUS

CODEC

6.Printing out

CCD

Amp

Page Memory

SDRAM

8MB

(IC27)

DRAM BORD

(CN27)

ADC

(IC20 ,21)

8MB

NCU

GA2

(IC30)

SDRAM

8MB

(IC28)

Work Memory

MODEM

GA1

(IC7)

BUF

(IC11)

PM22/33

(IC32)

CPU

SH-2

(IC1)

GA3

(IC34)

BUF

(IC35)

IEEE1284 I/F

LSU

CONECTER

(CN26)

Page Memory

SDRAM

8MB

(IC27)

DRAM BORD

(CN27)

8MB

GA2

(IC30)

SDRAM

8MB

(IC28)

Work Memory

12

Control &

SYSTEM DMA BUS

CODEC

PM22/33

(IC32)

CPU

SH-2

(IC1)

GA3

(IC34)

BUF

(IC35)

IEEE1284 I/F

CONECTER

(CN26)

7.Scaner Input

CCD

Amp

ADC

(IC20,21)

GA1

(IC7)

BUF

(IC11)

LSU

Control &

SYSTEM DMA BUS

CODEC

Page Memory

SDRAM

8MB

(IC27)

DRAM BORD

(CN27)

8MB

GA2

(IC30)

SDRAM

8MB

(IC28)

Work Memory

F-ROM

2 or 4 MB

PM22/33

(IC32)

CPU

SH-2

(IC1)

GA3

(IC34)

BUF

(IC35)

IEEE1284 I/F

CONECTER

(CN26)

13

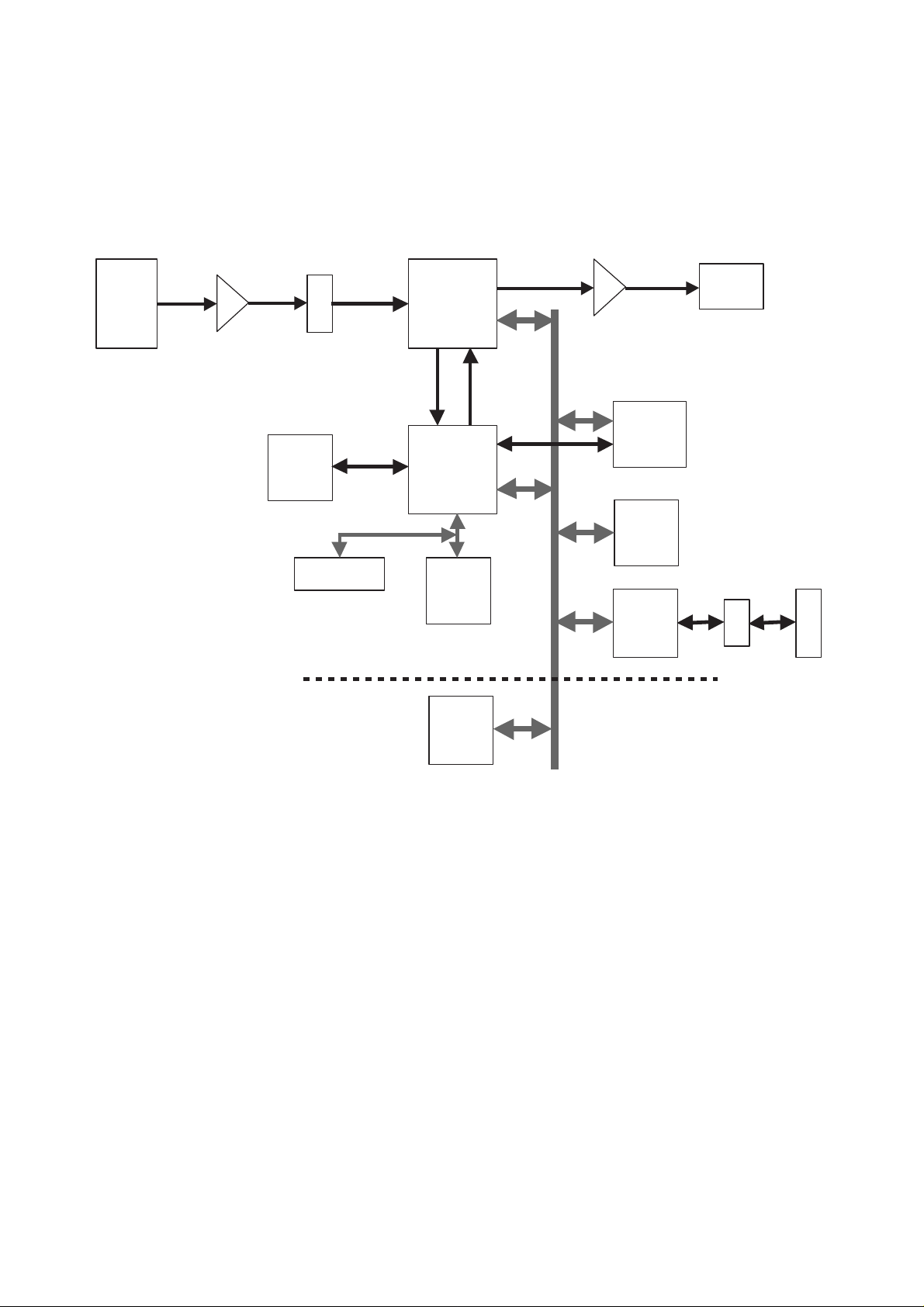

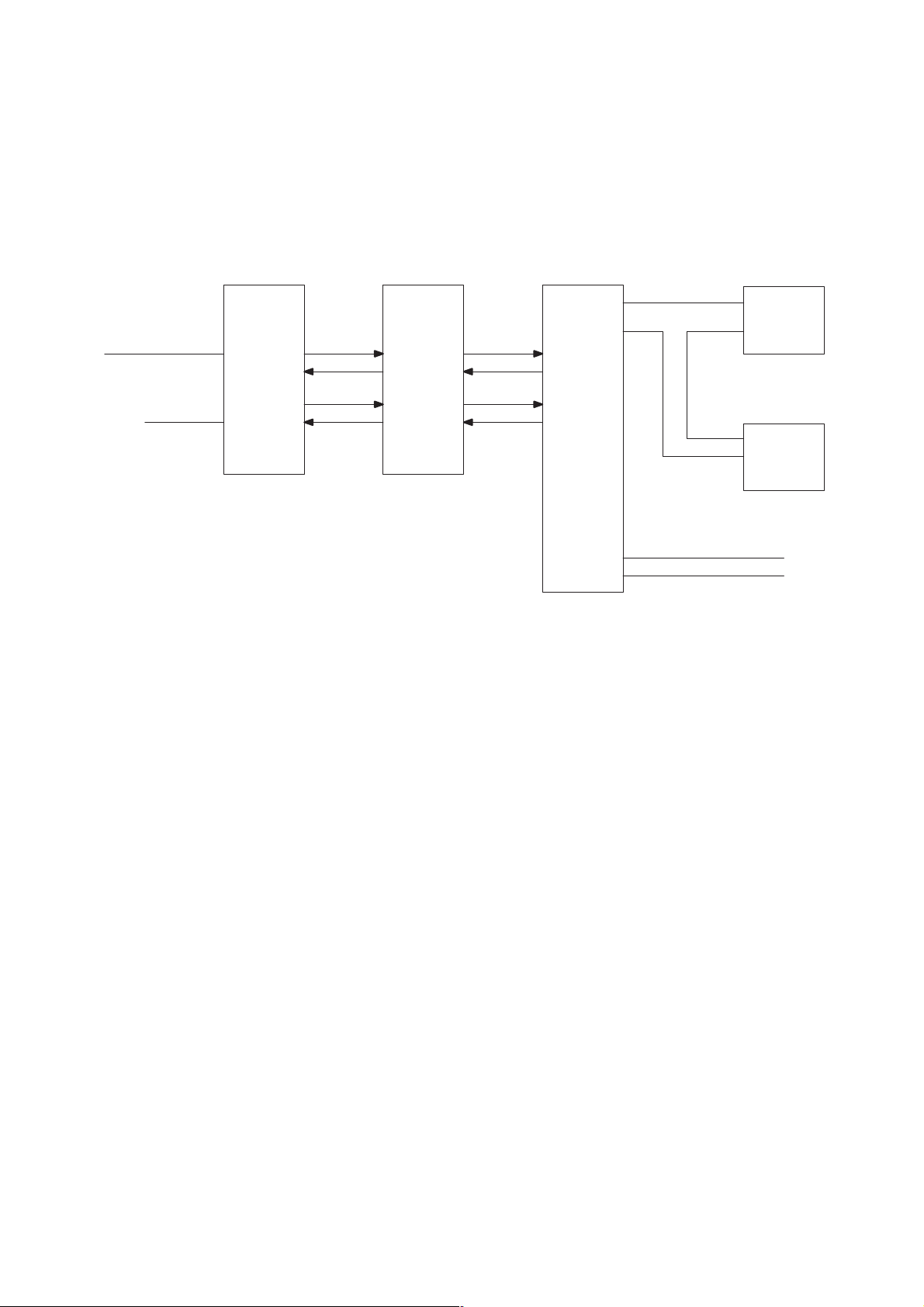

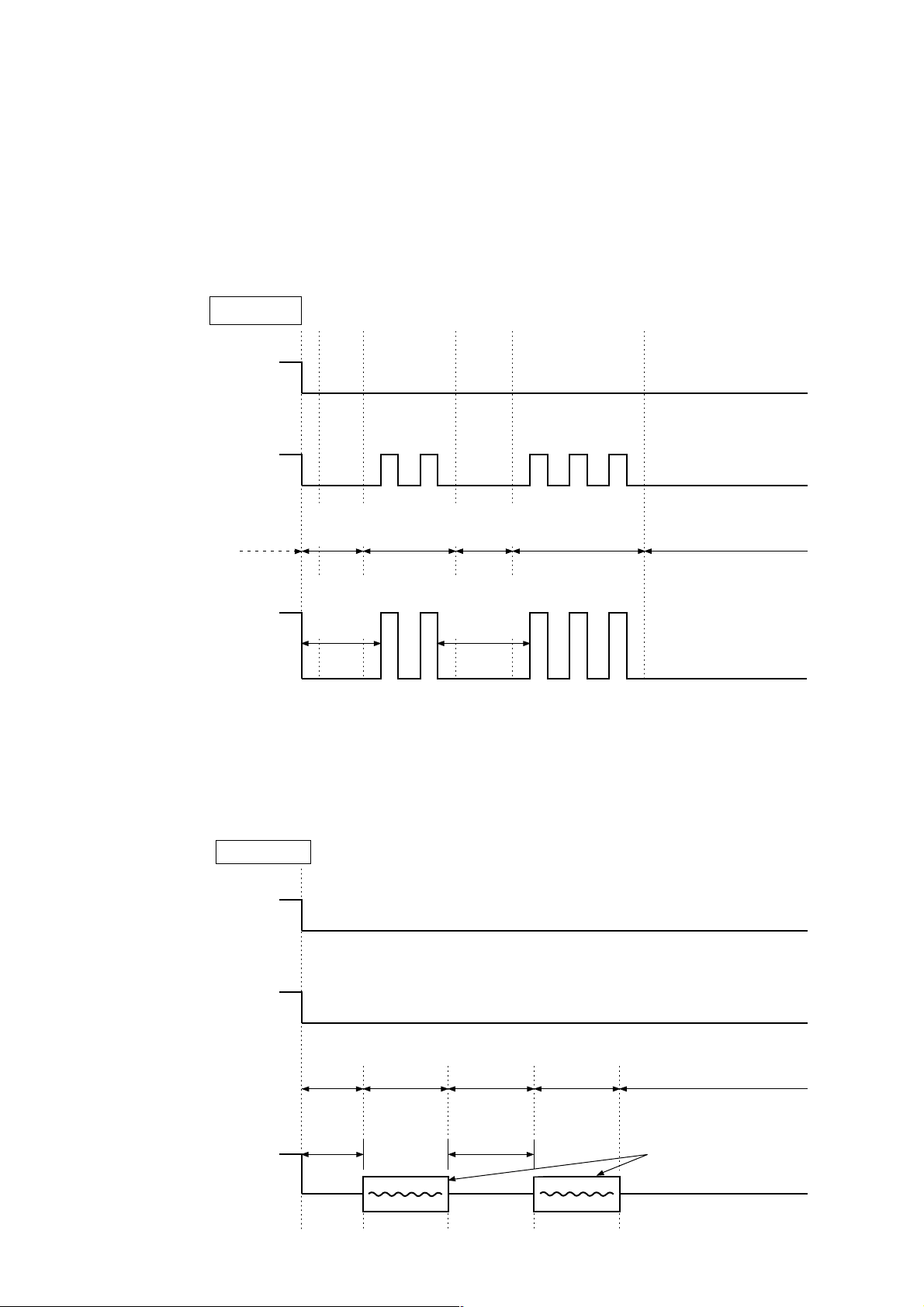

1.1.8. Modem and Peripheral Circuit (Optional FXB PCB)

This circuit consists of DSP, ROM, S-RAM, Analog Front End, Analog Master and peripheral circuitry.

This modem conforms to ITU-T, V.34, V.33, V.17, V.29, V.27ter, V.21 channel 2 (FSK), T.4, and T.30.

Macro order of DSP is sent from ROM to S-RAM and is outputted. DSP transfers/receives data from

Analog Front End and serial communication. Analog Front End communicates with the line through

Analog Master.

IC904

S-RAM

To Line

To Speaker

IC905

Analog

Master

IC906

Analog

Front

End

IC901

Modem

CPU

DSP

IC902

ROM

Modem

Program

System BUS

Modem Circuit Block Diagram

1.Receive Signal Control Circuit

This circuit consists of Operational Amplifier , Analog Master , and its peripheral circuit. On the received

signal from a line transformer (HYBSR), diffraction of signal transmission is attenuated using the

hybrid circuit, and the frequency of signal is limited to a certain band using a second LPF.

The signal is input to the analog front end via the analog SW for switching over between HYSIG and

the gain switching amplifier . 1300-Hz signal and remote signal are detected from HYSIG by switching

SW1.

2.Transmission Signal Control Circuit

This circuit consists of Operational Amplifier, Analog Master, and its peripheral circuit. On the signal

transmission from the analog front end, frequency of the signal is limited to a certain band using a

second LPF, and diffraction of the signal to a reception circuit is attenuated using the hybrid circuit.

The signal is sent out from the line transformer.

14

3.Line Monitor Circuit

The Line Monitor Circuit consists of an operational amplifier, analog master and its peripheral circuits.

Its function is to monitor the dial tone, DTMF tone, response signals, etc. over the speaker. It also

sounds the output of the key touch tones, alarm tones, etc. from the panel CPU over the speaker. The

received signal from the Ain (M) passes through an AGC circuit and is conditioned by the Analog FrontEnd DSP and is then input to the Analog SW2 for volume control. The signal is then input to the

Speaker Amplifier, where it is amplified to a level sufficient to drive the speaker. The key touch tones

and Buzzer Signals from the panel are input to the Analog SW2 for volume control and then input to the

Speaker Amplifier. The monitor tone from the phone line and the buzzer tone from the panel can be

adjusted from the Control Panel.

HYSIG

Analog Front-End DSP

Ain(M)

IC906

HYBSR

RX signal

Analog Master

Analog SW1

Speaker

TX signal

Hybrid Circuit

Amplifier

LPF Fc:7.8KHz

LPF Fc:4.5KHz

Electronic Volume

Analog SW2

Buzzer Signal from Panel

Gain Switch

Amplifier

Aout(M)

Aout(V)

AGC

15

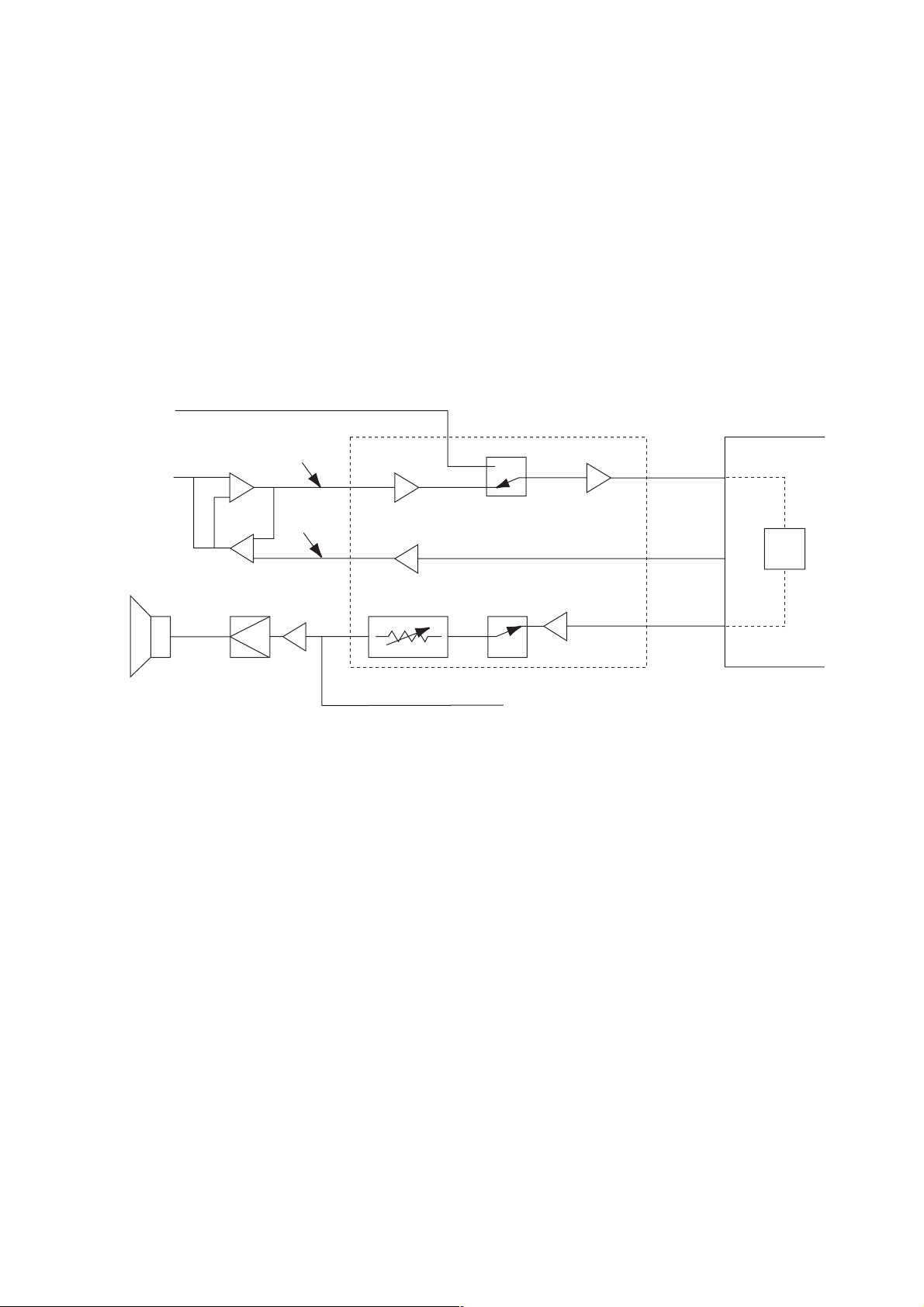

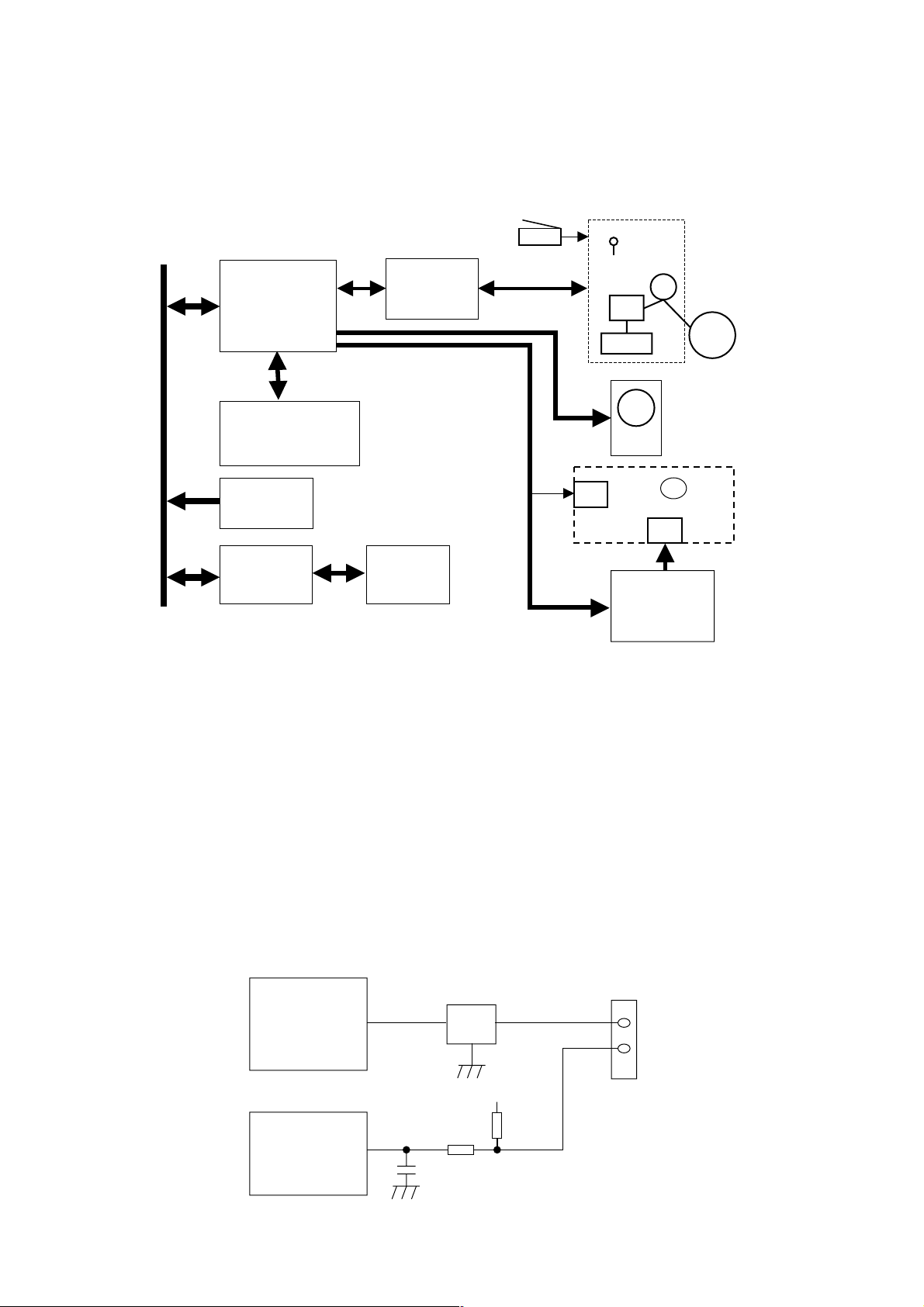

1.1.9. Line Control Board

The following shows a block diagram of the Line Control Board.

Line

Telephone

PC1

Off-Hook

Detector

CML

CML

PC2

Ring

Detector

for Auto Receive

+24V

CML

PLS

PLS

C5

T2

L : Off-Hook

H : On-Hook

nHKOFF 9

PC1

nCTON

PC2

L : Ring In 10

CMLD 5

Q1

PLSD 6

Q2

[DZYNA1435*]

HYBSR

GND

+5V

+5V

H : FAX Side

L : Telephone

H : Make

L : Break

CN7

HYBSR

CML

DC

RL4

HOLD

C5

L : Off-Hook

H : On-Hook

+24V

CML

RL4

nHKOFF 9

nCTON

L : Ring In 10

H : FAX Side

L : Telephone

pCMLD 5

H : Make

L : Break

pPLSD 6

AGND

MODEM

+5V

IC

< MDM >< LCE >

CML

IC1

Line

MODEM

PC1

Ring

Detector

IC

< MDM >< LCU >

[DZEP000441]

The Ring Detector consists of a photocoupler, PC2 (PC1 for LCE), and its peripheral circuits. The

ringing signal is a half-wave rectifier in the Ring Detector, and transferred through the nCTON signal

line to the IC on the SC PC Board. The IC observes the signal to distinguish from signals caused by

chattering.

The Off-Hook Detector (External Telephone) circuit consists of the photocoupler , PC1 (IC1 for LCE),

and its peripheral circuits. When PC1 detects loop current flow, it emits a Low active output signal

(nHKOF) to the IC which monitors it for a specified time. If the IC detects no change in the Low signal

level, it determines that the External Telephone is Off-Hook.

16

Dial Pulse Generator

The circuit consists of the CML relay, PLS relay and their peripheral circuits. This circuit generates

dial pulses. The CPU PC Board controls all dial pulse generation sequences. It turns relay CML and

PLS ON and OFF through the DZZSP58025. The status of the relays during dialing is shown below.

When the absence of the terminating message is confirmed by the Off-Hook detector , the CPU turns

CML relay ON to develop loop status (DC loop). After a few seconds, the CPU turns the PLS relay

On and Off to generate dial pulses, making and breaking the loop.

Dial Pulse

CML Relay

break

make

break

PLS Relay

make

Speech

condition

First

digit

Speech

condition

Second

digit

Speech

condition

Line release

break

Prepause

Line status

make

Inter-digit

pause

DTMF Tone Generator

The circuit is incorporated in the MODEM PC Board. The DTMF tone is conveyed to the telephone

line using the same route as the facsimile signal. The DTMF tone selection is controlled by the CPU.

The relay status during dialing is shown below.

PLS Relay

CML Relay

Line release

Line status

DTMF Tone

break

make

break

make

break

make

Speech

condition

Prepause

First

digit

Speech

condition

Inter-digit

pause

17

Second

digit

Speech

condition

DTMF signal

1.1.10. Laser Printer Motor Drive Circuit

1.System Description

It consists of 16 bit CPU TMP86CH06U, FROM for programming, peripheral I/O. The CPU controls

mechanism of Laser Printer, Fuser Lamp temperature, and Laser Unit.

IC1

CPU

SH2

SH7041

Processor

IC24

CPU

TMP86CH06U

FROM

IC2,42

GA3

IEEE1284

IC34 IC35

1284

IF

GA1

IC7

LDSW

TH

5VLD

LSU

PM

LD

APC

MM

Motor

Fuser Lamp

TS

LVPS

Drum

2.Printer Motor Drive Circuit

This Printer Motor is a Brushless DC Motor.

nMMCNT : When the signal level goes Low, the Printer Motor starts rotating.

nMMLCK : Rotation status signal for Printer Motor. When the Printer Motor reaches a constant

speed, nMMRDY signal level goes Low.

The Printer Motor is powered by +24 VDC supply. When the interlocks are open, the +24 VDC

supply is cut off and the Printer Motor stops rotating.

IC1

CPU

SH2

SH7041

Processor

GA1

IC7

111

144

DT6

nMMCNT

5V

CN7

2

1

nMMLCK

18

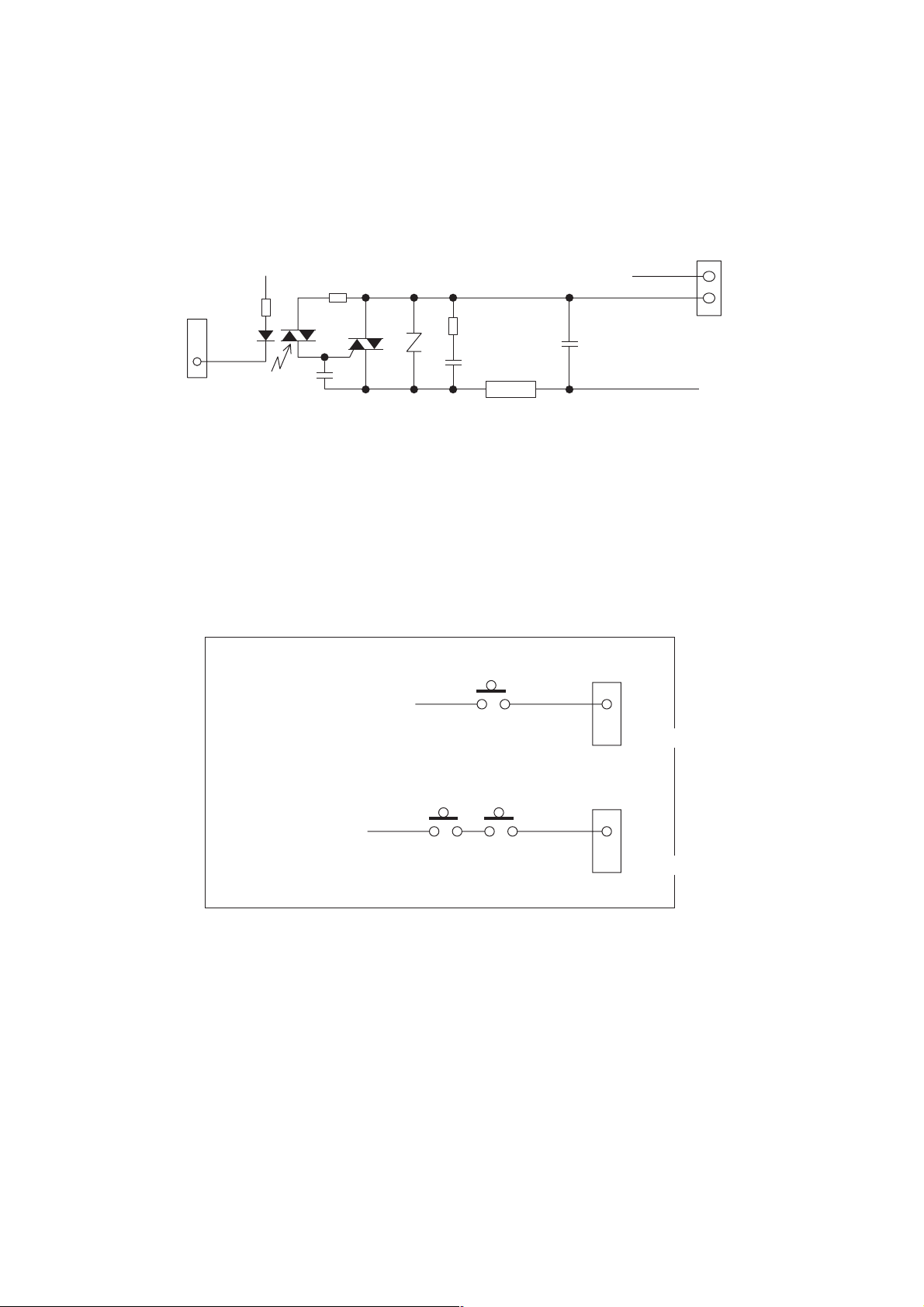

3.Fuser Lamp Drive Circuit

It consists of 1 Fuser Lamps and Fuser Lamp is controlled by two HTC PC Boards.

The Fuser Lamp is powered by 100 VAC. When the CN7, Pin 4 (HTCNT) on the LVPS PCB goes

LOW, the Fuser Lamp turns ON. This lights up the PC5 LED and activates the TR1 photo-triac, and

100 VAC is sent to the Fuser Lamp.

CN3

to CPU

Board

CN7

4

5V

AC1

L4

PC5

TR1

1

to Fuser Lamp

2

AC2

4.Interlock Safety Circuit

This safety circuit turns OFF the +24 VDC and +5 VDC supply voltages when the Printer Cover is

opened. When the Printer Cover is opened, the microswitch(es) on the LVPS Board are de-actuated, turning OFF +24 VDC to the Printer Motor Drive Circuit, the HVPS, the Paper Feed Solenoid

Circuits, the Clutch Drive Circuit, and the Laser Driver Circuit on the Laser Unit.

LVPS

SW3

SW2

SW4

24V

5V

CN5

1

to CPU PC board

CN6

1

to CPU PC board

19

5.LSU Control Circuit

The laser control signals are described below.

Actual data is sent from CPU PCB to LSU.

nVIDEO : Actual data is outputted by these 2 signals.

ADJUST : Laser Power Sample/Hold Timing Signal.

nHSYNC : This horizontal synchronization signal transmitted from the Beam Detection Sensor

sets the horizontal position of the laser beam as it crosses the OPC Drum.

ENABLE : The LSU is activated when this output signal is LOW. If an error occurs, the nLDON

output signal level goes High and the LSU is deactivated.

PMCLK : This is the Polygon Motor Drive Clock.

nPMLCK : When the Polygon Motor speed is constant, the nPMRDY is at a Low output signal

level.

nPMCNT : This is the Polygon Motor Control Signal. The Polygon Motor rotates when the nPMON

output signal level is LOW.

IC1

CPU

SH2

SH7041

Processor

GA1

IC7

143

90

113

DT5

DT22

IC11

5V

nPMCNT

PMCLK

nPMLCK

ENABLE

nVIDEO

ADJUST

CN4

11

13

12

5

6

7

IC13

20

nHSYNC

4

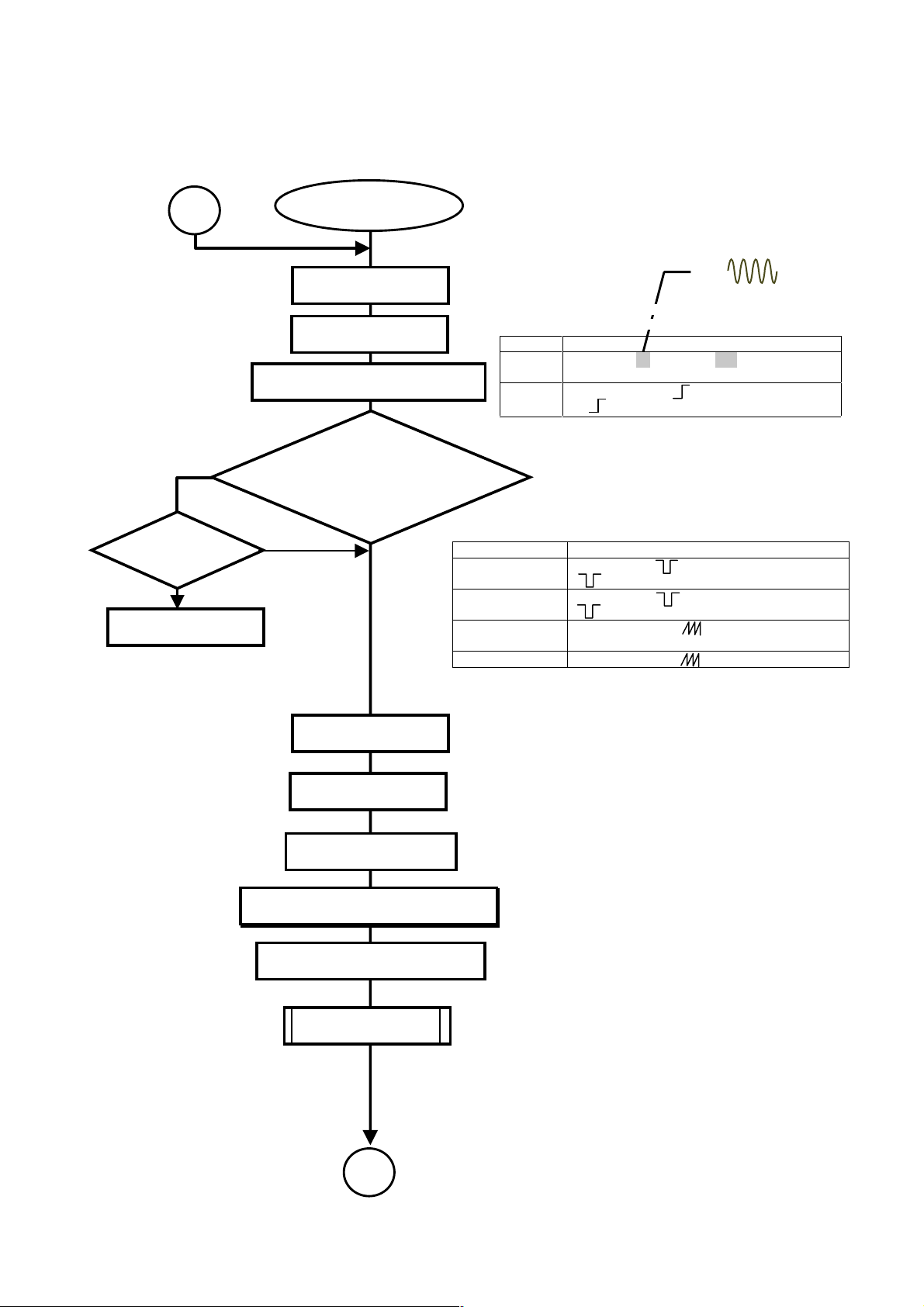

1.2. Power On Initial Flow Chart

1.2.1. Fax

0

Boot Program in CPU Start

Initial Flow

Power ON

Hardware Reset

* Check outside view of SC PCB before checking signal.

Especially check whether CN903 (FROM Card) pins

short or not.

XTAL

3.5V

0V

<Check Output : If Signal is not correct, each IC

Power CN13(12,13)5V -> CPU

Master

Clock

Reset ResetIC5(8) -> -> (173)

might be defective >

7.16Hz -> (94)IC1CPU( 107)28.3MHz

-> BL108

-> ->(108)IC1CPU

Y

Is program date

Same?

N

Update Program

Is Update Memory Card

Installed IC2(14) is Low ?

Y

N

API IC2(14) : Low / High

CPU(CS0)

CPU (RD)

CPU(A1-3)

CPU(D0-16) IC1CPU(D0-16) -> IC2(33,35,38-)

CPU I/O Port Set

I/O Device Reset

I/O Device Port Set

System Program (FROM) Start

System Program (FROM) Start

<Check Output : If Signal is not correct, each IC

might be defective >

IC1CPU(50) -> IC7(150)

-> (2) IC2(14)

IC1CPU(43) -> IC5

-> IC2(54)

(A0~20)IC7(7~39) -> MSC(14,

16,17) -> IC2(4~32)

DRAM Working Area Clear

Panel Initial

1

21

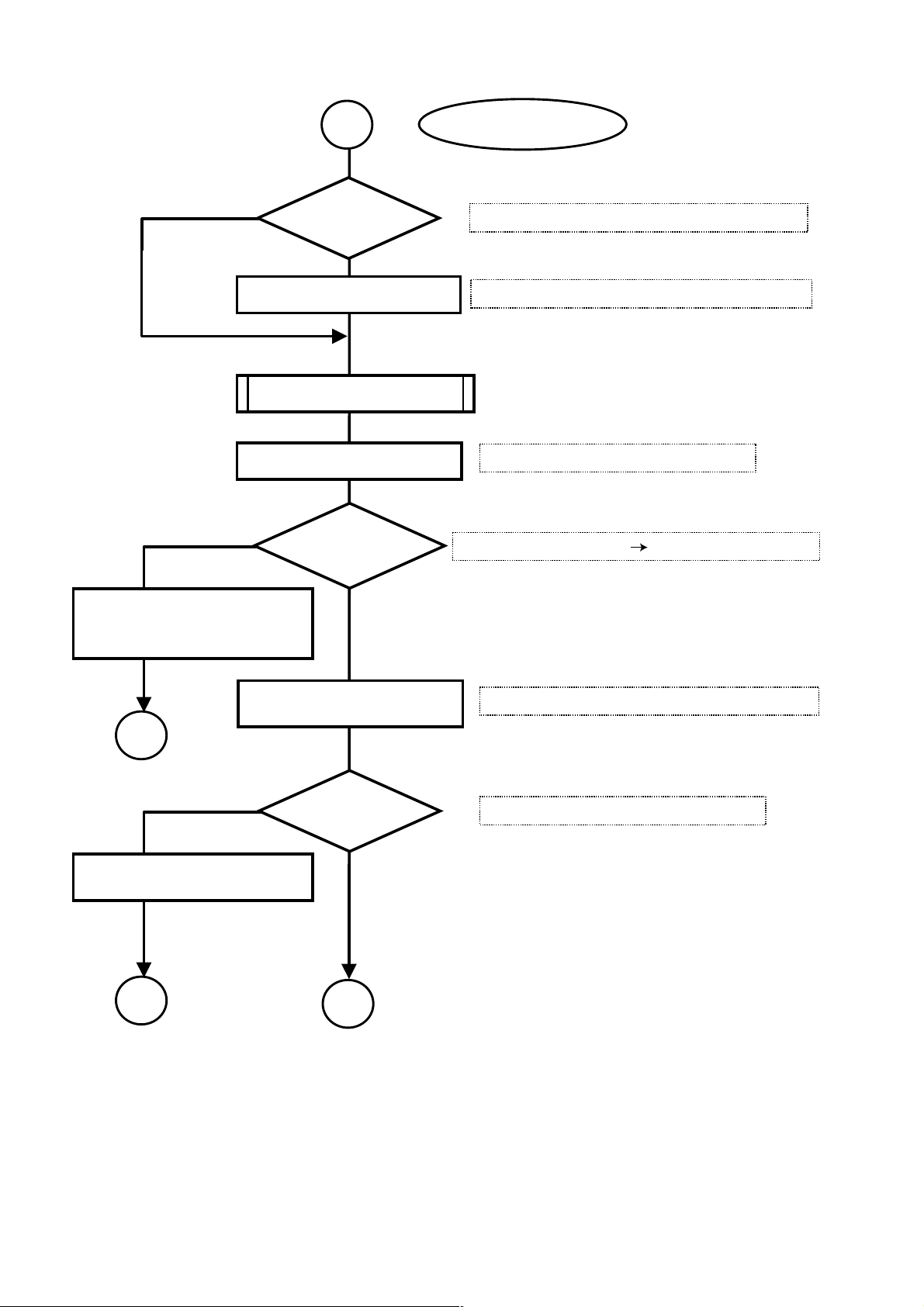

1

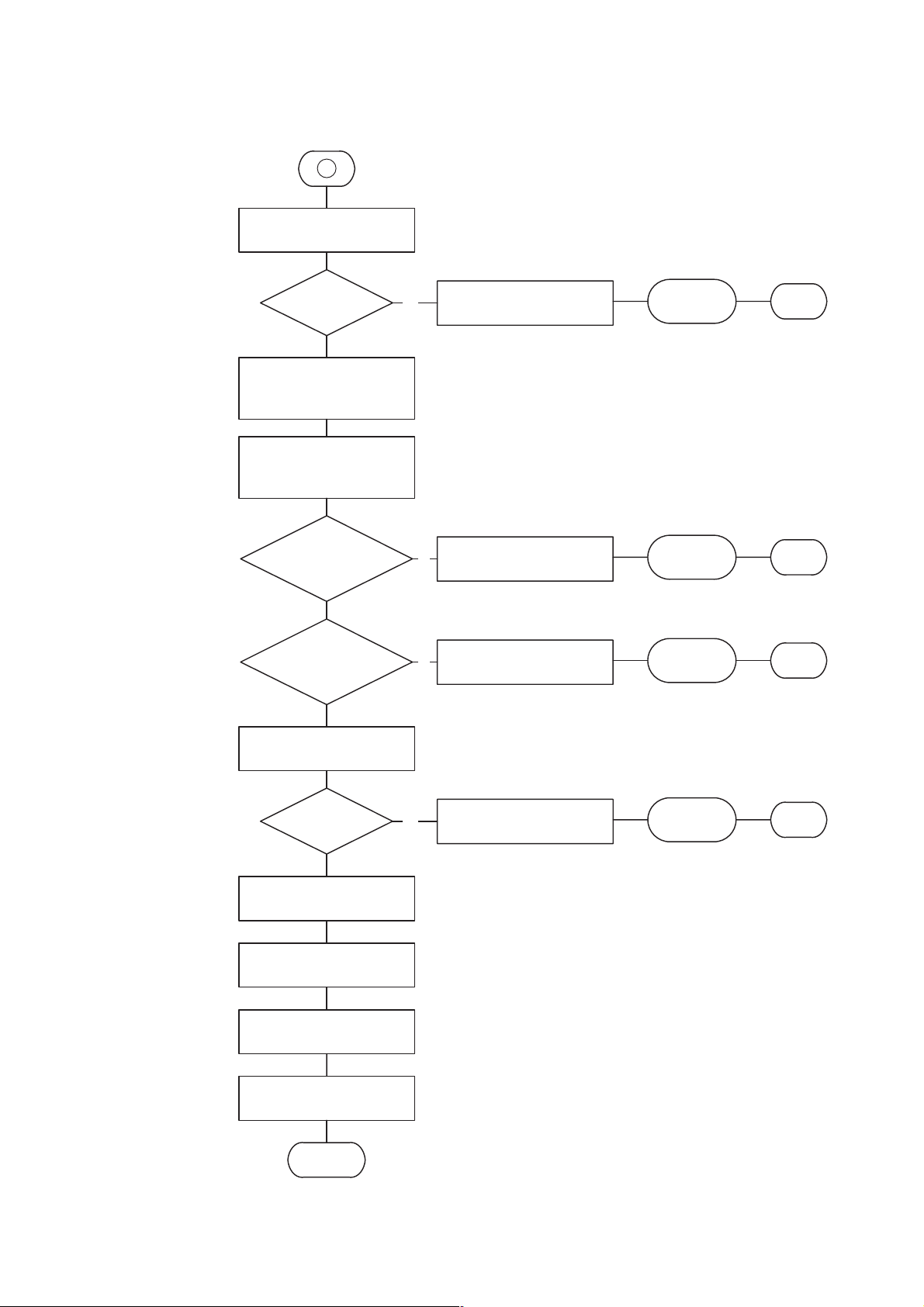

Initial Flow 2

Y

FROM (Image area) initial

Y

Shipment set

System data save to F-ROM

F-ROM image area format

FROM IC1

formated ?

N

PRINTER initial

Task Initialize

Back up data

PARITY ERROR ?

N

In case of replaced FROM on FXB PCB

It may take 15 - 20 sec. During formatting.

Task initialize for Software.

Back up data in SRAM Parameter, Journal,...

(F-ROM Card) Check

0

Y

F-ROM image area format

(New size)

0

Image memory

Memory size

change?

N

2

Confirmation of FROM Memory Card size.

Optional FROM Memory Card

22

2

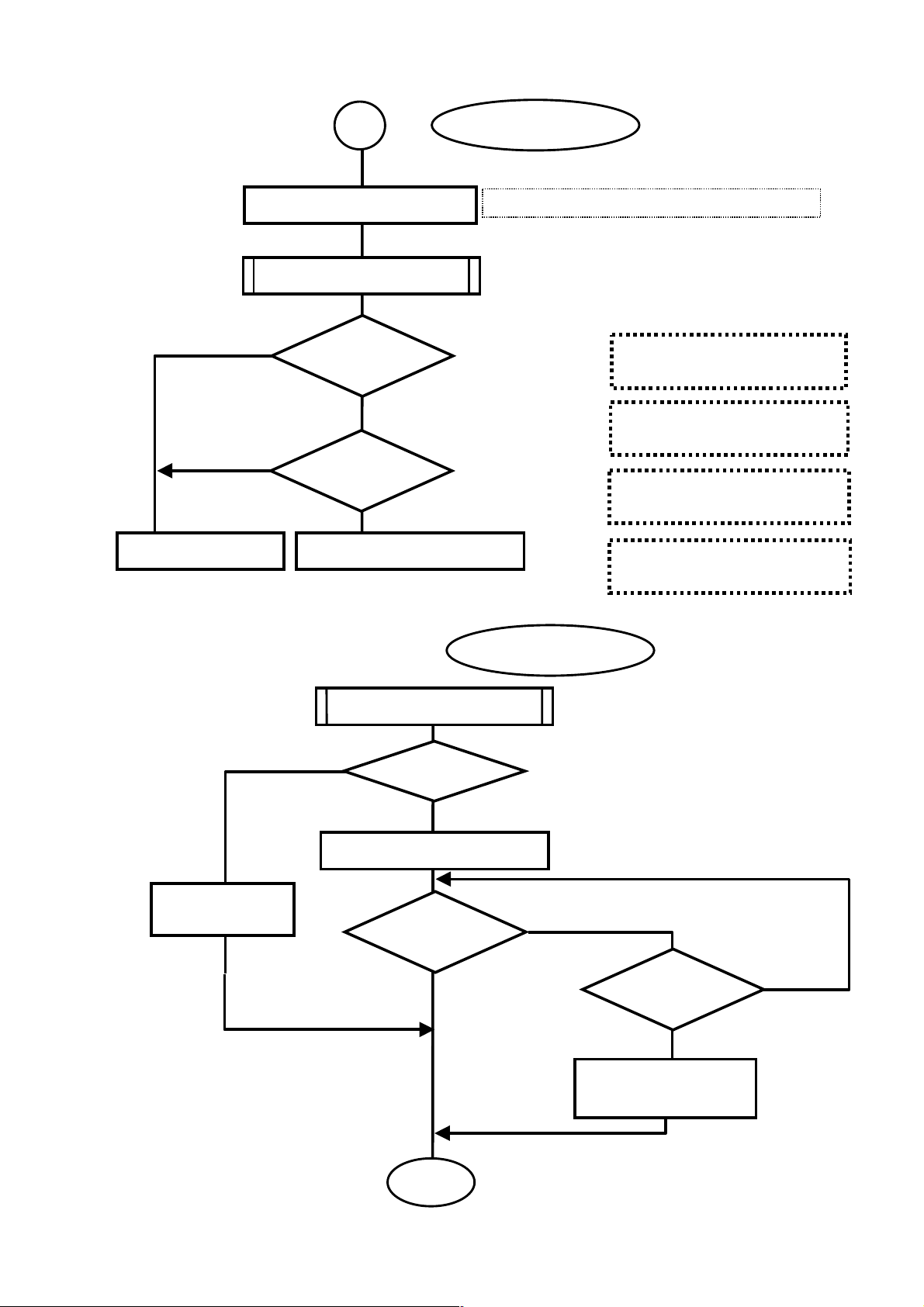

Initial Flow 3

JOB Recover, if need

SCANNER initial

Y

PRINTER error ?

N

Y

SCANNER error ?

N

DISPLAY ERROR DISPLAY DATE & TIME

Confirmation of timer, Po wer OFF/ON,…..

APR-22-2000 10:00

EX.

EX.

EX.

CHECK PRINTER

E04

DOCUMENT JAM

J31

ADF COVER OPEN

J61

Initial Flow 4

00%

Error Set

Info. Code 061

SCANNER initial

Y

ADF Door

EJECT START

B Point OFF ?

OPEN ?

N

Y

N

Jam Length

Over ?

Y

Error (Jam) Set

Info. Code 031

N

END

23

1.2.2. Printer Initial Flow Chart

SC Initial End

Hard Reset

Start Watching I/O Port

IC7

Pin109

N

IC7

Pin115

H

IC1

Pin54

H

IC1(53)

H

IC1(52)

L

B

Y

L

L

L

Right Cover Open

Regist Sensor ON

Exit Sensor ON

2nd Paper Pass Sensor ON

Feed Cover Open

STOP

STOP

STOP

STOP

When the optional

2nd Feed Module

H

2nd Paper Detecting Sensor ON

2nd Paper Tray Open

STOP

is installed.

24

B

Main Motor On

IC1(144)

IC7(111)

L

Internal Process of

High Voltage ON

IC7-Pin85, 89

Fuser Heat-up

(Lamps ON)

IC7(83)

IC1(118)

Vin < 0.016V

N

IC1(118)

Vin increase

under 0.016V

H: ON

L: OFF

H

Y

Y

Main Motor

Rotation Defect

Thermistor Open

Abnormal Temperature

Service

Error

Service

Error

Service

Error

STOP

STOP

STOP

N

Main Motor On

IC1 Pin144

IC7

Pin112

L

Internal Process of

High Voltage OFF

Motor OFF

Fuser Idle

(Lamps OFF)

Fan Motor OFF

(Watching during Initial Operation)

L: Stop

H: High Speed

H

Fan not Ready

Service

Error

STOP

Stand-by

25

2 Schematic Diagram

2.1. General Circuit Diagram System Circuit

1234

IMPORTANT SAFETY NOTICE

THE PARTS WITH MARK ON THIS SCHEMATIC

DIAGRAM INCORPORATE SPECIAL FEATURES

.....AC120V/220–240V Line

.....DC24V Line

.....DC5V Line

A

B

C

Control Panel PCB

14

13

12

11

10

9

8

7

6

5

4

3

2

1

CN401

14

13

12

11

10

9

8

7

6

5

4

3

2

1

D

IMPORTANT FOR SAFETY

WHEN SERVICING IT IS ESSENTIAL THAT ONLY

MANUFACTURE'S SPECIFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE PARTS WITH

MARK OF THE SCHEMATIC.

CCD PCB

CN 801

EPLED

EPKEY

VL

GND

KCLK

CPWR

CPLAT

CPLD

LCLK

CPKEY

CPDAT

123456789

Flat

Cable

201918

AGND

CN12

CN2

LMBB

CN6

12345

11

Optics Drive Motor

17

16

AGND

VOUTO

VOUTE

AGND

Pulse

LMB

SVP

LMAB

SVP

9

753

M

151413

CCDADT

LMA

6

1

CCDACLK

CCDALD

1516171819

111213

14

10

9

7

8

6

10

11

12

SH

GND

RS1

RS2

FCK

GND

SCK

50

50

VL

VL

HPSN

GND

PCSN

CN5

7

3

6

5

4

2

3

1

PCSN

HPSN

Platen/ADF

Open/Close Sensor

Lamp Unit Home

For DP-150A/PA/FP/FX, DP-130FP

543

VL

GND

GND

2

1

321

Position Sensor

20

2

1

-12V

+12V

AGND

24 0

PVP

HFSOL

CN3

987654321

10

1

2

Bypass Solenoid

24 0

PVP

RRSOL

PUSOL

PVP

2

1

2

1

Registration

Pick-up Solenoid

EXFM

EXFL

123

Solenoid

Inverter PCB

PGND

FM

Exhust Fan Motor

Flat Cable

CN16

1

CN2

123

PGND

23445

2

3

1

4

PGND

SVP

LPCNT

24 0

Detect

HFPS1

CN17

123

1

Bypass Paper Size

Detecting Switch

Exposure Lamp

CN1

123

VL

CN15

TXD1OUT

Detect

GND

GND

HFPS2

4

MS

MS

2

1

3

AC1

AC2

S1

CN 8

HVPS

701

N

C

987654321

10

4

1234567

CN8

VREF

TREF

GREF

GND

BREF

RXD1IN

HVLKC

HVTCNT

HVCNT

GND

GND

VL_LSU

CN4

123456789

876

HSYNC

54321

LSU

8

HVBCNT

50

ENABLE

9

PGND

VIDEO

CN LS

Main

Motor

11

10

PVP

ON

GND

PVP

PGND

PMCLK

PMCNT

PMLCK

ADJUST

111213

14

15

10

16

54321

CN LSM

M

Polygon

Motor

Power Switch

4

5

3

1

2

3

CN7

MMLCK

MMCNT

24 0

For DP-150A/PA/FP/FX

M

CN 1

1

2

5

4

GND

PVP

CN18

CNAFSC

CN 1

VL

GND

AFOSIZ2

12345

12345

ADF

Close

24V

Interlock Switch

S2

Paper

1

234

GND

50

VL

GND

GND

AFOSIZ1

6

10

12345

6

1

3

2

3

AFO

SIZ1

Paper Size

Detecting

Sensor

Only for

Choke

1

2

AC 2

LP 2

Close

Laser

S3

Paper

Exit

Sensor

Regist-

ration

Sensor

PE

RR

SN

PFO

SN

2

3

3

2

1

132

56789

11

10

PESN

VL

GND

VL

PFOSNVLGND

GND

RRSN

505050

50

50

50

VL

VL

GND

GND

APESN

AFOSN

AFRRSN

789

131415

11

12

6

CNAFC

2

312

1

3

1

2

AFRR

AFPE

SN

AFO

SN

Paper

Detecting

Sensor

Registration

Cover Open/

Close Sensor

Europ

Fuser

Mian Metal Frame

CN4

Close

Laser

S4

Detecting

Sensor

SN

1

12

VL

24 0

24 0

VL

SVP

AFRRCL

AFPSOL

181920212223242526

1

1

2

2

SN

Sensor

Registration

Clutch

Paper Feed

inret

Only for Europe

(Green/

Yellow)

E

SVP

SVP

ADMBB

9

11

Solenoid

L

(Blue)

(Brown)

Pulse

SVP

ADMAB

ADMB

753

M

ADF Drive

Motor

Only for North America

N

F2F1F3

(Black)

L

CN1

AC1

LVPS

24 0

ADMA

SVP

STPSOL

Mian Metal Frame

27

28

16

17

E3

1

2

CNSTC

1

2

CNTS

1

E4

Stamp

Solenoid

ADF

Metal

Frame

Thermostat x 2

Fuser Unit

(Green or Green/Yellow)

E

Mian Metal Frame

Mark (R)

(White)

N

(Red)

N

CN2

CN3

AC2

50

50

VL

GND

GND

SCRSN

SCPESN

CN22

1234567

1234567

CNPF

1

2

3

2

3

1

SCR

SN

SCPE

SN

Registration

Sensor

2nd Paper Feed

Paper Detecting

Sensor

Module (Option)

Fuser Lamp

Thermistor

(White)

2

1

LP1

AC1

CN6

CN7

CN5

24 0

PVP

VL

SCPSOL

8

8

9

E1

1

2

2nd Cassette Module

Metal Frame

E2

Paper Feed

Solenoid

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

4

3

2

1

4

3

2

1

GND

CN19

1234567

Mian Metal Frame

For DP-150FX

VL

GND

ADPSN2

CNAD1C

2

1

2

3

ADF

Paper Pass

ADU

1

2

3

4

5

6

7

8

9

1 5

2

3

4

5

4

3

2

1

50

24 0

VL

PVP

ADPFSOL

ADPSN1

8

1

2

3

1

SN1

Paper Exit Solenoid

Sensor

GND

VLC

-12V

AGND

+12V

GND

GND

3.3V

3.3V

10

GND

GND

11

12

VL

VL

13

14

15

VL_LSU

CN13

EPCNT

HTTR

ZCRS

SVCNT

PVCNT

CN9

PGND

PGND

SVP

PVP

CN14

CN21

EL

2

1

Discharge Lamp

1

2

CNEL

TE

SN

123

Toner Level Sensor

123456789

CN10

PVP

ELP

GND

VL

TESN

50

24 0

50

24 0

72Pin 2MB

CPU PCB

24 0

24 0

PVP

ADSBSOL1

ADSBSOL2

CN20

2

2

1

1

2

2

ADU Solenoid 2

Drum Virgin

Detecting Sensor

ND

SN

2

3

1

123

1

2

CNTH

10

TH2

TH1

GND

VL

NDSN

50

SDRAM

CN11 for DP-150FP/FX

CN27 for DP-150A/PA, DP-130A

PVP

CN24

1

1

ADU Solenoid 1

CNNDC

CN26

Printer Connector

36P

CN902

CN23

60P

8

8

VLC

1

7

-12V

6

GND

2

5

+12V

3

VL

4

4

3

GND

5

SVP

2

6

CN904

PGND

7

1

CN905

CNSP

For DP-150FP/FX

Speaker

(IEE1284)

68Pin 2MB

FAX Memory

(Option)

15

EAKD

14

TCKD

13

HYSIG

12

AGND

11

HYBSR

CTON

10

9

HKOF

8

HSDT

7

TURS

CN901

6

PLSD

5

CMLD

4

+24V

GND

3

2

+5V

1

(HOK2)

Fax PCB

GND

SPKOT

1

2

2

1

Except DP-130/150V/A

CN903

15

14

13

12

11

10

9

CNP25

8

7

6

5

4

3

2

1

CNJ20 CNJ21

NCU PCB

CNJ23

4

3

CNJ24

LINE

3

4

Hand Set

A

B

C

D

Model Drawing Name

DP-130/150

General Circuit

Diagram System Circuit

1234

26

2.2. CPU PC Board (V Model)

1234

CPUBLK

D[0..15]

nZC

nINT1

nINT2

nINT3

A

nSRAMCS

nPFOSNIN

nHVLKCIN

nWR

nROMCS

nPCSNIN

nNDSNIN

HTSNIN

TESNIN

PVPEM

SVPEM

nWAIT

RXD1

nSRAMCS2

EPAKEYIN

B

D[0..15]

A[0..21]

nCS0

nCS1

nRD

nWRH

nWRL

nRST0

SYSCK

nID0I

nID1I

nID2I

nCDI

CPKEYIN

nPESNIN

nDOPSNIN

C

nZC

nMMLCKIN

nEXFLIN

nPMLCKIN

nHPSNIN

nRRSNIN

SVDATAA[0..7]

SVDATAB[0..7]

VREF

nHSYNC

nHFPS1IN

nHFPS2IN

nRST1

D

CPUBLK.Sch

nZC

nINT1

nINT2

nINT3

nSRAMCS

nPFOSNIN

nHVLKCIN

nWR

nROMCS

nPCSNIN

nNDSNIN

HTSNIN

TESNIN

PVPEM

SVPEM

nWAIT

RXD1

nSRAMCS2

EPAKEYIN

GABLK

GABLK.Sch

D[0..15]

A[0..21]

nCS0

nCS1

nRD

nWRH

nWRL

nRST0

SYSCK

nID0I

nID1I

nID2I

nCDI

CPKEYIN

nPESNIN

nDOPSNIN

nZC

nMMLCKIN

nEXFLIN

nPMLCKIN

nHPSNIN

nRRSNIN

SVDATAA[0..7]

SVDATAB[0..7]

VREF

nHSYNC

nHFPS1IN

nHFPS2IN

nRST1

A[0..21]D[0..15]

SYSCK

nCS0

nCS1

nWRH

nWRL

nHFSOLI

nELPI

nPUSOLI

nSVCNT

nPVCNT

nPMCNT

nMMCNT

LMPDWN

TXD1

EPLDCNT

EPACNTIN

nRST0

nRST1

nWAIT

nINT3

nWR

nINT1

nINT2

nSRAMCS

nROMCS

nFAXROMCS

nLMAI

nLMABI

nLMBI

nLMBBI

nLMENB

nEXFMI

pHTCNT

nRRSOLI

ADCLK1

ADCLK2

nLPCNT

nHVCNT

nHVBCNT

nHVTCNT

PMCLK

CPDAT

LCLK

KCLK

pCPLAT

pCPLD

GREF

BREF

TREF

OGSET

EGSET

CCDADT

CCDACLK

CCDALD

nFCK

nSCK

nRS1

nRS2

ADJUST

nVIDEO

ENABLE

nSRAMCS2

nRD

nSH

A[0..21]

SYSCK

nCS0

nCS1

nRD

nWRH

nWRL

nHFSOLI

nELPI

nPUSOLI

nSVCNT

nPVCNT

nPMCNT

nMMCNT

LMPDWN

TXD1

EPLDCNT

EPACNTIN

nRST0

nRST1

nWAIT

nINT3

nWR

nINT1

nINT2

nSRAMCS

nROMCS

nFAXROMCS

nLMAI

nLMABI

nLMBI

nLMBBI

nLMENB

nEXFMI

pHTCNT

nRRSOLI

ADCLK1

ADCLK2

nLPCNT

nHVCNT

nHVBCNT

nHVTCNT

PMCLK

CPDAT

LCLK

KCLK

pCPLAT

pCPLD

GREF

BREF

TREF

OGSET

EGSET

CCDADT

CCDACLK

CCDALD

nSH

nFCK

nSCK

nRS1

nRS2

ADJUST

nVIDEO

ENABLE

nSRAMCS2

nPESN

nHPSN

nRRSN

ZCRS

pHTCNT

TH1

TH2

NID0

NID1

NID2

nCD

nMMLCK

nDOPSN

nPFOSN

nEXFL

nPMLCK

nHVLKC

nPCSN

nNDSN

TESN

CPKEY

EPAKEY

nRST1

EPACNTIN

EPLDCNT

nHFPS1

nHFPS2

nHFSOLI

nEXFMI

LMPDWN

TXD1

RXD1IN

INPUT

INPUT.Sch

nHPSN

nRRSN

pHTCNT

TH1

TH2

NID0

NID1

NID2

nCD

nMMLCK

nDOPSN

nPFOSN

nEXFL

nPMLCK

nHVLKC

nPCSN

nNDSN

TESN

CPKEY

EPAKEY

nRST1

EPACNTIN

EPLDCNT nHFPS1IN

nHFPS2 EPAKEYIN

OUTPUT

OUTPUT.Sch

nRRSOLI

nHFSOLI

nPUSOLI nPUSOL

nLMAI

nLMABI

nLMBI

nLMBBI

nLMENB

nEXFMI

LMPDWN

TXD1

RXD1IN

nPESNINnPESN

nHPSNIN

nRRSNIN

nHTTR

nID0I

nID1I

nID2I

nCDI

EPALED

nMMLCKIN

nDOPSNIN

nPCSNIN

nNDSNIN

PVPEM

TESNIN

HTSNIN

SVPEM

CPKEYIN

nEPCNT

nPFOSNIN

nEXFLIN

nPMLCKIN

nHVLKCIN

nHFPS2INnHFPS1

nRRSOL

nHFSOL

nELPnELPI

nLMA

nLMAB

nLMB

nLMBB

pEXFM

RXD1

TXD1OUT

nPESNIN

nHPSNIN

nRRSNIN

nZC

nZCZCRS

nHTTR

nID0I

nID1I

nID2I

nCDI

EPALED

nMMLCKIN

nDOPSNIN

nPCSNIN

nNDSNIN

PVPEM

TESNIN

HTSNIN

SVPEM

CPKEYIN

nEPCNT

nPFOSNIN

nEXFLIN

nPMLCKIN

nHVLKCIN

nHFPS1IN

nHFPS2IN

EPAKEYIN

nRRSOLnRRSOLI

nHFSOL

nPUSOLnPUSOLI

nELPnELPI

nLMAnLMAI

nLMABnLMABI

nLMBnLMBI

nLMBBnLMBBI

pEXFMnLMENB

RXD1

TXD1OUT

OGSET

ADCLK2

EGSET

ADCLK1

VOUTE

VOUTO

CPDAT

LCLK

KCLK

pCPLAT

pCPLD

pEXFM

nRRSOL

nPUSOL

nHFSOL

ENABLE

nVIDEO

ADJUST

nPMCNT

PMCLK

nMMCNT

TREF

GREF

BREF

nHVTCNT

nHVCNT

nHVBCNT

nSVCNT

nPVCNT

nHTTR

nELP

nRD

nWRL

nRST1

nLPCNT

CCDADT

CCDACLK

CCDALD

nSH

nFCK

nSCK

nRS1

nRS2

nEPCNT

nFAXROMCS

A[1..20]

D[0..15]

EPALED

TXD1OUT

nLMA

nLMAB

nLMB

nLMBB

CCDIF

CCDIF.sch

OGSET

SVDATAA[0..7]

ADCLK2

SVDATAB[0..7]

EGSET

ADCLK1

VOUTE

VOUTO

CONNECTOR

CONNECTOR.Sch

CPDAT

LCLK

KCLK

pCPLAT

pCPLD CPKEY

nRRSOL

nPUSOL

nHFSOL

ENABLE

nVIDEO

ADJUST

nPMCNT

PMCLK

nMMCNT

TREF

GREF

BREF

nHVTCNT

nHVCNT

nHVBCNT

nSVCNT

nPVCNT

nHTTR

nELP

nRD

nWRL

nRST1

nLPCNT

CCDADT

CCDACLK

CCDALD

nSH

nFCK

nSCK

nRS1

nRS2

nEPCNT

nFAXROMCS

A[1..20]

D[0..15]

EPALED

TXD1OUT

nLMA

nLMAB

nLMB

nLMBB

nDOPSN

nPFOSN

nRRSN

nPESN

nEXFLpEXFM

nHSYNC

nPMLCK

nHPSN

nPCSN

nMMLCK

VREF

nHVLKC

ZCRS

TESN

nNDSN

nWRH

VOUTE

VOUTO

EPAKEY

RXD1IN

nHFPS1

nHFPS2

SVDATAA[0..7]

SVDATAB[0..7]

nDOPSN

nPFOSN

nRRSN

nPESN

CPKEY

nEXFL

nHSYNC

nPMLCK

nHPSN

nPCSN

nMMLCK

VREF

nHVLKC

ZCRS

TESN

TH1

TH1

TH2

TH2

nNDSN

nWRH

VOUTE

VOUTO

nCD

nCD

nID0

nID0

nID1

nID1

nID2

nID2

EPAKEY

RXD1IN

nHFPS1

nHFPS2

A

B

C

D

Model Drawing Name

FFPWB06641

For DP-130/150

LCNROOT.PRJ (1/7)

1234

27

1234

A[0..21]

D[0..15]

[3:D1]

[3:D1]

DT20

DTA114EKA146

ERJ3GSYJ103V

VL

D2

MA152KTX

A[0..21]

D[0..15]

IC2

A1

25

24

A2

A1

23

A3

A2

22

A4

A3

21

A5

A4

20

A6

A5

A7

19

A6

18

A8

A7

8

A9

A8

7

A10

A9

A11

6

A10

5

A12

A11

4

A13

A12

A14

3

A13

2

A15

A14

1

A16

A15

A17

48

A16

17

A18

11

nWR

nWR

nROMCS

VL

R30

nSRAMCS2

[3:D1]

WE

12

nRST0

RP

13

VPP

14

nWP

WP

26

nROMCS

CE

28

nRD

OE

47

VL

BYTE

LHF40VZ3

IC3

10

A1

A0

9

A2

A1

8

A3

A2

7

A4

A3

6

A5

A4

5

A6

A5

4

A7

A6

3

A8

A7

25

A9

A8

24

A10

A9

21

A11

A10

23

A12

A11

2

A13

A12

26

A14

A13

1

A15

A14

nRD

22

OE

27

nWRL

WE

20

CE1

W24258S-70LL

IC4

10

A1

A0

A2

9

A1

8

A3

A2

7

A4

A3

6

A5

A4

5

A6

A5

4

A7

A6

3

A8

A7

25

A9

A8

24

A10

A9

21

A11

A10

23

A12

A11

2

A13

A12

26

A14

A13

1

A15

A14

22

nRD

OE

27

nWRH

WE

20

CE1

W24258S-70LL

IC25

10

A1

A0

9

A2

A1

8

A3

A2

7

A4

A3

6

A5

A4

5

A6

A5

4

A7

A6

3

A8

A7

A9

25

A8

A10

24

A9

21

A11

A10

A12

23

A11

2

A13

A12

26

A14

A13

1

A15

A14

22

nRD

OE

27

nWRL

WE

20

CE1

W24258S-70LL

IC26

10

A1

A0

9

A2

A1

8

A3

A2

A4

7

A3

6

A5

A4

5

A6

A5

4

A7

A6

3

A8

A7

25

A9

A8

A10

24

A9

21

A11

A10

23

A12

A11

2

A13

A12

26

A14

A13

A15

1

A14

22

nRD

OE

27

nWRH

WE

20

nSRAMCS2

CE1

W24258S-70LL

D0

D029A0

31

D1

D1

33

D2

D2

35

D3

D3

38

D4

D4

40

D5

D5

42

D6

D6

44

D7

D7

30

D8

D8

32

D9

D9

34

D10

D10

36

D11

D11

39

D12

D12

41

D13

D13

43

D14

D14

45

D15

D15

N.C9A17

TL72

10

N.C

TL73

15

N.C

TL74

16

N.C

TL108

VL

37

VCC

27

GND

46

GND

11

D0

I/O1

12

D1

I/O2

13

D2

I/O3

15

D3

I/04

16

D4

I/O5

17

D5

I/O6

18

D6

I/O7

19

D7

I/O8

C7

ECJ1VF1C104Z

28

VCC

14

GND

11

D8

I/O1

12

D9

I/O2

13

D10

I/O3

15

D11

I/04

16

D12

I/O5

17

D13

I/O6

18

D14

I/O7

19

D15

I/O8

C8

ECJ1VF1C104Z

28

VCC

14

GND

11

D0

I/O1

12

D1

I/O2

13

D2

I/O3

15

D3

I/04

16

D4

I/O5

17

D5

I/O6

18

D6

I/O7

19

D7

I/O8

VL

28

VCC

14

GND

11

D8

I/O1

12

D9

I/O2

13

D10

I/O3

15

D11

I/04

16

D12

I/O5

17

D13

I/O6

18

D14

I/O7

19

D15

I/O8

VL

28

VCC

14

GND

C11

ECJ1VF1C104Z

C102

ECJ1VF1C104Z

C97

ECJ1VF1C104Z

D[0..15]

VL

EC

Q1

2SB709ATX

D1

MA152KTX

R10

ERJ3GSYJ152V

BT1

CR2330-1HH

C104

ECQV1H155JL3

B

R32

ERJ3GSYJ102V

A

B

C

[3:E1] [7:D5]

[3:F1] [7:C5]

nVPPCNT

R33

ERJ3GSYJ152V

nSRAMCS

nSRAMCS

[3:D1]

D

ECEA1CKA100B

[3:B1] [4:A2]

[3:D1]

[3:D1]

[3:D1]

R44

ERJ3GSYJ683V

R40

ERJ3GSYJ102V

C64

nZC

nINT1

nINT2

nINT3

DT1

DTC114EKA146

MA152KTX

C6

ECJ1VF1C104Z

A[0..21]

D7

R53

ERJ3GSYJ103V

+12V

DT7

DTC114EKA146

(NOT MOUNT)

VL

3

2

1

4

nZC

nINT1

nINT2

nINT3

C78

ECJ1VB1H102K

VL

R13

ERJ3GSYJ103V

R34

ERJ3GSYJ103V

IC5

CK

R

CT

GND

MB3773TR

A21

C148

VL

ECJ1VF1C104Z

R146

R145

ERJ3GSY0R00V

ERJ3GSY0R00V

C4

RA2

RA4

MNR14EABJ103

RA1

MNR14EABJ103

VL

2

6

4

1

3

5

D0

D1

D2

D3

D4

D5

D6

D7

D8

D9

D10

D11

D12

D13

D14

D15

C79

ECJ1VB1H102K

[4:B2]

[4:B2]

[4:B2]

[4:B2]

[3:D1]

VL

5

VCC

6

VR

7

VS

8

R

MNR14EABJ103

RA3

MNR14EABJ103

8

8

2

6

4

2

6

4

7

1

7

3

5

1

3

5

C81

ECJ1VB1H102K

C80

ECJ1VB1H102K

HTSNIN

HTSNIN

TESNIN

TESNIN

PVPEM

PVPEM

SVPEM

SVPEM

SYSCK

SYSCK

ERJ3GSYJ100V

C77

ECJ1VB1H102K

EPAKEYIN

[4:D4]

R6

ERJ3GSYJ201V

XL1

HC49US7.15MT

ECUV1H220JCV

VL

R8

ERJ3GSYJ102V

TL105

TL104

nRST0

VL

R139

ERJ3GSYJ102V

IC11F

DT18

DTC114EKA146

ECJ1VF1C104Z

8

8

2

6

4

VL

R3

1

EPAKEYIN

nRST0

7

3

5

ECUV1H220JCV

TC74VHC05FEL

TL75

TL76

TL77

TL78

TL79

TL80

TL82

C75

[3:D1]

1213

ERJ3GSYJ103V

ECEA1CKA100B

92

91

90

89

88

86

84

83

82

81

80

78

76

75

74

73

98

72

70

69

68

67

66

65

64

46

118

119

120

121

122

123

125

126

108

44

33

30

107

94

96

R47

ERJ3GSYJ302V

C9

ECUV1H471JCV

VL

7

R143

C76

C2

ECJ1VF1C104Z

C1

C63

D[0]/PD0

D[1]/PD1

D[2]/PD2

D[3]/PD3

D[4]/PD4

D[5]/PD5

D[6]/PD6

D[7]/PD7

D[8]/PD8

D[9]/PD9

D[10]/PD10

D[11]/PD11

D[12]/PD12

D[13]/PD13

D[14]/PD14

D[15]/PD15

NMI

*IRQ0/D[16]/PD16

*IRQ1/D[17]/PD17

*IRQ2/D[18]/PD18

*IRQ3/D[19]/PD19

*IRQ4/D[20]/PD20

*IRQ5/D[21]/PD21

*IRQ6/D[22]/PD22

*IRQ7/D[23]/PD23

*IRQOUT/D[30]/PD30

PF0/AN0

PF1/AN1

PF2/AN2

PF3/AN3

PF4/AN4

PF5/AN5

PF6/AN6

PF7/AN7

*RES

*WDTOVF

*BREQ/PA18/DRAK0

*BACK/PA19/DRAK1

CK/PA15

XTAL

EXTAL

PLLCAP

105

R140

ERJ3GSYJ102V

nRST1

nRST1

C3

ECJ1VF1C104Z

135

112

Vcc

Vcc

Vcc99Vcc85Vcc77Vcc63Vcc40Vcc

PLLVss

PLLVcc

106

104

C10 ECJ1VF1C104Z

R7

ERJ3GSYJ201V

ECJ1VF1C104Z

C5

ECJ1VF1C104Z

VL

128

26

12

Vcc

Vss

Vss

Vss

Vss

Vss

Vss

71

79

93

61

87

117

141

129

VL

[3:B4] [4:B2] [7:B5]

38

41

37

39

127

AVcc

AVref

A[20]/PB8/nIRQ6/nWAIT

A[19]/PB7/nIRQ5/nBREQ

A[21]/PB9/nIRQ7/nADTRG

Vss

Vss

Vss28Vss

Vss

Vss

42

35

55

25

20

19

A[17]/P8127A[16]/P80

A[15]/PC1524A[14]/PC1423A[13]/PC1322A[12]/PC1221A[11]/PC11

A[10]/PC10

A[18]/PB6/nIRQ4/nBACK

PD3/D[31]/nADTRG45PA8/nIREQ2/TCLKC

PA7/nCS3/TCLKB

PA6/nCS2/TCLKA

Vss6Vss14AVss

PA9/nIREQ3/TCLKD

52

53

54

51

124

TL83

TL84

ERJ3GSYJ103V

18

29

TL85

10

A[9]/PC9

A[8]/PC817A[7]/PC716A[6]/PC615A[5]/PC513A[4]/PC411A[3]/PC3

PE15/nDACK1/TIOC4D/nIRQOUT

PA23/nWRHH

PA22/nWRHL3PA21/nCASHH4PA20/nCASHL

1

103

nVPPCNT

nCTI

nWP

R48

5

364

182

7

5

364

182

7

5

364

182

7

5

364

182

7

5

364

182

R1

ERJ3GSYJ103V

9

7

8

A[2]/PC2

A[0]/PC0

A[1]/PC1

*CS0/PA10

*CS1/PA11

*CS2/D[28]/PD28

*CS3/D[29]/PD29

*RD/PA14

*WRH/PA13

*WRL/PA12

*WAIT/PA17

*RAS/PB2/*IRQ0/*POE0

*CASH/PB4/*IRQ2/POE2

*CASL/PB3/*IRQ1/*POE1

RDWR/PB5/*IRQ3/*POE3

*AH/PA16

*DREQ0/D[24]/PD24

*DREQ1/D[25]/PD25

DACK0/D[26]/PD26

DACK1/D[27]/PD27

DRAK0/PE1/TIOC0B

DRAK1/PE3/TIOC0D

TXD0/PA1

RXD0/PA0

TXD1/PA4

RXD1/PA3

SCK0/nIRQ0/PA2/nDREQ0

SCK1/nIRQ1/PA5/nDREQ1

PE0/nDREQ0/TIOC0A

PE2/nDREQ1/TIOC0C

PE4/TIOC1A

PE5/TIOC1B

PE6/TIOC2A

PE7/TIOC2B

PE8/TIOC3A

PE9/TIOC3B

PE10/TIOC3C

PE11/TIOC3D

PE12/TIOC4A

PE13/nMRES/TIOC4B

PE14/nDACK0/TIOC4C/nAH

MD0

MD1

MD297MD3

95

102

TL109

nPFOSNIN

nHVLKCIN

RA6 MNR14EABJ103

RA7 MNR14EABJ103

RA8 MNR14EABJ103

RA9 MNR14EABJ103

ERJ3GSYJ103V

R2

RA10

MNR14EABJ103

IC1

50

49

57

56

43

47

48

101

31

34

32

36

100

62

60

59

58

110

113

131

130

134

133

132

136

109

111

114

115

116

137

138

139

140

142

143

144

2

5

HD6437041F28

VL

R49

ERJ3GSYJ103V

R50

ERJ3GSYJ103V

VL

R51

ERJ3GSYJ103V

R52

ERJ3GSYJ103V

nCTI

[5:C1]

nPFOSNIN

[4:E3]

nHVLKCIN

[4:F2]

VL

ERJ3GSYJ103V

8

2

6

4

R4

R5

ERJ3GSYJ103V

1

7

3

5

nCS0

nCS0

[3:D1]

nCS1

nCS1

nRD

nWRH

nWRL

nWAIT

nPCSNIN

nCTSIN

nNDSNIN

EPACNTIN

EPLDCNT

TXD1

RXD1

nHFSOLI

nPUSOLI

nELPI

pSVCNT

pPVCNT

pPMCNT

pMMCNT

LMPDWN

nRD

nWRH

nWRL

nWAIT

nPCSNIN

nCTSIN

nNDSNIN

EPACNTIN

EPLDCNT

TXD1

RXD1

nHFSOLI

nPUSOLI

nELPI

LMPDWN

DT3

DTC114EKA146

DT4

DTC114EKA146

DT5

DTC114EKA146

DT6

DTC114EKA146

[3:D1]

[3:D1] [7:B5]

[3:D1] [7:B5]

[3:D1] [7:B5]

[3:D1]

[4:E3]

[4:D3]

[4:E3]

[4:A2]

[4:D5]

[5:E4]

[5:E4]

[5:D1]

[5:D1]

[5:D1]

[5:E1]

nSVCNT

nPVCNT

nPMCNT

nMMCNT

1

[7:E2]

nSVCNT

[7:E2]

nPVCNT

nPMCNT

[7:D1]

nMMCNT

[7:B1]

TL103

TL102

TL100

TL99

TL98

TL97

TL96

TL95

TL94

TL93

TL92

TL4

TL87

TL88

TL89

TL90

TL91

TL106

pSVCNT

pPVCNT

1

pPMCNT

pMMCNT

VL

RA5 MNR14EABJ103

7

A0A1A2A3A4A5A6A7A8A9A10

A11

A12

A13

A14

A15

A16

A17

A18

A19

A20

A

B

C

D

Model Drawing Name

FFPWB06641

For DP-130/150

CPUBLK.SCH (2/7)

1234

28

1234

C117

R132

R133

R134

R135

R136

TL62

[7:D1]

C119

ECJ1VB1H103K

[2:A4] [4:B2] [7:B5]

TL61

ERJ3GSYJ100V

ERJ3GSYJ100V

ERJ3GSYJ100V

ERJ3GSYJ100V

ERJ3GSYJ100V

1

ECEA1CKA100B

nHSYNC

1

XL3

INH

GND2OSC

KCO766S17P43

TL71

3.3V

R75

ERJ3GSY0R00V

XL2

4

INH

VCC

BL1

CCDCLK

3

GND2OSC

KCO736S27P38

C66

MA717TX

BLM11B221SDT

IC10

CCDADTI

2

1A1

1Y1

4

CCDACLKI

1A2

1Y2

6

CCDALDI

1A3

1Y3

8

1A4

1Y4

11

2A1

2Y1

13

2A2

2Y2

15

2A3

2Y3

17

2A4

2Y4

1

1G

VL

19

2G

GND

T74VHC244FEL

BL68

IC11A

ADJUSTI

1 2

TC74VHC05FEL

7 14

IC11B

3 4

VIDEOI

TC74VHC05FEL

IC11C

5 6

ENABLEI

TC74VHC05FEL

VL

R76

ERJ3GSY0R00V

4

VCC

BL2

(CK 34M)

3

BLM11B221SDT

TL63

TL64

TL65

TL66

BL70

VL

nHSYNC LLSYNCI

XL4

1

INH

GND2OSC

KCO736S21P00

nRST1

ECJ1VB1H103K

+12V

D4

ZD1

MA3051MTX

TL67

BLM11P600SPT

C30

C31

ECJ1VF1C104Z

ECJ1VF1C104Z

VL VL

R54

ERJ3GSYJ103V

IC13A

1 2

TC74VHC14FEL

IC13B

3 4

TC74VHC14FEL

R77

ERJ3GSY0R00V

4

VCC

BL3

3

BLM11B221SDT

nRST1

C153

VREFIN

ECJ1VF1C104Z

R74

ERJ3GSYJ122V

C106

ECEA1CKA100B

C107

ECJ1VF1C104Z

(CK 26M)

18

16

14

12

9

7

5

3

20

10

BLM11P600SPT

C151

ECJ1VF1C104Z

nVIDEO

1

2

3

4

6

7

16

12

5

8

3.3V

GACLK

DADATA

DACLK

DALD

VL

(ANALOG)

(ANALOG)

C65

CCDADT

CCDACLK

CCDALD

nSH

nFCK

nSCK

nRS1

nRS2

BLM11P600SPT

C29

ECJ1VF1C104Z

C152

ADJUST

ENABLE

IC12

CLK IN

TEST1

TEST2

PULSE

CKO/2

CKO/2

VCC

VCC

GND

GND

M66235FPT2

ERJ3EKF3601V

R84

18

17

11

10

BL67

VL

ECJ1VF1C104Z

ADJUST

nVIDEO

ENABLE

IC8

3

DI

2

CLK

1

LD

R

VDD

VREFU1

VREFU2

8

GND

9

VREFL

M62356P

CCDADT

CCDACLK

CCDALD

nSH

nFCK

nSCK

nRS1

nRS2

C150

ECJ1VF1C104Z

TR

CKO

CKO

CNTCK

TEST3

GND

C122

ECUV1H101JCV

5 6

[7:F5]

[7:F5]

[7:F5]

[7:E5]

[7:E5]

[7:E5]

[7:E5]

[7:E5]

3.3V

[7:D1]

[7:D1]

[7:D1]

13

11

10

TL68

9

TL69

15

TL70

14

C32 ECJ1VF1C104Z

IC13C

TC74VHC14FEL

AO1

AO2

AO3

AO4

AO5

AO6

AO7

AO8

DO

A

nLPCNT

[7:B2]

pLPCNTI

nHVCNT

DT9

DTC114EKA146

pHVCNTI

nHVBCNT

DT10

DTC114EKA146

pHVBCNTI

nHVTCNT

DT11

DTC114EKA146

pHVTCNTI

PMCLK

DT22

DTC143EKA146

PMCLKI

TRGI

PVCLKI

BL63

BLM11B121SDT

LLSYNCDI

(ANALOG)

12

13

(ANALOG)

14

(ANALOG)

15

(ANALOG)

4

EGSET

(ANALOG)

(ANALOG)

[7:F2]

EGSET

OGSET

OGSET

VREF

VREF

1

5

6

7

16

nHVCNT

nHVBCNT

KCLKI

nHVTCNT

PMCLK

(ANALOG)

C149

ECJ1VF1C104Z

[6:D2]

[6:B2]

[7:F2]

[7:F2]

R141

ERJ3GSY0R00V

R142

ERJ3GSY0R00V

[7:F2]

[7:C1]

10

9

5

6

3

2

12

13

(NOT MOUNT)

00

+

-

00

+

-

+12V

411

+

-

00

+

-

CPDATI

LCLKI

CPLATI

CPLDI

BA10324FT2

nLPCNT

DT8

DTC114EKA146

IC9C

BA10324FT2

IC9B

BA10324FT2

IC9A

IC9D

BA10324FT2

8

7

1

14

TREF

C108

ECJ2VF1H104Z

DT23

DTC143EKA146

DT24

DTC143EKA146

DT25

DTC143EKA146

DT26

DTC143EKA146

DT27

DTC143EKA146

GREF

BREF

CPDAT

CPDAT

[7:E1]

LCLK

[7:E1]

LCLK

KCLK

[7:E1]

KCLK

pCPLAT

[7:E1]

pCPLAT

pCPLD

pCPLD

[7:E1]

(ANALOG)

[7:F2]

GREF

C25

ECJ1VF1C104Z

(ANALOG)

BREF

[7:F2]

C26

ECJ1VF1C104Z

(ANALOG)

TREF

[7:F2]

C27

ECJ1VF1C104Z

(ANALOG)

VREFIN

C28

ECJ1VF1C104Z

B

C

D

A

VL

D[0..15]

D[0..15]

[2:F1] [7:C5]

A[0..21]

A[0..21]

[2:F1] [7:D5]

B

nWRL

nWRL

[2:D6] [7:B5]

[2:D6] [7:B5]

[2:D6] [7:B5]

[2:B1]

[2:E1]

[7:B5]

[2:A1]

C

[4:C2]

[4:F2]

[2:D3] [4:A2]

[4:F2]

[4:F2]

[4:F2]

[4:F2]

[4:F2]

[4:D3]

[4:D3]

nWRH

nWRH

nRD

nRD

nCS0

nCS0

[2:D6]

nCS1

[2:D6]

nCS1

nWAIT

[2:D6]

nWAIT

nINT3

[2:D3]

nINT3

nRST0

[2:B4]

nRST0

SYSCK

[2:C4]

SYSCK

nWR

[2:E1]

nWR

nINT1

[2:D3]

nINT1

nINT2

[2:D3]

nINT2

nSRAMCS

nSRAMCS

nROMCS

nROMCS

nFAXROMCS

nFAXROMCS

nID0I

[4:E3]

nID0I

nID1I

[4:D3]

nID1I

nID2I

[4:D3]

nID2I

nCDI

[4:D3]

nCDI

nSRAMCS2

nSRAMCS2

nLMAI

nLMAI

[5:F2]

nLMABI

nLMABI

[5:F2]

nLMBI

[5:E2]

nLMBI

nLMBBI

nLMBBI

[5:E2]

nLMENB

nLMENB

[5:E2]

DADATA

DACLK

DALD

CPDATI

LCLKI

KCLKI

CPLATI

CPLDI

nEXFMI

[5:B1]

nEXFMI

pHTCNT

pHTCNT

[4:F4]

pLPCNTI

pHVCNTI

pHVBCNTI

pHVTCNTI

PMCLKI

nRRSOLI

nRRSOLI

[5:D1]

CPKEYIN

CPKEYIN

nPESNIN

[4:F2]

nPESNIN

nDOPSNIN

nDOPSNIN

nZC

nZC

nMMLCKIN

nMMLCKIN

nEXFLIN

nEXFLIN

nPMLCKIN

nPMLCKIN

nHPSNIN

nHPSNIN

nRRSNIN

nRRSNIN

nHFPS1IN

nHFPS1IN

nHFPS2IN

nHFPS2IN

IC7

FFPAV0009

158

D0

DATA0

159

D1

DATA1

D2

160

DATA2

D3

161

DATA3

162

D4

DATA4

D5

167

DATA5

168

D6

DATA6

D7

169

DATA7

170

D8

DATA8

171

D9

DATA9

172

D10

DATA10

173

D11

DATA11

174

D12

DATA12

175

D13

DATA13

D14

176

DATA14

177

D15

DATA15

125

A0

AD0

126

A1

AD1

127

A2

AD2

128

A3

AD3

129

A4

AD4

130

A5

AD5

131

A6

AD6

132

A7

AD7

133

A8

AD8

134

A9

AD9

135

A10

AD10

136

A11

AD11

A12

137

AD12

138

A13

AD13

139

A14

AD14

A15

140

AD15

143

A16

AD16

A17

144

AD17

145

A18

AD18

146

A19

AD19

A20

147

AD20

148

A21

AD21

124

WRL

103

WRH

149

RD

150

CSA0

151

CSA1

152

WAIT

153

INTA

123

RESET

104

SYSCLK

55

WR

56

INT1

57

INT2

58

SRAMCS

59

ROMCS

62

FAXROMCS

96

NID0

97

NID1

98

NID2

99

NCD

100

SRAMCS2

63

LMAI

64

LMABI

65

LMBI

66

LMBBI

67

LMENB

68

ADMAI

TL23

69

ADMABI

TL24

70

ADMBI

TL25

71

ADMBBI

TL26

72

ADMENB

TL27

73

CPUDADATA

74

CPUDACLK

75

CPUDALD

76

CPDAT

77

LCLK

78

KCLK

79

CPLAT

80

CPLD

81

CPWR

TL28

82

EXFMI

83

HTCNT

84

LPCNT

85

HVCNT

88

HVBCNT

89

HVTCNT

90

PMCLK

91

RRSOLI

92

AFRRSOLI

TL29

93

SCPSOLI

TL30

105

CPKEY

106

ADPSNIN1

107

ADPSNIN2

108

PESNIN

109

DOPSNIN

110

ZC

111

MMLCKIN

112

EXFLIN

113

PMLCKIN

114

HPSNIN

115

RRSNIN

116

AFRRSNIN

117

ENCODER0

118

ENCODER1

VDDI3V1VDDI3V39VDDI3V60VDDI3V86VDDI3V

3.3V

C12

ECJ1VF1C104Z

C13

ECJ1VF1C104Z

ECJ1VF1C104Z

101

121

C14

ECJ1VF1C104Z

C19

ECJ1VF1C104Z

119

154

VDDI5V21VDDI5V

VDDI5V

VDDI3V

VDDI3V

VDDI3V

141

165

C20

VSSI5V20VSSI5V52VSSI5V

VDDI3V

VDDI3V

180

194

225

ECJ1VF1C104Z

ECJ1VF1C104Z

VL

122

155

VSSI5V

VDDI3V

VSSI3V38VSSI3V61VSSI3V87VSSI3V

C15

ECJ1VF1C104Z

C22

C23

C21

156

VDDO5V18VDDO5V40VDDO5V47VDDO5V53VDDO5V94VDDO5V

VSSI3V

VSSI3V

VSSI3V

VSSI3V

102

120

142

166

181

ECJ1VF1C104Z

C24

ECJ1VF1C104Z

ECJ1VF1C104Z

163

178

VDDO5V

VDDO5V

VSSI3V

VSSI3V

VSSI3V

195

226

240

C16

ECJ1VF1C104Z

157

VSSO5V19VSSO5V41VSSO5V48VSSO5V54VSSO5V95VSSO5V

VDDO3V4VDDO3V13VDDO3V

VDDO3V

VDDO3V

196

209

219

C17

164

179

VSSO5V

VSSO5V

VDDO3V

VSSO3V5VSSO3V14VSSO3V

227

3.3V

C18

ECJ1VF1C104Z

ECJ1VB1H103K

SVDATAA0

SVDATAA1

SVDATAA2

SVDATAA3

SVDATAA4

SVDATAA5

SVDATAA6

SVDATAA7

SVDATAB0

SVDATAB1

SVDATAB2

SVDATAB3

SVDATAB4

SVDATAB5

SVDATAB6

SVDATAB7

CCDCLK

CCDACLKI

CCDADTI

CCDALDI

nSHI

nRS1I

nRS2I

nSCKI

nFCKI

ADCLK1

ADCLK2

TRGI

ENABLEI

ADJUSTI

LLSYNCI

LLSYNCDI

PVCLKI

GACLK

TL59

TL58

TL57

TL56

TL55

TL54

TL53

TL52

TL51

TL50

TL49

TL48

TL47

TL46

TL45

TL44

TL43

TL42

TL41

TL40

TL39

TL38

TL37

TL36

TL35

TL34

TL33

TL32

TL31

R131

TL60

R41

ERJ3GSYJ103V

R55

ERJ3GSYJ103V

3.3V

BLM11B221SDT

ERJ3GSYJ103V

SVDATAA[0..7]

SVDATAB[0..7]

ADCLK1

ADCLK2

BL65

3.3V

R9

ERJ3GSYJ103V

R129

ERJ3GSYJ103V

3.3V

R56

[6:C4]

[6:A4]

VIDEOI

1

R130

ERJ3GSYJ103V

R57

ERJ3GSYJ103V

22

SVDATAA0

23

SVDATAA1

24

SVDATAA2

25

SVDATAA3

26

SVDATAA4

27

SVDATAA5

28

SVDATAA6

29

SVDATAA7

30

SVDATAA8

31

SVDATAA9

32

SVDATAA10

33

SVDATAA11

34

SVDATAA12

35

SVDATAA13

36

SVDATAA14

37

SVDATAA15

3

CCDCLK

6

DACLK

7

DADATA

8

DALD

9

SH

10

RS1

11

RS2

12

SCK

15

FCK

16

ADCLK1

17

ADCLK2

42

VIDEO

43

CKSEL

44

TRG

45

ENABLE

46

ADJUST

49

LLSYNC

50

LLSYNCD

51

PVCLK

2

CLK

229

BIDATA0

230

BIDATA1

231

BIDATA2

232

BIDATA3

233

BIDATA4

234

BIDATA5

235

BIDATA6

236

BIDATA7

221

BILEN

222

BIVEN

223

BIRDY

224

BIRD

198

BRDATA0

199

BRDATA1

200

BRDATA2

201

BRDATA3

202

BRDATA4

203

BRDATA5

204

BRDATA6

205

BRDATA7

206

BRLEN

207

BRVEN

208

BRSTB

182

TVDATA0

183

TVDATA1

184

TVDATA2

185

TVDATA3

186