Panasonic CQC-7305-N Service manual

Specifications*

ORDER NO. ACED070104C8

AUTOMOTIVE AFTERMARKET

CQ-C7305N

WMA MP3 AAC CD Player/Receiver

General

Power Supply DC 12V (11V - 16V),

Test Voltage 14.4V

Negative Ground

Tone Controls (Bass/Treble) Bass: ±12dB at 60Hz

Treble: ±12dB at 16kHz

Equlizer Center Frequency 60, 160, 400, 1k, 3k, 6k, 16k Hz

Variable Range of Equalizer -12dB to 12dB (2dB step)

Current Consumption Less than 2.2A

(CD mode; 0.5W × 4-speaker)

Maximum Power Output 50W × 4(at 1kHz)

Power Output 23Wx4(at 4Ω)

Speaker Impedance 4-8Ω

Pre-amp Output Voltage 2.5V (CD mode; 1kHz, 0dB)

Subwoofer Output Voltage 2.5V (CD mode; 1kHz, 0dB)

Pre-amp Output Impedance 200Ω

Subwoofer Output Impedance 200Ω

FM Stereo Radio

Frequency Range 87.5MHz - 108MHz

Usable Sensitivity 6dB/µV(S/N30dB)

Stereo Separation 35dB (at 1kHz)

AM(LW)Radio

Frequency Range 153kHz - 279kHz

Usable Sensitivity 32dB/µV (S/N 20dB)

CD Player

Sampling Frequency 8 Times Oversampling

DA Converter 4 DAC System

Pick-up Type Astigma 3-Beam

Light Source Semiconductor Laser

Wave Length 790 nm

Frequency Response 20 Hz-20kHz (±1dB)

Signal to Noise Ratio 96dB

Total Harmonic Distortion 0.01% (1kHz)

Wow and Flutter Below Measurable Limits

Channel Separation 85dB

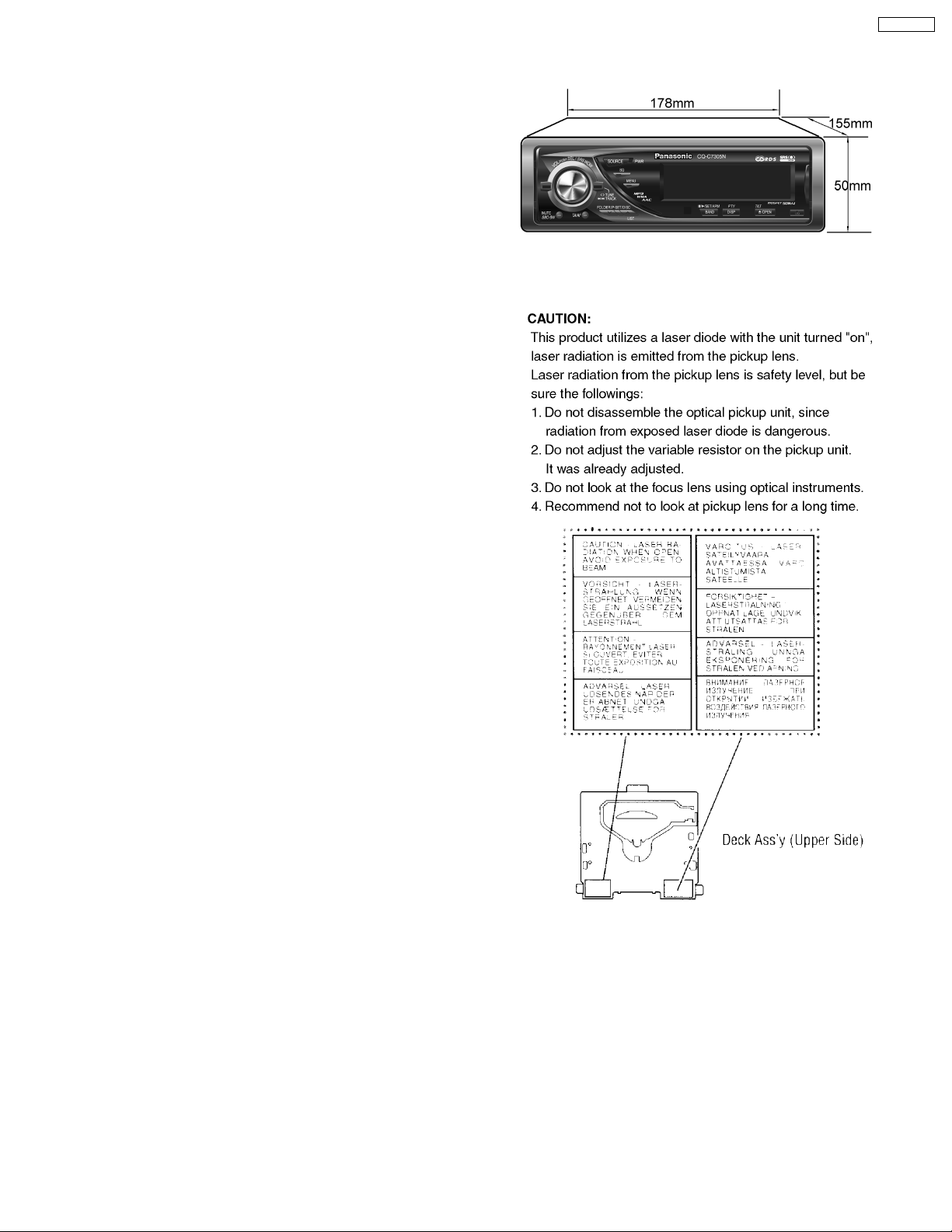

Dimensions (W×H×D)** 178×50×155mm

Weight** 1.6 kg

* Specifications and the design are subject to possible modification

without notice due to improvements.

** Dimensions and Weight shown are approximate.

** Above specifications comply with EIA standards.

© 2006 Matsushita Electric Industrial Co., Ltd. All

rights reserved. Unauthorized copying and

distribution is a violation of law.

CQ-C7305N

CONTENTS

Page Page

1 ABOUT LEAD FREE SOLDER (PbF) 3

2 FEATUERS

3 REPLACEING THE FUSE

4 MAINTENANCE

5 NOTES

6 DIMENSIONS

7 LASER PRODUCTS

8 WIRING CONNECTION

9 BLOCK DIAGRAM

10 DISASSEMBLY INSTRUCTIONS

11 TERMINALS DESCRIPTI ON

12 IC BLOCK DIAGRAM

3

3

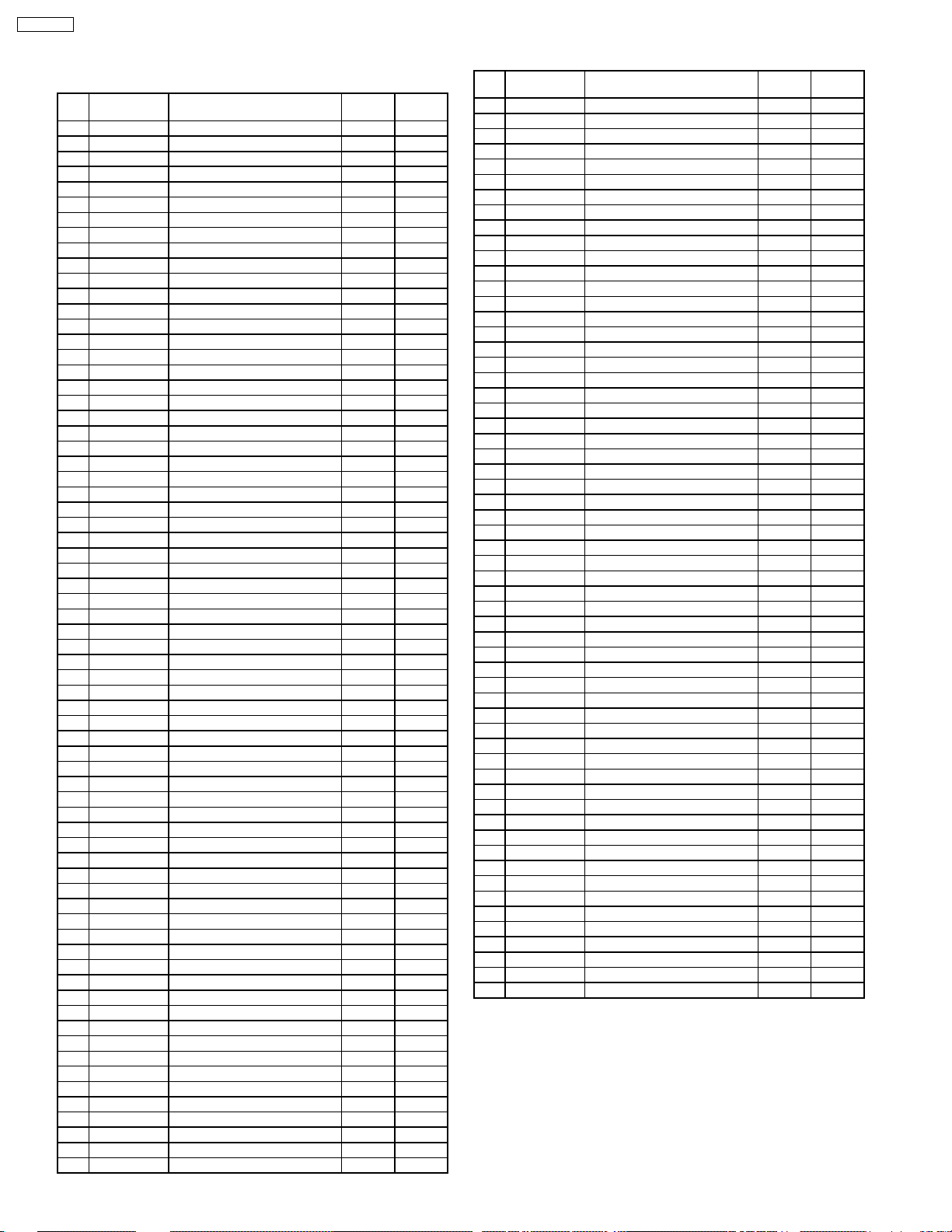

13 REPLACEMENT PARTS LIST

14 EXPLODED VIEW (Unit)

3

3

15 CD PLAYER PARTS LIST

3

16 EXPLODED VIEW (CD PLAYER)

17 WIRING DIAGRAM

3

4

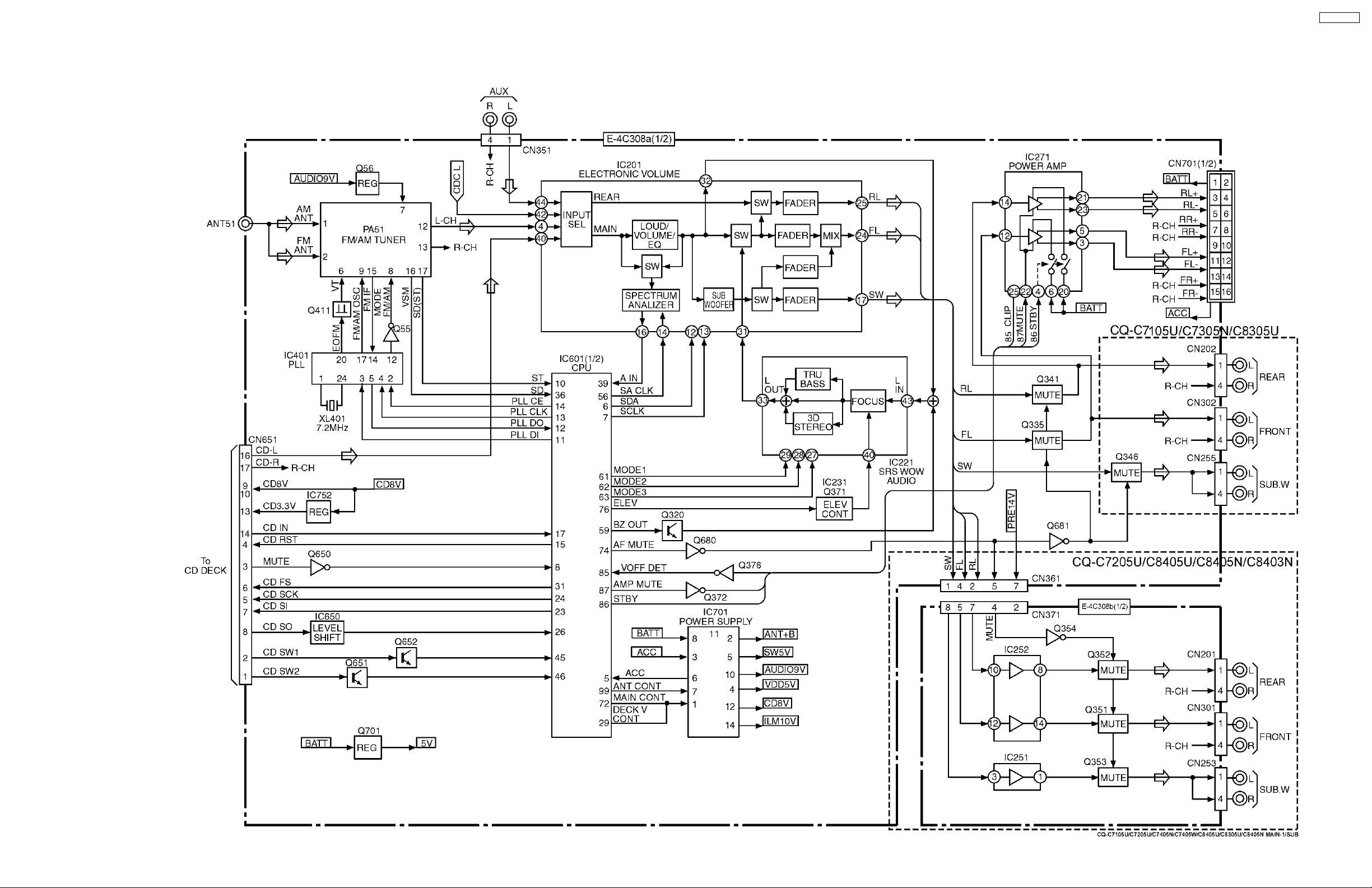

18 SCHEMATIC DIAGRAM

19 SCHEMATIC DIAGRAM for printing with A4 size

5

9

12

16

18

24

25

27

28

35

41

2

CQ-C7305N

1 ABOUT LEAD FREE

SOLDER (PbF)

Distinction of PbF PCB:

PCBs (manufactured) using lead free solder will have a PbF

stamp on the PCB.

Caution :

•

• Pb free solder has a higher melting point than standard

• •

solder; Typically the melting point is 50 - 70°F (30 40°C) higher. Please use a soldering iron with

temperature control and adjust it to 700 ± 20°F (370 ±

10°C). In case of using high temperature soldering iron,

please be careful not to heat too long.

•

• Pb free solder will tend to splash when heated too high

• •

(about 1100°F/600°C)

•

• This lead free solder will be used for the products after

• •

serial No. 1,000,001.

2 FEATUERS

•

• Hands Free Phone System. (The optional Bluetooth hands-

• •

free kit: CY-BT100U)

•

• Expansion Module (The optional Hub unit: CY-EM100U)

• •

•

• The optional adapter allows you to connect the optional

• •

Panasonic DVD changer unit (CX-DH801U).

•

• The optional adapter allows you to connect the optional

• •

Panasonic CD changer unit (CX-DP880).

•

• The optional adapter allows you to connect the optional

• •

®

iPod

series.

•

• SQ7 (7-Band Sound Quality) .

• •

•

• Customize the Display (Customize Function)

• •

•

• MP3/WMA/AAC Playback from CD-R/RW.

• •

6 DIMENSIONS

7 LASER PRODUCTS

3 REPLACEING THE FUSE

Use fuses of the same specified rating 15 amps. Using different

substitutes or fuses with higher ratings, or connecting the unit

directly without a fuse, could cause fire or damage to the stereo

unit.

4 MAINTENANCE

Your products is designed and manufactured to ensure a

minimum of maintenance. Use a soft cloth for routine exterior

cleaning. Never use benzine, thinner or other solvent.

5 NOTES

[RADIO BLOCK]

Do not align the AM/FM package block. When the package

block is necessary, it will be supplied already aligned at the

factory.

[CD DECK BLOCK]

This model has no servo alignment points because

microcomputer controls the servo circuit

3

CQ-C7305N

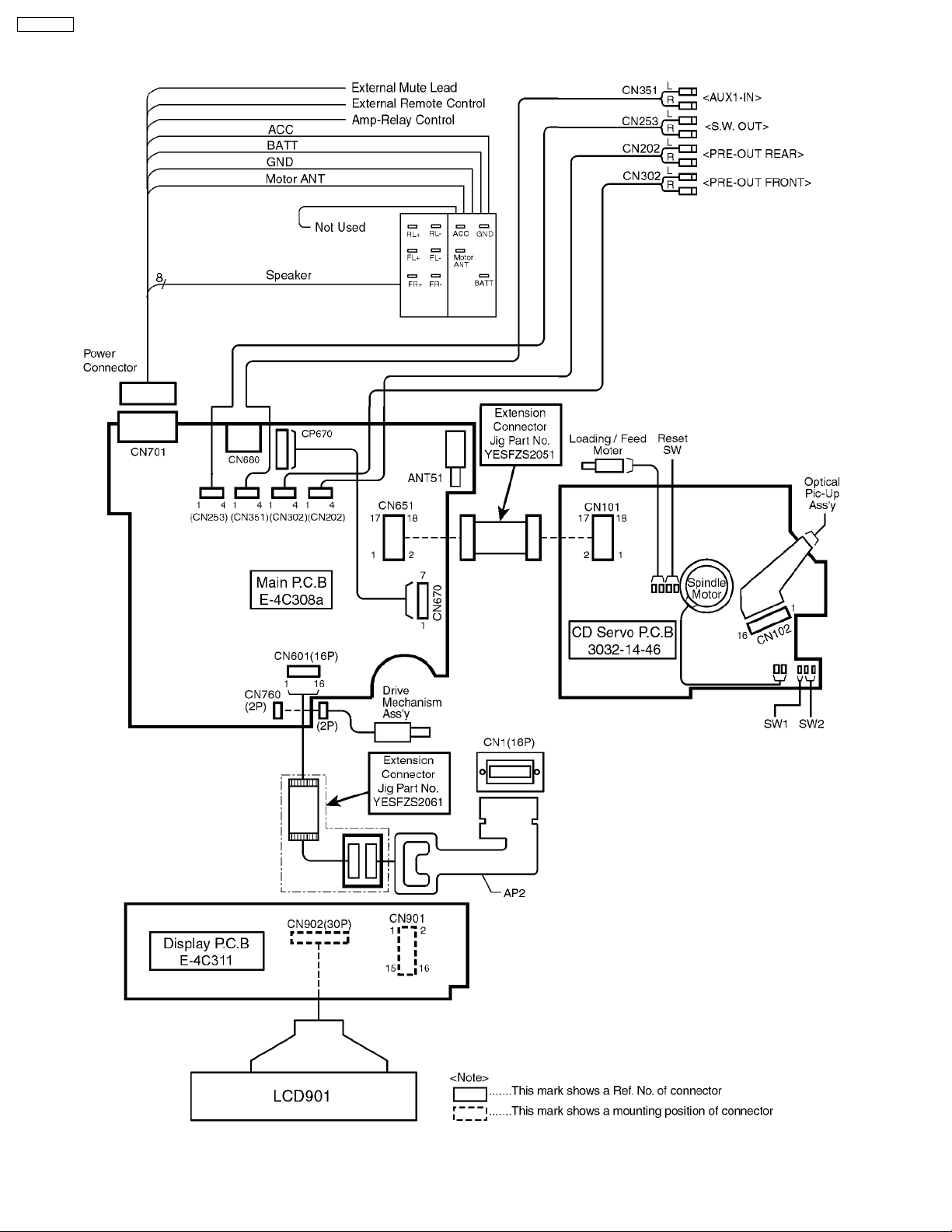

8 WIRING CONNECTION

4

9 BLOCK DIAGRAM

9.1. Main-1 Block

CQ-C7305N

5

CQ-C7305N

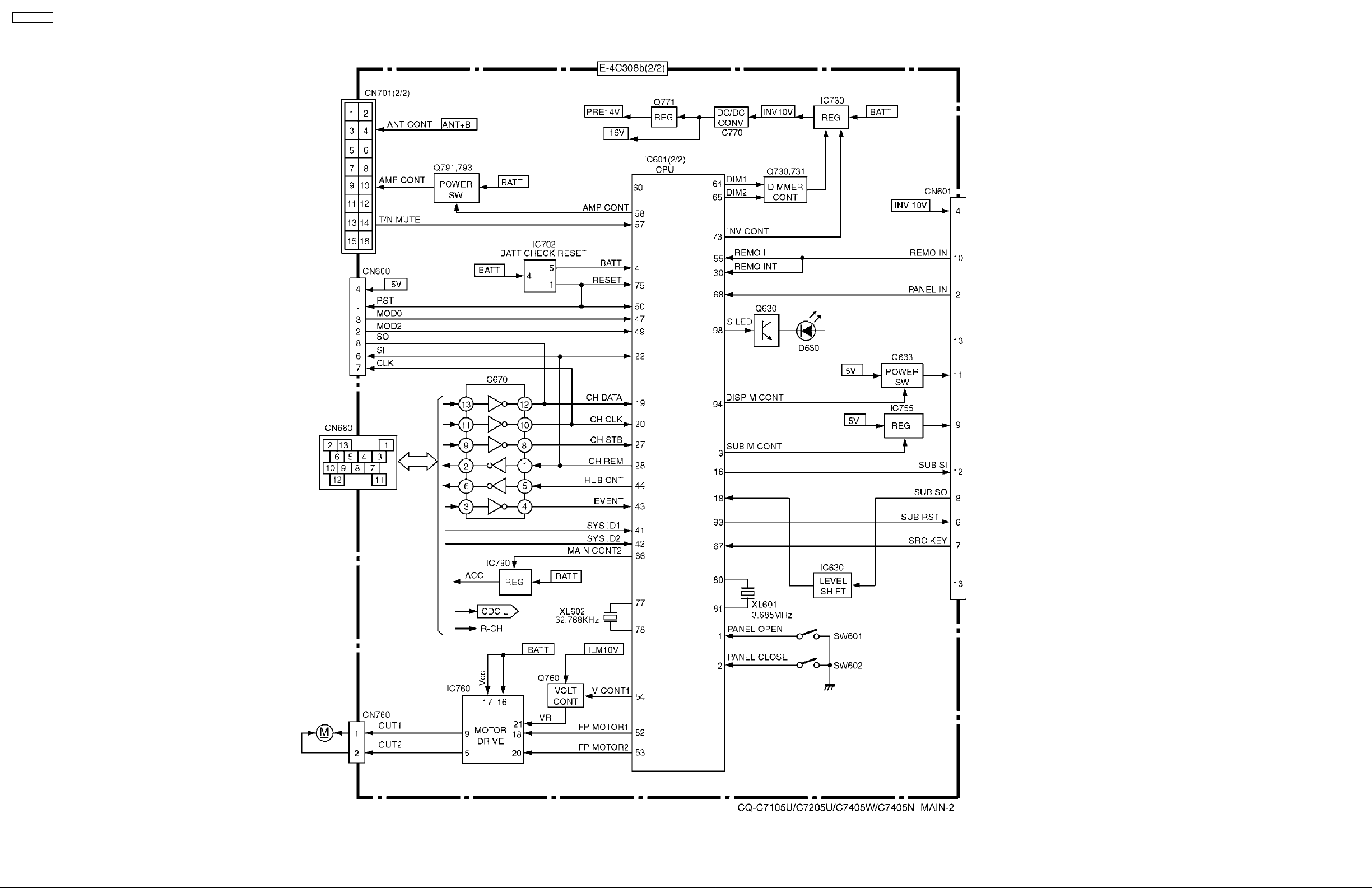

9.2. Main-2 Block

6

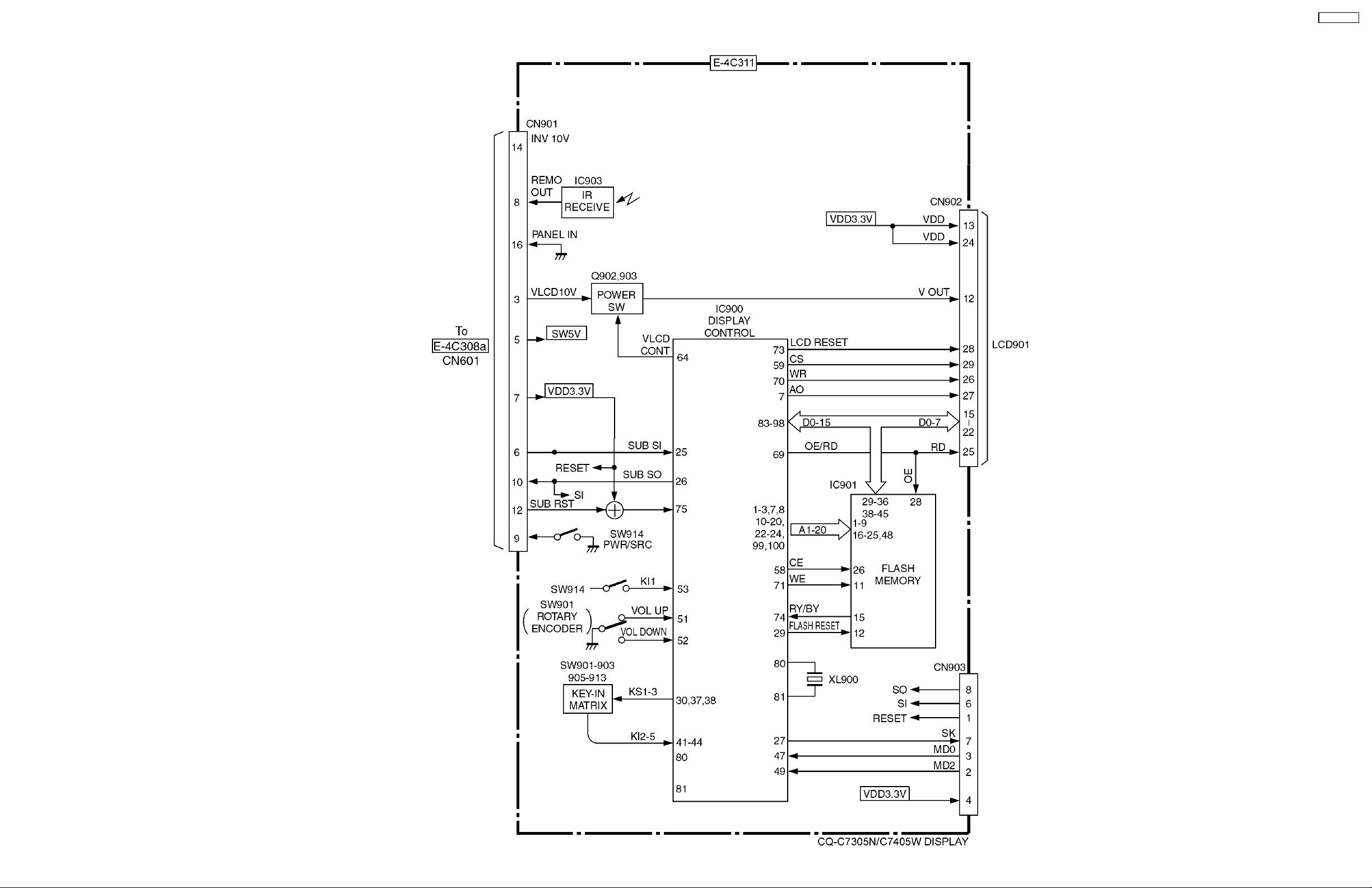

9.3. Display Block

CQ-C7305N

7

CQ-C7305N

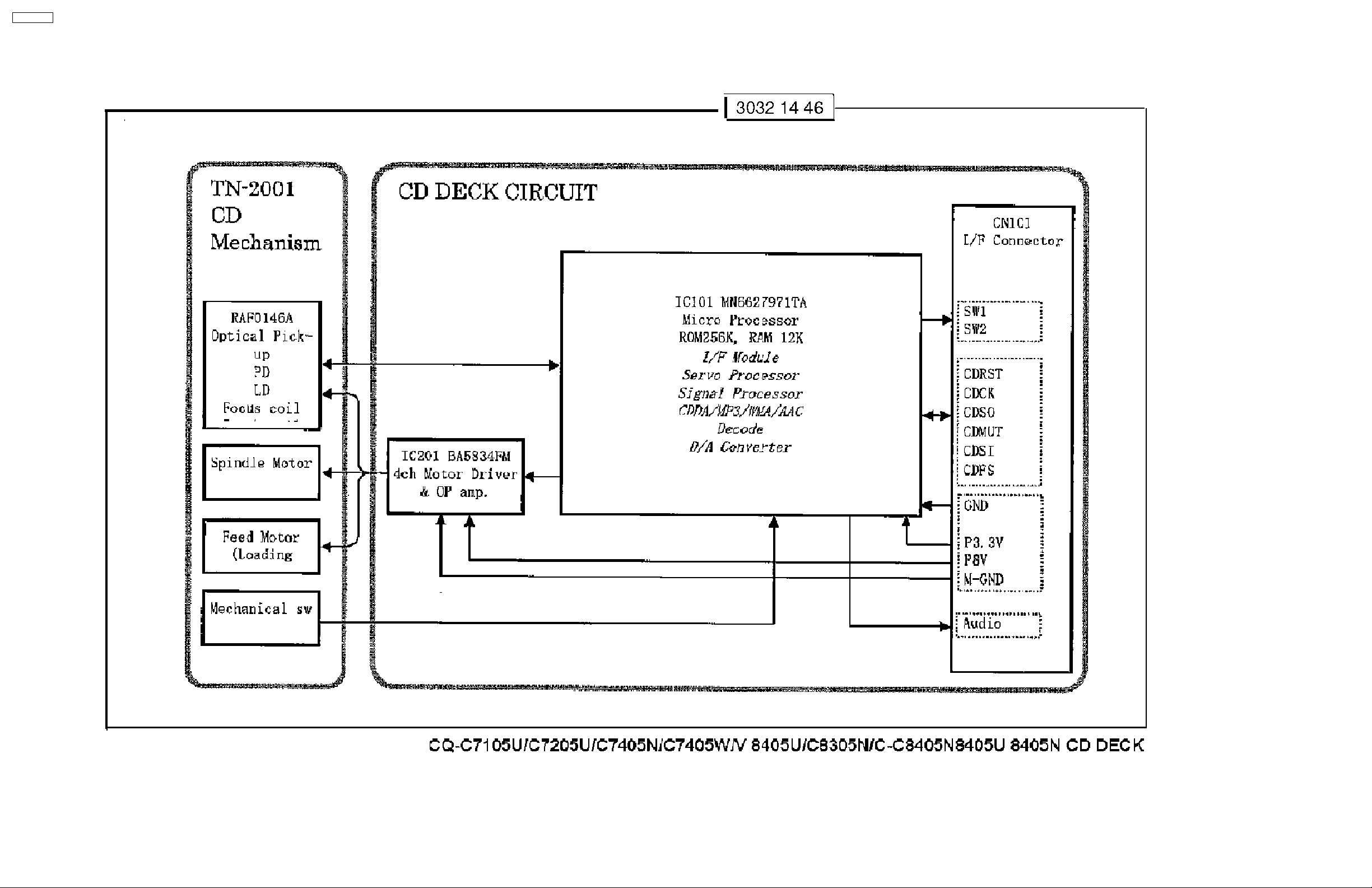

9.4. CD Servo Block

8

10 DISASSEMBLY INSTRUCTIONS

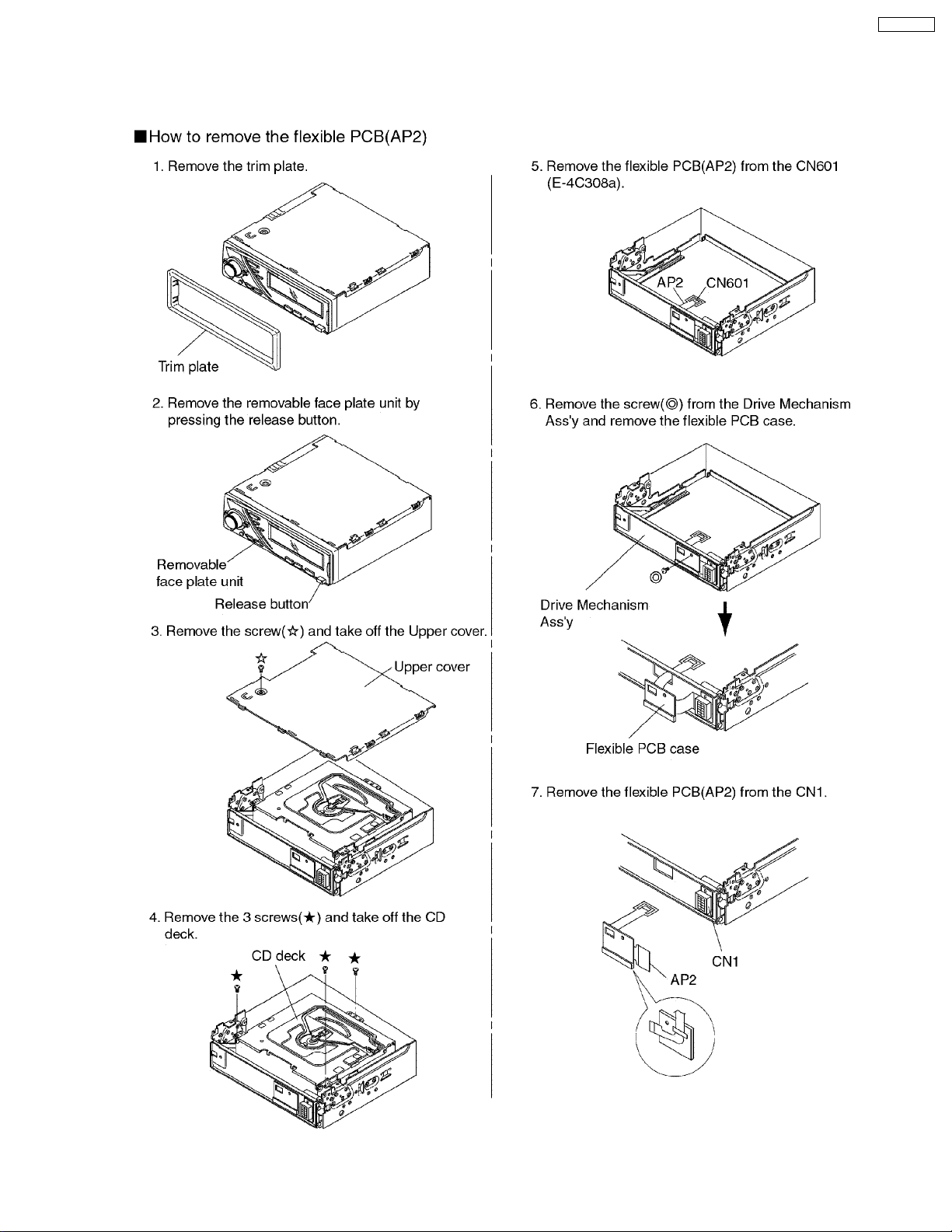

10.1. How to Remove the Flexible PCB(AP2)

CQ-C7305N

9

CQ-C7305N

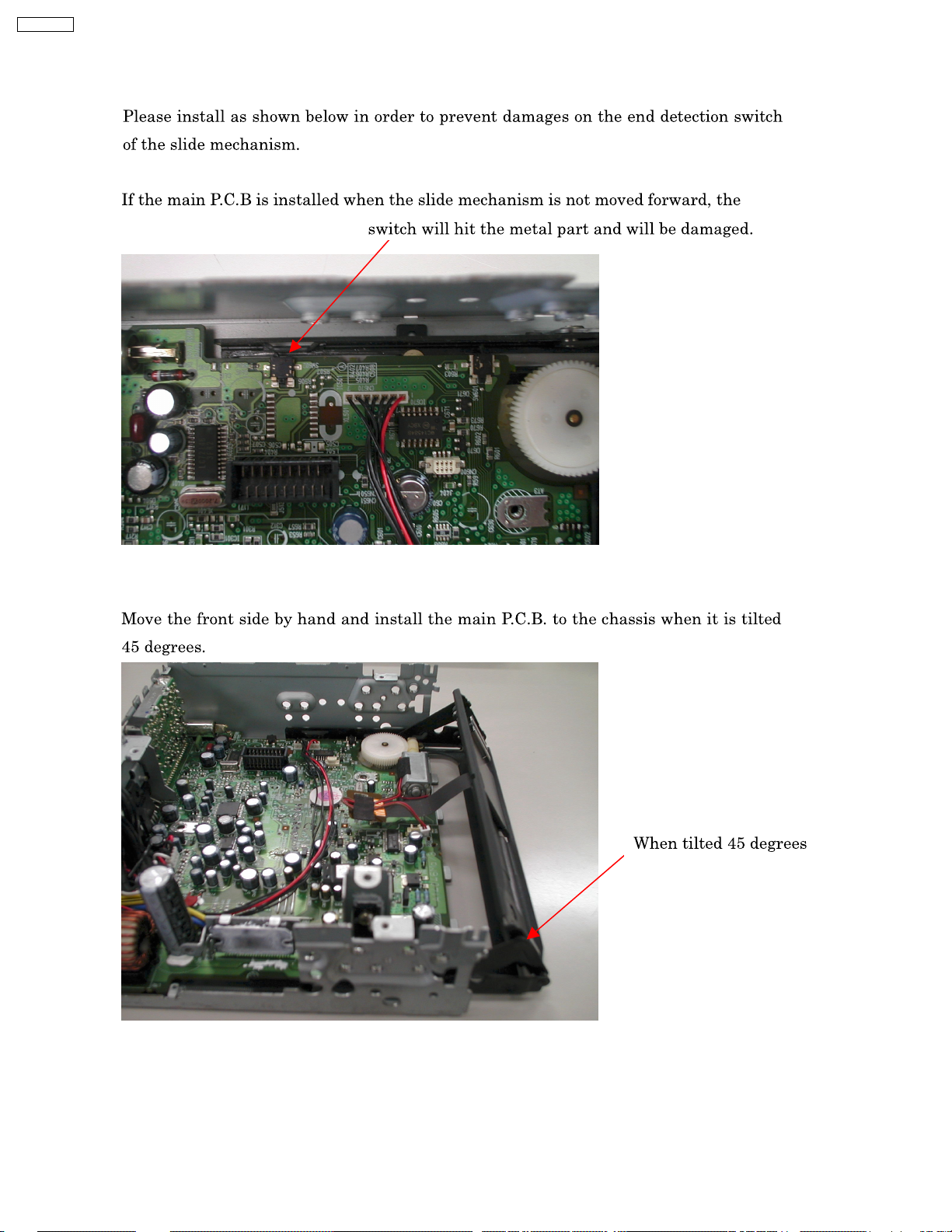

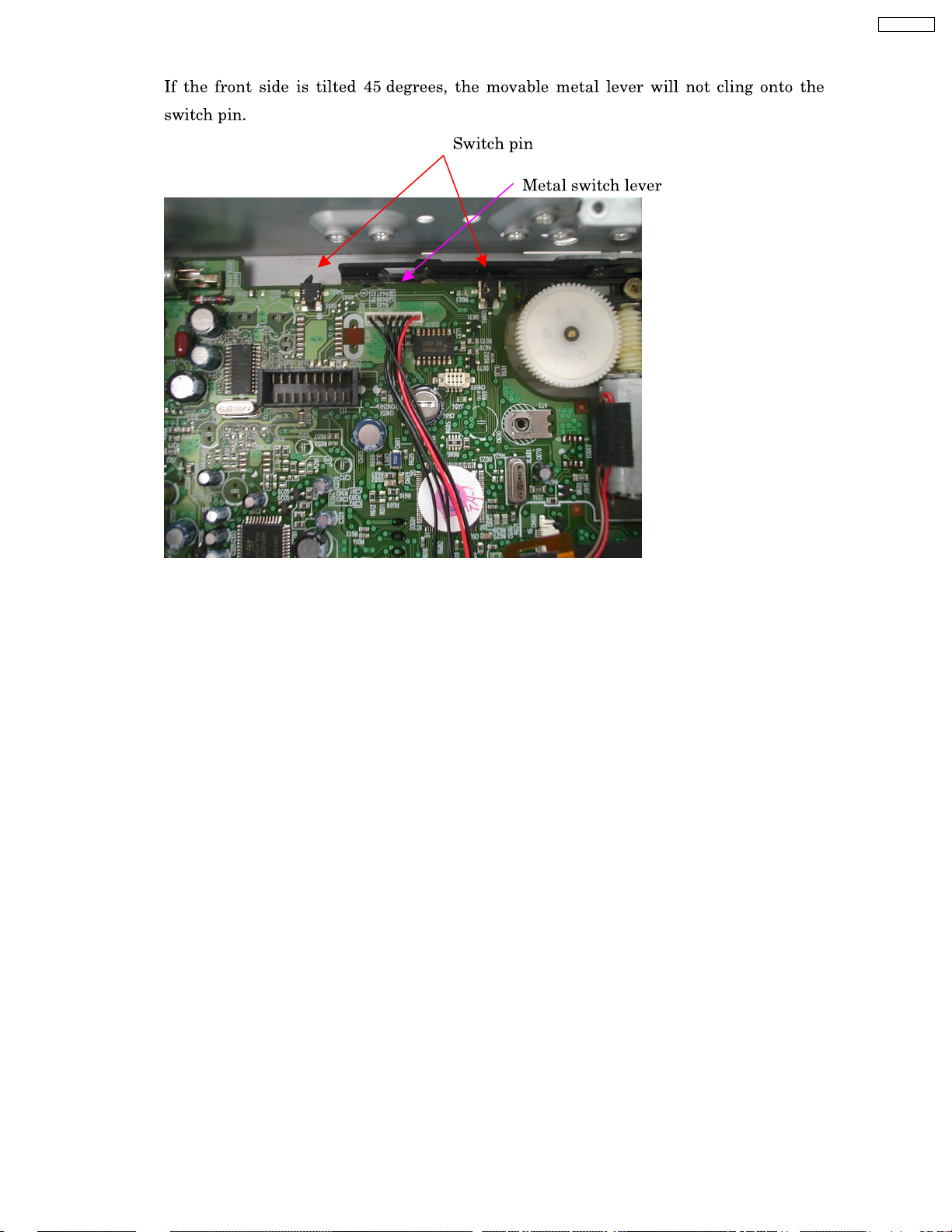

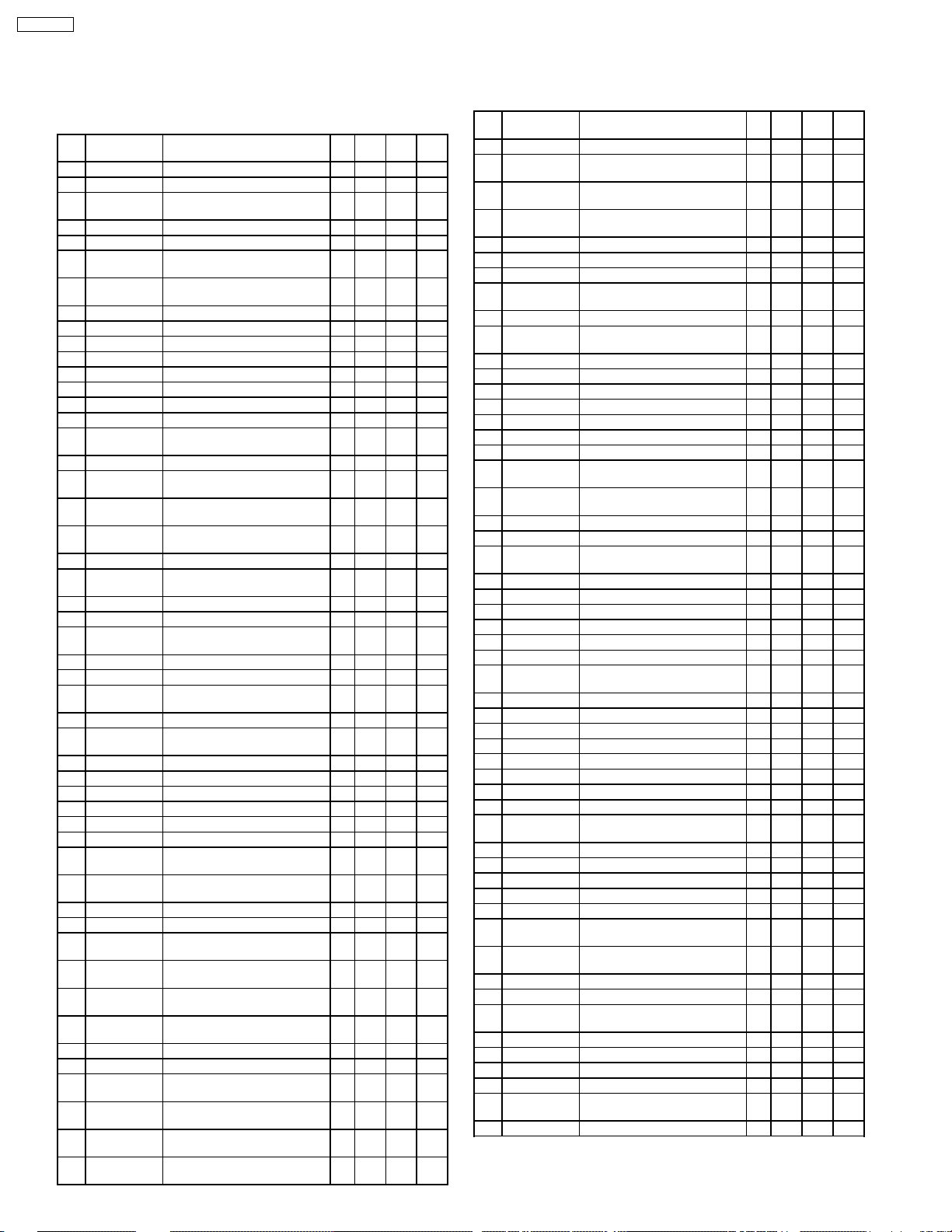

10.2. How to Install the Main P.C.B. of the Electric Display

10

CQ-C7305N

11

CQ-C7305N

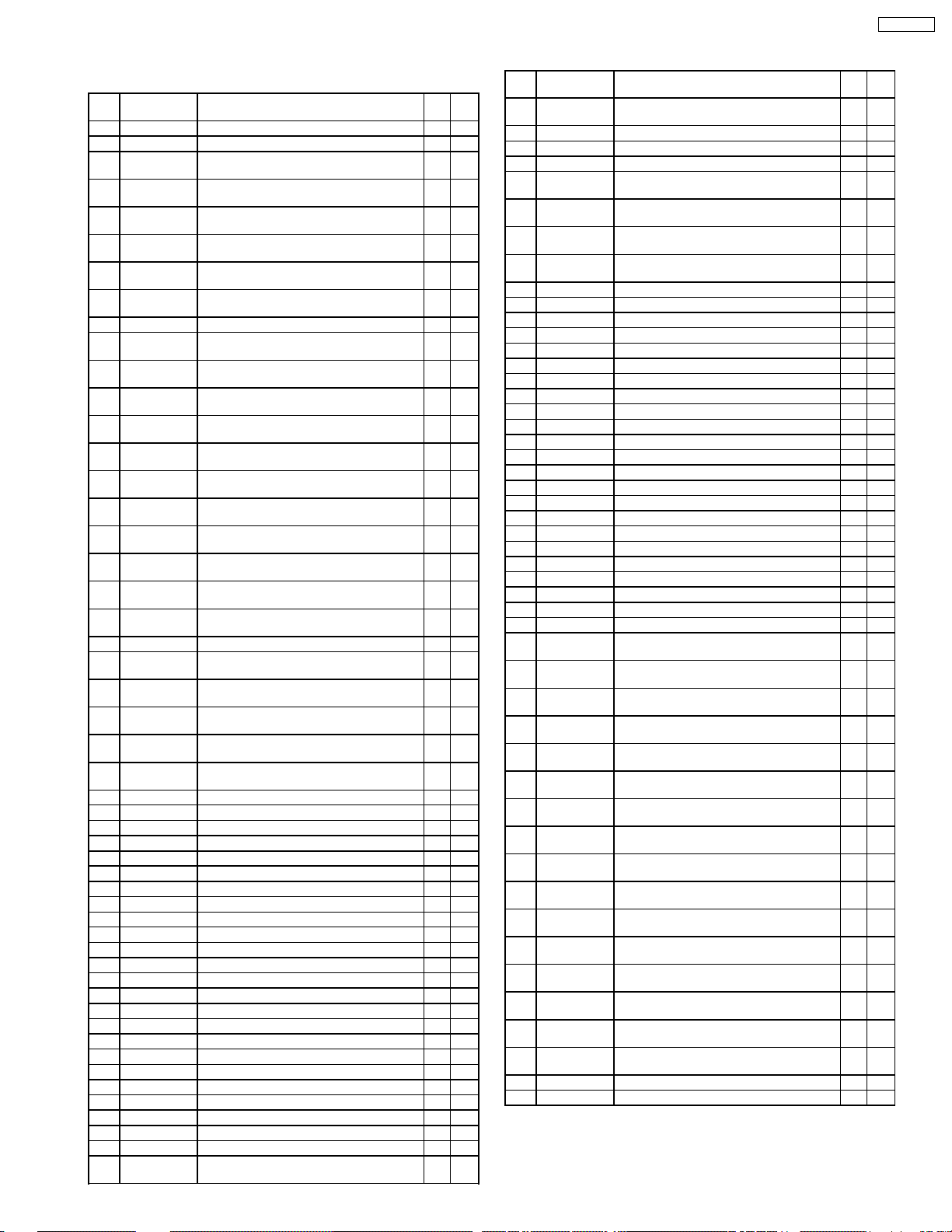

11 TERMINALS DESCRIPTION

11.1. Main BLOCK

IC601:YEAMB90F439P

Pin

No.

Port Description I/O FM AM CD

1 PANEL_OPEN Panel open detection I 5.2 5.2 5.2

2 PANEL_CLOSE Panel close detection I 0 0 0

3 SUBM_CNT 3.3V power control

4 BATT Battery power check I 4.8 4.8 4.8

5 ACC Acc. power check I 5.4 5.4 5.4

6 SDA Serial data for

7 SCLK Serial clock for

8 CD_MUTE Signal mute from CD deck I 0 0 0

9 Vss GND I 0 0 0

10 ST FM stereo detection I 0 0 0

11 PLL_DI(MO) Serial data to PLL O 0 0 0

12 PLL_DO(MI) Serial data from PLL I 5.3 5.3 5.3

13 PLL_CLK Serial clock for PLL O 5.1 5.1 5.1

14 PLL_CE Chip enable for PLL O 0 0 0

15 CD_RESET Reset for CD deck O 5.1 5.1 5.1

16 SUB_SI Serial data to Display

17 CD_IN Disc-in detection I 5.1 5.1 5.1

18 SUB_SO Serial data from Display

19 CH_DATA /

XM_SO/UP_SO

20 CH_CLK/

UP_CLK

21 Vdd +5V power supply I 5.1 5.1 5.1

22 XM_SI(MO)/

UP_SI

23 CD_SI(MO) Serial data to CD deck SO 0 0 5.2

24 CD_SCLK Serial clock for CD deck SCK 5 5 5.3

25 CONDENSOR Capacitor connection

26 CD_SO(MI) Serial data from CD deck SI 0 0 5.5

27 CH_STB Strobe from Changer INT 0 0 0

28 CH_REM_OUT Remote control codes to

29 DECK_V_CONT Power control for CD deck O 5.1 5.1 5.1

30 REMO_INT Interrupt for remote

31 CD_FS Frame sync. for CD deck O 5.1 5.1 5.1

32 Avdd +5V power supply I 5.1 5.1 5.1

33 AVREF +5V power supply I 5.1 5.1 5.1

34 AVGND GND I 0 0 0

35 AVSS GND I 0 0 0

36 SD FM/AM signal level meter A/D 2.48 2.96 0

37 INIT_A Model setting A by

38 INIT_B Model setting B by

39 A_IN Spectrum analyzer data A/D 0 0 0

40 Vss GND I 0 0 0

41 SYS_ID1 Hub connection

42 SYS_ID2 Hub connection

43 HUB_EVENT Bluetooth incoming

44 HUB_CNT Request of hub

45 CD_SW1 Disc detection switch 1 I 5.2 5.2 5.2

46 CD_SW2 Disc detection switch 2 I 0 0 0

47 MOD0 Operating mode control 0

48 MOD1 Operating mode control 1

49 MOD2 Operating mode control 2

50 H_STANDBY Standby control

for Display

electronic volume

electronic volume

CPU

CPU

XM SO/UP SO SI 5.3 5.3 5.3

Serial clock for

Changer or Flash writer

Serial data to

Satellite or Flash writer

for power

Changer

control

voltage level

voltage level

device detection ID 1

device detection ID 2

detection

connection check

from Flash writer

pulled up to H

from Flash writer

from external

O 5.1 5.1 5.1

I/O 5.1 5.1 5.1

O 5.2 5.2 5.2

SO 5.7 5.7 5.7

SI 5.8 5.8 5.8

SCK 5.3 5.3 5.3

SO 5.1 5.1 5.1

3.4 3.4 3.4

O 5.1 5.1 5.1

INT 5.1 5.1 5.1

A/D 1.76 1.76 1.76

A/D 0 0 0

I 0 0 0

I 5.1 5.1 5.1

I 0 0 0

O 5.2 5.2 5.2

I 5.2 5.2 5.2

I 5.2 5.2 5.2

I 0 0 0

I 5.2 5.2 5.2

Pin

No.

100 NC/EP_CS Not connected I 0 0 0

Port Description I/O FM AM CD

51 DCDC_CONT Not connected O 0 0 0

52 FP_MOTOR1 Open/Close of Front

53 FP_MOTOR2 Open/Close of Front

54 V_CONT1 Reference voltage control

55 REMO_1 Remote control data IN 5.1 5.1 5.1

56 SA_CLK Spectrum analyzer clock O 5.1 5.1 5.1

57 EXT_MUTE Pulled up to H I 5.1 5.1 5.1

58 AMP_CONT Power control for

59 BZ_OUT Buzzer signal PPG 0 0 0

60 (8403)OEL_

VCONT

(Other)NC O

61 WOW_MODE1 SRS WOW mode 1 O 0 0 0

62 WOW_MODE2 SRS WOW mode 2 O 0 0 0

63 WOW_MODE3 SRS WOW mode 3 O 0 0 0

64 DIM1 Dimmer control 1 O 0 0 0

65 DIM2 Dimmer control 2 O 0 0 0

66 MAIN_CNT2 Power control for Hub O 0 0 0

67 SRC_KEY SOURCE key detection INT/I5.1 5.1 5.1

68 PANEL_IN Panel attachment

69 NC Not connected O 0 0 0

RDS_CLK INT

70 NC

(DCDC_FRQ)

71 NC Not connected O 0 0 0

RDS_DATA I

72 MAIN_CONT Main power control O 5.2 5.2 5.2

73 INV_CONT Dimmer power control O 5.2 5.2 5.2

74 AF_MUTE Audio mute O/I 5.2 5.2 5.2

75 RESET Reset I 5.2 5.2 5.2

76 FOCUS_ELV Focus elevation for

77 X1A Oscillator clock O 5.2 5.2 5.2

78 X0A Oscillator clock I 1.9 1.9 1.9

79 Vss GND I 0 0 0

80 X1 Crystal oscillator clock I 3.2 3.2 3.2

81 X2 Crystal oscillator clock O 4.4 4.4 4.4

82 Vdd +5V power supply I 5.3 5.3 5.3

83 P00 Pulled down to L I 0 0 0

84 P01 Pulled up to H I 5.2 5.2 5.2

85 OFFSET_DET Audio clipping level

86 STBY Standby for Power amp. O 5.2 5.2 5.2

87 (7703)MUTE Mute for Power amp. O 5.2 5.2 5.2

88 ILL_SENS Pulled up to H I 5.2 5.2 5.2

89 (7703)HB_AM Not connected O 0 0 0

90 NC/

EP_DO(MI)

91 NC/

EP_DI(MO)

92 NC/EP_CLK Not connected O 0 0 0

93 SUB_RESET Reset for display CPU O 5.1 5.1 5.1

94 DISPM_CONT 5V power control for

95 NC Not connected O 0 0 0

96 NC Not connected O 0 0 0

97 NC Not connected O 0 0 0

98 S_LED Security LED drive O 0 0 0

99 ANT_CONT Power control for

panel 1

panel 2

for motor driver

external Amplifier

Not connected O 0 0 0

detection

Not connected O 0 0 0

SRS WOW

detection from Power amp.

EPROM comuni. data input O/I 0 0 0

Not connected O 0 0 0

Display

antenna motor

O 5.1 5.1 5.1

O 5.1 5.1 5.1

O 0 0 0

O 5.1 5.1 5.1

I 0 0 0

O 0 0 0

I 5.2 5.2 5.2

O/I 0 0 0

O 5.1 5.1 5.1

12

11.2. Display Block

CQ-C7305N

IC900:YEAMB90488BP

Pin

No.

10 P32/A02/

11 P33/A03/

12 P34/A04/

13 P35/A05/

14 P36/A06/

15 P37/A07/

16 P40/A08/

17 P41/A09/

18 P42/A10/

19 P43/A11/

20 P44/A12/

21 VCC +3.3v power supply -- 3.5

22 P45/A13/

23 P46/A14/

24 P57/A15/

25 P70/SIN0 Serial data from Main CPU or

26 P71/SOT0 Serial data from Main CPU or

27 P71/SCK0 External Flash rewriting switch I 3.5

28 P73/TIN0 NC O 29 P74/TOT0 Flash reset O 3.5

30 P75/PWC2 Key scan 1 I 0

31 P76/SCL NC O 32 P77/SDA NC O 33 AVCC +3.3 Power supply -- 3.5

34 AVRH +3.3 Power supply -- 3.5

35 AVSS/AVRL GND -- 0

36 P60/AN0 Key matrix setting I 3.5

37 P61/AN1 Key scan 2 I 0

38 P62/AN2 Key scan 3 I 0

39 P63/AN3 NC O 40 VSS GND -- 0

41 P64/AN4 Key-in return 5 I 0

42 P65/AN5 Key-in return 4 I 0

43 P66/AN6 Key-in return 3 I 0

44 P67/AN7 Key-in return 2 I 0

45 P80/IRQ0 NC I 0

46 P81/IRQ1 NC I 3.8

47 MD0 MODE SET 0 I 3.5

48 MD1 MODE SET 1 I 3.5

49 MD2 MODE SET 2 I 0

50 P82/IRQ2 NC O 51 P83/IRQ3 Volume-up detection from

Port Description I/O (V)

1 P22/A18 A18 in Address bus O 3.5

2 P23/A19 A19 in Address bus O 3.5

3 P24/A20/

PPG0

4 P25/A21/

PPG1

5 P26/A22/

PPG2

6 P27/A23/

PPG3

7 P30/A00/

AIN0

8 P31/A01/

BIN0

9 VSS GND -- 0

ZIN0

AIN1

BIN1

ZIN1

PWC0

PWC1

SIN2

SOT2

SCK2

MT00

MT01

EXTC

OUT4

OUT5

A20 in Address bus O 3.5

NC O -

LED_G Control O 0.7

LED_B Control O 0.7

LCD driver data command

distinction terminal

A0 in Address bus O 3.5

A1 in Address bus O 3.5

A2 in Address bus O 3.5

A3 in Address bus O 3.5

A4 in Address bus O 3.5

A5 in Address bus O 3.5

A6 in Address bus O 0

A7 in Address bus O 3.5

A8 in Address bus O 0

A9 in Address bus O 0

A10 in Address bus O 3.5

A11 in Address bus O 3.5

A12 in Address bus O 3.2

A13 in Address bus O 3.2

A14 in Address bus O 3.2

Flash writer

Flash writer

Rotary encoder

0 3.5

O 3.2

O 3.5

I 3.2

Pin

No.

52 P84/IRQ4 Volume-down detection from

53 P85/IRQ5 NC O 54 P86/IRQ6 NC O 55 P87/IRQ7 NC O 56 P90/SIN1/CS0NC O -

57 P91/SOT1/CS1NC O -

58 P92/SCK1/

59 P93/FRCK/

60 PN94/PPG4 LED_R Control O 0.7

61 PN95/PPG5 NC O 62 P96/IN0 NC O 63 P97/IN1 NC O 64 PA0/OUT0 Power control for LCD O 3.5

65 PA1/OUT1 NC O 66 PA2/OUT2 NC O 67 PA3/OUT3 NC O 68 P50/ALE NC O 69 P51/RDX output enable for Flash memory O 3.4

70 P52/WRLX Write strobe for LCD O 3.4

71 P53/WRHX Write enable O 3.4

72 P54/HRQ NC O 73 P55/HAKX Reset for LCD O 3.4

74 P56/RDY Ready/Busy from Flash memory I 3.4

75 RSTX RESET I 3.5

76 P57/CLK NC O 77 X1A NC O 78 X0A NC I 79 VSS GND -- 0

80 X0 System clock (12.5MHZ) I 3.2

81 X1 System clock (12.5MHZ) O 3.2

82 VCC +3.3 Power supply -- 3.5

83 P00/AD00/D00D0 in Address bus I 3.8

84 P01/AD01/

85 P02/AD02/

86 P03/AD03/

87 P04/AD04/

88 P05/AD05/

89 P06/AD06/

90 P07/AD07/

91 P08/AD08/

92 P09/AD09/

93 P10/AD10/

94 P11/AD11/

95 P12/AD12/

96 P13/AD13/

97 P14/AD14/

98 P15/AD15/

99 P20/A16 A15 in Address bus O 3.8

100 P21/A17 A16 in Address bus O 3.8

Port Description I/O (V)

Rotary encoder

CS2

ADTG/CS3

D01

D02

D03

D04

D05

D06

D07

D08

D09

D10

D11

D12

D13

D14

D15

chip enable for Flash memory O 3.5

LCD chip select O 3.5

D1 in Address bus I 3.8

D2 in Address bus I 3.8

D3 in Address bus I 3.8

D4 in Address bus I 3.8

D5 in Address bus I 3.8

D6 in Address bus I 3.8

D7 in Address bus I 3.8

D8 in Address bus I/O 3.8

D9 in Address bus I/O 3.8

D10 in Address bus I/O 3.8

D11 in Address bus I/O 3.8

D12 in Address bus I/O 3.8

D13 in Address bus I/O 3.8

D14 in Address bus I/O 3.8

D15 in Address bus I/O 3.8

I 3.2

13

CQ-C7305N

11.3. CD Servo Block

IC101 : MN6627971TA

Pin

No.

10 P85 CDMUT 0 3.3

11 P84 N.C. - 12 NPWDOWN NPWDOWN 1.2 1.2

13 DVSS3 DVSS3 0 0

14 SRAMVDD SRAMVDD 1.5 1.5

15 REGOUT REGOUT 1.5 1.5

16 REGVDD REGVDD 3.3 3.3

17 REGON2 REGON2 3.3 3.3

18 P83 N.C. - 19 P82 NPWDOWN 3.3 3.3

20 P81 N.C. - 21 P80 SEQIN 0 0

22 P34 DI/DO 0 0

23 P35 SK 0 0

24 P36 CS 0 0

25 P37 N.C. 0 0

26 P44 LD-MT 0 0

27 P45 LD-EJ 3.2 3.2

28 P46 CNT 3.2 3.2

29 P47 /RST 3.2 3.2

30 P60 STREQ 0 0

31 P61 STCLK 0 0

32 P62 STIN 0 0

33 P63 N.C. 0 0

34 P64 N.C. 0 0

35 P65 N.C. 0 0

36 P66 N.C. 0 0

37 P67 N.C. 0 0

38 SDRCK SDRCK - 39 A11 N.C. - 40 A9 N.C. - 41 A8 N.C. - 42 A7 N.C. - 43 A6 N.C. - 44 A5 N.C. - 45 A4 N.C. - 46 NEW N.C. - 47 NCAS N.C. - 48 NRAS N.C. - 49 A3 N.C. - 50 A2 N.C. - 51 A1 N.C. - 52 A0 N.C. - 53 A10 N.C. - 54 DVSS1 DVSS1 0 0

55 IOVDD1 IOVDD1 3.3 3.3

56 DVDD1 DVDD1 1.5 1.5

57 FVDD FVDD 0 0

58 N.C. N.C. 0 0

59 REGON REGON 3.3 3.3

60 SPOUT SPOUT - 1.65

61 SPPOL SPPOL - 62 TRVP TRVP - 1.65

63 P40 N.C. 0 0

64 N.C. N.C. - 65 TRVP2 TRVP2 0 0

66 P41 N.C. 0 0

67 TRP TRP - 1.65

68 P42 N.C. 0 0

69 FOP FOP - 1.65

Port Description Play(V) Stop(V)

1 P96 SW1 0.2 0.2

2 P95 RESET_SW 3.3 3.3

3 P94 LD-MON 2.1 2.2

4 P93 TEST1 0 0

5 P92 TEST2 0 0

6 P91 TEST3 0 0

7 P90 TEST4 0 0

8 P87 MON1 - 9 P86 MON0 - -

Pin

No.

70 P43 N.C. 0 0

71 AVSS2 AVSS2 0 0

72 OSCIN OSCIN 1.65 1.65

73 CTRCRS CTRCRS 1.6 1.6

74 VREF VREF 1.65 1.65

75 E E *2.1 1.65

76 F F *2.1 1.65

77 D D *1.8 1.65

78 B B *1.8 1.65

79 C C *1.8 1.65

80 A A *1.8 1.65

81 PD PD 0.17 0

82 LD LD 2.5 3.3

83 CENV CENV 1.9 1.5

84 RFENV RFENV 1.7 1.7

85 RFOUT RFOUT *1.1 1.6

86 RFIN RFIN *1.8 1.8

87 AVDD2 AVDD2 3.3 3.3

88 ARFDC ARFDC 1.1 1.1

89 ARFOUT ARFOUT *1.2 1.2

90 ARFFB ARFFB *1.25 1.25

91 ARFIN ARFIN *1.6 0

92 DSLF DSLF 1.6 0

93 IREF IREF 0.8 0

94 PLLF PLLF 1.4 0

95 PLLF0 PLLF0 1.4 0

96 VCOF VCOF 0 0

97 OUTL OUTL - 1.65

98 AVSS1 AVSS1 0 0

99 AVREF AVREF 1.65 1.65

100 AVDD1 AVDD1 3.3 3.3

101 OUTR OUTR - 1.65

102 TEST TEST 0 0

103 CSEL CSEL 0 0

104 PWMSEL PWMSEL 3.3 3.3

105 SRVMONON SRVMONON 0 0

106 SEQMODE SEQMODE 0 0

107 NRST NRST 3.3 3.3

108 IOVDD2 IOVDD2 3.3 3.3

109 X1 X1 16.9MHz 16.9MHz

110 X2 X2 16.9MHz 16.9MHz

111 SVSS2 SVSS2 0 0

112 MX1 MX1 0 0

113 MX2 MX2 - 114 IOVDD3 IOVDD3 3.3 3.3

115 MXSEL MXSEL 0 0

116 P00 CDSO 3.3/0 3.3/0

117 P01 CDSI 3.3/0 3.3/0

118 P02 CDCK 3.3/0 3.3/0

119 P03 OCDD 3.3 3.3

120 P04 OCDCK 3.3 3.3

121 OCDSEL OCDSEL 3.3 3.3

122 P15 STAT - 123 P16 MDATA - 124 P17 MCLK - 125 P20 MLD 3.3 3.3

126 P21 CDFS 3.3/0 3.3/0

127 DVDD2 DVDD2 3.3 3.3

128 P97 SW2 0.2 0.2

Port Description Play(V) Stop(V)

14

Loading...

Loading...