OKI MSM6255GS-BK, MSM6255GS-K Datasheet

E2B0039-27-Y2

¡ Semiconductor

This version: Nov. 1997

Previous version: Mar. 1996

MSM6255¡ Semiconductor

MSM6255

DOT MATRIX LCD CONTROLLER

GENERAL DESCRIPTION

The MSM6255 is a CMOS si-gate LSI designed to display characters and graphics on a DOT

MATRIX LCD panel.

FEATURES

• Display control capacity

– Graphic mode : 512,000 dots (216 bytes)

Memory address MA0 to MA

– Character mode : 65,536 characters (216 bytes)

Display address MA0 to MA

• Direct interface with 8085 or Z80 CPU

• Duty : 1/2 to 1/256 selectable

• Attributes

– Screen clear

– Cursor ON/OFF/blink

• Scrolling and paging

• Display system : AC inversion at each frame

• Data output (upper and lower display outputs)

4-bit parallel output, 2-bit parallel output, 1-bit serial output

• Crystal oscillation/external clock selectable

• Single +5V power supply

• Package options:

80-pin plastic QFP (QFP80-P-1420-0.80-K) (Product name: MSM6255GS-K)

80-pin plastic QFP (QFP80-P-1420-0.80-BK) (Product name: MSM6255GS-BK)

15

15

1/39

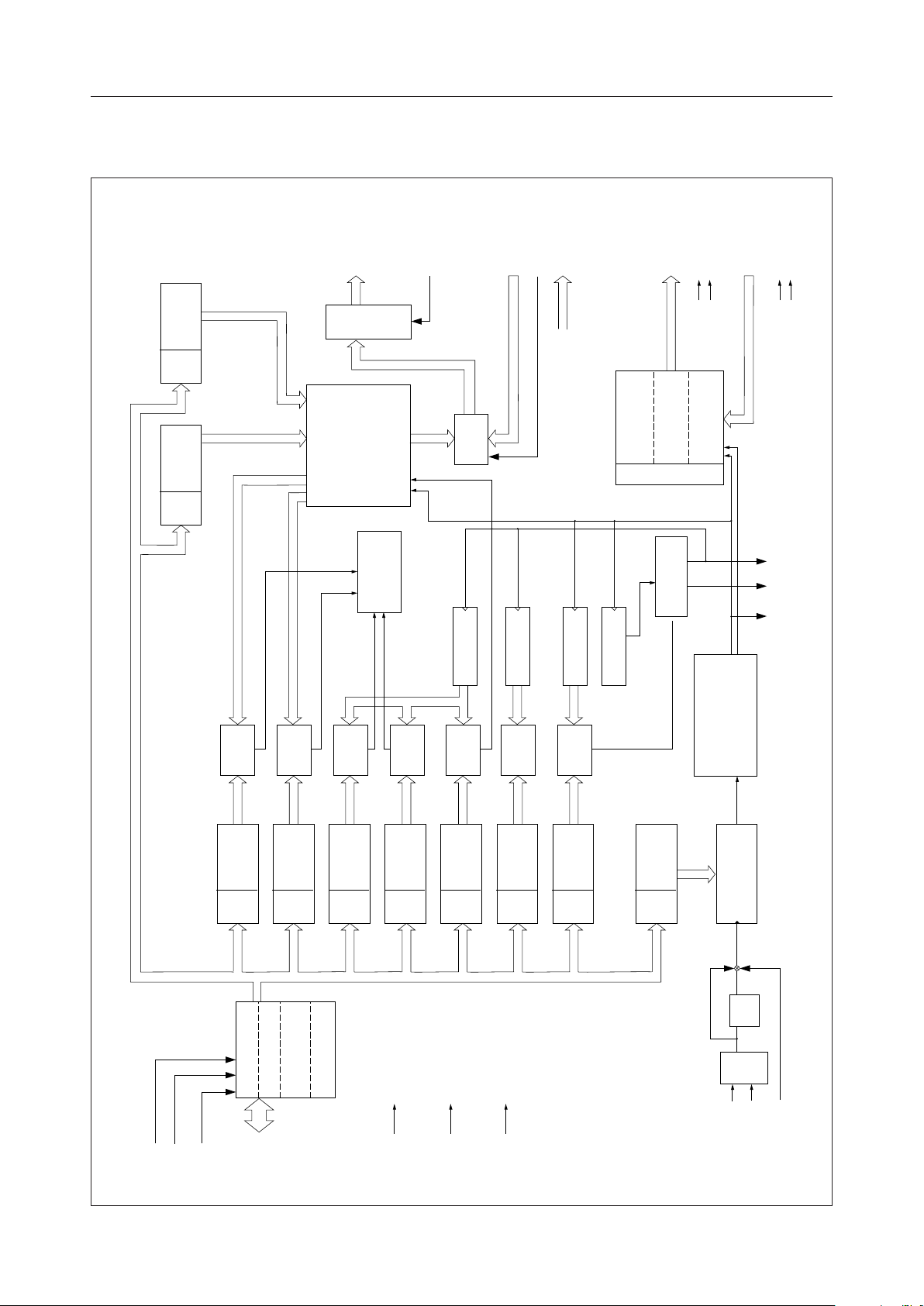

BLOCK DIAGRAM

MSM6255¡ Semiconductor

Start

Start

address

(upper)

SUAR

address

(lower)

SLR

15

- MA

0

MA

Linear

address

3-state

output

counter

Cursor

generation

circuit

ADF

MPX

counter

p

V

15

- A

0

A

DIEN

Duty counter

3

- RA

0

RA

Raster

address

Character

Shift clock sus-

counter

3

- UD

- LD

0

UD

LD

2-bit parallel

output

4-bit parallel

output

Timing

control

pension counter

3

0

CLP

8-bit parallel/

φ

CE

serial

φ

CH

7

- RD

0

RD

FRP

BUSY LIP

φ

CH

FRMB

RD

WR

CS

CMP

Cursor

address

CUP

Input register

7

- DB

0

DB

CMP

Cursor

address

CLR

Output register

R/W control

Instruction

register

CMP

Cursor

position

CPR

(upper)

CMP

Cursor

position

CPR

RES

(lower)

CMP

p

Number

of V

DPR

DD

V

CMP

Number

of duty

DUR

SS

V

CMP

Number of

characters hori-

zontal direction

HNR

p

Number

of H

PR

Timing generator

circuit for CHφ

PS and Load

Dot counter

Q

T

OSC

XT

XT

DIV

2/39

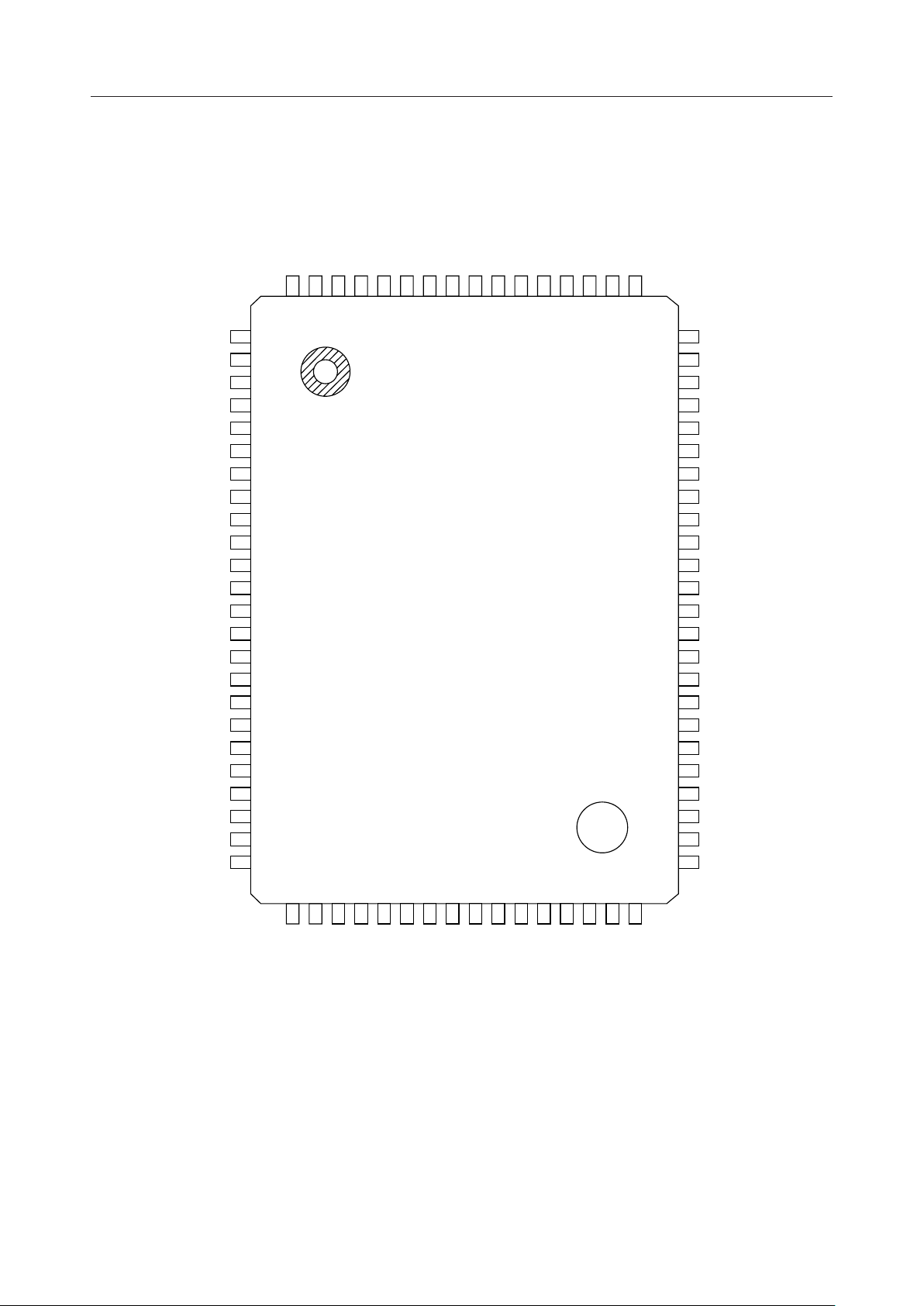

PIN CONFIGURATION (TOP VIEW)

10

6

MA

80

MA

79

9MA8

7

MA

MA

78

76

77

11

MA

75

12

MA

74

13

MA

73

14

MA

72

15

MA

71

DIV

70

2

TEST

69

1

TEST

68

V

67

SS

XT

66

MSM6255¡ Semiconductor

XT

65

MA

MA

MA

MA

MA

MA

A

A

A

A

A

A

FRP

LIP

1

5

2

4

3

3

4

2

5

1

6

0

7

15

8

14

9

13

10

12

11

11

12

10

13

A

9

14

A

8

15

A

7

16

A

6

17

A

5

18

A

4

19

A

3

20

A

2

21

A

1

22

A

0

23

24

64

RA

63

RA

62

RA

61

RA

60

RD

59

RD

58

RD

57

RD

56

RD

55

RD

54

RD

53

RD

52

DB

51 DB

50

DB

49

DB

48

DB

47

DB

46

DB

45

DB

44

RES

43

WR

42

RD

41

CS

3

2

1

0

7

6

5

4

3

2

1

0

7

6

5

4

3

2

1

0

25

CEf

26

CLP

31

30

29

28

27

3

2

1

0

LD

LD

LD

LD

FRMB

80-Pin Plastic QFP

32

V

DD

33

0

UD

34

1

UD

35

2

UD

36

3

UD

37

CHf

39

38

DIEN

BUSY

40

ADF

3/39

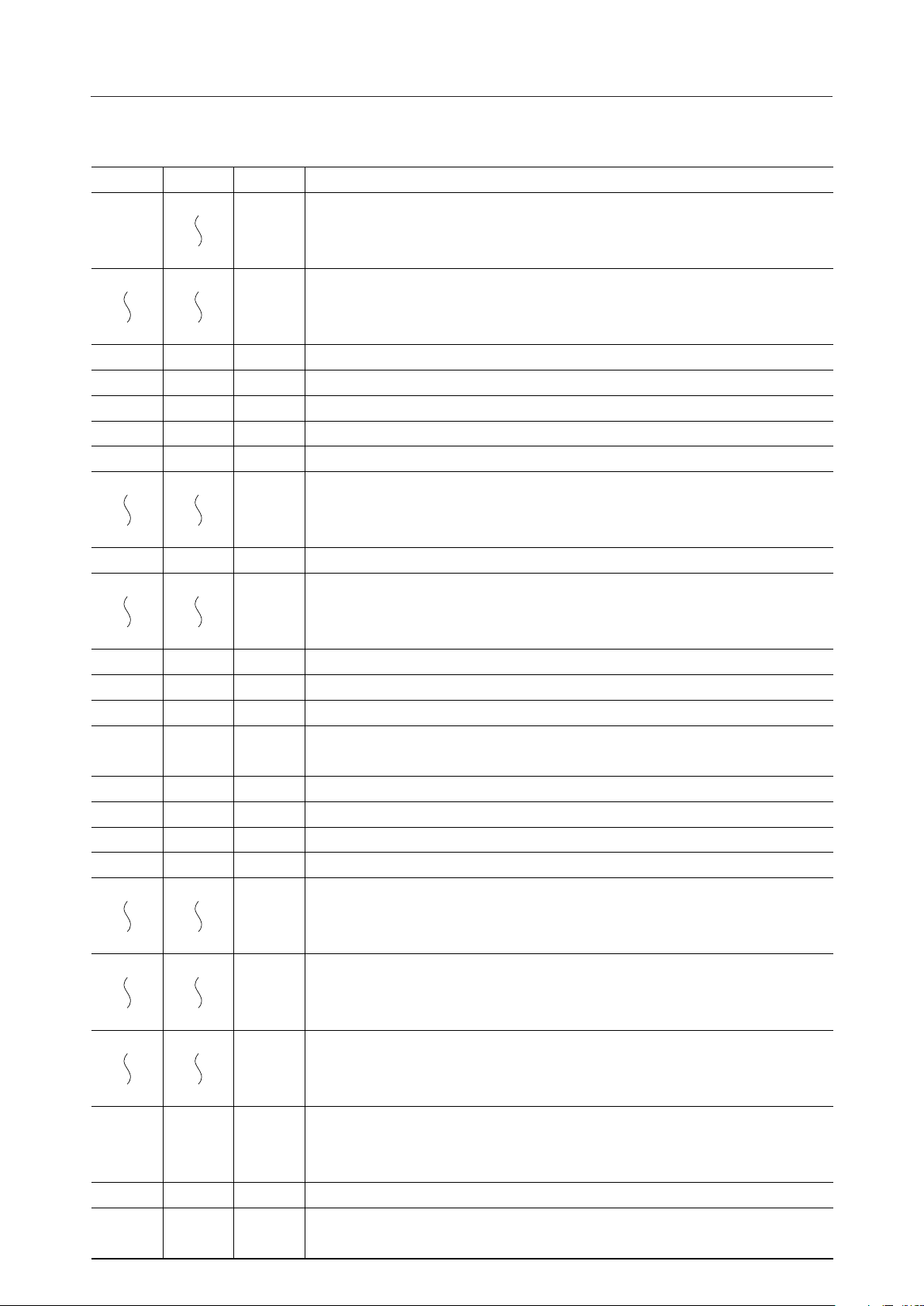

PIN DESCRIPTIONS

Pin Symbol Type Description

1 - 6

71 - 80

7

22

23 FRP O

24 LIP O

25 CE

26 CLP O

27 FRMB O

28

31

32 V

33

36

37 CH

38 Busy O

39 DIEN I

40 ADF I

41 CS I

42 RD I

43 WR I

44 RES I

45

52

53

60

61

64

65

66

67 V

70 DIV I

MA

MA

A

LD

LD

UD

UD

DB

DB

RD

RD

RA

RA

A

DD

XT

XT

SS

15

0

O

15

0

Address output for displaying RAM.

MA

- MA15 are high impedance when ADF = "L".

0

Memory address input pins

I

Frame signal. Synchronization of display

Display data latch signal

φ

O

Chip enable clock for LCD segment driver

Display data shift clock

Alternate signal output pin

0

O

3

O

0

O

3

φ

O

Display data parallel output for lower side

Supply voltage

Display data parallel output, Upper display 4-bit output

(OD1, ED1, OD2 and ED2 outputs)

Character clock

Ready state signal. This signal is used while serial transmission stops.

Display enable signal. When this signal is "H", display is enabled.

Address floating input. When this signal is "L", MA0 - MA15, RA0 - RA3 are high impedance,

and when it is "H", A0 - A15 or a refresh address is output to MA0 - MA15.

Chip select. CS = "L"

Read. Reading data is valid when RD = "L"

Write. Data is written when WR = "H"

Reset. Resets each counter.

0

I/O

7

0

7

0

O

3

8-bit data bus. Common pins for 3-state I/O.

ROM/RAM data input. Dot pattern data for the character generator

I

Raster address output.

*This output is not used in the graphic mode.

RA

- RA3 are high impedance when ADF = "L".

0

I

X’tal osc. When an external clock is used by setting DIV to "H", feeds it to XT.

O

—

Ground pin.

"H" : EXT clock

"L" : Self oscillation

MSM6255¡ Semiconductor

4/39

ABSOLUTE MAXIMUM RATINGS

Parameter Symbol Condition Rating Unit

Supply Voltage V

Input Voltage V

Storage Temperature T

DD

I

STG

Ta = 25°C –0.3 to +6 V

Ta = 25°C –0.3 to V

— –50 to +150 °C

RECOMMENDED OPERATING CONDITIONS

Parameter Symbol Condition Range Unit

Supply Voltage V

Operating Temperature T

Operating Frequency f

DD

op

osc

VSS = 0V 4.5 to 5.5 V

— –20 to +85 °C

VDD = 5V ±10% 0 to 11 MHz

ELECTRICAL CHARACTERISTICS

DD

MSM6255¡ Semiconductor

V

Input Characteristics

= 5V ± 5%, Ta = –20 to +85°C)

(V

DD

Parameter Symbol Min. Typ. Max. Unit Applicable pin

"H" Input Voltage V

"L" Input Voltage

"H" Input Voltage

"L" Input Voltage

"H" Input Current DB

"L" Input Current

"H" Input Current

"L" Input Current

IH

V

IL

V

IH

V

IL

I

IH

I

IL

I

IH

I

IL

2.4 — — V DB0 - DB7, CS, RD, WR, A0 - A15,

— — 0.7 V

DIEN, ADF, RD0 - RD7

4.5 — — V

RES, DIV, XT

— — 1.0 V

—— 1 mA

——–1mA

- DB7, CS, RD, WA, A0 - A15,

0

DIEN, ADF, RD

- RD7, RES, DIV

0

25 — 100 mA

TEST1, TEST2

——–1mA

Output Characteristics

= 5V ± 5%, Ta = –20 to +85°C)

(V

DD

Parameter Symbol Min. Typ. Max. Unit Applicable pin

"H" Output Current

"L" Output Current

I

OH

I

OL

Condition

V

= 2.8V

OH

V

= 0.4V

OL

–500 — — mA

2.4 — — mA

CHφ, CEφ, LIP, FRP

FRMB, BUSY, CLP

- LD

LD

0

UD0 - UD

MA0 - MA

RA0 - RA

DB

- DB

0

3

3

15

3

7

5/39

Supply Current

= 5V ± 5%, Ta = –20 to +85°C)

(V

DD

Parameter Symbol V

Static Current I

Dynamic Current I

DDS

DD

DD

5f

5f

Condition Min. Typ. Max. Unit

= 0 Hz, no load — — 50 mA

osc

= 10 MHz, no load — — 15 mA

osc

Note: TEST 1 and TEST2 are open, and other inputs are either VDD or GND.

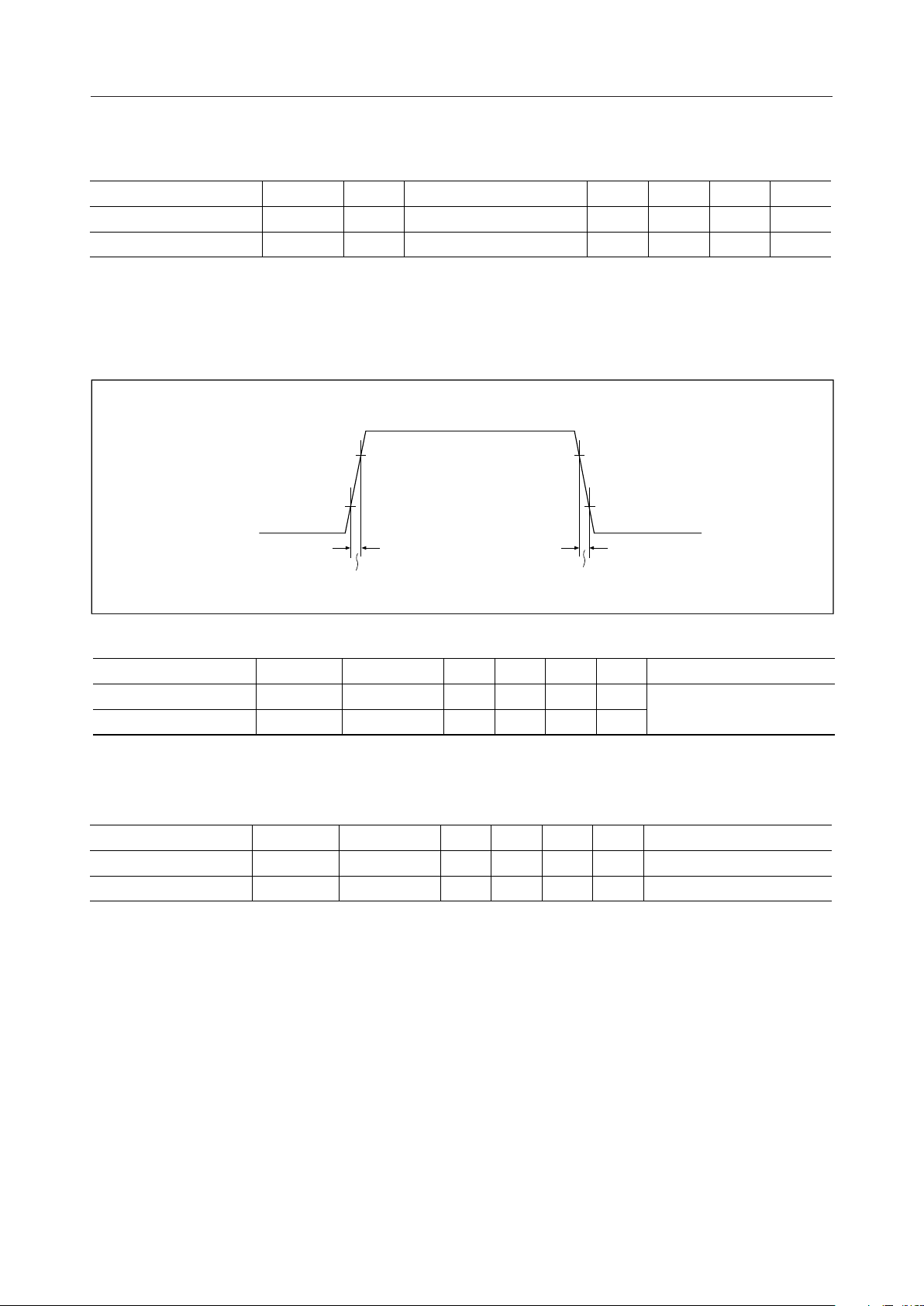

Switching Characteristics

MSM6255¡ Semiconductor

0.8 V

DD

0.2 V

DD

t

r

Parameter Symbol Min. Typ. Max. Unit Applicable pin

Rise Time t

Fall Time t

r

f

Condition

C

= 60 pF

L

— — 100 ns

— — 100 nsCL = 60 pF

0.8 V

t

f

DD

0.2 V

DD

= 5V ± 5%, Ta = –20 to +85°C)

(V

DD

All output pins

Operating Frequency

= 5V ± 5%, Ta = –20 to +85°C)

(V

DD

Parameter Symbol Min. Typ. Max. Unit Notes

Oscillating Frequency f

Basic Clock Frequency f

osc

s

Condition

DIV = "L"

——11MHz

— — 5.5 MHzDIV = "H"

Crystal oscillator

External clock

6/39

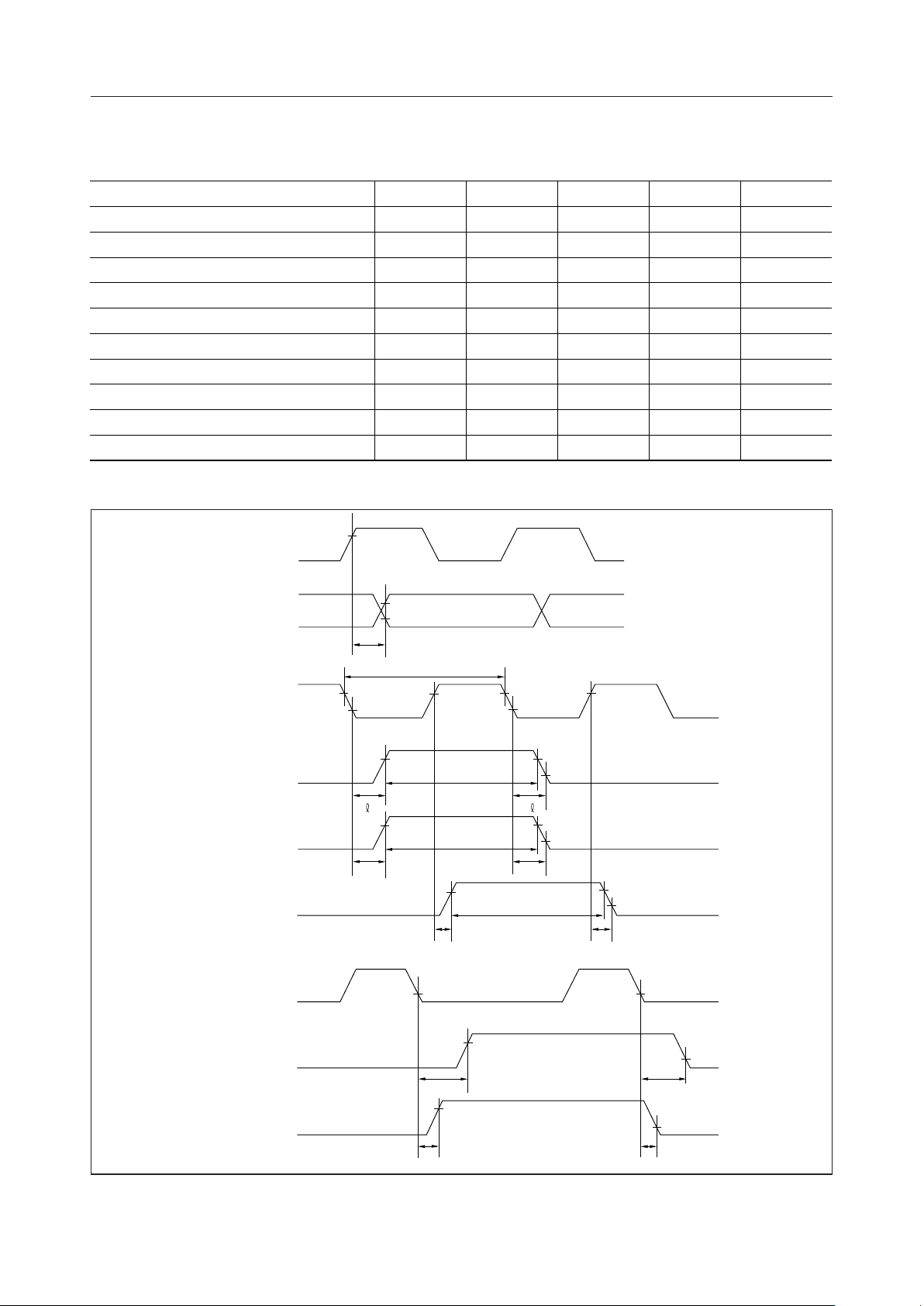

TIMING DIAGRAM

LCDC Control Signal Timing Characteristics

Parameter Symbol Min. Typ. Max. Unit

Clock Cycle Time t

Clock "H" Level Pulse Width P

Clock "L" Level Pulse Width P

Clock Rise/Fall Time t

Character Clock Delay Time t

Memory Address Clock Delay Time t

Memory Address Disable Delay Time t

Memory Address Enable Delay Time t

CPU Address Delay Time t

Refresh Address Delay Time t

Reset "H" Level Pulse Width t

CPU Address Delay Time t

CP

WH

WL

cr/tcf

CH

MA

AD1

AD2

AD3

AD4

RES

AD5

MSM6255¡ Semiconductor

= 30pF, VDD = 5V ± 5%, Ta = –20 to +85°C)

(C

L

180 — — ns

80 — — ns

80 — — ns

——20ns

— — 200 ns

— — 100 ns

——40ns

——40ns

— — 100 ns

— — 100 ns

1——ms

— — 100 ns

XT

(External clock)

CH

φ

MA0 - MA

15

ADF

MA0 - MA

15

RA0 - RA

3

DIEN

MA0 - MA

15

RES

t

CP

P

WL

P

WH

t

cr

Upper Side Address Lower Side Address

Refresh Address CPU Address Refresh Address

t

cf

t

CH

t

MA

VALID VALID

t

AD1

t

AD3

Floating

t

t

AD2

AD4

t

MA

A

- A

0

15

MA0 - MA

t

RES

t

AD5

15

t

AD5

7/39

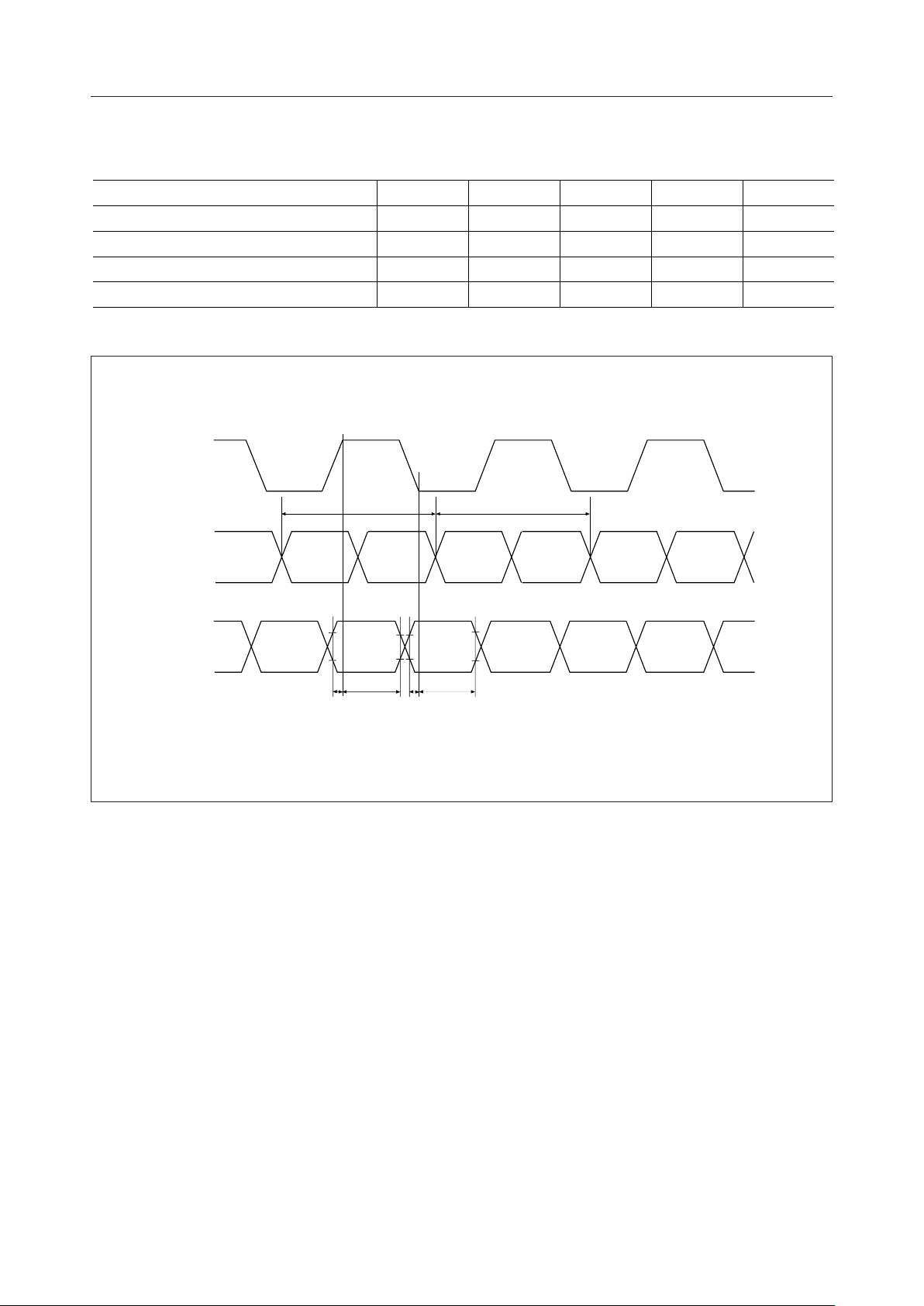

Bus Timing Characteristics

Parameter Symbol Min. Typ. Max. Unit

A

, CS Setup Time t

o

RD, WR Pulse Width t

Address Hold Time t

Data Setup Time t

Data Hold Time t

Output Disable Time t

Access Time t

A0, CS

CS

CW

AH

DS

DH

OH

ACC

MSM6255¡ Semiconductor

= 50pF, VDD = 5V ± 5%, Ta = –20 to +85°C)

(C

L

30——ns

200 — — ns

10——ns

60——ns

20——ns

0 — 40 ns

— — 200 ns

t

AH

WR, RD

- DB

DB

0

(WRITE)

DB

- DB

0

(READ)

t

cs

7

7

t

ACC

t

cw

t

DS

VALID

VALID

t

DH

t

OH

8/39

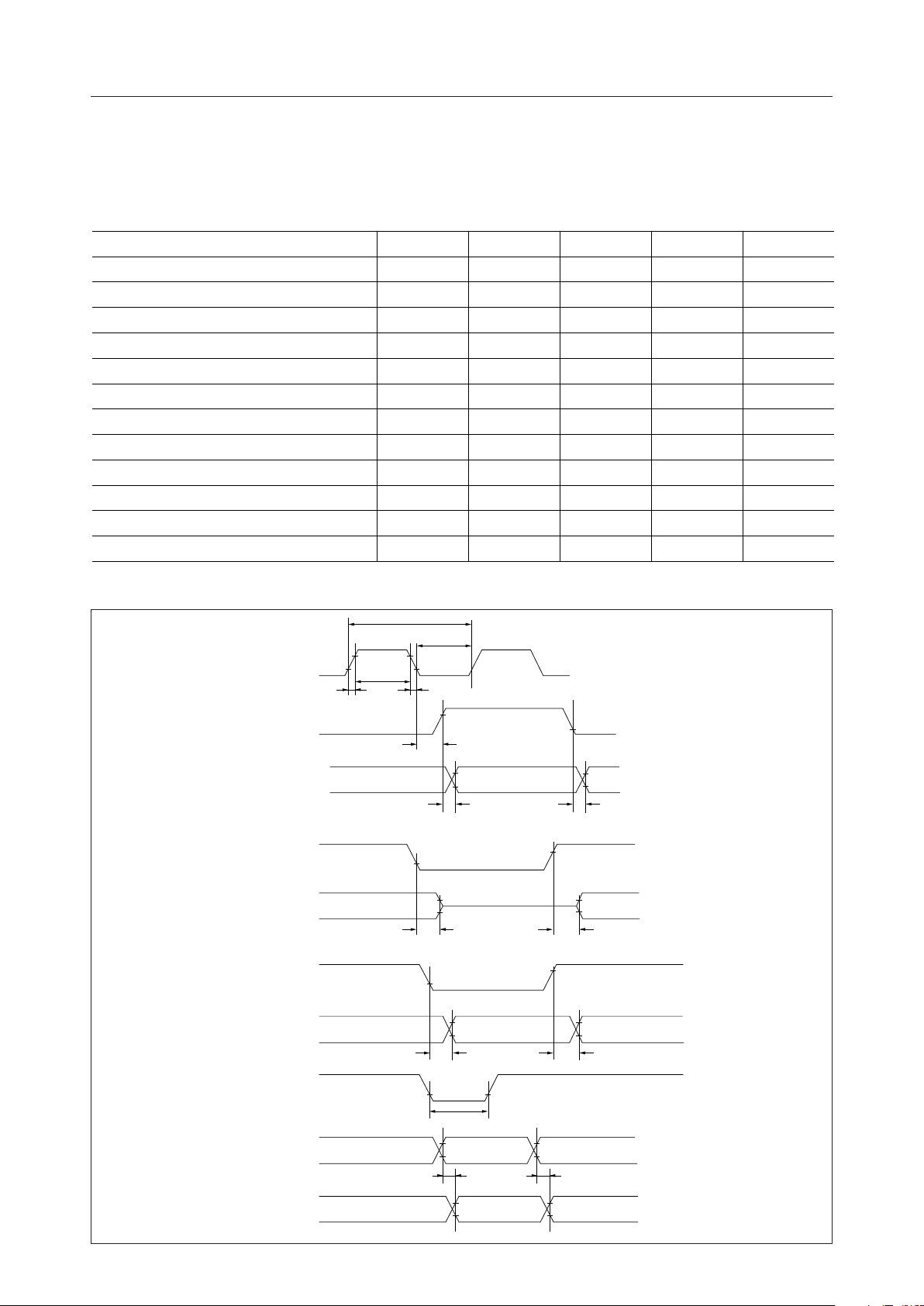

LCDC Driver Interface Timing Characteristics

Parameter Symbol Min. Typ. Max. Unit

Data Delay Time t

1 Character Cycle Time t

Latch Signal Delay Time t

Latch Signal "H" Time t

Chip Enable Clock Delay Time t

Chip Enable Clock "H" Time t

Ready Signal Delay Time t

Ready Signal "H" Time t

Frame Signal Delay Time t

Alternating Frame Signal Delay Time t

DA

CHφ

R

LIP

CE

CEφ

B

BUSY

FRP

FR

MSM6255¡ Semiconductor

(C

= 30pF, VDD = 5V ± 5%, Ta = –20 to +85°C)

L

— — 100 ns

730 — — ns

— — 200 ns

1.46 — — ms

— — 200 ns

730 — — ns

— — 200 ns

5.11 — — ms

2t

CHφ

— — 200 ns

—2t

+200 ns

CHφ

CLP

UD

0

LD

0

CHφ

LIP

CEφ

BUSY

LIP

- UD

- LD

3

3

t

DA

t t

t

CE

t

CHφ

t

LIP

t

CEφ

t

CE

t

BUSY

t

B

t

B

FRP

FRMB

t

FRP

t

FR

t

FRP

t

FR

9/39

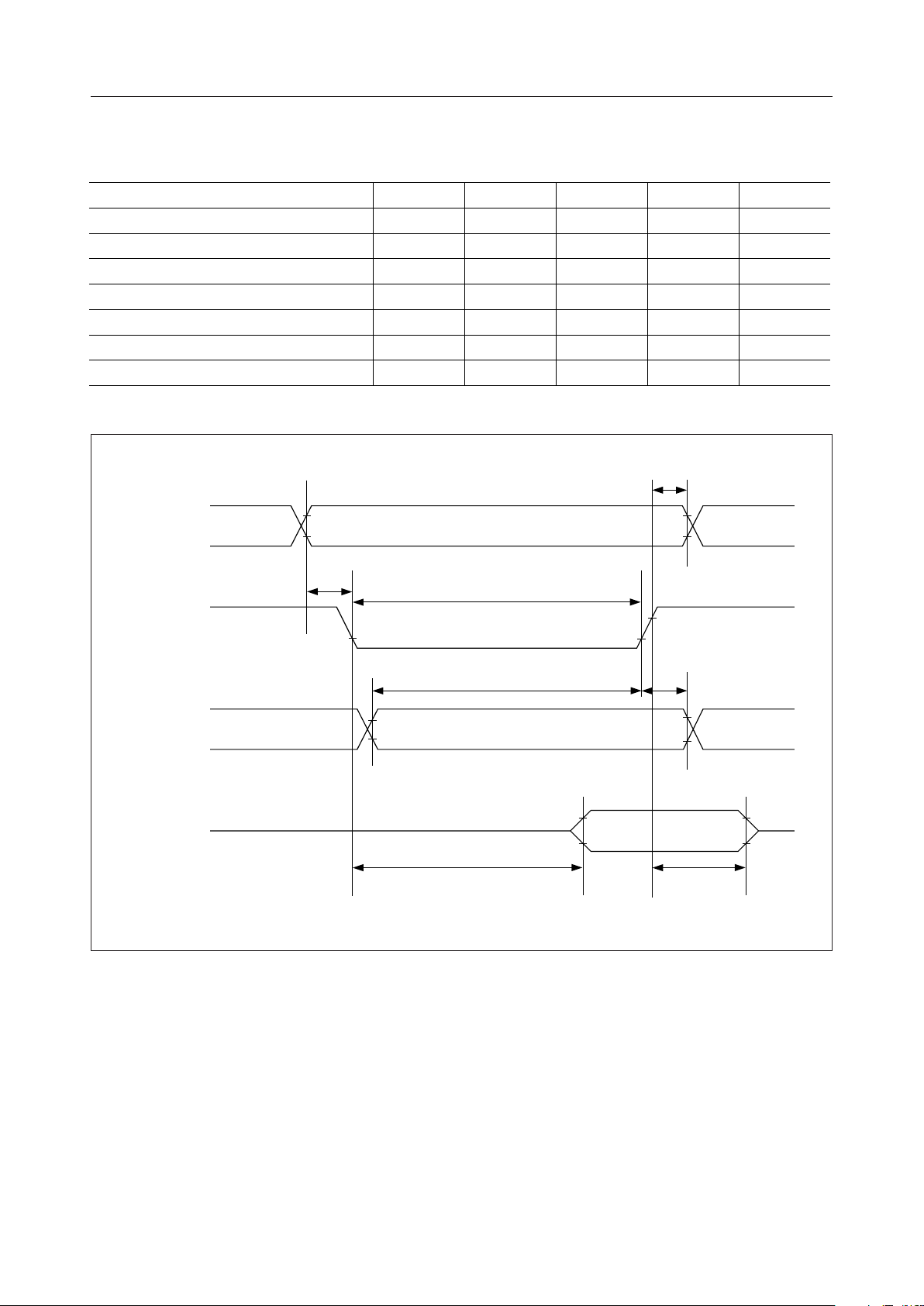

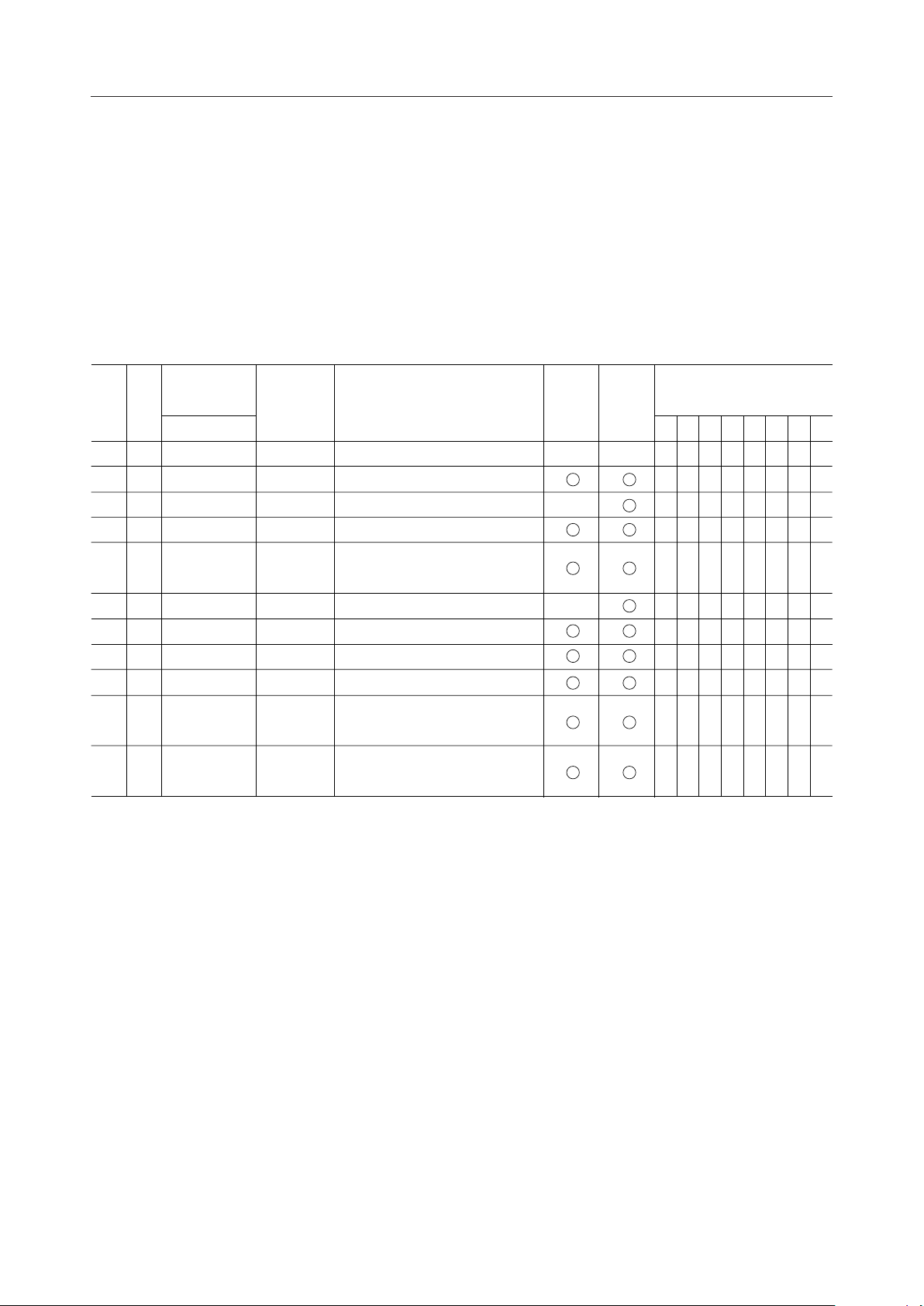

Timing for Fetching Pattern Data

Parameter Symbol Min. Typ. Max. Unit

Upper Side Data Setup Time t

Upper Side Data Hold Time t

Lower Side Data Setup Time t

Lower Side Data Hold Time t

CHφ

qw

UDS

UDH

LDS

LDH

MSM6255¡ Semiconductor

= 5V ± 5%, Ta = –20 to +85°C)

(V

DD

120 — — ns

0——ns

120 — — ns

0——ns

- MA

MA

0

RD0 - RD

15

7

Upper

side

Upper

side data

of q

t

UDS

Lower

side

t

UDH

t

Lower

side data

of q

LDS

Upper

side

t

LDH

Lower

side

Upper

side data

of w

Lower

side data

of w

10/39

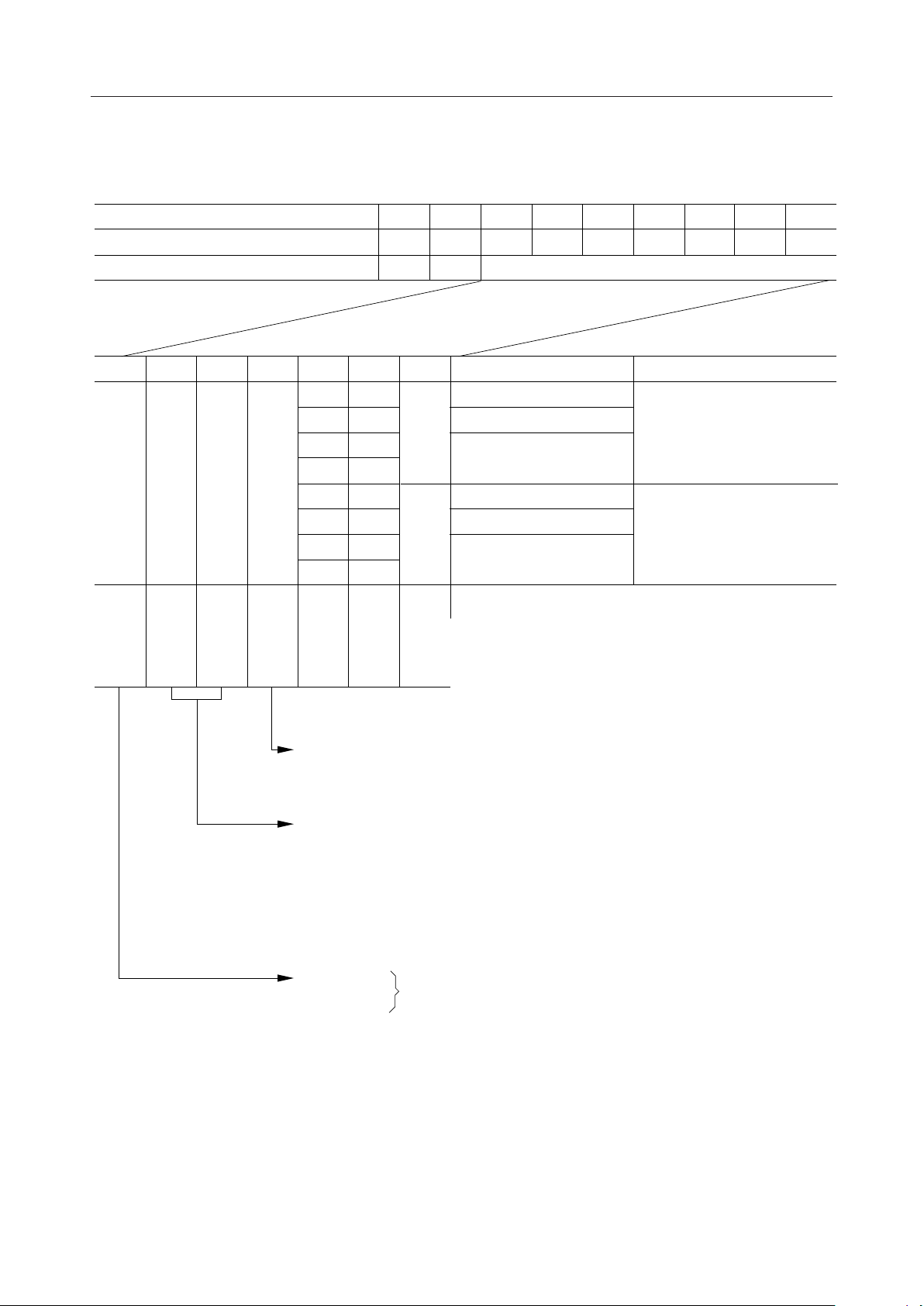

MSM6255¡ Semiconductor

FUNCTIONAL DESCRIPTION

LCDC Internal Registers

The internal registers include one instruction register (IR) and nine data registers. (See Table

1.)

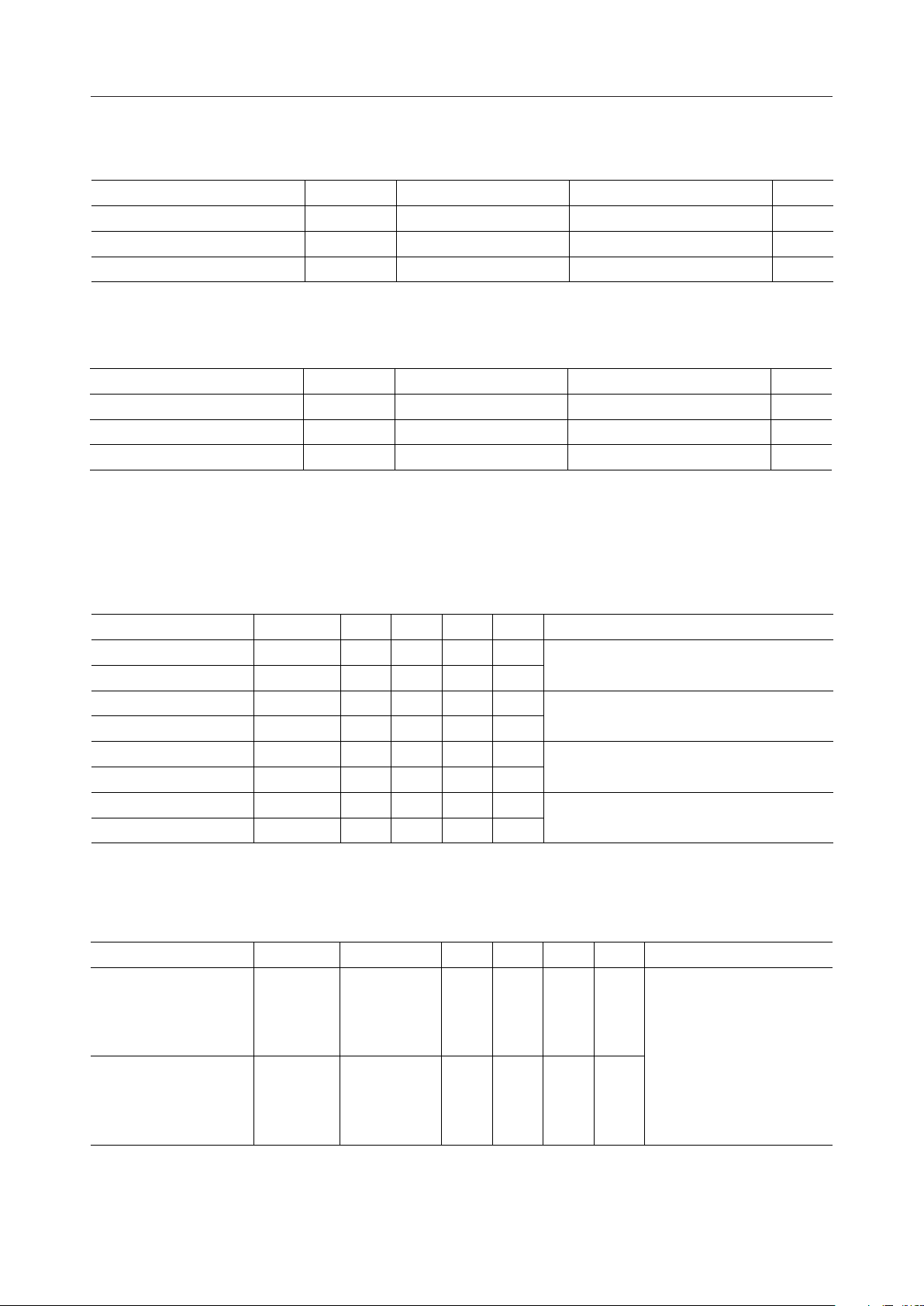

Table 1 MSM6255 Internal Registers

Instruction

CS A

H X Invalid – –

register

0

3 2 1 0

X X X X

X X X XL H Instruction registerIR

L L L LL L Mode control register MOR X

L L L HL L Character pitch registerPR

L L H LL L

L L H HL L Duty number registerDVR

L H L LL L Cursor form registerCPR

L H L HL L

L H H LL L

L H H HL L

H L L LL L

Register Register name

–

HNR

SLR

SUR

CLR

CUR

Horizontal character number

register

Start address (lower) register

Start address (upper) register

Cursor address (lower)

register

Cursor address (upper)

register

X

Note: "L" is read if the data of the registers marked X is read.

WRITEREAD

7

X

X

X

Data bit

5432106

XXX

X

– Instruction register

The instruction register is a register for specifying the address of the data register which is

accessed.

This register is cleared when RES input is "L".

11/39

– Mode control register

The mode control register is specified by writing "00H" in the instruction register.

MSM6255¡ Semiconductor

Register

Instruction register

Mode control register

D

D

6

D

5

D

4

H/L H/L H/L H/L

D

3

LL

HL

XH

XH

LL

HL

XH

XH

A

D

0

D

7

D

6

D

5

D

4

D

3

D

2

D

1

0

HLLLLLL LL

L L MODE DATA

D

2

D

1

0

Output mode

1-bit serial

2-bit parallel

L

Character display

4-bit parallel

1-bit serial

2-bit parallel

H

Graphics

4-bit parallel

Blink time

Cursor

ON/OFF

Cursor blink

Display

ON/OFF

2-bit parallel

4-bit parallel/

1-bit serial

Mode

H: Display ON

L: Display OFF

D

D

5

4

L L Cursor OFF

L H Cursor OFF

H L Cursor ON

H H Cursor blink

H: 16 frames

L: 32 frames

Half of blinking cycle

12/39

Loading...

Loading...