E2B0032-27-Y3

¡ Semiconductor

This version: Nov. 1997

Previous version: Mar. 1996

MSM6222B-xx¡ Semiconductor

MSM6222B-xx

DOT MATRIX LCD CONTROLLER WITH 16-DOT COMMON DRIVER AND 40-DOT

SEGMENT DRIVER

GENERAL DESCRIPTION

The MSM6222B-xx is a dot matrix LCD controller which is fabricated in low power CMOS

silicon gate technology. Character display on the dot matrix character type LCD can be

controlled in combination with a 4-bit/8-bit microcontroller. This LSI consists of 16-dot

COMMON driver, 40-dot SEGMENT driver, display data RAM, character generator RAM,

character generator ROM and control circuit.

The MSM6222B-xx is the equivalent of Hitachi's HD44780. There is, however, a slight difference

between the two devices as described in the table on the last page.

The MSM6222B-xx has the character generator ROM that can be programmed by custom mask.

MSM6222B-01 is a standard version having 160 characters with lowercase (5 x 7 dots), and 32

characters with uppercase (5 x 10 dots) in this ROM.

FEATURES

• Easy interface with an 8-bit or 4-bit microcontroller.

• Dot matrix LCD controller/driver for lowercase (5 x 7 dots) or uppercase (5 x 10 dots).

• Automatic power ON reset.

• COMMON signal drivers (16) and SEGMENT signal drivers (40).

• Can control up to 80 characters when used in combination with MSM5259.

• Character generator ROM for 160 characters with lowercase (5 x 7 dots) and 32 characters with

uppercase (5 x 10 dots).

• Character patterns are programmable by character generator RAM. (Lowercase: 5 x 8 dots,

8 kinds, uppercase: 5 x 11 dots, 4 kinds).

• Oscillation circuit for external resistor or ceralock.

• 1/8 duty (1 line; 5 x 7 dots + cursor), 1/11 duty (1 line; 5 x 10 dots + cursor), or 1/16 duty (2

lines; 5 x 7 dots + cursor), selectable.

• Clear display even at 1/5 bias, 3.0V LCD driving voltage.

• Package options:

80-pin plastic QFP (QFP80-P-1420-0.80-L) (Product name: MSM6222B-xxGS-L)

80-pin plastic QFP (QFP80-P-1420-0.80-BL) (Product name: MSM6222B-xxGS-BL)

xx indicates code number.

1/45

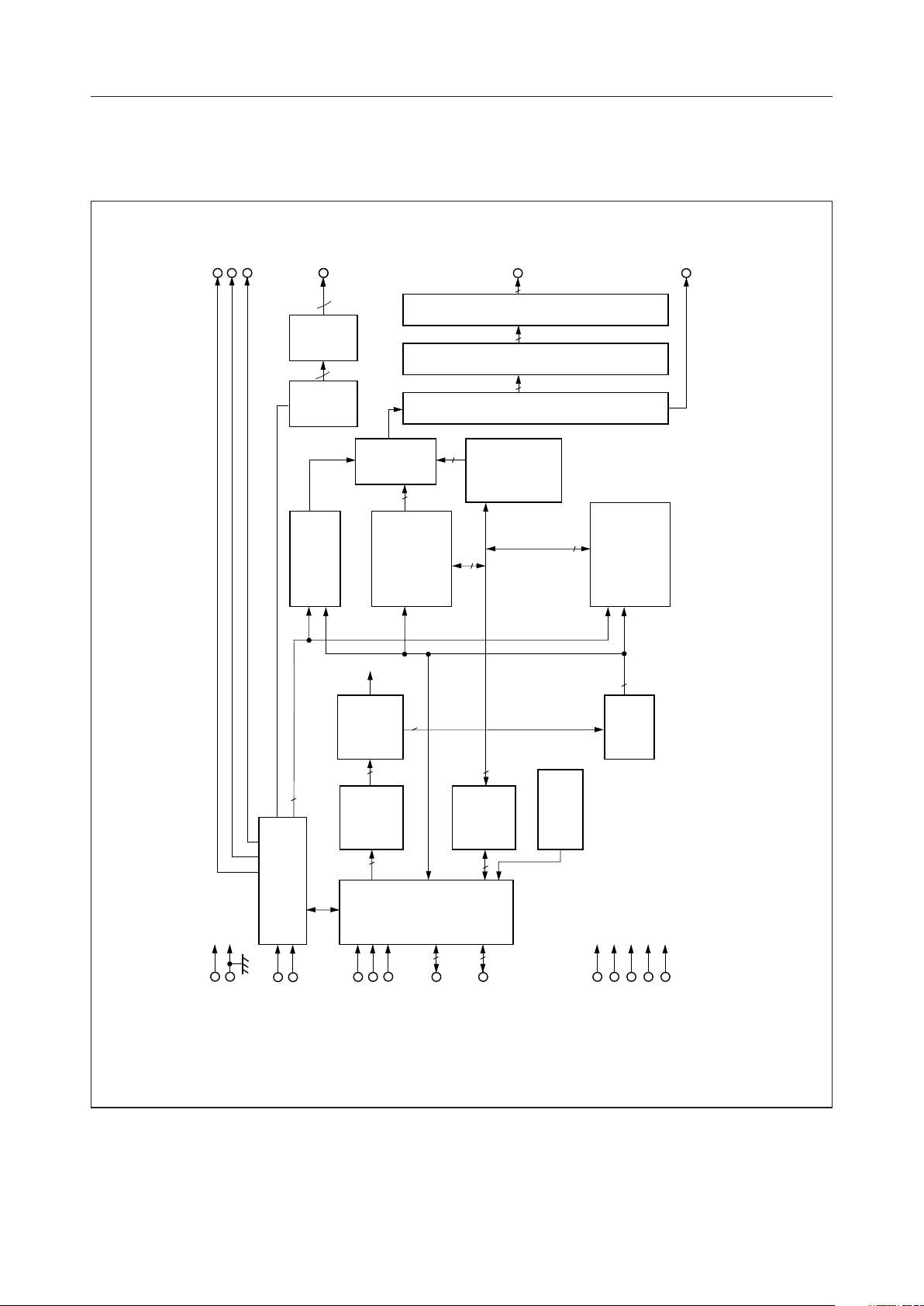

BLOCK DIAGRAM

MSM6222B-xx¡ Semiconductor

L

CP

DF

1~16

COM

16

Common

signal

driver

16

16-bit

shift

register

Cursor blink

control

Parallel/

serial

55

Character

conver-

sion

generator

RAM

(CG RAM)

5

Character

8

40

Seg-

ment

4040

40-bit

latch

40-bit

shift

generator

ROM

1~40

SEG

signal

driver

register

(CG RAM)

DO

8

Display data

RAM

(DD RAM)

77

V

DD

GND

Timing

generation

1

OSC

7

circuit

2

OSC

Instruction

decoder

(ID)

8

Instruction

register

(IR)

8

ERSR/W

7

Input/

output

buffer

4

3

- DB

0

DB

Data

4

8

register

(DR)

8

7

- DB

4

DB

Busy flag

(BF)

Address

1

V

V2V3V4V

counter

(ADC)

5

2/45

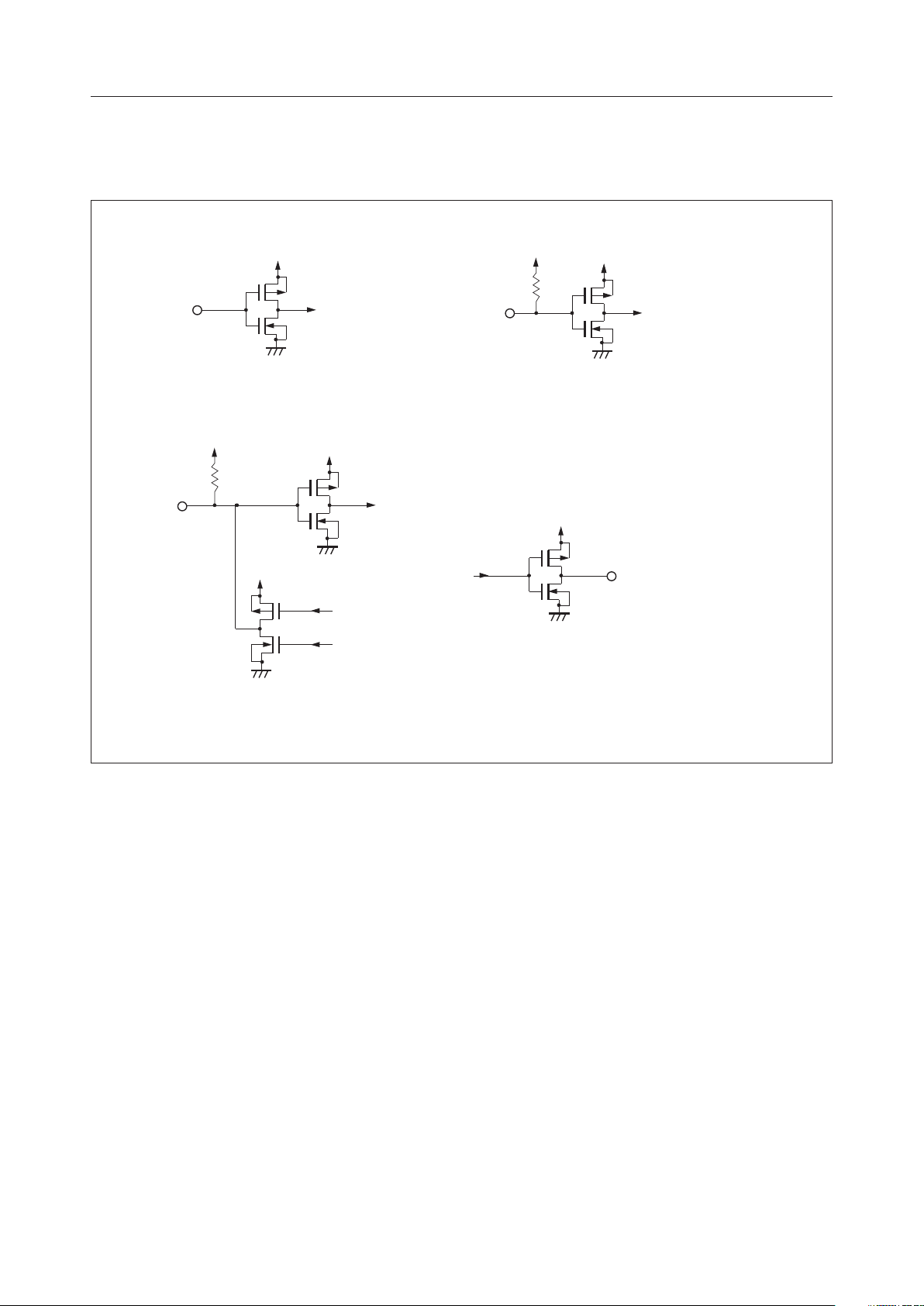

INPUT AND OUTPUT CONFIGURATION

V

DD

MSM6222B-xx¡ Semiconductor

V

DD

V

DD

P

N

Applicable to pin E.

V

DD

V

DD

P

N

V

Applicable to pins DB

DD

- DB7.

0

P

N

Applicable to pins R/W and RS.

P

V

DD

N

P

N

Applicable to pins DO, CP, L, and DF.

3/45

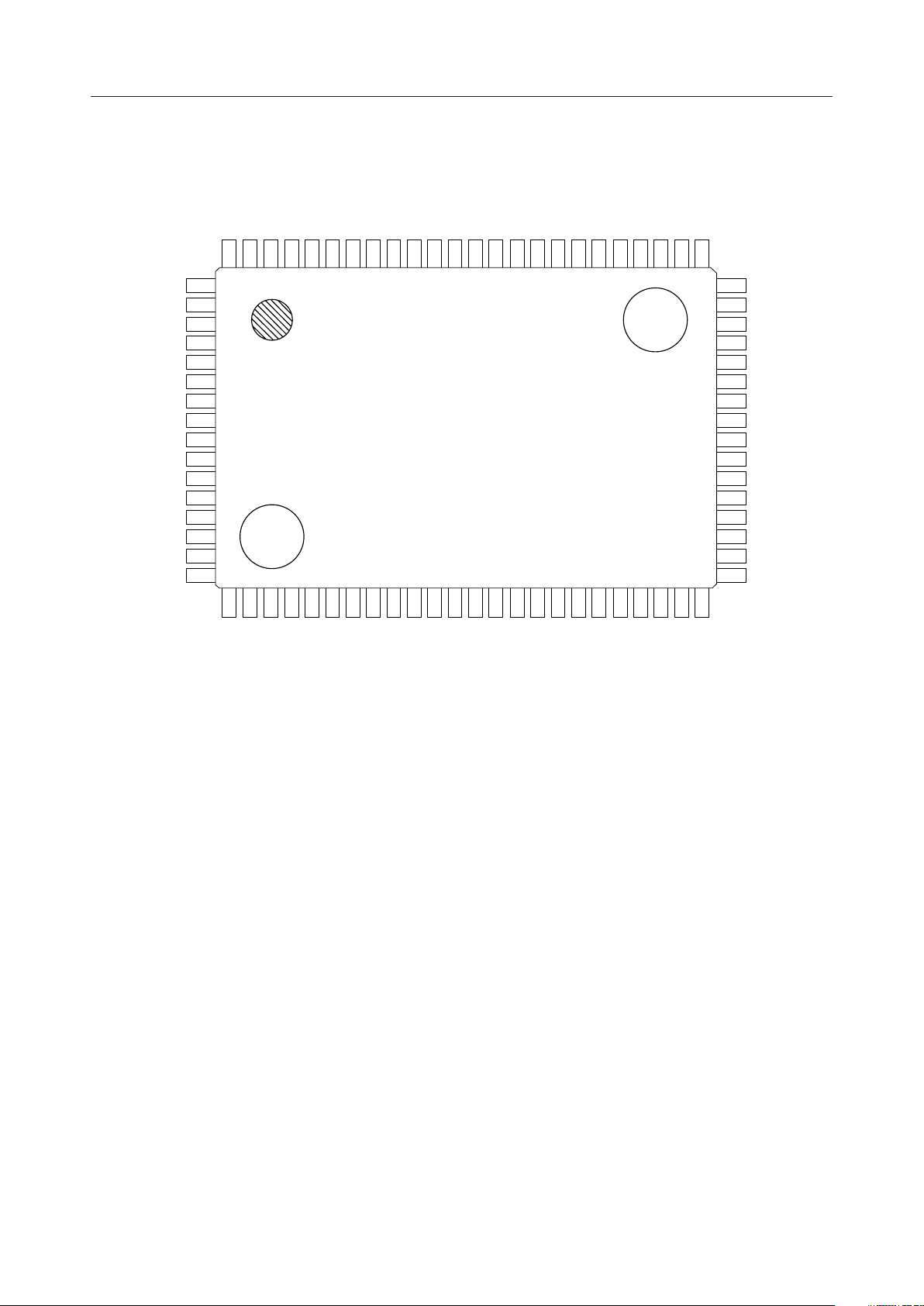

PIN CONFIGURATION

MSM6222B-xx¡ Semiconductor

SEG

SEG

SEG

SEG

SEG

SEG

SEG

SEG

SEG

SEG

SEG

SEG

SEG

SEG

SEG

SEG

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

80

79

78

77

76

75

74

73

72

71

70

69

68

67

66

65

22

SEG

1

64

39

SEG

21

SEG

2

63

40

SEG

20

18

17

16

15

SEG

7

12

COM

SEG

8

11

COM

14

SEG

9

19

SEG

SEG

SEG

SEG

4

3

5

6

61

62

605958575655545352

16

15

14

13

COM

COM

COM

COM

13

12

11

SEG

SEG

SEG

1011121314

10

9

8

7

COM

COM

COM

COM

10

9

8

SEG

SEG

SEG

1516171819

5049484746

51

6

5

COM

COM

4

COM

7

SEG

3

COM

6

SEG

2

COM

5

4

3

SEG

SEG

SEG

2021222324

4544434241

7

1

DB

COM

2

1

SEG

SEG

GND

6DB 5DB 4DB 3DB 2

DB

1

OSC

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

OSC

DB

DB

V

V

V

V

V

CP

V

DD

DF

DO

RS

R/W

0

1

2

1

2

3

4

5

L

E

80-Pin Plastic QFP

Note : The figure for Type L shows the configuration viewed from the reverse side of the package.

Pay attention to the difference in pin arrangement.

4/45

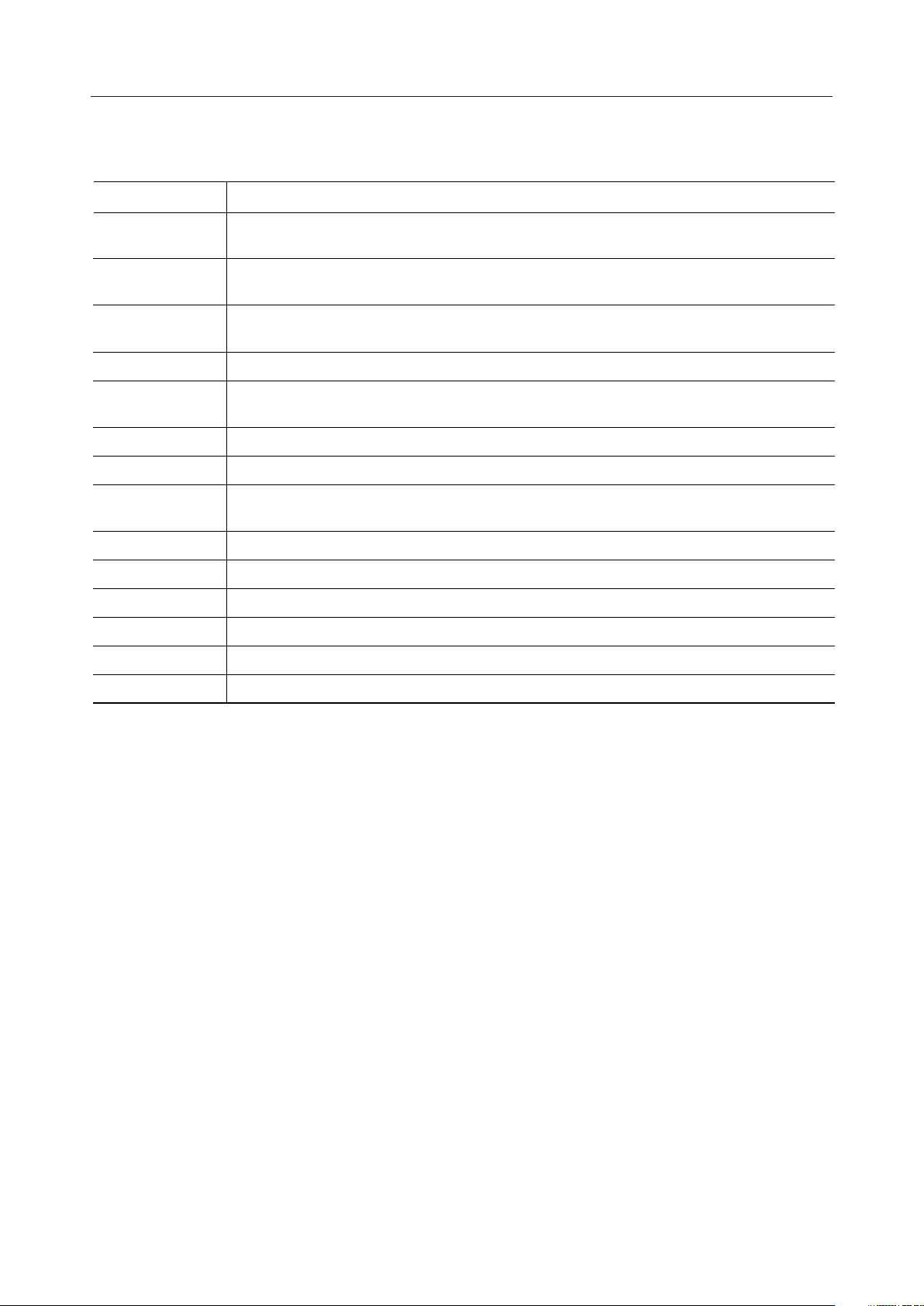

PIN DESCRIPTIONS

MSM6222B-xx¡ Semiconductor

Symbol

Description

R/W Read/write selection input pin.

"H" : Read, and "L" : Write

RS Register selection input pin.

"H" : Data register, and "L" : Instruction register

E Input pin for data input/output between CPU and MSM6222B-xx and for instruction

register activation.

DB0 - DB

7

OSC1, OSC

2

Input/output pins for data send/receive between CPU and MSM6222B-xx.

Clock oscillating pins required for internal operation upon receipt of the LCD drive signal

and CPU instruction.

COM1 - COM

SEG1 - SEG

16

40

LCD COMMON signal output pins.

LCD SEGMENT signal output pins.

DO Output pin to be connected to MSM5259 to expand the number of characters to be

displayed.

CP Clock output pin used when DO pin data output shifts inside of MSM5259.

L Clock output pin for the serially transferred data to be latched to MSM5259.

DF The alternating current signal (Display Frequency) output pin.

V

DD

Power supply pin.

GND Ground pin.

V1, V2, V3, V4, V

Bias voltage input pins to drive the LCD.

5

5/45

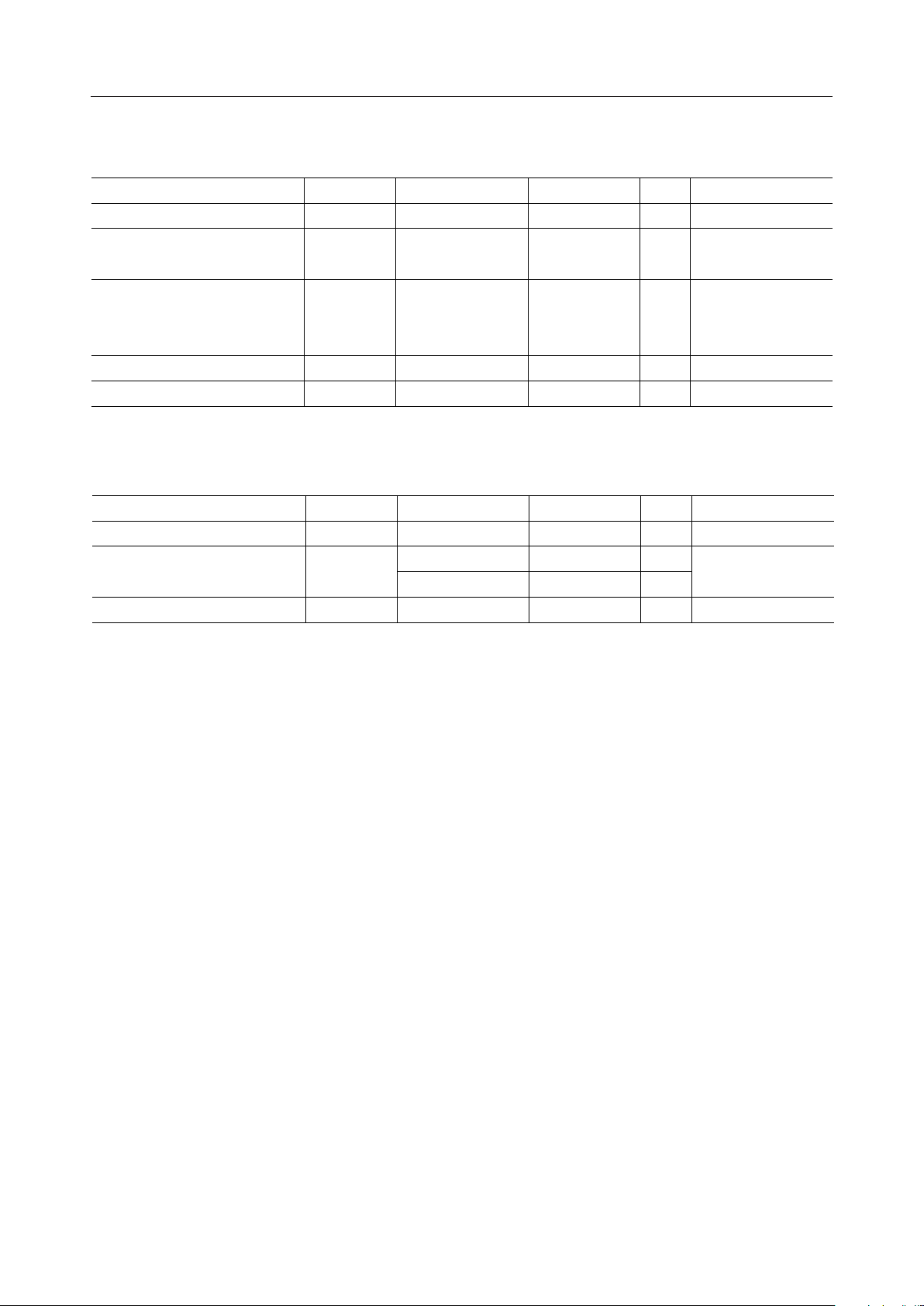

ABSOLUTE MAXIMUM RATINGS

MSM6222B-xx¡ Semiconductor

Parameter

Supply Voltage

LCD Driving Voltage

Input Voltage V

Power Dissipation P

Storage Temperature T

Symbol Condition Rating Unit Applicable pin

V

1

V4, V

V

DD

, V2, V

5

I

D

STG

3

Ta = 25°C –0.3 to + 7.0 V VDD, GND

Ta = 25°C

Ta = 25°C –0.3 to V

— 500 mW —

— –55 to + 150 °C —

RECOMMENDED OPERATING CONDITIONS

Parameter

Supply Voltage

LCD Driving Voltage V

Operating Temperature T

Symbol Condition Range Unit Applicable pin

V

DD

LCD

op

1/4 bias, VDD–V

*1

1/5 bias, VDD–V

— 4.5 to 5.5 V VDD, GND

— –20 to + 75 °C —

V

V

DD

V

DD

– 9.0 to

+ 0.3

V

, V2, V

1

V4, V

3

5

R/W, RS, E,

- DB

+ 0.3 V

DD

*2

5

5

3.0 to 8.0 V

*3

3.0 to 8.0 V

DB

0

OSC

V

DD

, V

7

1

5

*1 Voltage between VDD and V

5.

*2 Voltages applicable to V1, V2, V3 and V4 are as follows.

V1 = VDD – 1/4 (VDD – V5)

V2 = V3 = VDD – 1/2 (VDD - V5)

V4 = VDD – 3/4 (VDD – V5)

*3 Voltages applicable to V1, V2, V3 and V4 are as follows.

V1 = VDD – 1/5 (VDD – V5)

V2 = VDD – 2/5 (VDD – V5)

V3 = VDD – 3/5 (VDD – V5)

V4 = VDD – 4/5 (VDD – V5)

6/45

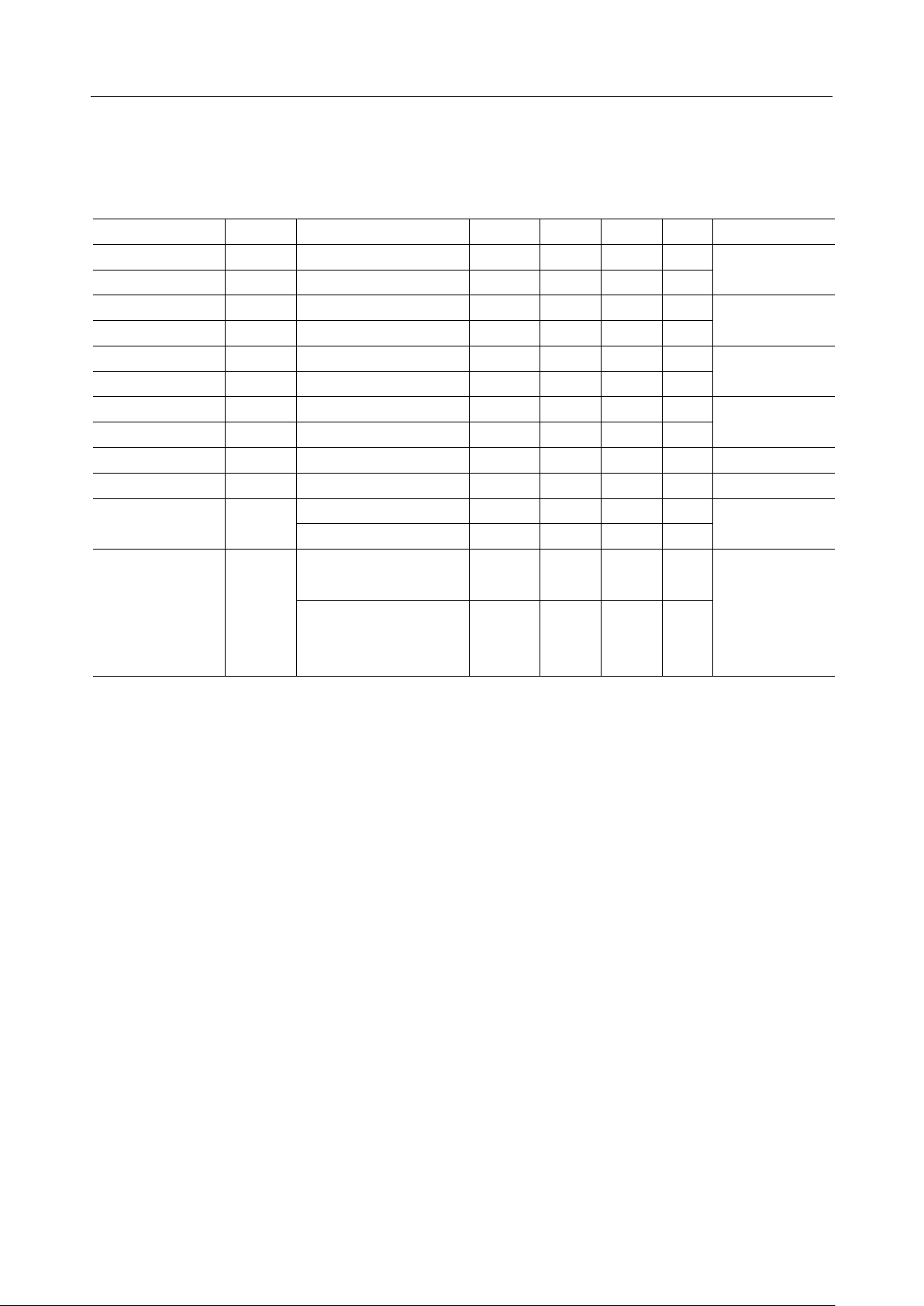

ELECTRICAL CHARACTERISTICS

DC Characteristics

Parameter

"H" Input Voltage

"L" Input Voltage V

"H" Input Voltage V

"L" Input Voltage V

"H" Output Voltage V

"L" Output Voltage V

"H" Output Voltage V

"L" Output Voltage V

COM Voltage Drop V

SEG Voltage Drop V

Input Leakage Current

Input Current I

Symbol Condition Min. Typ. Max. Unit Applicable pin

V

IH1

IL1

IH2

IL2

OH1

OL1

OH2

OL2

C

S

I

IL

— 2.2 — V

— –0.3 — 0.6 V

—V

— –0.3 — 1.0 V

IO = –0.205mA 2.4 — — V

IO = 1.2mA — — 0.4 V

IO = –40mA 0.9V

IO = 40mA — — 0.1V

IO = ±50mA *1 — — 2.9 V COM1 - COM

IO = ±50mA *1 — — 3.8 V SEG1 - SEG

VI = V

SS

V

= V

I

DD

VDD = 5.0V

V

= V

I

SS

IL2

VI = VDD, excluding current

flowing over pullup resistor

and output drive MOS

= 4.5 to 5.5V, Ta = –20 to +75°C)

(V

DD

DD

– 1.0 — V

DD

DD

— — V DO, CP, L,

DD

DD

——–1mA

——1mA

–50 –125 –250 mA

——2mA

MSM6222B-xx¡ Semiconductor

V R/W, RS, E,

DB

- DB

0

V

V

OSC

1

DB

- DB

0

DC, OSC

E

R/W, RS

DB

- DB

0

2

7

7

16

40

7

*1 Applicable to the voltage drop (VC) occurring in pins VDD, V1, V4, and V5 to each COMMON

pin (COM1 to COM16) when 50 mA flows in or out of all COM and SEG pins. Also applicable

to voltage drop (VS) occurring in pins VDD, V2, V3, and V5 to each SEG pin (SEG1 to SEG40).

When output level is at VDD, V1 or V2 level, 50 mA flows out, while 50 mA flows in when the

output level is at V3, V4 or V5 level.

This occurs when +5V is input to VDD, V1, and V2, and when –3V is input to V3, V4, and V5.

7/45

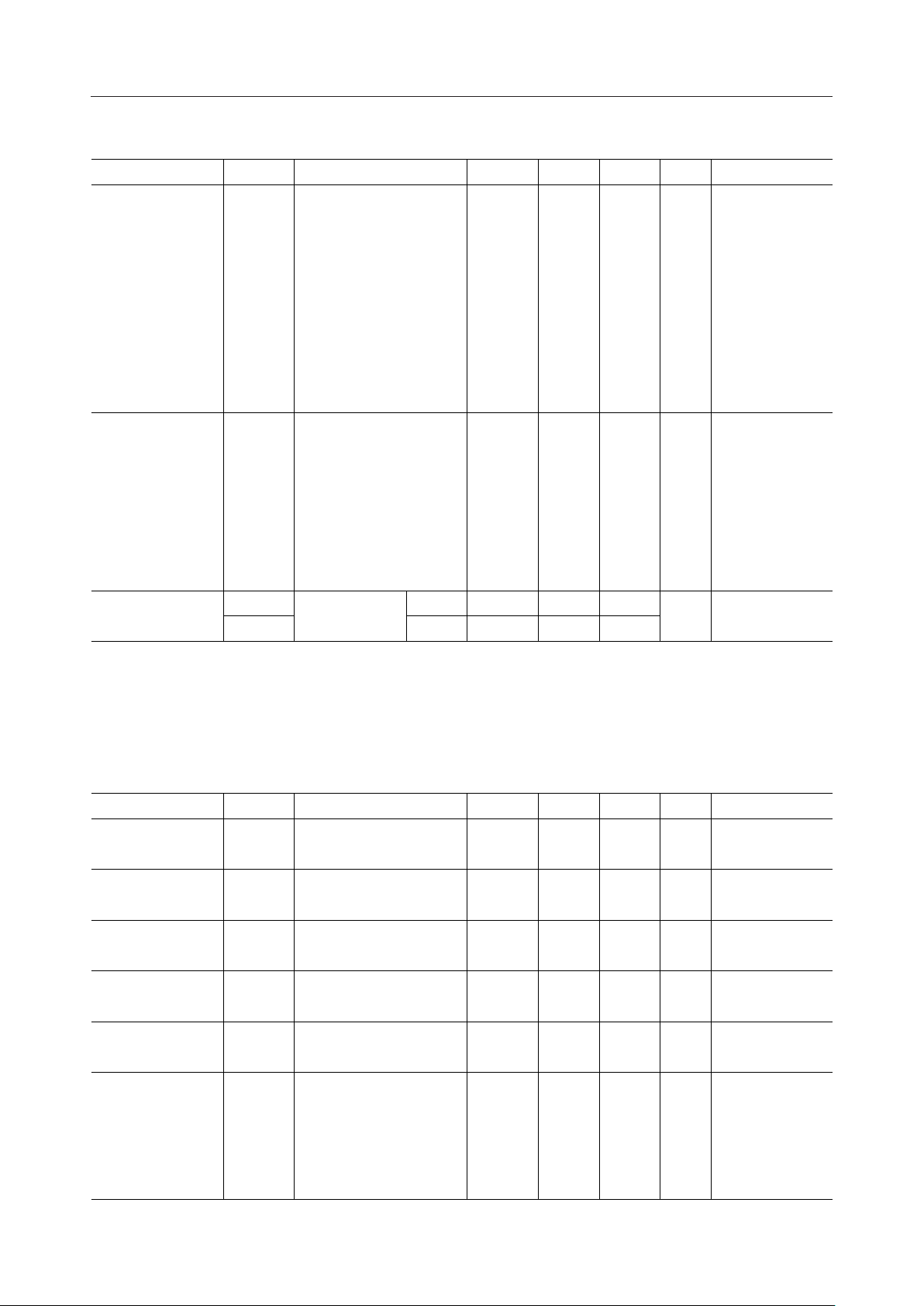

Parameter

Symbol Condition Min. Typ. Max. Unit Applicable pin

Supply Current (1) I

Supply Current (2) I

LCD Driving Bias

Input Voltage

V

V

DD1

DD2

LCD1

LCD2

VDD = 5.0V,

resistor oscillation or

external clock input via

.

OSC

1

= 270kHz.

f

OSC

E is in "L" level.

Other inputs are open.

Output pins are

all no load. *2

VDD = 5.0V,

ceramic oscillation,

= 250kHz.

f

OSC

E is in "L" level.

Other pins are open.

Output pins are

all no load. *2

1/5 bias 3.0 — 8.0

V

DD–V5

*7

1/4 bias 3.0 — 8.0

= 4.5 to 5.5V, Ta = –20 to +75°C)

(V

DD

— 0.35 0.6 mA

— 0.55 0.8 mA

V

MSM6222B-xx¡ Semiconductor

VDD, V1, V2,

V

V

DD

V

DD

, V4, V

3

5

*2 Applicable to the current that flows in pin VDD when power is input as follows:

VDD = 5V, GND = 0V, V1 = 3.4V, V2 = 1.8V, V3 = 0.2V, V4 = –1.4V, and V5 = –3V.

AC Characteristics

(V

= 4.5 to 5.5V, Ta = –20 to +75°C)

DD

Parameter

Clock Oscillation

R

f

Frequency

Clock Input

Frequency

Input Clock Duty f

Input Clock Rise

Time

Input Clock Fall

Time

Ceramic Filter

Oscillation

Frequency

Symbol Condition Min. Typ. Max. Unit Applicable pin

f

OSC1

f

DUTY

t

t

f

OSC

Rf = 91kW ± 2%

*3

OSC2 is open.

IN

Input from OSC

r

f

= 510kW,

R

f

= C2 = 200 pF,

C

1

= 30kW, and

R

d

1

*4

*5

*5

175 250 350 kHz

125 250 350 kHz OSC

45 50 55 % OSC

— — 0.2 ms OSC

— — 0.2 ms OSC

245 250 255 kHz

Ceralock CSB250A.

*6

OSC

OSC

OSC

OSC

1

2

1

1

1

1

1

2

8/45

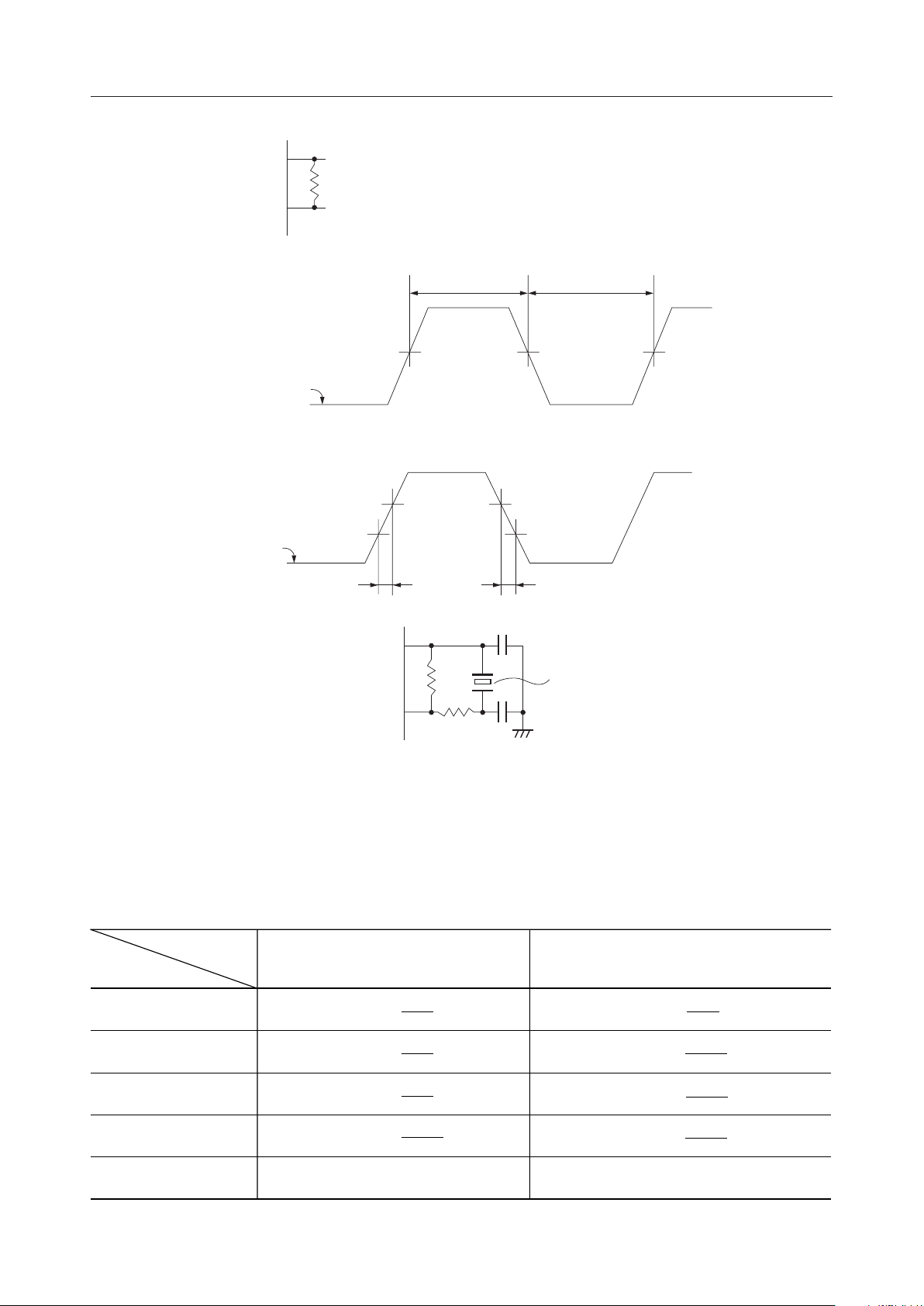

*3

OSC

OSC

MSM6222B-xx¡ Semiconductor

1

R

f

2

Rf=91kW ±2%

Minimum wiring is required between

and Rf and between OSC2 and Rf.

OSC

1

*4 Applied to pulse input via OSC

0.5V

fIN

waveform

*5 Applied to pulse input via OSC

V

–1.0V

DD

fIN

waveform

1.0V

*6

OSC

OSC

.

1

DD

.

1

t

HW

0.5V

DD

f

= tHW/ (tHW + tLW) x 100(%)

DUTY

–1.0V

1.0V

t

r

t

f

DD

DD

t

LW

0.5V

DD

C1

1

R

f

2

R

d

C2

Ceralock

Pin

Ceralock : CSB250A (mfd. by MURATA MFG.Co.)

R

: 510kW ±5%

f

R

: 30kW ±5%

d

C

: 200pF ±10%

1

C

: 200pF ±10%

2

Please contact us when using this circuit.

*7

Input the voltage listed in the table below to V1 - V5:

N (LCD lines)

1-line mode 2-line mode

V

V

1

V

2

V

3

V

4

V

5

V

DD

V

DD

V

DD

V

DD

V

DD

–

–

–

–

– V

LCD

V

LCD

V

LCD

3V

LCD

4

2

2

LCD

4

V

–

–

–

–

– V

2V

3V

4V

LCD

LCD

5

LCD

5

LCD

5

LCD

5

V

DD

V

DD

V

DD

V

DD

V

DD

V

is an LCD driving voltage. (For "N" (number of LCD lines),

LCD

refer to the initial set of the instruction code.)

9/45

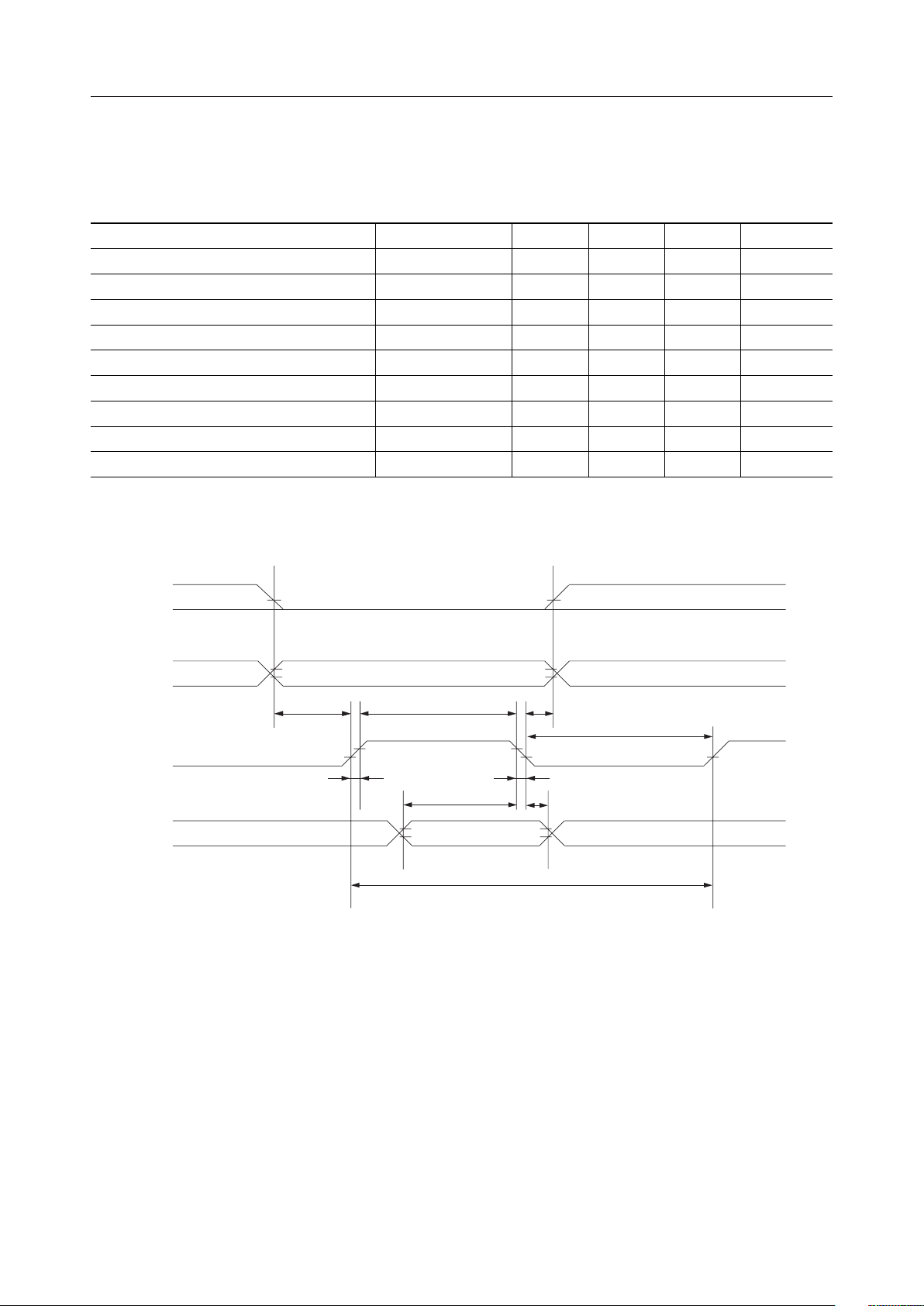

Switching Characteristics

• Timing for input from the CPU

Parameter

R/W and RS set-up time

E "H" pulse width t

R/W and RS holding time t

E rise time t

E fall time t

E "L" pulse width t

E cycle time t

DB

to DB7 input data set-up time t

0

DB

to DB7 input data holding time t

0

Symbol Min. Typ. Max. Unit

MSM6222B-xx¡ Semiconductor

= 4.5 to 5.5V, Ta = –20 to +75°C)

(V

DD

t

B

W

A

r

f

L

C

I

H

140 — — ns

280 — — ns

10—— ns

——25 ns

——25 ns

280 — — ns

667 — — ns

180 — — ns

10—— ns

DB

0

R/W

RS

E

- DB

V

IL

V

IH

V

IL

V

V

IH

IL

t

W

t

Input data

I

t

B

V

V

t

r

7

IH

IL

V

IL

V

IH

V

IL

t

A

t

L

V

IH

V

IL

t

f

t

H

V

IH

V

IL

t

C

V

IL

10/45

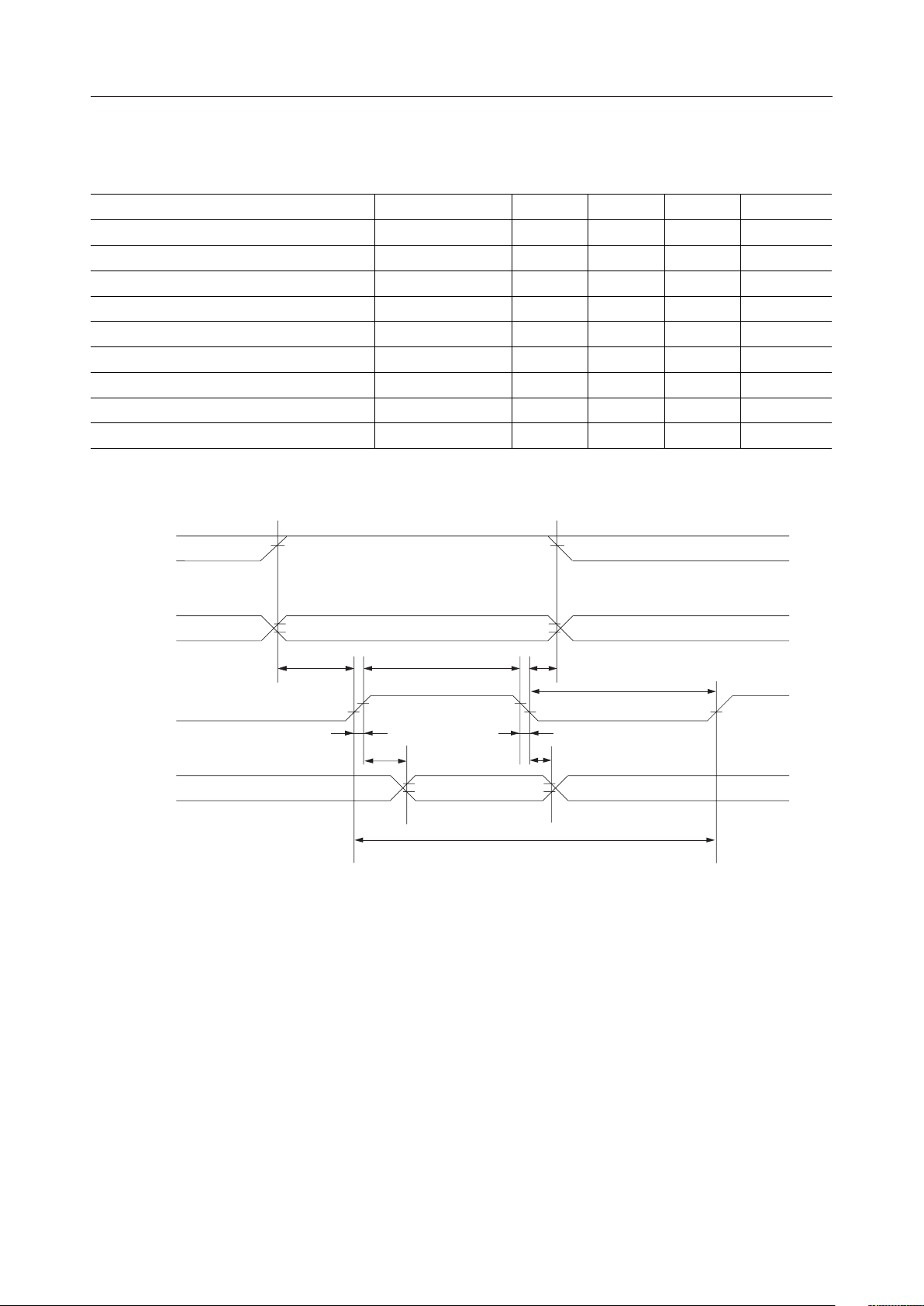

• Timing for output to the CPU

Parameter

R/W and RS set-up time

E "H" pulse width t

R/W and RS holding time t

E rise time t

E fall time t

E "L" pulse width t

E cycle time t

to DB7 data output delay time t

DB

0

to DB7 data output holding time t

DB

0

Symbol Min. Typ. Max. Unit

MSM6222B-xx¡ Semiconductor

= 4.5 to 5.5V, Ta = –20 to +75°C)

(V

DD

t

B

W

A

r

f

L

C

D

O

140 — — ns

280 — — ns

10—— ns

——25 ns

——25 ns

280 — — ns

667 — — ns

— — 220 ns

20—— ns

DB

0

R/W

-DB

RS

V

IH

V

IH

V

IL

t

B

V

E

V

t

r

IH

IL

t

7

t

W

D

V

OH

Output data

V

OL

V

IH

V

IH

V

IL

t

A

t

L

V

IH

V

IL

t

f

t

D

V

OH

V

OL

t

C

V

IL

11/45

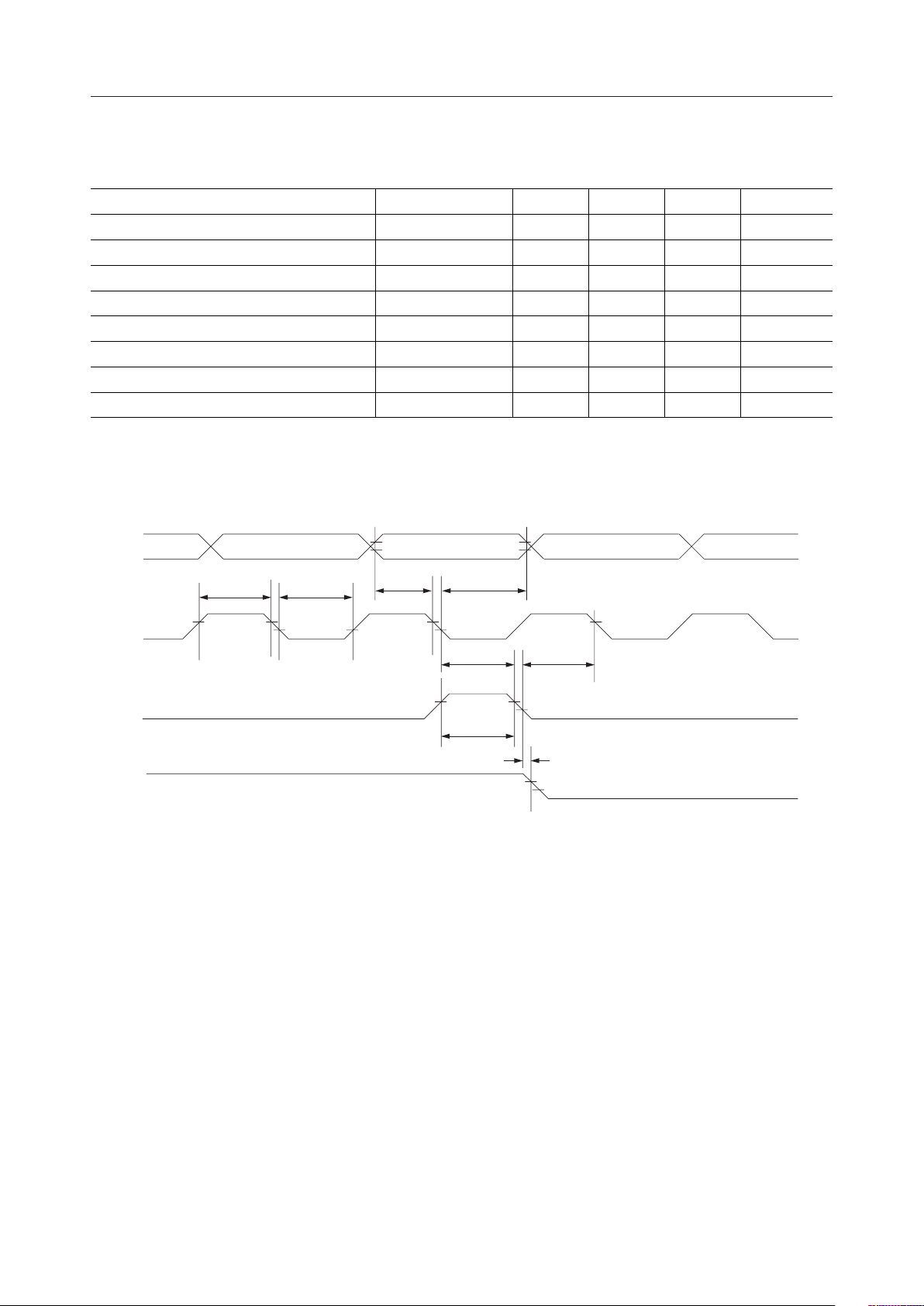

• Timing for output to MSM5259

Parameter

CP "H" pulse width

CP "L" pulse width t

DO set-up time t

DO holding time t

L clock set-up time t

L clock holding time t

L "H" pulse width t

DF delay time t

Symbol Min. Typ. Max. Unit

t

HW1

LW

HW2

DH

SU

HO

MSM6222B-xx¡ Semiconductor

= 4.5 to 5.5V, Ta = –20 to +75°C)

(V

DD

800 — — ns

800 — — ns

S

M

300 — — ns

300 — — ns

500 — — ns

100 — — ns

800 — — ns

–1000 — 1000 ns

DO

CP

DF

V

OH2

V

OL2

t

t

HW1

V

OH2VOH2

t

LW

V

OL2

s

V

OL2

OH2

V

OH2

V

L

V

OH2

V

OL2

t

DH

V

V

OL2

t

t

SU

HW2

V

OH2

t

HO

V

OL2

t

M

V

OH2

OH2

12/45

MSM6222B-xx¡ Semiconductor

FUNCTIONAL DESCRIPTION

Instruction Register (IR) and Data Register (DR)

These two registers are selected by the REGISTER SELECTOR (RS) pin.

The DR is selected when the "H" level is input to the RS pin and IR is selected when the "L"

level is input.

The IR is used to store the address of the display data RAM (DD RAM) or character

generator RAM (CG RAM) and instruction code.

The IR can be written, but not be read by the microcomputer (CPU).

The DR is used to write and read the data to and from the DD RAM or CG RAM.

The data written to DR by the CPU is automatically written to the DD RAM or CG RAM

as an internal operation.

When an address code is written to IR, the data (of the specified address) is automatically

transferred from the DD RAM or CG RAM to the DR. Next, when the CPU reads the DR,

it is possible to verify DD RAM or CG RAM data from the DR data.

After the writing of DR by the CPU, the next adress in the DD RAM or CG RAM is selected

to be ready for the next CPU writing.

Likewise, after the reading out of DR by the CPU, DD RAM or CG RAM data is read out

by the DR to be ready for the next CPU reading.

Write/read to and from both registers is carried out by the READ/WRITE (R/W) pin.

Table 1 RS and R/W pins functions

R/W

L

H L Read of busy flag (BF) and address counter (ADC)

L H DR write

H H DR read

RS Function

L IR write

Busy Flag (BF)

When the busy flag is at "H", it indicates that the MSM6222B-xx is engaged in internal

operation.

When the busy flag is at "H", any new instruction is ignored.

When R/W = "H" and RS = "L", the busy flag is output from DB7.

New instruction should be input when busy flag is "L" level.

When the busy flag is at "H", the output code of the address counter (ADC) is undefined.

Address Counter (ADC)

The address counter (ADC) allocates the address for the DD RAM and CG RAM write/read

and also for the cursor display.

When the instruction code for a DD RAM address or CG RAM address setting is input to IR,

after deciding whether it is DD RAM or CG RAM, the address code is transferred from IR

to ADC. After writing (reading) the display data to (from) the DD RAM or CG RAM, the

ADC is incremented (decremented) by 1 internally.

The data of the ADC is output to DB0 - DB6 on the conditions that R/W = "H", RS = "L", and

BF = "L".

13/45

MSM6222B-xx¡ Semiconductor

)

Timing Generator Circuit

This circuit is used to generate timing signals to activate internal operations upon receipt

of CPU instruction and also from such internal circuits as the DD RAM, CG RAM, and CG

ROM.

It is designed so that the internal operation caused by accessing from the CPU will not

interfere with the internal operation caused by LCD driving. Consequently, when data is

written from the CPU to DD RAM, flickering does not occur in a display area other than

the display area where the data is written.

In addition, this circuit generates the transfer signal to MSM5259 for display character

expansion.

Display Data RAM (DD RAM)

This RAM is used to store display data of 8-bit character codes (see Table 2).

DD RAM address corresponds to the display position of the LCD. The correspondence

between the two is described in the following.

DD RAM address (set to ADC) is expressed in hexadecimal notation as shown below:

ADC

(Example)

When DD RAM

address is 2A

DB

6

Hexadecimal notation Hexadecimal notation

HLHLH

2A

DB

LSBMSB

0

LL

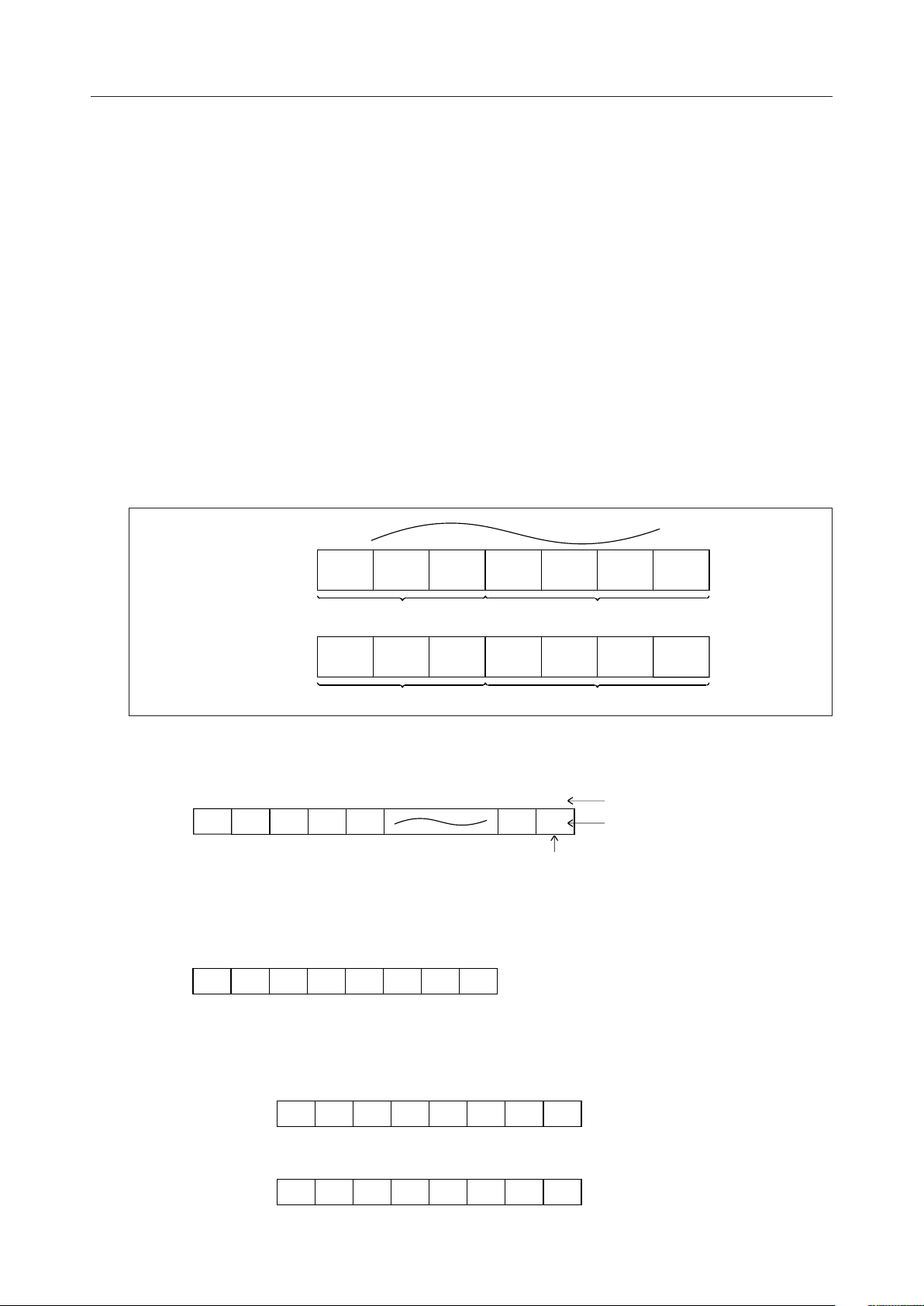

(1) Correspondence between address and display position in the 1-line display mode

First

digit

MSB LSB

2023034045

00

01

794F80

4E

Display position

DD RAM address (hex.)

• When the MSM6222B-xx alone is used, up to 8 characters can be displayed from the

first to eighth digit.

First

digit

2023034045056067078

00

01

When the display is shifted by instruction, the correspondence between the LCD

display position and the DD RAM address changes as shown below:

First

(Display

shifted

to right)

(Display

shifted

to left

digit

First

digit

2013024035046057068

00

4F

2033044055066077088

02

01

14/45

Loading...

Loading...