OKI MR27V1652DTP, MR27V1652DMA, MR27V1652DTA, MR27V1652DRA Datasheet

1/10

¡

DESCRIPTION

1A

MR27V1652D

1,048,576-Word x 16-Bit or 2,097,152-Word x 8-Bit

8-Word x 16-Bit or 16-Word x 8-Bit Page Mode One Time PROM

The MR27V1652D is a 16Mbit electrically Programmable Read-Only Memory with page mode. Its

configuration can be electrically switched between 1,048,576 word x 16bit and 2,097,152 word x 8

bit. The MR27V1652D operates on a single +3.3V power supply and is TTL compatible. The MR27

V1652D provides Page mode which can greatly reduce the read access time. Since the MR27V1652

D operates asynchronously , external clocks are not required , making this device easy-to-use. The

MR27V1652D is suitable as large-capacity fixed memory for microcomputers and data terminals. It

is manufactured using a CMOS double silicon gate technology and is offered in 42-pin DIP , 44-pin

SOP , 44-pin TSOP or 48-pin TSOP packages.

FEATURES

• 1,048,576 word x 16bit / 2,097,152 word x 8bit electrically switchable configuration

• Single +3.3V power supply

• Access time 80ns

Page mode access time 30ns

• Input / Output TTL compatible

• Three-state output

• Packages

42-pin plastic DIP (DIP42-P-600-2.54) (Product name : MR27V1652DRA)

44-pin plastic SOP (SOP44-P-600-1.27-K) (Product name : MR27V1652DMA)

44-pin plastic TSOP (TSOP II 44-P-400-0.80-K) (Product name : MR27V1652DTP)

48-pin plastic TSOP (TSOP II 48-P-550-0.80-K) (Product name : MR27V1652DTA)

Semiconductor

November 1999

2/10

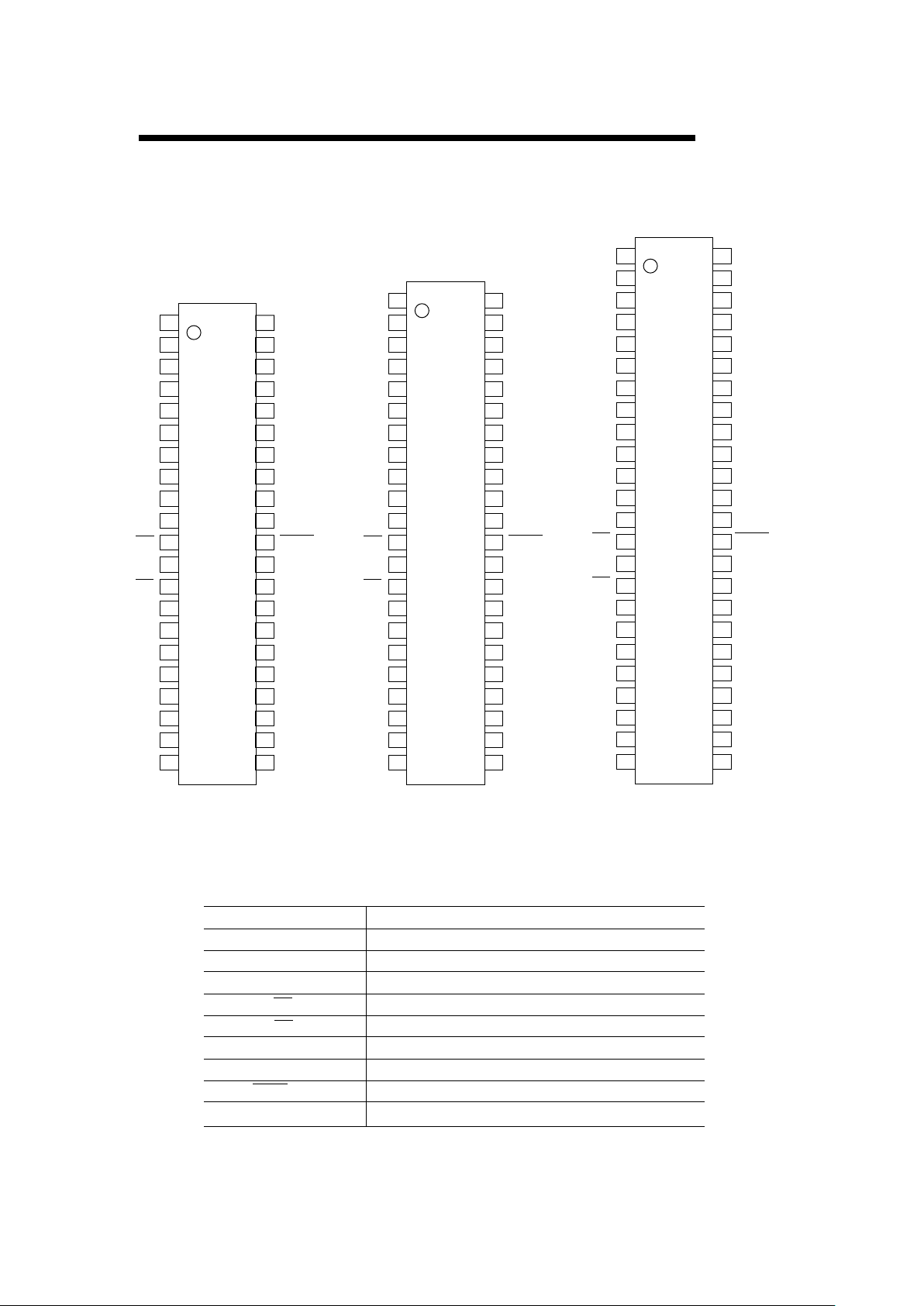

PIN CONFIGURATION (TOP VIEW)

MR27V1652D

PIN NAMES

FUNCTIONS

D15/A-1 Data output / Address input

A0 - A19 Address input

D0 - D14 Data output

CE

OE

Output enable

V

CC

Power supply voltage

BYTE/V

PP

Mode switch / Program power supply voltage

NC

Non connection

Chip enable

V

SS

GND

43

A18

A8

A9

A11

A12

A13

A14

A15

A16

V

SS

D15/A-1

D7

D14

D6

D13

D5

D12

D4

V

CC

A10

42

41

40

2

3

4

5

39

38

37

36

6

7

8

9

35

34

33

32

10

11

12

13

31

30

29

28

14

15

16

17

27

26

25

24

18

19

20

21

2322

A19

A17

A7

A6

A5

A4

A3

A2

A1

A0

CE

V

SS

OE

D0

D8

D1

D9

D2

D10

D3

D11

44

NC

1

BYTE/Vpp

44-pin SOP , TSOP (II)

NC

A18

A8

A9

A11

A12

A13

A14

A15

A16

V

SS

D15/A-1

D7

D14

D6

D13

D5

D12

D4

V

CC

A10

42

41

40

2

3

4

5

39

38

37

36

6

7

8

9

35

34

33

32

10

11

12

13

31

30

29

28

14

15

16

17

27

26

25

24

18

19

20

21

23

A19

A17

A7

A6

A5

A4

A3

A2

A1

A0

CE

V

SS

OE

D0

D8

D1

D9

D2

D10

D3

D11

BYTE/Vpp

42-pin DIP

22

1

45

A18

A8

A9

A11

A12

A13

A14

A15

A16

V

SS

D15/A-1

D7

D14

D6

D13

D5

D12

D4

V

CC

A10

44

43

42

4

5

6

7

41

40

39

38

8

9

10

11

37

36

35

34

12

13

14

15

33

32

31

30

16

17

18

19

29

28

27

26

20

21

22

23

2524

A19

A17

A7

A6

A5

A4

A3

A2

A1

A0

CE

V

SS

OE

D0

D8

D1

D9

D2

D10

D3

D11

48

NC

NC

47

1

2

NC

NC

NC

463

BYTE/Vpp

48-pin TSOP (II)

NC

3/10

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14

A15

A16

A17

A18

A19

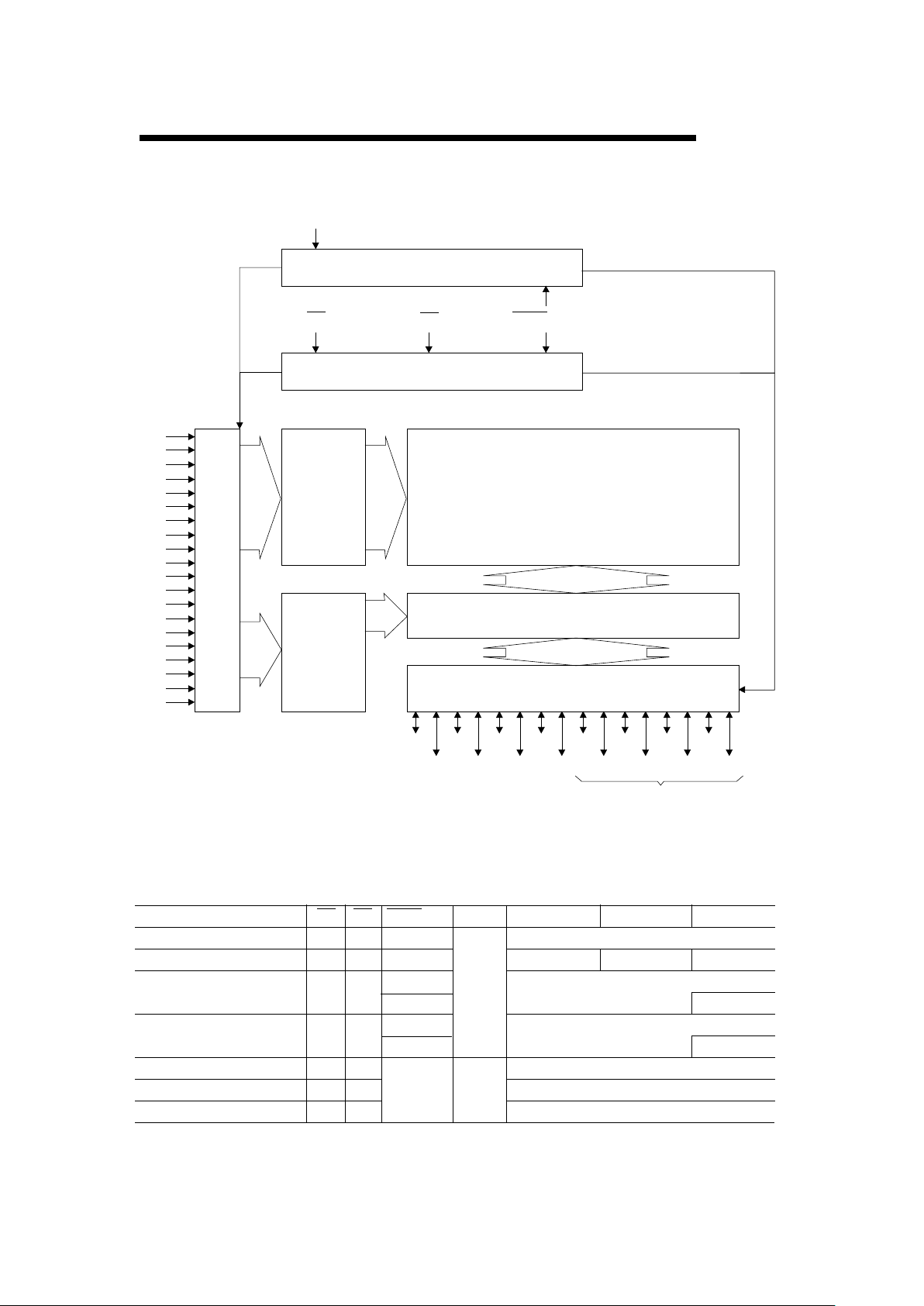

BLOCK DIAGRAM

D0

CE BYTE/V

PP

OE

CE PGMOE

Address Buffer

Row Decoder

Column Decoder

Memory Matrix

Multiplexer & Page Data Latch

Output Buffer

FUNCTION TABLE

STAND-BY

OUTPUT DISABLE

READ (8-Bit)

READ (16-Bit)

MODE

D15/A-1

CE OE

V

CC

LL

D

OUT

L

L

L/H

L

H

L

*

H

*

H

L

* : Don't Care

D1D2D3D4D5D6D7D8D9

D10

D11

D12

D13

D14

D15

X8/X16 Switch

A-1

In 8-bit output mode, these pins are

three-stated and pin D15 functions

as the A-1 address pin.

3.3V

D8 - D14D0 - D7

H

L

D

OUT

Hi-Z

H

Hi-Z

*

Hi-Z

PROGRAM

LH

D

IN

PROGRAM INHIBIT

H H Hi-Z

PROGRAM VERIFY

HL

D

OUT

9.75V

4.0V

MR27V1652D

BYTE/V

PP

1,048,576X16-Bit or 2,097,152X8-Bit

Loading...

Loading...