Page 1

TDA8752B

Triple high-speed Analog-to-Digital Converter 110 Msps

Rev. 03 — 21 July 2000 Product specification

1. General description

The TDA8752B is a triple 8-bit ADC with controllable amplifiers and clamps for the

digitizing of large bandwidth RGB signals.

The clamp level, the gain and all other settings are controlled via a serial interface

(either I2C-bus or 3-wire serial bus, selected via a logic input).

The IC also includes a PLL that can be locked to the horizontal line frequency and

generates the ADC clock. The PLL jitter is minimized for high resolution PC graphics

applications. An external clock can also be input to the ADC.

It is possible to set the TDA8752B serial bus address to four different values, when

several TDA8752B ICs are used in a system, by means of the I2C-bus interface (for

example, two ICs used in an odd/even configuration).

2. Features

■ Triple 8-bit ADC

■ Sampling rate up to 110 Msps

c

c

■ IC controllable via a serial interface, which can be either I2C-bus or 3-wire serial

bus, selected via a TTL input pin

■ IC analog voltageinputfrom0.4 to 1.2 V (p-p) to produce a full-scale ADC input of

1 V (p-p)

■ Three clamps for programming a clamping code between −63.5 and +64 in steps

of1⁄2LSB for RGB signals, and from +120 to +136 in steps of1⁄2LSB for YUV

signals

■ Three controllable amplifiers: gain controlled via the serial interface to produce a

full-scale resolution of1⁄2LSB peak-to-peak

■ Amplifier bandwidth of 250 MHz

■ Low gain variation with temperature

■ PLL controllable via the serial interface to generate the ADC clock which can be

locked to a line frequency of 15 to 280 kHz

■ Integrated PLL divider

■ Programmable phase clock adjustment cells

■ Internal voltage regulators

■ TTL compatible digital inputs and outputs

■ Chip enable high-impedance ADC output

Page 2

Philips Semiconductors

TDA8752B

Triple high-speed Analog-to-Digital Converter 110 Msps

■ Power-down mode

■ Possibility to use up to four ICs in the same system when using the I2C-bus

interface, or more when using the 3-wire serial bus interface

■ 1.1 W power dissipation.

3. Applications

■ RGB high-speed digitizing

■ LCD panels drive

■ LCD projection systems

■ VGA and higher resolutions

■ Using two ICs in parallel, a higher display resolution can be obtained: 200 MHz

pixel frequency.

4. Quick reference data

Table 1: Quick reference data

Symbol Parameter Conditions Min Typ Max Unit

V

CCA

V

DDD

V

CCD

V

CCO

V

CCA(PLL)

V

CCO(PLL)

I

CCA

I

DDD

I

CCD

I

CCO

I

CCA(PLL)

I

CCO(PLL)

f

clk

f

ref(PLL)

f

VCO

INL DC integral non-linearity from analog input to digital

DNL DC differential non-linearity from analog input to digital

∆G

amp

B amplifier bandwidth −3 dB; T

t

set

9397 750 07338

Product specification Rev. 03 — 21 July 2000 2 of 38

analog supply voltage for R, G and B channels 4.75 5.0 5.25 V

logic supply voltage for I2C-bus and 3-wire

4.75 5.0 5.25 V

serial bus

digital supply voltage 4.75 5.0 5.25 V

output stages supply voltage for R, G and B channels 4.75 5.0 5.25 V

analog PLL supply voltage 4.75 5.0 5.25 V

output PLL supply voltage 4.75 5.0 5.25 V

analog supply current − 120 − mA

logic supply current for I2C-bus and 3-wire − 1.0 − mA

digital supply current − 40 − mA

output stages supply current f

= 110 MHz; ramp input − 26 − mA

clk

analog PLL supply current − 28 − mA

output PLL supply current − 5 − mA

clock frequency −−110 MHz

PLL reference clock

15 − 280 kHz

frequency

VCO output clock frequency 12 − 110 MHz

−±0.5 ±1.5 LSB

output; full-scale; ramp

input; f

= 110 MHz

clk

−±0.5 ±1.0 LSB

output; full-scale; ramp

/∆T amplifier gain stability as a

function of temperature

settling time of the ADC block

plus AGC

input; f

V

ref

100 ppm/°C maximum

input signal settling

time <1 ns; T

= 110 MHz

clk

= 2.5 V with

=25°C 250 −−MHz

amb

amb

−−200 ppm/°C

−−6ns

=25°C

© Philips Electronics N.V. 2000. All rights reserved.

Page 3

Philips Semiconductors

TDA8752B

Triple high-speed Analog-to-Digital Converter 110 Msps

Table 1: Quick reference data

…continued

Symbol Parameter Conditions Min Typ Max Unit

DR

PLL

P

tot

j

PLL(rms)

PLL divider ratio 100 − 4095

total power dissipation f

maximum PLL phase jitter

(RMS value)

= 110 MHz; ramp input − 1.1 − W

clk

f

= 66.67 kHz;

ref

= 110 MHz

f

clk

− 112 − ps

5. Ordering information

Table 2: Ordering information

Type number Package Sampling

Name Description Version

TDA8752BH/8 QFP100 plastic quad flat package; 100 leads (lead length

SOT317-2 110

1.95 mm); body 14 × 20 × 2.8 mm

frequency (MHz)

9397 750 07338

Product specification Rev. 03 — 21 July 2000 3 of 38

© Philips Electronics N.V. 2000. All rights reserved.

Page 4

Philips Semiconductors

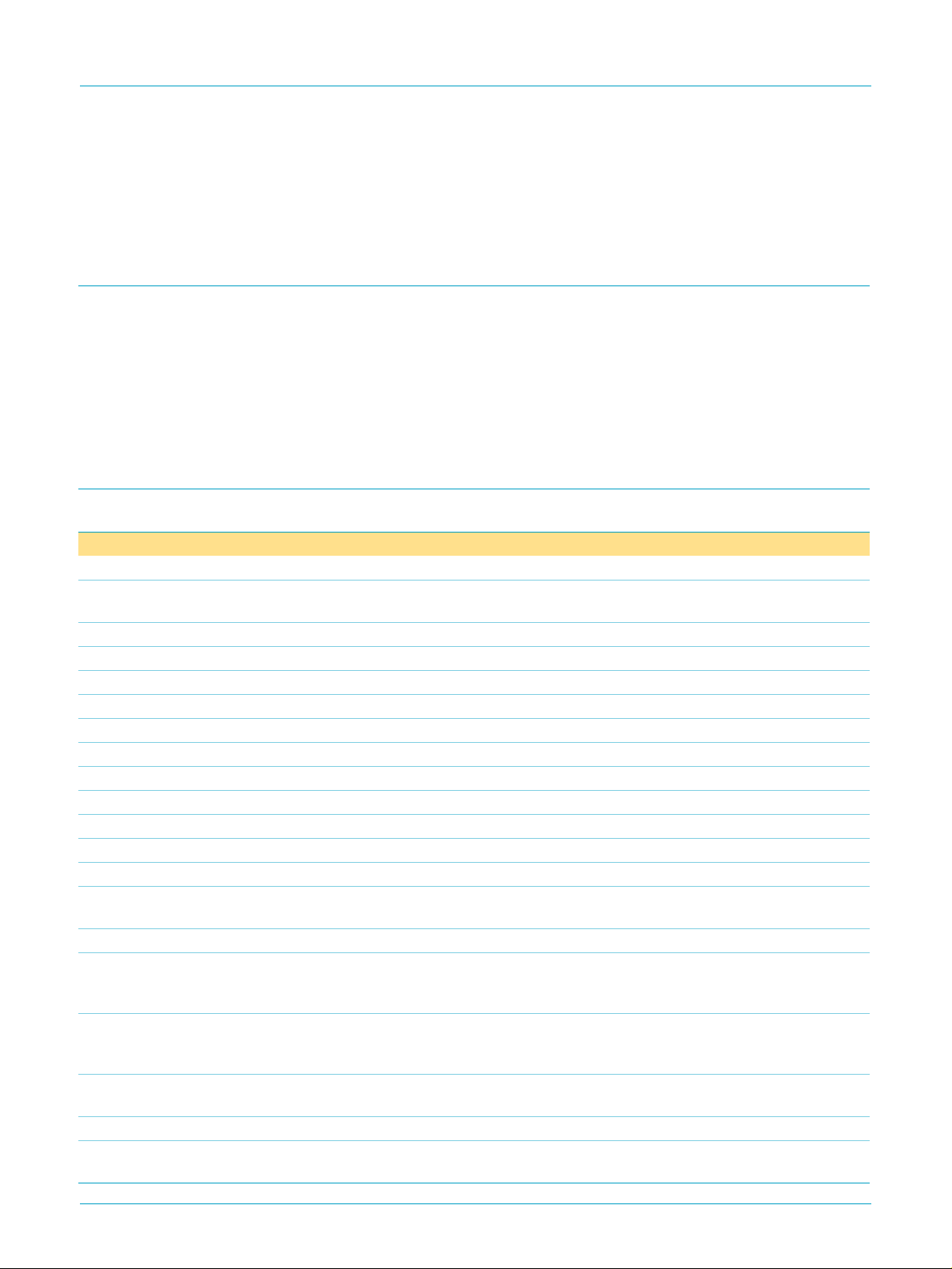

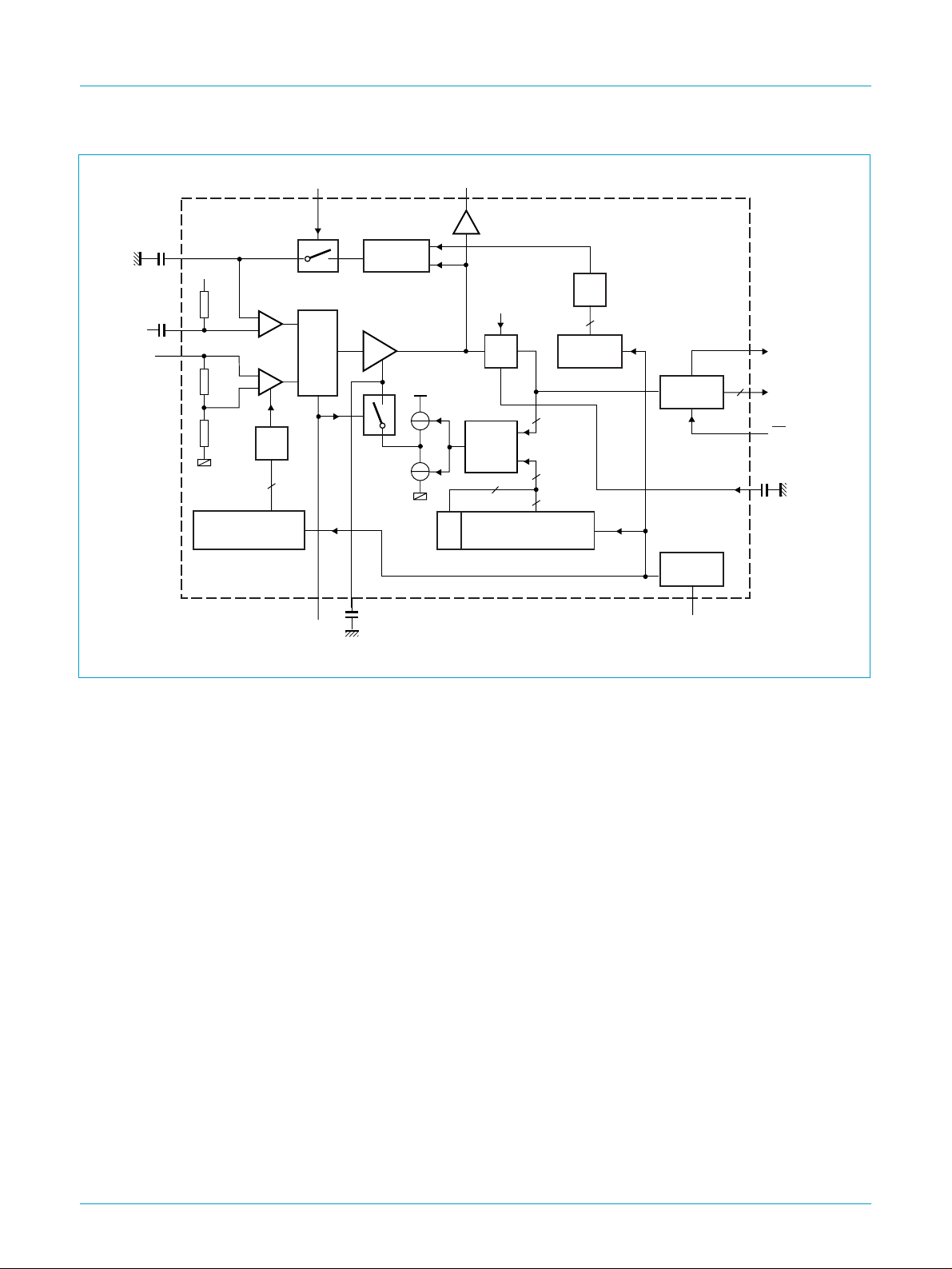

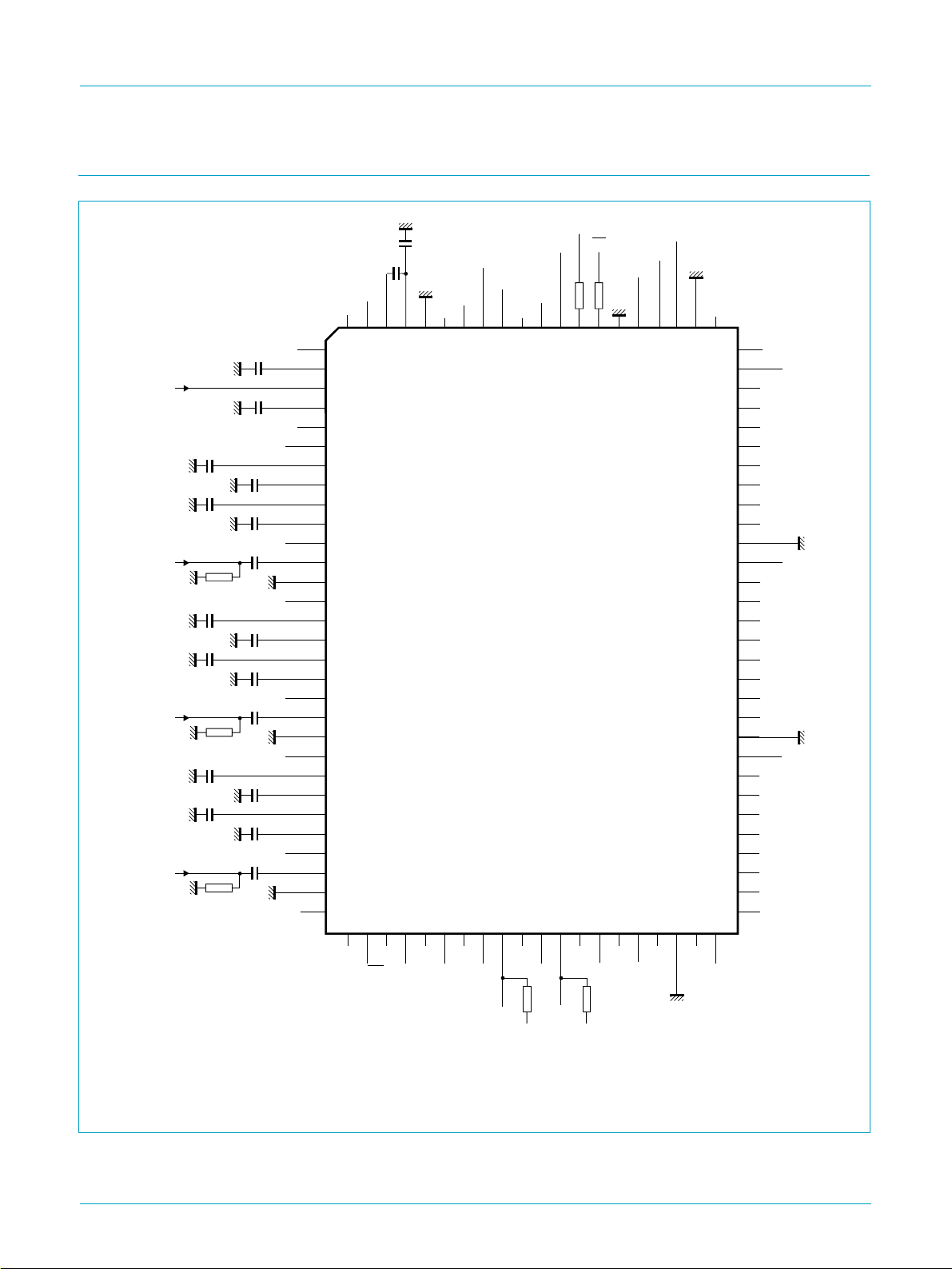

6. Block diagram

TDA8752B

Triple high-speed Analog-to-Digital Converter 110 Msps

RAGC

RGAINC

RIN

RDEC

V

GAGC

GGAINC

GIN

GDEC

BAGC

BGAINC

BIN

BDEC

TDO

TCK

ADD2

ADD1

SEN

SCL

SDA

DIS

2

I

C/3W

V

ref

CCA(R)

V

CCA(G)

11

6

8

12

10

3

14

16

20

18

22

24

28

26

36

35

34

33

38

42

39

37

32

1, 5, 30, 31, 43 , 44

50, 51, 100

V

CCA(B)

V

DDD

19

27

SERIAL

INTERFACE

2

I

C-BUS

OR

3-WIRE

V

CCO(R)

40

V

CCO(G)

79

MUX

V

CCO(B)

69

HSYNCI

2

C-bus; 1-bit

I

(Hlevel)

90

59

V

CCA(PLL)

V

V

CCD

95

99

GREEN CHANNEL

G

AGND

21

V

SSD

B

29

ADC

CCO(PLL)

85

CLAMP

CLP

AGND

89

AGND

R

13

RED CHANNEL

BLUE CHANNEL

TDA8752B

REGULATOR

4 2 88 97 98

DEC2DEC1HSYNCn.c.

PWDWN

CP

OGND

41

PLL

OGND

70

CZ

G

OGND

R

60

OUTPUTS

AGND

B

48

PLL

OGND

96

DGND

PLL

86

82

71 to 78

61 to 68

49, 52 to 58

FCE467

45

17

15

25

23

47

84

83

81

80

92

91

93

94

9

7

46

87

RCLP

RBOT

R0 to R7

ROR

GCLP

GBOT

G0 to G7

GOR

OE

BCLP

BBOT

B0 to B7

BOR

CKADCO

CKBO

CKAO

CKREFO

CKEXT

INV

COAST

CKREF

Fig 1. Block diagram.

9397 750 07338

Product specification Rev. 03 — 21 July 2000 4 of 38

© Philips Electronics N.V. 2000. All rights reserved.

Page 5

Philips Semiconductors

TDA8752B

Triple high-speed Analog-to-Digital Converter 110 Msps

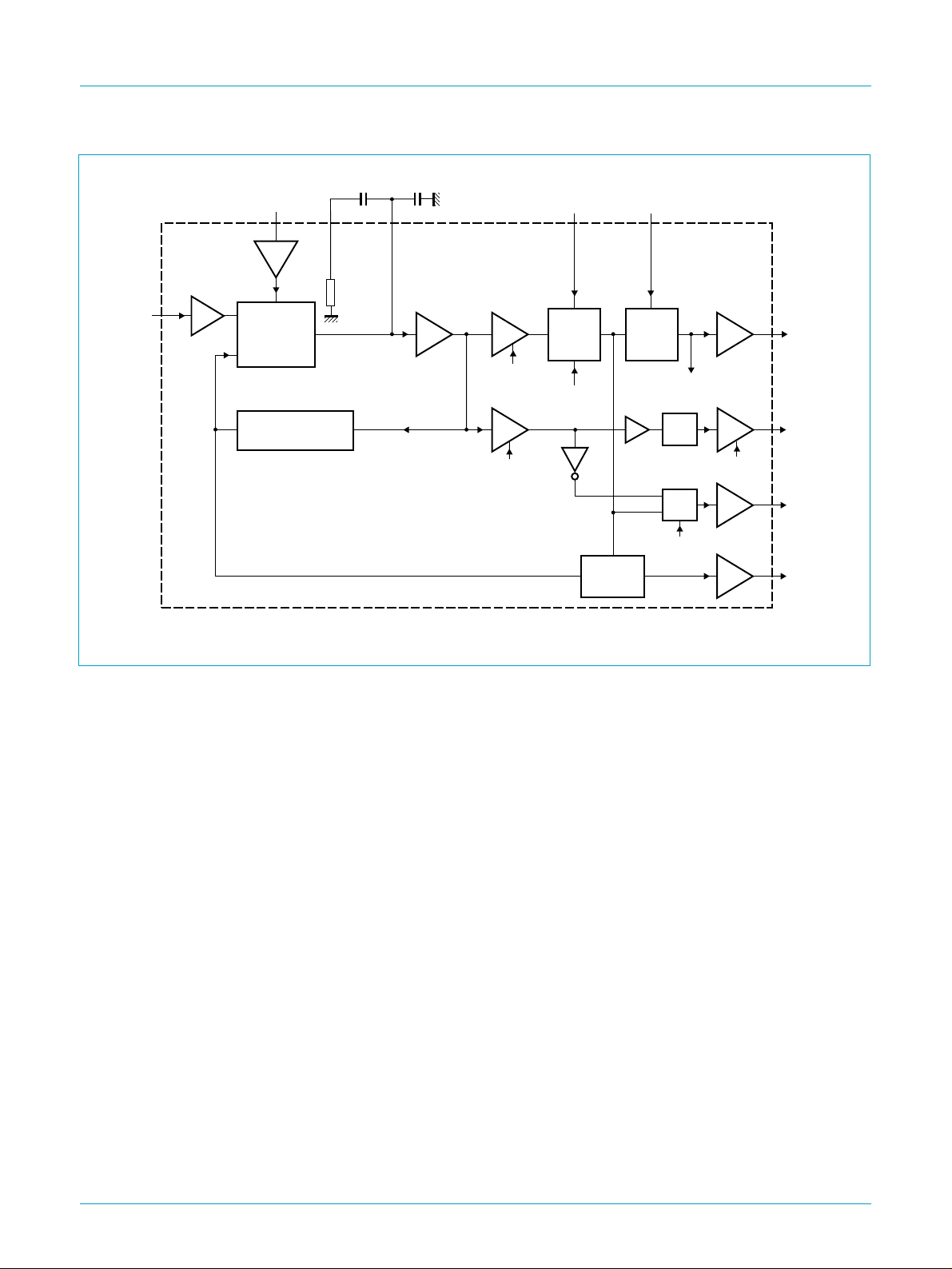

CLP RAGC

RCLP

V

P

150

RIN

V

ref

kΩ

3 kΩ

45 kΩ

FINE GAIN ADJUST

2

I

DAC

5

REGISTER

C-bus: 5 bits (Fr) I2C-bus: 7 bits (Cr)

Fig 2. Red channel diagram.

MUX

HSYNCI

CLAMP

CONTROL

AGC

RGAINC

V

CCAR

CLKADC

ADC

8

D

D ≥ R

R

8

1

7

1

REGISTER

COARSE GAIN ADJUST

DAC

8

REGISTER

2

C-bus: 8 bits (Or)

I

OUTPUTS

I2C-BUS

ROR

8

R0 to R7

OE

RBOT

FCE468

9397 750 07338

© Philips Electronics N.V. 2000. All rights reserved.

Product specification Rev. 03 — 21 July 2000 5 of 38

Page 6

Philips Semiconductors

TDA8752B

Triple high-speed Analog-to-Digital Converter 110 Msps

CKREF

2

I

C-bus; 1 bit

(Vlevel)

edge selector

2

I

C-bus;

1 bit

(Edge)

COAST

PHASE

FREQUENCY

DETECTOR

2

C-bus; 5 bits

I

(Ip, Up, Do)

DIV N (100 to 4095)

2

C-bus; 12 bits (Di)

I

C

Z

CZ CP

loop filter

2

I

C-bus;

3 bits (Z)

C

P

VCO

2

C-bus;

I

2 bits (Vco)

12 to

100 MHz

phase selector A

2

I

C-bus;

5 bits (Pa)

phase selector B

2

C-bus; 5 bits (Pb)

I

CKEXT INV

MUX

2

C-bus;

I

1 bit (Cka)

NCKBO

SYNCHRO

0°/180°

CLKADC

MUX

MUX

2

C-bus;

I

1 bit (Ckab)

2

C-bus;

I

1 bit (Ckb)

FCE465

CKADCO

CKBO

CKAO

CKREFO

Fig 3. PLL diagram.

9397 750 07338

© Philips Electronics N.V. 2000. All rights reserved.

Product specification Rev. 03 — 21 July 2000 6 of 38

Page 7

Philips Semiconductors

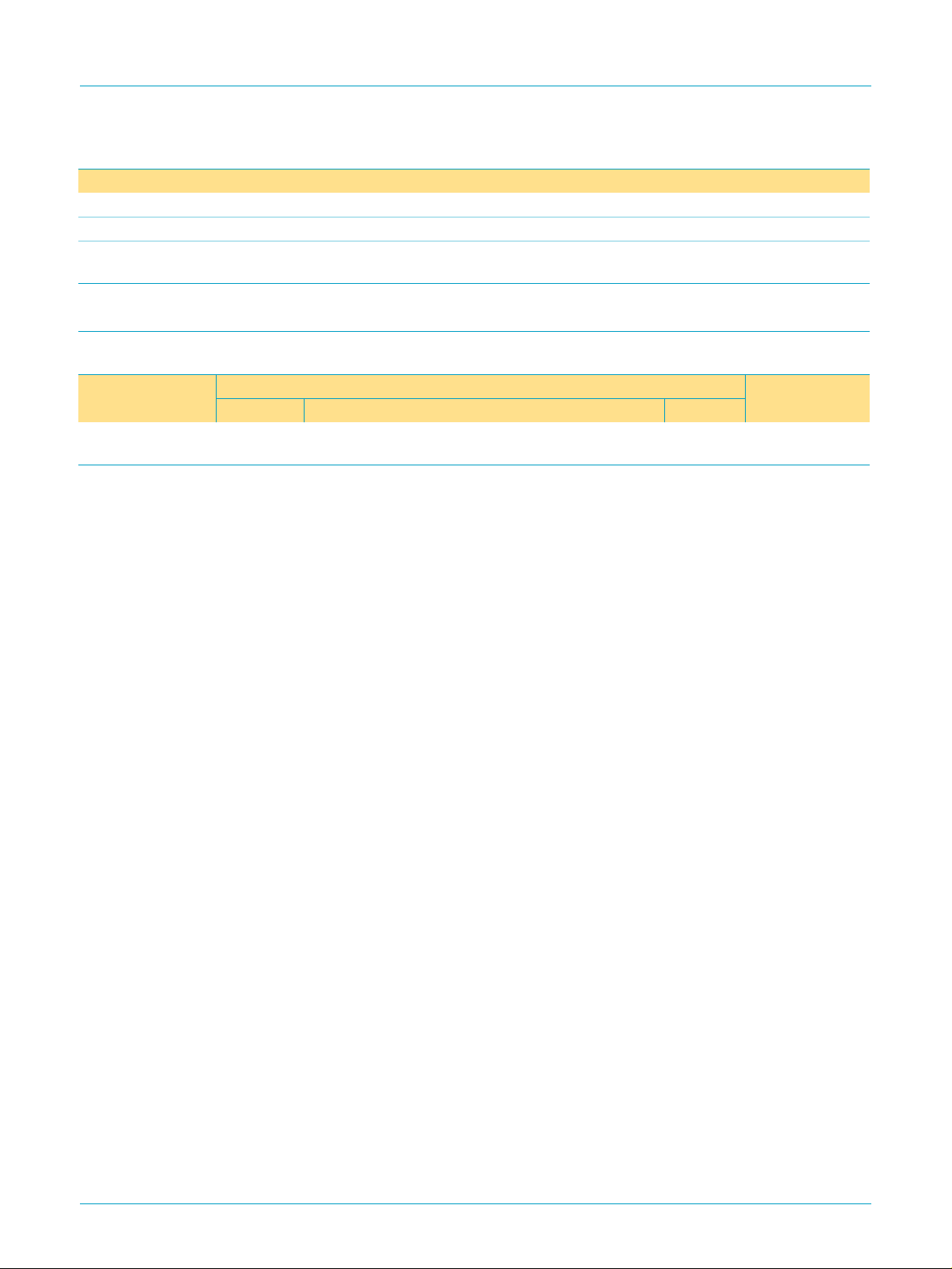

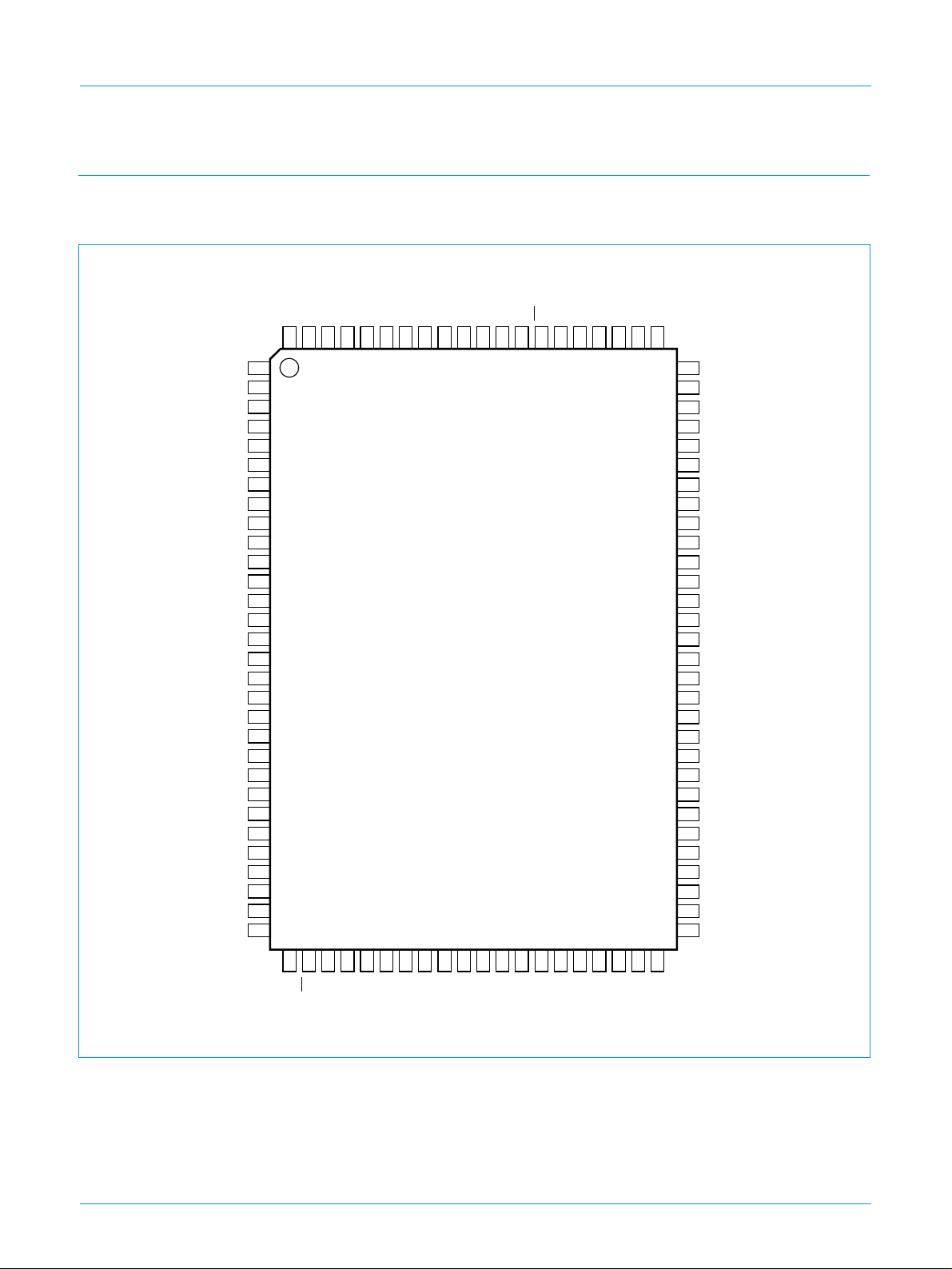

7. Pinning information

7.1 Pinning

TDA8752B

Triple high-speed Analog-to-Digital Converter 110 Msps

DEC2

V

DEC1

RAGC

RBOT

RGAINC

RCLP

RDEC

V

CCA(R)

RIN

AGND

GAGC

GBOT

GGAINC

GCLP

GDEC

V

CCA(G)

GIN

AGND

BAGC

BBOT

BGAINC

BCLP

BDEC

V

CCA(B)

AGND

n.c.

n.c.

BIN

n.c.

CKADCO

CKBO

PLL

OGND

CKAO

80

79

78

77

76

75

74

73

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

5130

CKREFO

V

CCO(R)

R7

R6

R5

R4

R3

R2

R1

R0

OGND

V

CCO(G)

G7

G6

G5

G4

G3

G2

G1

G0

OGND

V

CCO(B)

B7

B6

B5

B4

B3

B2

B1

n.c.

R

G

PLL

CCA(PLL)

n.c.

V

CZCPAGND

99989796959493929190898887868584838281

100

1

2

3

ref

4

5

6

7

8

9

10

11

12

13

R

14

15

16

17

18

19

20

21

G

22

23

24

25

26

27

28

29

B

CCD

V

CKREF

COAST

TDA8752BH

CKEXT

INV

HSYNC

CLP

PWDWNOEDGND

V

CCO(PLL)

31323334353637383940414243444546474849

n.c.

n.c.

C/3W

2

I

ADD1

ADD2

TCK

TDO

DIS

SEN

SDA

DDD

V

SSD

V

SCL

n.c.

ROR

GOR

BOR

B

B0

OGND

50

n.c.

FCE469

Fig 4. Pin configuration.

9397 750 07338

Product specification Rev. 03 — 21 July 2000 7 of 38

© Philips Electronics N.V. 2000. All rights reserved.

Page 8

Philips Semiconductors

7.2 Pin description

Table 3: Pin description

Symbol Pin Description

n.c. 1 not connected

DEC2 2 main regulator decoupling input 2

V

ref

DEC1 4 main regulator decoupling input 1

n.c. 5 not connected

RAGC 6 red channel AGC output

RBOT 7 red channel ladder decoupling input (BOT)

RGAINC 8 red channel gain capacitor input

RCLP 9 red channel gain clamp capacitor input

RDEC 10 red channel gain regulator decoupling input

V

CCA(R)

RIN 12 red channel gain analog input

AGND

GAGC 14 green channel AGC output

GBOT 15 green channel ladder decoupling input (BOT)

GGAINC 16 green channel gain capacitor input

GCLP 17 green channel gain clamp capacitor input

GDEC 18 green channel gain regulator decoupling input

V

CCA(G)

GIN 20 green channel gain analog input

AGND

BAGC 22 blue channel AGC output

BBOT 23 blue channel ladder decoupling input (BOT)

BGAINC 24 blue channel gain capacitor input

BCLP 25 blue channel gain clamp capacitor input

BDEC 26 blue channel gain regulator decoupling input

V

CCA(B)

BIN 28 blue channel gain analog input

AGND

n.c. 30 not connected

n.c. 31 not connected

2

C/3W 32 selection input between I2C-bus (active HIGH) and 3-wire

I

ADD1 33 I

ADD2 34 I

TCK 35 scan test mode input (active HIGH)

TDO 36 scan test output

DIS 37 I

SEN 38 select enable for 3-wire serial bus input (see Figure 10)

TDA8752B

Triple high-speed Analog-to-Digital Converter 110 Msps

3 gain stabilizer voltage reference input

11 red channel gain analog power supply

R

G

B

13 red channel gain analog ground

19 green channel gain analog power supply

21 green channel gain analog ground

27 blue channel gain analog power supply

29 blue channel gain analog ground

serial bus (active LOW)

2

C-bus address control input 1

2

C-bus address control input 2

2

C-bus and 3-wire serial bus disable control input (disable at

HIGH level)

9397 750 07338

Product specification Rev. 03 — 21 July 2000 8 of 38

© Philips Electronics N.V. 2000. All rights reserved.

Page 9

Philips Semiconductors

TDA8752B

Triple high-speed Analog-to-Digital Converter 110 Msps

Table 3: Pin description

…continued

Symbol Pin Description

SDA 39 I2C-bus/3-wire serial bus data input

V

DDD

V

SSD

SCL 42 I

40 logic I2C-bus/3-wire serial bus digital power supply

41 logic I2C-bus/3-wire serial bus digital ground

2

C-bus/3-wire serial bus clock input

n.c. 43 not connected

n.c. 44 not connected

ROR 45 red channel ADC output bit out of range

GOR 46 green channel ADC output bit out of range

BOR 47 blue channel ADC output bit out of range

OGND

B

48 blue channel ADC output ground

B0 49 blue channel ADC output bit0 (LSB)

n.c. 50 not connected

n.c. 51 not connected

B1 52 blue channel ADC output bit1

B2 53 blue channel ADC output bit2

B3 54 blue channel ADC output bit3

B4 55 blue channel ADC output bit4

B5 56 blue channel ADC output bit5

B6 57 blue channel ADC output bit6

B7 58 blue channel ADC output bit7 (MSB)

V

CCO(B)

OGND

G

59 blue channel ADC output power supply

60 green channel ADC output ground

G0 61 green channel ADC output bit 0 (LSB)

G1 62 green channel ADC output bit 1

G2 63 green channel ADC output bit 2

G3 64 green channel ADC output bit 3

G4 65 green channel ADC output bit 4

G5 66 green channel ADC output bit 5

G6 67 green channel ADC output bit 6

G7 68 green channel ADC output bit 7 (MSB)

V

CCO(G)

OGND

R

69 green channel ADC output power supply

70 red channel ADC output ground

R0 71 red channel ADC output bit 0 (LSB)

R1 72 red channel ADC output bit 1

R2 73 red channel ADC output bit 2

R3 74 red channel ADC output bit 3

R4 75 red channel ADC output bit 4

R5 76 red channel ADC output bit 5

R6 77 red channel ADC output bit 6

R7 78 red channel ADC output bit 7 (MSB)

V

CCO(R)

79 red channel ADC output power supply

9397 750 07338

Product specification Rev. 03 — 21 July 2000 9 of 38

© Philips Electronics N.V. 2000. All rights reserved.

Page 10

Philips Semiconductors

TDA8752B

Triple high-speed Analog-to-Digital Converter 110 Msps

Table 3: Pin description

…continued

Symbol Pin Description

CKREFO 80 reference output clock re-synchronized horizontal pulse

CKAO 81 PLL clock output 3 (in phase with reference output clock

CKBO)

OGND

PLL

CKAO or

82 PLL digital ground

CKBO 83 PLL clock output 2

CKADCO 84 PLL clock output1 (in phase with internal ADC clock)

V

CCO(PLL)

85 PLL output power supply

DGND 86 digital ground

OE 87 outputenable; active LOW (when OEis HIGH, the outputs are

in high-impedance)

PWDWN 88 power-down control input (device is in Power-down mode

when this pin is HIGH)

CLP 89 clamp pulse input (clamp active HIGH)

HSYNC 90 horizontal synchronization input pulse

INV 91 PLL clock output inverter command input (invert when HIGH)

CKEXT 92 external clock input

COAST 93 PLL coast command input

CKREF 94 PLL reference clock input

V

CCD

AGND

PLL

95 digital power supply

96 PLL analog ground

CP 97 PLL filter input

CZ 98 PLL filter input

V

CCA(PLL)

99 PLL analog power supply

n.c. 100 not connected

9397 750 07338

Product specification Rev. 03 — 21 July 2000 10 of 38

© Philips Electronics N.V. 2000. All rights reserved.

Page 11

Philips Semiconductors

8. Functional description

This triple high-speed 8-bit ADC is designed to convert RGB signals, coming from an

analog source, into digital data used by a LCD driver (pixel clockupto 200 MHz when

using 2 ICs).

8.1 IC analog video inputs

The video inputs are internally DC polarized. These inputs are AC coupled externally.

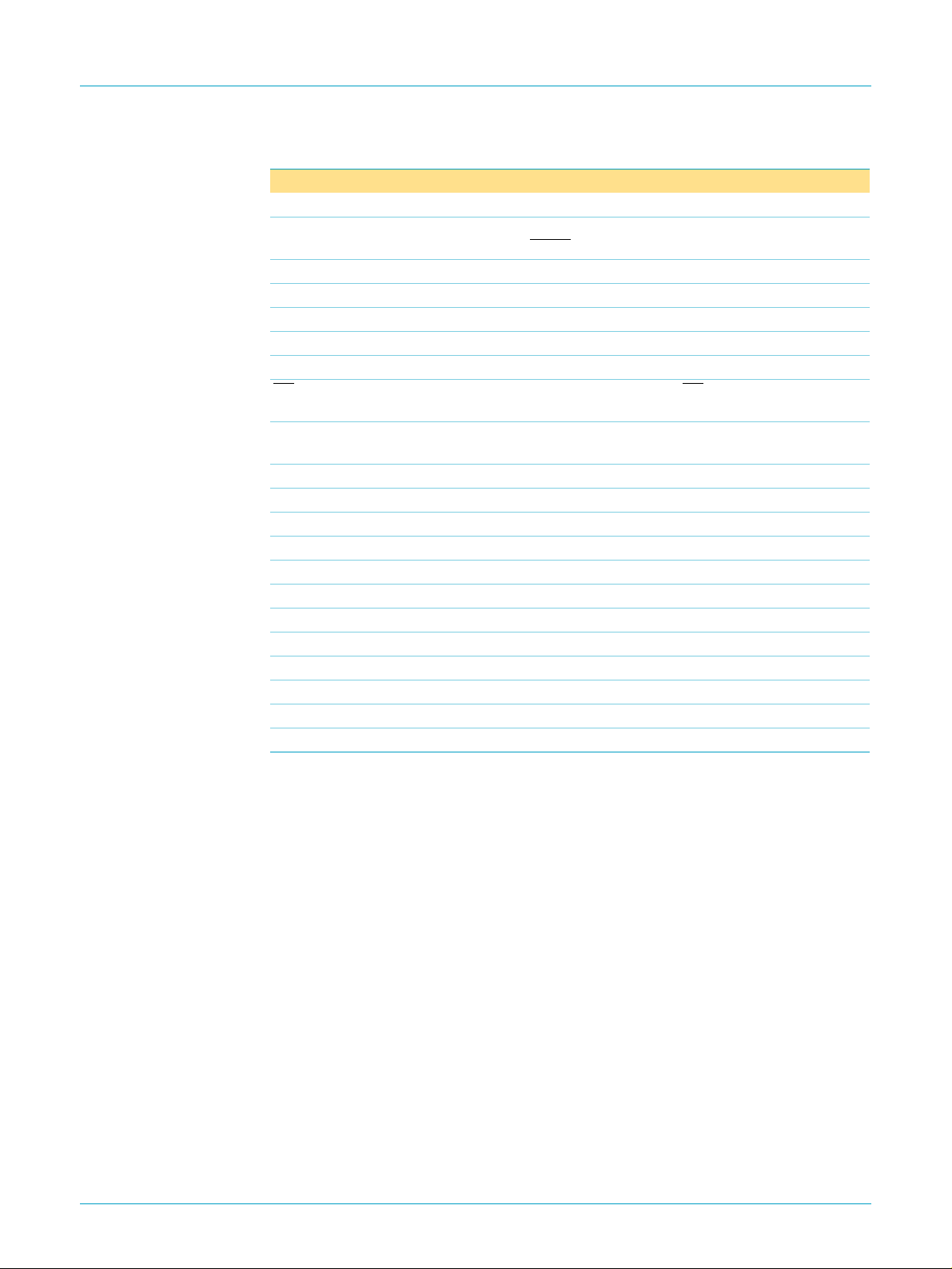

8.2 Clamps

Three independent parallel clamping circuits are used to clamp the video input

signals on the black level and to control the brightness level. The clamping code is

programmable between code −63.5 and +64 and from +120 to +136 in steps of

1

⁄2LSB. The programming of the clamp value is achieved via an 8-bit DAC. Each

clamp must be able to correct an offset from ±0.1 V to ±10 mV within 300 ns, and

correct the total offset in 10 lines.

TDA8752B

Triple high-speed Analog-to-Digital Converter 110 Msps

Fig 5. Clamp definition.

8.3 Variable gain amplifiers

The clamps are controlled by an external TTL positive going pulse (pin CLP). The

drop of the video signal is <1 LSB.

Normally, the circuit operates with a 0 code clamp, corresponding to the 0 ADC code.

This clamp code can be changed from −63.5 to +64 as represented in Figure 5, in

steps of1⁄2LSB. The digitizedvideo signal is alwaysbetween code 0 and code 255 of

the ADC. It is also possible to clamp from code 120 to code 136 corresponding to

120 ADC code to 136 ADC code. Then clamping on code 128 of the ADC is possible.

255

digitized

video signal

CLP

video

signal

code 64

code 0

−63.5

code

clamp

programming

FCE471

= 120 to 136

Three independent variable gain amplifiers are used to provide, to each channel, a

full-scale input range signal to the 8-bit ADC. The gain adjustment range is designed

so that for an input range varying from 0.4 to 1.2 V (p-p), the output signal

corresponds to the ADC full-scale input of 1 V (p-p).

To ensure that the gain does not vary over the whole operating temperature range, an

external supplied reference voltage V

= 2.5 V (DC), with a maximum variation of

ref

100 ppm/°C, is used to calibrate the gain at the beginning of each video line before

the clamp pulse.

9397 750 07338

Product specification Rev. 03 — 21 July 2000 11 of 38

© Philips Electronics N.V. 2000. All rights reserved.

Page 12

Philips Semiconductors

The calibration of the gains is done using the following principle.

TDA8752B

Triple high-speed Analog-to-Digital Converter 110 Msps

From the reference voltage V

a reference signal of 0.156 V (p-p) (1⁄16V

ref

ref

) is

generated internally. During the synchronization part of the video line, the multiplexer,

controlled by the TTL synchronization signal (HSYNCI, coming from HSYNC;

see Figure 1) with a width equal to one of the video synchronization signals (e.g. the

signal coming from a synchronization separator), is switched between the two

amplifiers.

The output of the multiplexer is either the normal video signal or the 0.156 V

reference signal (during HSYNC).

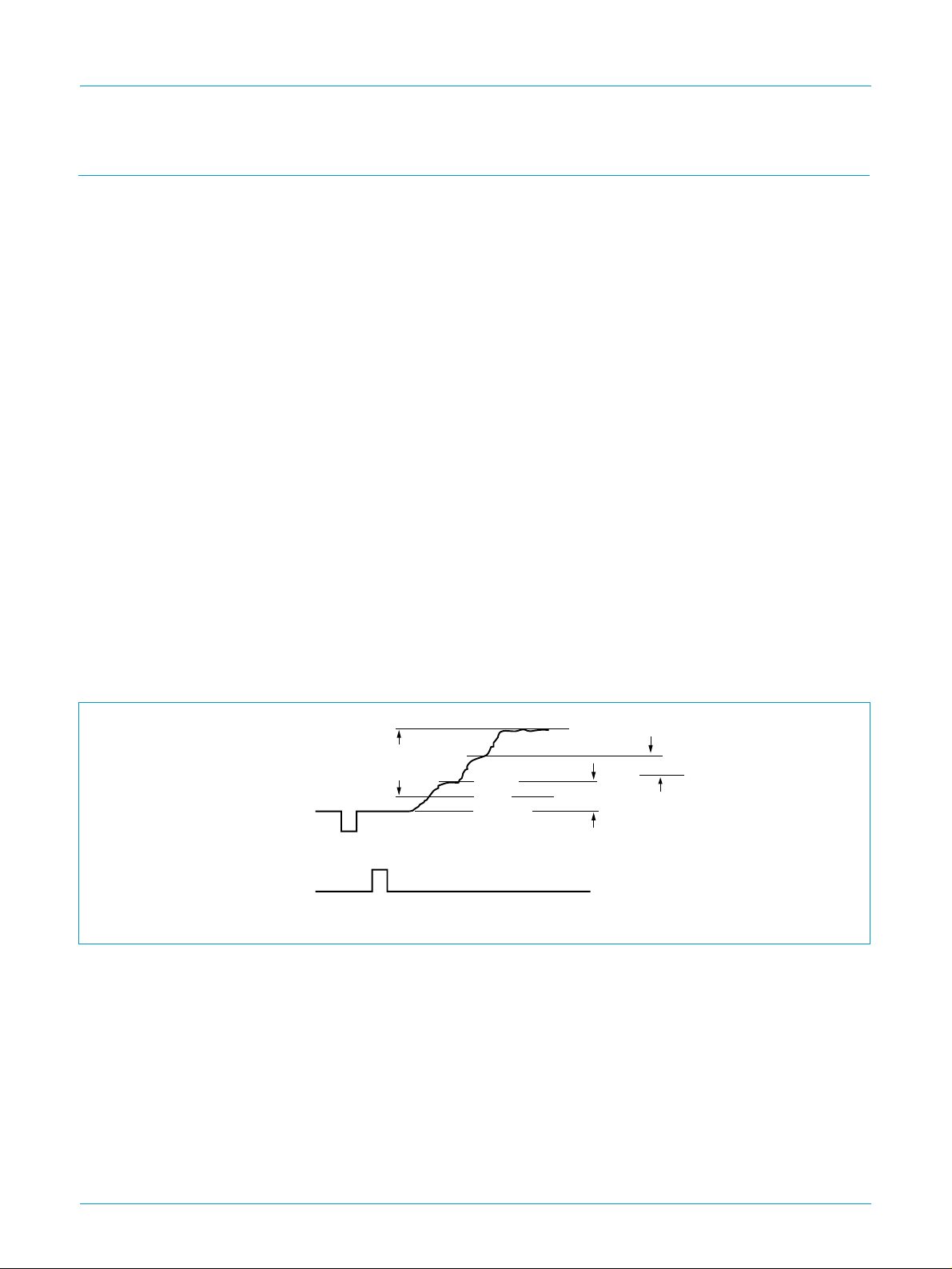

The corresponding ADC outputs are then compared to a preset value loaded in a

register. Depending on the result of the comparison, the gain of the variable gain

amplifiers is adjusted (coarse gain control; see Figure 2 and 6). The three 7-bit

registers receive data via a serial interface to enable the gain to be programmed.

The preset value loaded in the 7-bit register is chosen between approximately

67 codes to ensure the full-scale input range (see Figure 6). A contrast control can be

achieved using these registers. In this case care should be taken to stay within the

allowed code range (32 to 99).

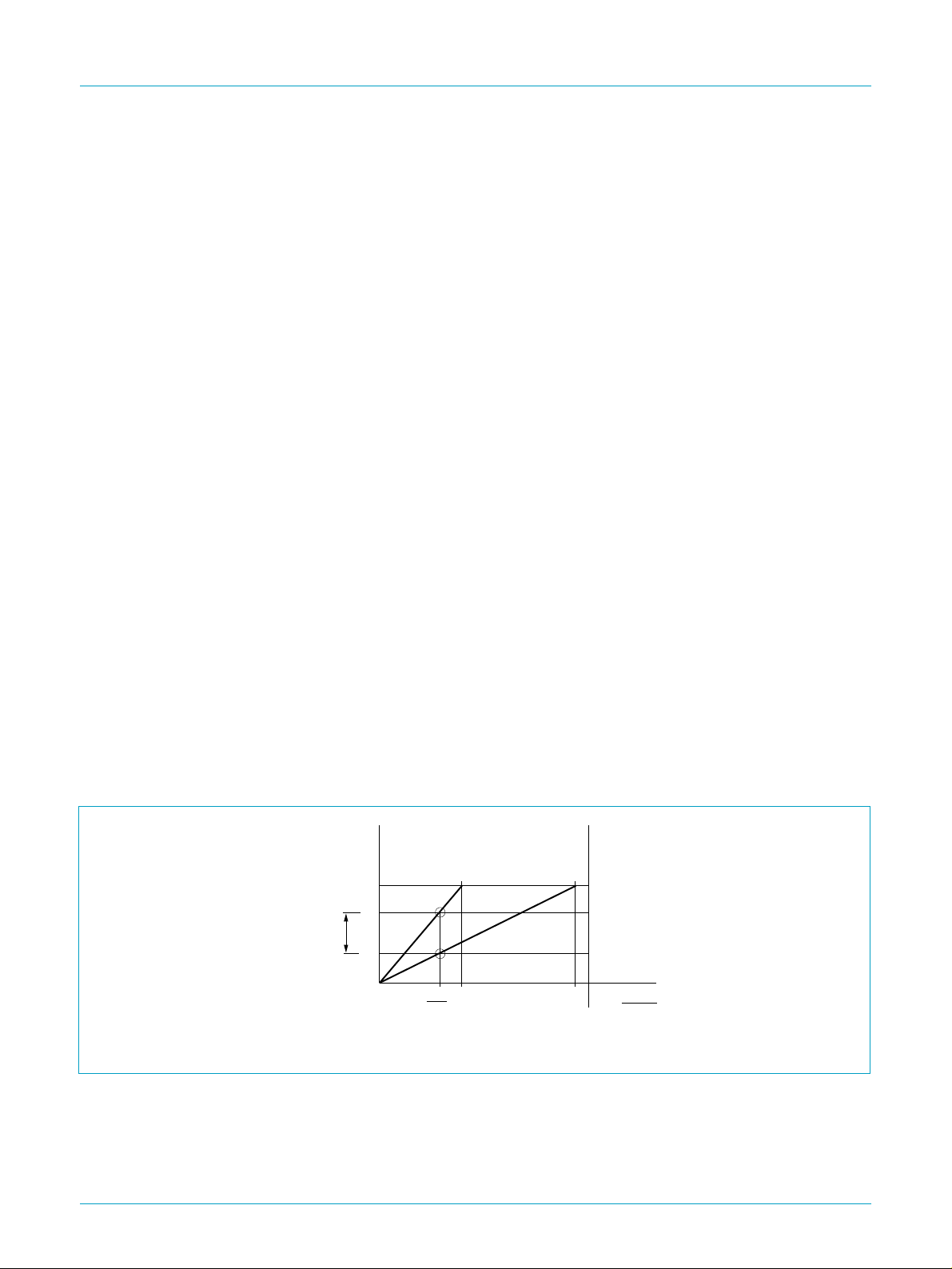

A fine correction using three 5-bit DACs, also controlled via the serial interface, is

used to fine tune the gain of the three channels (fine gain control; see Figure 2 and 7)

and to compensate the channel-to-channel gain mismatch.

With a full-scale ADC input, the resolution of the fine register corresponds to1⁄2LSB

peak-to-peak variation.

Fig 6. Coarse gain control.

To use these gain controls correctly,it is recommended to fix the coarse gain (to have

a full-scale ADC input signal) to within 4 LSB and then adjust it with the fine gain. The

gain is adjusted during HSYNC. During this time the output signal is not related to the

amplified input signal. The outputs, when the coarse gain system is stable, are

related to the programmed coarse code (see Figure 6).

0.6

ADC output

code

255

227

160

128

V

i (p-p)

2

FCE472

N

COARSE

coarse

register

value

(67 codes)

code

127

99

32

0

0.156 =

G

(max)

G

(min)

V

0.2

ref

16

9397 750 07338

Product specification Rev. 03 — 21 July 2000 12 of 38

© Philips Electronics N.V. 2000. All rights reserved.

Page 13

Philips Semiconductors

coarse

register

value

(67 codes)

ADC

output code

255

227

N

COARSE

160

TDA8752B

Triple high-speed Analog-to-Digital Converter 110 Msps

G

NCOARSE

G

(max)

G

(min)

128

Fig 7. Fine gain correction for a coarse gain G

8.4 ADCs

The ADCs are 8-bit with a maximum clock frequency of 110 Msps. The ADCs input

range is 1 V (p-p) full-scale. One out of range bit exists per channel (ROR, GOR and

BOR). It will be at logic 1 when the signal is out of range of the full-scale of the ADCs.

Pipeline delay in the ADCs is 1 clock cycle from sampling to data output.

The ADCs reference ladders regulators are integrated.

8.5 ADC outputs

ADC outputs are straight binary. An output enable pin (OE; active LOW) enables the

output status between active and high-impedance (OE = HIGH) to be switched; it is

recommended to load the outputs with a 10 pF capacitive load. The timing must be

checked very carefully if the capacitive load is more than 10 pF.

8.6 Phase-locked loop

NCOARSE

N

FINE

.

N

FINE

= 31

= 0

V

ref

FCE473

The ADCs are clocked either by an internal PLL locked to the CKREF clock (all of the

PLL is on-chip except the loop filter capacitance) or by an external clock applied to

pin CKEXT. Selection is performed via the serial interface bus.

The reference clock (CKREF) range is between 15 and 280 kHz. Consequently, the

VCO minimum frequency is 12 MHz and the maximum frequency is 110 MHz. The

gain of the VCO part can be controlled via the serial interface, depending on the

frequency range to which the PLL is locked.

To increase the bandwidth of the PLL, the charge pump current, controlled by the

serial interface, must also be increased. The relationship between the frequency and

the current is given by the following equation:

1

f

------

n

2π

9397 750 07338

Product specification Rev. 03 — 21 July 2000 13 of 38

KOIP⋅

------------------------------------- -⋅=

CZCP+()DR⋅

(1)

© Philips Electronics N.V. 2000. All rights reserved.

Page 14

Philips Semiconductors

Where:

fn= the natural PLL frequency

KO= the VCO gain

DR = PLL divider ratio

CZ and CP= capacitors of the PLL filter.

The other PLL equation is as follows:

TDA8752B

Triple high-speed Analog-to-Digital Converter 110 Msps

f

=

z

1

----------------------------- -

2π R× CZ×

and ξ

f

1

n

×=

-- -

-----

2

f

z

(2)

Where:

fz= loop filter zero frequency

R = the chosen resistance for the filter

ξ = the damping factor

FO= 0 dB loop gain frequency.

Different resistances for the filter can be programmed via the serial interface. To

improve the performances, the PLL parameters should be chosen so that:

2ξ fn⋅ RIP⋅⇒

==

O

F

O

0.15 R I

--------- -

f

ref

2π DR× FO×

---------------------------------- -

K

O

0.3π DR× f

≤⋅⇒≤ Lim=

----------------------------------------- -

P

×

K

O

ref

(3)

(4)

The values of R and IP must be chosen so that the product is the closest to Lim. In

the eventthat there are several choices, the couple forwhich the ξ value is the closest

to 1 must be chosen.

A software program called “PLL calculator’” is available on Philips Semiconductor

Internet site to calculate the best PLL parameters.

It is possible to control (independently) the phase of the ADC clock and the phase of

an additional clock output (which could be used to drive a second TDA8752B). For

this, two serial interface-controlled digital phase-shift controllers are included

(controlled by 5-bit registers, phase-shift controller steps are 11.25 deg each on the

whole PLL frequency range).

CKREF is re-synchronized, by the synchro block, on the CKAO clock. The output is

CKREFO (LOW during 8 clock periods). CKAO is the clock at the output of the phase

selector A. This clock can be used as the clocks for CKBO and CKADCO. The timing

is given in Figure 8.

Pin COAST is used to disconnect the PLL phase frequency detector during the frame

flyback or the unavailability of the CKREF signal. This signal can normally be derived

from the VSYNC signal.

The clock output is able to drive an external 10 pF load (for the on-chip ADCs).

9397 750 07338

Product specification Rev. 03 — 21 July 2000 14 of 38

© Philips Electronics N.V. 2000. All rights reserved.

Page 15

Philips Semiconductors

The PLL can be used in three different methods:

•

•

•

TDA8752B

Triple high-speed Analog-to-Digital Converter 110 Msps

The IC can be used as stand-alone with a sampling frequency of up to 110 MHz.

When an RGB signal is at a pixel frequency exceeding 100 to 200 MHz, it is

possible to follow one of the two possibilities given below:

– Using one TDA8752B: the sampling rate can be reduced by a factor of two, by

sampling the even pixels in the even frame and the odd pixels in the odd frame.

Pin INV is used to toggle between the frames.

– Using two TDA8752Bs: the PLL of the master TDA8752B is used to drive both

ADC clocks. The PLL of the slave TDA8752B is disconnected and the CKBO of

the master TDA8752Bis connected to pin CKEXT of the TDA8752B master and

CKAO to the slave TDA8752B. In this case, on pin CKAO CKBO will be the

output (with bit CKAB of the master at logic 1).

The master TDA8752B is used to sample the even pixels and the slave

TDA8752B forodd pixels,using a 180 deg phase shift between the clocks (both

pins CKADCO). The master chip and the slave chip have their pin INV LOW,

which guarantees the 180 deg shift ADC clock drive. It is then necessary to

adjust phase B of the master chip. Special care should be taken with the quality

of the input signal (input settling time).

If CKREFO output signal at the master chip is needed, it is possible to use one

of the two phase A values in order to avoid set-up and hold problems in the

SYNCHRO function; e.g. PHASEA = 100000 and PHASEA = 111111.

When INV is LOW, CKADCO is equal to CKEXT inverted.

CKREF

CKAO

CKREFO

t

CKAO=tCLK(buffer)+tphase selector

t

= either t

CKREFO

CKAO

Fig 8. Timing diagram.

t

CKAO

t

CKREFO

[t

CLK(buffer)

T

CLK(pixel)

− if PHASEA ≥ 01000 or t

------------------------

2

= 10 ns and t

phase selector

t

phase selector

=].

-------------------------- -

2π

T

CLK(pixel)

+ if PHASEA < 01000.

------------------------

CKAO

2

T

×

FCE470

CLK(pixel)

9397 750 07338

Product specification Rev. 03 — 21 July 2000 15 of 38

© Philips Electronics N.V. 2000. All rights reserved.

Page 16

Philips Semiconductors

CKREF

Triple high-speed Analog-to-Digital Converter 110 Msps

COAST CKEXT INV

12 to

100 MHz

MUX

phase selector A

PLL

2

I

C-bus;

5 bits (Pa)

phase selector B

2

C-bus; 5 bits (Pb)

I

Master TDA8752B

(even pixels)

2

I

C-bus;

1 bit (Cka)

(Cka = 1)

NCKBO

SYNCHRO

0 /180

I2C-bus;

1 bit (Ckab)

(Ckab = 1)

CLKADC

MUX

MUX

I2C-bus;

1 bit (Ckb)

(Ckb = 1)

TDA8752B

CKADCO

CKBO

CKAO

CKREFO

CKEXT INV

MUX

2

I

C-bus;

1 bit (Cka)

(Cka = 1)

NCKBO

SYNCHRO

0 /180

I2C-bus;

1 bit (Ckab)

(Ckab = 0)

CLKADC

MUX

MUX

I2C-bus;

1 bit (Ckb)

(Ckb = 0)

CKADCO

CKBO

CKAO

CKREFO

FCE466

CKREF

PLL

COAST

12 to

100 MHz

phase selector A

2

I

C-bus;

5 bits (Pa)

phase selector B

2

C-bus; 5 bits (Pb)

I

Slave TDA8752B

(odd pixels)

Slave at 180 deg phase shift with respect to pin CKADCO of the master TDA8752B.

Fig 9. Dual TDA8752B solution for pixel clock rate with a single phase adjustment (100 to 200 MHz).

8.7 I2C-bus and 3-wire serial bus interface

The I2C-bus and 3-wire serial buses control the status of the different control DACs

and registers. Control pin DIS enables or disables the full serial interface function

(disable at HIGH level). Four ICs can be used in the same system and programmed

by the same bus. Therefore, two pins (ADD1 and ADD2) are available to set each

address respectively, for use with the I2C-bus interface. All programming is described

in Section 9 “I2C-bus and 3-wire serial bus interfaces”.

9397 750 07338

© Philips Electronics N.V. 2000. All rights reserved.

Product specification Rev. 03 — 21 July 2000 16 of 38

Page 17

Philips Semiconductors

TDA8752B

Triple high-speed Analog-to-Digital Converter 110 Msps

9. I2C-bus and 3-wire serial bus interfaces

9.1 Register definitions

The configuration of the different registers is shown in Table 4.

Table 4: I2C-bus and 3-wire serial bus registers

Function

name

SUBADDR −−−−−−−−X X X Mode Sa3 Sa2 Sa1 Sa0 XXX1 0000

OFFSETR XXXX0000Or7 Or6 Or5 Or4 Or3Or2Or1Or00111 1111

COARSER XXXX0001Or8 Cr6 Cr5 Cr4 Cr3Cr2Cr1Cr00010 0000

FINER XXXX0010X X X Fr4 Fr3 Fr2 Fr1 Fr0 XXX0 0000

OFFSETG XXXX0011Og7 Og6 Og5 Og4 Og3Og2Og1Og00111 1111

COARSEG XXXX0100Og8 Cg6 Cg5 Cg4 Cg3Cg2Cg1Cg00010 0000

FINEG XXXX0101X X X Fg4 Fg3Fg2Fg1Fg0XXX0 0000

OFFSETB XXXX0110Ob7 Ob6 Ob5 Ob4 Ob3Ob2Ob1Ob00111 1111

COARSEB XXXX0111Ob8 Cb6 Cb5 Cb4 Cb3Cb2Cb1Cb00010 0000

FINEB XXXX1000X X X Fb4 Fb3Fb2Fb1Fb0XXX0 0000

CONTROL XXXX1001VlevelHlevelEdge Up Do Ip2 Ip1 Ip0 0000 0100

VCO XXXX1010Z2 Z1 Z0 Vco1 Vco0 Di11 Di10 Di9 0110 0001

DIVIDER

(LSB)

PHASEA XXXX1100X Di0 Cka Pa4 Pa3Pa2Pa1Pa0X000 0000

PHASEB XXXX1101X Ckab Ckb Pb4 Pb3 Pb2 Pb1 Pb0 X000 0000

Subaddress Bit definition Default

A7 A6 A5 A4 A3 A2 A1 A0 MSB LSB

XXXX1011Di8 Di7 Di6 Di5 Di4 Di3 Di2Di11001 0000

value

All the registers are defined by a subaddress of 8 bits; bit A4 refers to the mode which

is used with the I2C-bus interface; bits Sa3 to Sa0 are the subaddresses of each

register.

Bit Mode, used only with the I2C-bus, enables two modes to be programmed:

Mode 0 if bit Mode = 0, each register is programmed independently by giving its

subaddress and its content

Mode 1 if bit Mode = 1, all the registers are programmed one after the other by

giving this initial condition (XXX1 1111) as the subaddress state; thus,

the registers are charged following the predefined sequence of 16 bytes

(from subaddress 0000 to 1101).

9.1.1 Offset register

This register controls the clamp levelforthe RGB channels. The relationship between

the programming code and the level of the clamp code is given in Table 5.

9397 750 07338

Product specification Rev. 03 — 21 July 2000 17 of 38

© Philips Electronics N.V. 2000. All rights reserved.

Page 18

Philips Semiconductors

Table 5: Coding

Programmed code Clamp code ADC output

0 −63.5 underflow

1 −63

2 −62.5

... ...

127 0 0

... ... ...

254 63.5 63 or 64

255 64 64

256 120 120

... ... ...

287 136 136

The default programmed value is:

•

•

•

TDA8752B

Triple high-speed Analog-to-Digital Converter 110 Msps

Programmed code = 127

Clamp code = 0

ADC output = 0.

9.1.2 Coarse and fine registers

These two registers enable the gain control, the AGC gain with the coarse register

and the reference voltage with the fine register. The coarse register programming

equation is as follows:

GAIN

Where: V

N

COARSE

----------------------------------------------- -

V

1

⋅

ref

= 2.5 V.

ref

N

–

----------------- -

32 16×

1+

FINE

The gain correspondence is given in Table 6. The gain is linear with reference to the

programming code (N

Table 6: Gain correspondence (COARSE)

N

COARSE

32 0.825 1.212

99 2.5 0.4

FINE

The default programmed value is as follows:

N

•

COARSE

Gain = 0.825

•

Vi to be full-scale = 1.212 V.

•

=32

1

×

----- -

16

N

COARSE

--------------------------------------------------

V

512 N

ref

1+

–()⋅

FINE

32×==

= 0).

Gain Vi to be full-scale (V)

(5)

To modulate this gain, the fine register is programmed using the above equation. With

a full-scale ADC input, the fine register resolution is a1⁄2LSB peak-to-peak

(see Table 7 for N

9397 750 07338

Product specification Rev. 03 — 21 July 2000 18 of 38

COARSE

= 32).

© Philips Electronics N.V. 2000. All rights reserved.

Page 19

Philips Semiconductors

Table 7: Gain correspondence (FINE)

N

FINE

0 0.825 1.212

31 0.878 1.139

TDA8752B

Triple high-speed Analog-to-Digital Converter 110 Msps

Gain Vi to be full-scale (V)

The default programmed value is: N

9.1.3 Control register

COAST and HSYNC signals can be inverted by setting the I2C-bus control bits

‘Vlevel’ and ‘Hlevel’ respectively. When ‘Vlevel’ and ‘Hlevel’ are set to zero

respectively, COAST and HSYNC are active HIGH.

The bit ‘Edge’ defines the rising or falling edge of CKREF to synchronize the PLL. It

will be on the rising edge if the bit is at logic 0 and on the falling edge if the bit is at

logic 1.

The bits ‘Up’ and ‘Do’ are used for the test, to force the charge pump current. These

bits have to be logic 0 during normal use.

The bits ‘Ip0’, ‘Ip1’ and ‘Ip2’ control the charge pump current, to increase the

bandwidth of the PLL, as shown in Table 8.

Table 8: Charge pump current control

Ip2 Ip1 Ip0 Current (µA)

0 0 0 6.25

0 0 1 12.5

01025

01150

100100

101200

110400

111700

FINE

=0.

The default programmed value is as follows:

Charge pump current = 100 µA

•

Test bits: no test mode; bits ‘Up’ and ‘Do’ at logic 0

•

Rising edge of CKREF: bit ‘Edge’ at logic 0

•

COAST and HSYNC inputs are active HIGH: bits ‘Vlevel’ and ‘Hlevel’ at logic 0.

•

9.1.4 VCO register

The bits ‘Z2’, ‘Z1’ and ‘Z0’ enable the internal resistance for the VCO filter to be

selected.

9397 750 07338

Product specification Rev. 03 — 21 July 2000 19 of 38

© Philips Electronics N.V. 2000. All rights reserved.

Page 20

Philips Semiconductors

Table 9: VCO register bits

Z2 Z1 Z0 Resistance (kΩ)

0 0 0 high impedance

001128

01032

01116

1008

1014

1102

1111

Table 10: VCO gain control

Vco1 Vco0 VCO gain (MHz/V) Pixel clock

0 0 15 10to20

0 1 20 20to40

1 0 35 40to70

115070to110

TDA8752B

Triple high-speed Analog-to-Digital Converter 110 Msps

frequency range

(MHz)

The bits Vco1 and Vco0 control the VCO gain.

The default programmed value is as follows:

Internal resistance = 16 kΩ

•

VCO gain = 15 MHz/V.

•

9397 750 07338

Product specification Rev. 03 — 21 July 2000 20 of 38

© Philips Electronics N.V. 2000. All rights reserved.

Page 21

Philips Semiconductors

9.1.5 Divider register

This register controls the PLL frequency. The bits are the LSB bits.

The default programmed value is 0011 0010 0000 = 800.

The MSB bits (Di11, Di10 and Di9) and the LSB bit (Di0) have to be programmed

before bits ‘Di8’ to ‘Di1’ are programmed, to obtain the required divider ratio. Bit ‘Di0’

is used for the parity divider number (bit ‘Di0’ = 0 means even number, while

bit ‘Di0’ = 1 means odd number). It should be noted that if the I2C-bus programmingis

done in mode 1 (bit Mode = 1) and bit ‘Di0’ has to be toggled, then the registers have

to be loaded twice to have the update divider ratio.

9.1.6 Power-down mode

•

•

TDA8752B

Triple high-speed Analog-to-Digital Converter 110 Msps

When the supply is completely switched off, the registers are set to their default

values; in that event they have to be reprogrammed if the required settings are

different (e.g. through an EEPROM)

When the device is in Power-down mode, the previously programmed register

values remain unaffected.

9.1.7 PHASEA and PHASEB registers

Bit ‘Cka’ is logic 0 when the used clock is the PLL clock, and logic 1 when the used

clock is the external clock.

Bit ‘Ckb’ is logic 0 when the second clock is not used.

Bits ‘Pa4’ to ‘Pa0’ and bits ‘Pb4’ to ‘Pb0’ are used to program the phase shift for the

clock, CKADCO,CKAO and CKBO (see Table 11). Concerning the PHASEB register,

bit ‘Ckab’ is used to have either CKAO or CKBO at pin CKAO (pin 81).

Table 11: Phase registers bits

Pa4 and Pb4 Pa3 and Pb3 Pa2 and Pb2 Pa1 and Pb1 Pa0 and Pb0 Phase shift (deg)

000000

0000111.25

... ... ... ... ... ...

11110337.5

11111348.75

The default programmed value is as follows:

No external clock: bit ‘Cka’ is logic 0

•

No use of the second clock: bit ‘Ckb’ is logic 0

•

Phase shift for CKAO and CKADCO is 0 deg

•

Phase shift for CKBO is 0 deg

•

Clock CKAO at pin CKAO: bit ‘Ckab’ is logic 0.

•

9397 750 07338

Product specification Rev. 03 — 21 July 2000 21 of 38

© Philips Electronics N.V. 2000. All rights reserved.

Page 22

Philips Semiconductors

Triple high-speed Analog-to-Digital Converter 110 Msps

9.2 I2C-bus protocol

Table 12: I2C-bus address

A7 A6 A5 A4 A3 A2 A1 A0

1 0 0 1 1 ADD2 ADD1 0

The I2C-bus address of the circuit is 1001 1xx0.

Bits ‘A2’ and ‘A1’ are fixed by the potential on pins ADD1 and ADD2. Thus, four

TDA8752Bs can be used on the same system, using the addresses for

ADD1 and ADD2 with the I2C-bus. Bit ‘A0’ must always be equal to logic 0 because it

is not possible to read the data in the register. The timing and protocol for the I2C-bus

are standard. Two sequences are available, see Table 13 and 14.

Table 13: Address sequence for mode 0

Where: S = START condition, ACK = acknowledge and P = STOP condition.

S IC ADDRESS ACK SUBADDRESS

REGISTER1

ACK DATA

REGISTER1

(see Table 4)

ACK SUBADDRESS

REGISTER2

TDA8752B

ACK ... P

Table 14: Address sequence for mode 1

Where: S = START condition, ACK = acknowledge and P = STOP condition.

S IC ADDRESS ACK SUBADDRESS

XXX1 1111

ACK DATA

REGISTER1

(see Table 4)

ACK DATA

REGISTER2

ACK ... P

9397 750 07338

Product specification Rev. 03 — 21 July 2000 22 of 38

© Philips Electronics N.V. 2000. All rights reserved.

Page 23

9397 750 07338

Product specification Rev. 03 — 21 July 2000 23 of 38

9.3 3-wire serial bus protocol

For the 3-wire serial bus the first byte refers to the register address which is programmed. The second byte refers to the

data to be sent to the chosen register (see Table 4). The acquisition is achieved via SEN.

Using the 3-wire serial bus interface, an indefinite number of ICs can operate on the same system. Pin SEN is used to

validate the circuits.

SEN

t

= 600 ns

r3W

1199

SCL

t

= 100 ns

s3W

t

h3W

Philips Semiconductors

100 ns

= 100 ns

SDA

Fig 10. 3-wire serial bus protocol.

© Philips Electronics N.V. 2000. All rights reserved.

XXXXA3A2A1A0XD7D6D5D4D3D2D1D0X

FCE474

Triple high-speed Analog-to-Digital Converter 110 Msps

TDA8752B

Page 24

Philips Semiconductors

10. Limiting values

Table 15: Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134).

Symbol Parameter Conditions Min Max Unit

V

V

V

V

∆V

V

I

o

I

I(OE)

I

I(PWDWN)

T

T

T

CCA

CCD

DDD

CCO

CC

i(RGB)

stg

amb

j

TDA8752B

Triple high-speed Analog-to-Digital Converter 110 Msps

analog supply voltage −0.3 +7.0 V

digital supply voltage −0.3 +7.0 V

logic supply voltage −0.3 +7.0 V

output stages supply voltage −0.3 +7.0 V

supply voltage differences

− V

V

CCA

CCD

− V

; V

V

V

V

CCO

CCA

CCA

− V

− V

CCD

DDD

CCO

; V

CCO

CCD

− V

− V

DDD

DDD

RGB input voltage range referenced

to AGND

output current − 10 mA

input current pin OE − 1.0 mA

input current pin PWDWN − 1.0 mA

storage temperature −55 +150 °C

ambient temperature 0 70 °C

junction temperature − 150 °C

−1.0 +1.0 V

−1.0 +1.0 V

−1.0 +1.0 V

−1.0 +1.0 V

−0.3 +7.0 V

11. Thermal characteristics

Table 16: Thermal characteristics

Symbol Parameter Conditions Value Unit

R

th(j-a)

thermal resistance from junction to

in free air 52 K/W

ambient

12. Characteristics

Table 17: Characteristics

V

CCA=V11

(V

86

OGND (V

values measured at V

Symbol Parameter Conditions Min Typ Max Unit

Supplies

V

CCA

V

CCD

V

DDD

V

CCO

I

CCA

9397 750 07338

Product specification Rev. 03 — 21 July 2000 24 of 38

(or V19,V27or V99) referenced to AGND (V13,V21,V29or V96) = 4.75 to 5.25 V; V

) = 4.75 to 5.25 V; V

48,V60,V70

or V82) = 4.75 to 5.25 V; AGND, DGND, OGND andV

CCA=VDDD=VCCD=VCCO

DDD=V40

referenced to V

(V41) = 4.75 to 5.25 V; V

SSD

= 5 V and T

=25°C; unless otherwise specified.

amb

SSD

analog supply voltage 4.75 5.0 5.25 V

digital supply voltage 4.75 5.0 5.25 V

logic supply voltage 4.75 5.0 5.25 V

output stages supply

voltage

analog supply current − 120 − mA

CCD=V95

CCO=V59

(or V69,V79or V85) referenced to

connected together; T

referenced to DGND

= 0 to 70°C; typical

amb

4.75 5.0 5.25 V

© Philips Electronics N.V. 2000. All rights reserved.

Page 25

Philips Semiconductors

TDA8752B

Triple high-speed Analog-to-Digital Converter 110 Msps

Table 17: Characteristics

V

CCA=V11

(V

86

OGND (V

(or V19,V27or V99) referenced to AGND (V13,V21,V29or V96) = 4.75 to 5.25 V; V

) = 4.75 to 5.25 V; V

48,V60,V70

values measured at V

…continued

DDD=V40

referenced to V

(V41) = 4.75 to 5.25 V; V

SSD

or V82) = 4.75 to 5.25 V; AGND, DGND, OGND andV

CCA=VDDD=VCCD=VCCO

= 5 V and T

=25°C; unless otherwise specified.

amb

CCO=V59

connected together; T

SSD

(or V69,V79or V85) referenced to

CCD=V95

referenced to DGND

= 0 to 70°C; typical

amb

Symbol Parameter Conditions Min Typ Max Unit

I

DDD

logic supply current for

2

C-bus and 3-wire serial

I

− 1.0 − mA

bus

I

CCD

I

CCO

I

CCO(PLL)

I

CCA(PLL)

∆V

CC

P

tot

P

pd

digital supply current − 40 − mA

output stages supply current ramp input; f

= 110 MHz − 26 − mA

clk

output PLL supply current − 5 − mA

analog PLL supply current − 28 − mA

supply voltage differences

− V

V

V

V

V

V

V

CCA

CCO

CCO

CCA

CCD

CCA

− V

− V

− V

− V

− V

CCD

CCD

DDD

DDD

DDD

CCO

;

;

total power dissipation ramp input; f

power dissipation in

= 110 MHz − 1.1 − W

clk

−0.25 − +0.25 V

−0.25 − +0.25 V

−0.25 − +0.25 V

−0.25 − +0.25 V

− 87 − mW

Power-down mode

R, G and B amplifiers

B bandwidth −3 dB; T

t

set

settling time of the block

ADC plus AGC

full-scale (black-to-white)

transition; input signal settling

=25°C 250 −−MHz

amb

− 4.5 6 ns

time <1 ns (1 to 99%);

=25°C

T

amb

G

NCOARSE

coarse gain range V

= 2.5 V; minimum coarse

ref

−−1.67 − dB

gain register; code = 32

(see Figure 6)

maximum coarse gain

− 8 − dB

register; code = 99

(see Figure 6)

G

FINE

fine gain correction range fine register input code = 0

− 0 − dB

(see Figure 7)

fine register input code = 31

−−0.5 − dB

(see Figure 7)

∆G

/∆T amplifier gain stability as a

amp

function of temperature

I

t

GC

stab

gain current −±20 −µA

amplifier gain adjustment

speed

V

i(p-p)

input voltage range

(peak-to-peak value)

t

r(Vi)

t

f(Vi)

9397 750 07338

Product specification Rev. 03 — 21 July 2000 25 of 38

input voltage rise time fi= 110 MHz; square wave −− 2.5 ns

input voltage fall time fi= 110 MHz; square wave −− 2.5 ns

V

= 2.5 V with 100 ppm/°C

ref

maximum variation

HSYNC active; capacitors on

pins 8, 16 and 24 = 22 nF

corresponding to full-scale

output

−− 200 ppm/°C

− 25 − mdB/µs

0.4 − 1.2 V

© Philips Electronics N.V. 2000. All rights reserved.

Page 26

Philips Semiconductors

TDA8752B

Triple high-speed Analog-to-Digital Converter 110 Msps

Table 17: Characteristics

V

CCA=V11

(V

86

OGND (V

(or V19,V27or V99) referenced to AGND (V13,V21,V29or V96) = 4.75 to 5.25 V; V

) = 4.75 to 5.25 V; V

48,V60,V70

values measured at V

…continued

DDD=V40

referenced to V

(V41) = 4.75 to 5.25 V; V

SSD

or V82) = 4.75 to 5.25 V; AGND, DGND, OGND andV

CCA=VDDD=VCCD=VCCO

= 5 V and T

=25°C; unless otherwise specified.

amb

CCO=V59

connected together; T

SSD

(or V69,V79or V85) referenced to

CCD=V95

referenced to DGND

= 0 to 70°C; typical

amb

Symbol Parameter Conditions Min Typ Max Unit

G

E(rms)

channel-to-channel gain

matching (RMS value)

maximum coarse gain;

=25°C

T

amb

minimum coarse gain;

=25°C

T

amb

− 1 − %

− 2 − %

Clamps

P

CLP

precision black level noise on RGB

−1 − +1 LSB

channels = 10 mV (max.)

amb

=25°C

−− 300 ns

t

COR1

clamp correction time to

within ±10 mV

(RMS value); T

±100 mV black level input

variation; clamp

capacitor = 4.7 nF

t

COR2

clamp correction time to

less than 1 LSB

±100 mV black level input

variation; clamp

−− 10 lines

capacitor = 4.7 nF

t

W(CLP)

CLP

E

clamp pulse width 500 − 2000 ns

channel-to-channel clamp

−1 − +1 LSB

matching

A

off

code clamp reference clamp register input code = 0 −−63.5 − LSB

clamp register input

− +64 − LSB

code = 255

clamp register input

− +120 − LSB

code = 367

clamp register input

− +136 − LSB

code = 398

Phase-locked loop

j

PLL(rms)

maximum PLL phase jitter

f

= 110 MHz; see Table 18 − 112 − ps

clk

(RMS value)

DR divider ratio 100 − 4095

f

ref

reference clock frequency

15 − 280 kHz

range

f

PLL

output clock frequency

12 − 110 MHz

range

t

COAST(max)

t

recap

t

cap

Φ

step

maximum coast mode time −− 40 lines

PLL recapture time when coast mode is aborted − 3 − lines

PLL capture time in start-up conditions −− 5ms

phase shift step T

=25°C − 11.25 − deg

amb

ADCs

f

s

maximum sampling

110 −−MHz

frequency

INL DC integral non-linearity from IC analog input to digital

−±0.5 ±1.5 LSB

output; ramp input;

f

= 110 MHz

clk

9397 750 07338

Product specification Rev. 03 — 21 July 2000 26 of 38

© Philips Electronics N.V. 2000. All rights reserved.

Page 27

Philips Semiconductors

TDA8752B

Triple high-speed Analog-to-Digital Converter 110 Msps

Table 17: Characteristics

V

CCA=V11

(V

86

OGND (V

(or V19,V27or V99) referenced to AGND (V13,V21,V29or V96) = 4.75 to 5.25 V; V

) = 4.75 to 5.25 V; V

48,V60,V70

values measured at V

…continued

DDD=V40

referenced to V

(V41) = 4.75 to 5.25 V; V

SSD

or V82) = 4.75 to 5.25 V; AGND, DGND, OGND andV

CCA=VDDD=VCCD=VCCO

= 5 V and T

=25°C; unless otherwise specified.

amb

CCO=V59

connected together; T

SSD

(or V69,V79or V85) referenced to

CCD=V95

referenced to DGND

= 0 to 70°C; typical

amb

Symbol Parameter Conditions Min Typ Max Unit

DNL DC differential non linearity from IC analog input to digital

−±0.5 ±1.0 LSB

output; ramp input;

= 110 MHz

f

clk

ENOB effective number of bits from IC analog input to digital

[1]

− 7.4 − bits

output; 10 kHz sine wave

input; ramp input;

f

= 110 MHz

clk

Signal-to-noise ratio

S/N signal-to-noise ratio maximum gain; f

minimum gain; f

= 110 MHz − 45 − dB

clk

= 110 MHz − 44 − dB

clk

Spurious free dynamic range

SFDR spurious free dynamic

range

maximum gain; f

minimum gain; f

= 110 MHz − 60 − dB

clk

= 110 MHz − 60 − dB

clk

Clock timing output (CKADCO, CKBO and CKAO)

η

ext

f

clk

ADC clock duty cycle 100 MHz output 45 50 55 %

clock frequency −− 110 MHz

Clock timing input (CKEXT)

f

clk

t

CPH

t

CPL

t

d(CLKO)

∆t-t

d(CLKO)

clock frequency −− 110 MHz

clock pulse width HIGH 3.6 −−ns

clock pulse width LOW 4.5 −−ns

delay from CKEXT to

CKADCO

time difference between

samples

INV set to LOW 9.5 10.1 10.7 ns

1

⁄2t

INV set to HIGH − 10.1 +

when operated in the same

− 0.1 0.3 ns

− ns

clk

supply and temperature

conditions

Data timing (see Figure 11); f

t

t

t

d(s)

d(o)

h(o)

sampling delay time referenced to CKADCO −− − ns

output delay time −−2 −1.5 ns

output hold time 1.5 2.3 − ns

= 110 MHz; CL=10pF;

clk

[2]

3-state output delay time (see Figure 12)

t

t

t

t

dZH

dZL

dHZ

dLZ

output enable HIGH − 12 − ns

output enable LOW − 10 − ns

output disable HIGH − 50 − ns

output disable LOW − 65 − ns

PLL clock output

V

OL

V

OH

I

OL

I

OH

LOW-level output voltage Io=1mA − 0.3 0.4 V

HIGH-level output voltage Io= −1 mA 2.4 3.5 − V

LOW-level output current VOL= 0.4 V − 2 − mA

HIGH-level output current VOH= 2.7 V −−0.4 − mA

9397 750 07338

Product specification Rev. 03 — 21 July 2000 27 of 38

© Philips Electronics N.V. 2000. All rights reserved.

Page 28

Philips Semiconductors

TDA8752B

Triple high-speed Analog-to-Digital Converter 110 Msps

Table 17: Characteristics

V

CCA=V11

(V

86

OGND (V

(or V19,V27or V99) referenced to AGND (V13,V21,V29or V96) = 4.75 to 5.25 V; V

) = 4.75 to 5.25 V; V

48,V60,V70

values measured at V

…continued

DDD=V40

referenced to V

(V41) = 4.75 to 5.25 V; V

SSD

or V82) = 4.75 to 5.25 V; AGND, DGND, OGND andV

CCA=VDDD=VCCD=VCCO

= 5 V and T

=25°C; unless otherwise specified.

amb

CCO=V59

connected together; T

SSD

(or V69,V79or V85) referenced to

CCD=V95

referenced to DGND

= 0 to 70°C; typical

amb

Symbol Parameter Conditions Min Typ Max Unit

ADC data outputs

V

OL

V

OH

I

OL

I

OH

LOW-level output voltage Io=1mA − 0 0.4 V

HIGH-level output voltage Io= −1 mA 2.4 V

CCD

− V

LOW-level output current VOL= 0.4 V − 2 − mA

HIGH-level output current VOH= 2.7 V −−0.4 − mA

TTL digital inputs (CKREF, COAST, CKEXT, INV, HSYNC and CLP)

V

IL

V

IH

I

IL

I

IH

Z

i

C

i

TTL digital inputs (PWDWN,

V

IL

V

IH

I

I(OE)

I

I(PWDWN)

LOW-level input voltage −− 0.8 V

HIGH-level input voltage 2.0 −−V

LOW-level input current VIL= 0.4 V 400 −−µA

HIGH-level input current VIH= 2.7 V −− 100 µA

input impedance − 4 − kΩ

input capacitance − 4.5 − pF

OE)

LOW-level input voltage −− 0.8 V

HIGH-level input voltage 2.0 −−V

input current pin OE with 10 kΩ resistor

input current pin PWDWN with 10 kΩ resistor

[3]

−− 1.0 mA

[3]

−− 1.0 mA

3-wire serial bus

t

rst

reset time of the chip before

− 600 − ns

3-wire serial bus

communication

t

su

t

h

2

C-bus

I

f

SCL

t

BUF

data set-up time − 100 − ns

data hold time − 100 − ns

[4]

clock frequency 0 − 100 kHz

time the bus must be free

4.7 −−µs

before new transmission

can start

t

HD;STA

t

SU;STA

t

CKL

t

CKH

t

SU;DAT

t

HD;DAT

t

r

t

f

t

SU;STOP

C

L(bus)

start condition hold time 4.0 −−µs

start condition set-up time repeated start 4.7 −−µs

LOW-level clock period 4.7 −−µs

HIGH-level clock period 4.0 −−µs

data set-up time 250 −−ns

data hold time 0 −−ns

SDA and SCL rise time f

SDA and SCL fall time f

= 100 kHz −− 1.0 µs

SCL

= 100 kHz −− 300 ns

SCL

stop condition set-up time 4.0 −−µs

bus line capacitive loading −− 400 pF

9397 750 07338

Product specification Rev. 03 — 21 July 2000 28 of 38

© Philips Electronics N.V. 2000. All rights reserved.

Page 29

Philips Semiconductors

TDA8752B

Triple high-speed Analog-to-Digital Converter 110 Msps

[1] Effective bits are obtained via a Fast Fourier Transform (FFT) treatment taking 8000 acquisition points per equivalent fundamental

period. The calculation takes into account all harmonics and noise up to half clock frequency (NYQUIST frequency).

Conversion-to-noise ratio: S/N = EB × 6.02 + 1.76 dB.

[2] Output data acquisition is available after the maximum delay time t

timings are given for a 10 pF capacitive load. A higher load can be used but the timing must then be rechecked.

[3] The input current must be limited in accordance with the limiting values.

[4] The I2C-bus timings are given for a frequency of 100kbit/s (100 kHz). This bus can be used at a frequency of 400 kbit/s (400 kHz).

, which is the time during which the data is available. All the

d(o)

CKADCO

DATA

R0 to R7, ROR

G0 to G7, GOR

B0 to B7, BOR

V

in

Fig 11. Data timing diagram.

handbook, full pagewidth

OE

output

data

output

data

V

CCD

t

dLZ

LOW

10%

n

I

n − 1

t

CPH

t

d(s)

sample N

HIGH

t

dZL

I

n

sample N + 1

t

dHZ

HIGH

50%

t

CPL

t

d(o)

I

n + 1

t

sample N + 2

90%

h(o)

LOW

TDA8752B

I

n + 2

50%

t

dZH

50 % = 1.4 V

2.4 V

1.4 V

0.4 V

FCE475

50%

3.3 kΩ

S1

V

CCD

10 pF

FCE476

fOE= 100 kHz; switch S1 connected to V

CCD

for t

dLZ

and t

OE

; switch S1 connected to GND for t

dZL

dHZ

and t

dZH

.

Fig 12. Timing diagram and test conditions of 3-state output delay time.

9397 750 07338

Product specification Rev. 03 — 21 July 2000 29 of 38

© Philips Electronics N.V. 2000. All rights reserved.

Page 30

Philips Semiconductors

TDA8752B

Triple high-speed Analog-to-Digital Converter 110 Msps

Table 18: Examples of PLL settings and performance

V

CCA=VDDD=VCCD=VCCO

Video standards f

CGA: 640 × 200 15.75 14.3 912 15 39 0.15 100 8 593 3.56

VGA: 640 × 480 31.5 25.18 800 20 39 0.15 200 4 255 1.53

VGA: 640 × 482 48.07 38.4 800 20 39 0.15 400 4 173 1.04

VESA: 800 × 600

(SVGA 72 Hz)

VESA: 1024 × 768

(XGA 75 Hz)

SUN: 1152 × 900 66.67 100 1500 50 39 0.15 400 4 115 0.69

VESA: 1280 × 1024

(SXGA 60 Hz)

[1] PLL long-term time jitter is measured at the end of the video line, where it is at its maximum.

=5V; T

ref

(kHz)

amb

f

(MHz)

=25°C.

clk

N K

O

(MHz/V)

C

Z

(nF)

C

P

(nF)

I

P

(µA)Z(kΩ)

Long-term time jitter

RMS-value

(ps)

peak-to-peak

value (ns)

48.08 50 1040 35 39 0.15 200 4 200 1.2

60.02 78.75 1312 50 39 0.15 700 2 122 0.73

63.98 108 1688 50 39 0.15 400 4 112 0.67

[1]

9397 750 07338

Product specification Rev. 03 — 21 July 2000 30 of 38

© Philips Electronics N.V. 2000. All rights reserved.

Page 31

Philips Semiconductors

13. Application information

TDA8752B

Triple high-speed Analog-to-Digital Converter 110 Msps

2.5 V

RIN

GIN

BIN

10 nF

4.7 nF

100 nF

75 Ω or 50 Ω

10 nF

4.7 nF

100 nF

75 Ω or 50 Ω

10 nF

4.7 nF

100 nF

75 Ω or 50 Ω

10 nF

1.5 nF

22 nF

10 nF

22 nF

10 nF

22 nF

10 nF

DEC2

DEC1

RAGC

RBOT

RGAINC

RCLP

RDEC

V

CCA(R)

AGND

GAGC

GBOT

GGAINC

GCLP

GDEC

V

CCA(G)

AGND

BAGC

BBOT

BGAINC

BCLP

BDEC

V

CCA(B)

AGND

PWDWN

150 pF

39 nF

CP

CZ

V

CCA(PLL)

n.c.

100 99 98 97 96 95 94 93 92 91 90 89 88 87 86 85 84 83 82 81

n.c.

1

2

V

ref

3

4

n.c.

5

6

7

8

9

10

11

RIN

12

R

13

14

15

16

17

18

19

GIN

20

G

21

22

23

24

25

26

27

BIN

28

B

29

n.c.

30

31 40 4132 4233 4334 4435 4536 4637 4738 4839 49 50

AGND

V

CCD

PLL

CKREF

COAST

CKEXT

TDA8752B

HSYNC

INV

CLP

R1 R2

OE

V

CCO(PLL)

DGND

CKADCO

CKBO

OGND

CKAO

80

79

78

77

76

75

74

73

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

PLL

CKREFO

V

CCO(R)

R7

R6

R5

R4

R3

R2

R1

R0

OGND

V

CCO(G)

G7

G6

G5

G4

G3

G2

G1

G0

OGND

V

CCO(B)

B7

B6

B5

B4

B3

B2

B1

n.c.

R

G

n.c.

2

I

C/3W

ADD1

ADD2

TCK

TDO

DIS

SEN

SDA

V

DDD

V

DDD

V

SSD

4.7

kΩ

SCL

V

DDD

4.7

kΩ

BORRORn.c.

B0

n.c.GORn.c.

OGND

B

FCE477

All supplypins haveto be decoupled,with two capacitors: one forthe high frequencies(approximately 1 nF) and one forthe low

frequencies (approximately 100 nF orhigher). If a capacitor of39 nF betweenpins CZ and CPis notavailable, use a higherone

as close as possible to this value. Resistors R1 and R2 must be connected: the recommended value is 10 kΩ.

Fig 13. Application diagram.

9397 750 07338

Product specification Rev. 03 — 21 July 2000 31 of 38

© Philips Electronics N.V. 2000. All rights reserved.

Page 32

Philips Semiconductors

14. Package outline

TDA8752B

Triple high-speed Analog-to-Digital Converter 110 Msps

QFP100: plastic quad flat package; 100 leads (lead length 1.95 mm); body 14 x 20 x 2.8 mm

c

y

X

E

e

w M

p

A

A

H

E

E

2

A

A

1

80 51

81

pin 1 index

100

1

50

Z

b

31

30

detail X

L

p

L

SOT317-2

(A )

3

θ

w M

b

0.25

0.40

0.25

p

D

H

D

(1) (1)(1)

D

0.25

20.1

0.14

19.9

e

DIMENSIONS (mm are the original dimensions)

UNIT A1A2A3bpcE

Note

1. Plastic or metal protrusions of 0.25 mm maximum per side are not included.

A

max.

0.25

mm

3.20

OUTLINE

VERSION

SOT317-2 MO-112

0.05

2.90

2.65

IEC JEDEC EIAJ

Z

D

B

0 5 10 mm

scale

(1)

eHELL

H

D

14.1

0.65

13.9

REFERENCES

24.2

23.6

18.2

17.6

v M

v M

A

B

Zywv θ

Z

E

D

o

1.0

0.8

0.4

7

o

0.6

0

ISSUE DATE

97-08-01

99-12-27

1.0

0.6

p

0.15 0.10.21.95

EUROPEAN

PROJECTION

Fig 14. SOT317-2 package outline.

9397 750 07338

Product specification Rev. 03 — 21 July 2000 32 of 38

© Philips Electronics N.V. 2000. All rights reserved.

Page 33

Philips Semiconductors

15. Handling information

Inputs and outputs are protected against electrostatic discharge in normal handling.

However, to be completely safe, it is desirable to take normal precautions appropriate

to handling integrated circuits.

16. Soldering

16.1 Introduction to soldering surface mount packages

This text gives a very brief insight to a complex technology. A more in-depth account

of soldering ICs can be found in our

Packages

There is no soldering method that is ideal for all surface mount IC packages. Wave

soldering can still be used for certain surface mount ICs, but it is not suitable for fine

pitch SMDs. In these situations reflow soldering is recommended.

TDA8752B

Triple high-speed Analog-to-Digital Converter 110 Msps

Data Handbook IC26; Integrated Circuit

(document order number 9398 652 90011).

16.2 Reflow soldering

Reflow soldering requires solder paste (a suspension of fine solder particles, flux and

binding agent) to be applied to the printed-circuit board by screen printing, stencilling

or pressure-syringe dispensing before package placement.

Several methods exist for reflowing; for example, convection or convection/infrared

heating in a conveyor type oven. Throughput times (preheating, soldering and

cooling) vary between 100 and 200 seconds depending on heating method.

Typical reflow peak temperatures range from 215 to 250 °C. The top-surface

temperature of the packages should preferable be kept below 220 °C for thick/large

packages, and below 235 °C small/thin packages.

16.3 Wave soldering

Conventional single wave soldering is not recommended for surface mount devices

(SMDs) or printed-circuit boards with a high component density, as solder bridging

and non-wetting can present major problems.

To overcome these problems the double-wave soldering method was specifically

developed.

If wave soldering is used the following conditions must be observed for optimal

results:

Use a double-wave soldering method comprising a turbulent wave with high

•

upward pressure followed by a smooth laminar wave.

For packages with leads on two sides and a pitch (e):

•

– larger than or equal to 1.27 mm, the footprint longitudinal axis is preferred to be

parallel to the transport direction of the printed-circuit board;

– smaller than 1.27 mm, the footprint longitudinal axis must be parallel to the

transport direction of the printed-circuit board.

9397 750 07338

Product specification Rev. 03 — 21 July 2000 33 of 38

© Philips Electronics N.V. 2000. All rights reserved.

Page 34

Philips Semiconductors

•

During placement and before soldering, the package must be fixed with a droplet of

adhesive. The adhesive can be applied by screen printing, pin transfer or syringe

dispensing. The package can be soldered after the adhesive is cured.

Typical dwell time is 4 seconds at 250 °C. A mildly-activated flux will eliminate the

need for removal of corrosive residues in most applications.

16.4 Manual soldering

Fix the component by first soldering two diagonally-opposite end leads. Use a low

voltage (24 V or less) soldering iron applied to the flat part of the lead. Contact time

must be limited to 10 seconds at up to 300 °C.

When using a dedicated tool, all other leads can be soldered in one operation within

2 to 5 seconds between 270 and 320 °C.

TDA8752B

Triple high-speed Analog-to-Digital Converter 110 Msps

The footprint must incorporate solder thieves at the downstream end.

For packages with leads on four sides, the footprint must be placed at a 45° angle

to the transport direction of the printed-circuit board. The footprint must

incorporate solder thieves downstream and at the side corners.

16.5 Package related soldering information

Table 19: Suitability of surface mount IC packages for wave and reflow soldering

methods

Package Soldering method

Wave Reflow

BGA, LFBGA, SQFP, TFBGA not suitable suitable

HBCC, HLQFP, HSQFP, HSOP, HTQFP,

HTSSOP, SMS

[3]

PLCC

LQFP, QFP, TQFP not recommended

SSOP, TSSOP, VSO not recommended

[1] All surface mount (SMD)packages are moisture sensitive. Depending upon the moisture content, the

[2] These packages arenot suitable for wavesoldering as a solder joint between the printed-circuit board

[3] If wave soldering is considered, then the package must be placed at a 45° angle to the solder wave

[4] Wave soldering is only suitable for LQFP, QFP and TQFP packages with a pitch (e) equal to or larger

[5] Wave soldering is onlysuitable forSSOP andTSSOP packages with a pitch(e) equal to or largerthan

, SO, SOJ suitable suitable

maximum temperature(with respect totime) and bodysize of thepackage, there is a risk that internal

or external package cracks may occur due to vaporization of the moisture in them (the so called

popcorn effect). For details, refer to the Drypack information in the

Circuit Packages; Section: Packing Methods

and heatsink (atbottom version) can not be achieved, and as solder may stickto the heatsink (on top

version).

direction. The package footprint must incorporate solder thieves downstream and at the side corners.

than 0.8 mm; it is definitelynot suitable for packages with a pitch (e)equal to orsmaller than 0.65 mm.

0.65 mm; it is definitely not suitable for packages with a pitch (e) equal to or smaller than 0.5 mm.

not suitable

.

[2]

[3][4]

[5]

Data Handbook IC26; Integrated

suitable

suitable

suitable

[1]

9397 750 07338

Product specification Rev. 03 — 21 July 2000 34 of 38

© Philips Electronics N.V. 2000. All rights reserved.

Page 35

Philips Semiconductors

17. Revision history

Table 20: Revision history

Rev Date CPCN Description

3 20000721 Product specification

2 20000110 Preliminary specification

1 19991111 Objective specification

TDA8752B

Triple high-speed Analog-to-Digital Converter 110 Msps

9397 750 07338

Product specification Rev. 03 — 21 July 2000 35 of 38

© Philips Electronics N.V. 2000. All rights reserved.

Page 36

Philips Semiconductors

18. Data sheet status

TDA8752B

Triple high-speed Analog-to-Digital Converter 110 Msps

Datasheet status Product status Definition

Objective specification Development This data sheet contains the design target or goal specifications for product development. Specification may

change in any manner without notice.

Preliminary specification Qualification This data sheet contains preliminary data, and supplementary data will be published at a later date. Philips

Semiconductors reserves the right to make changes at any time without notice in order to improve design and

supply the best possible product.

Product specification Production This data sheet contains final specifications. Philips Semiconductors reserves the right to make changes at any

time without notice in order to improve design and supply the best possible product.

[1] Please consult the most recently issued data sheet before initiating or completing a design.

19. Definitions

Short-form specification — The data in a short-form specification is

extracted from a full data sheet with the same type number and title. For

detailed information see the relevant data sheet or data handbook.

Limiting values definition — Limiting values given are in accordance with

the Absolute Maximum Rating System (IEC 60134). Stress above one or

more of the limiting values may cause permanent damage to the device.

These are stress ratings only and operation of the device at these or at any

other conditions above those given in the Characteristics sections of the

specification is not implied. Exposure to limiting values for extended periods

may affect device reliability.

Application information — Applications that are described herein for any

of these products are for illustrative purposes only. Philips Semiconductors

make no representation or warranty that such applications will be suitable for

the specified use without further testing or modification.

20. Disclaimers

Life support — These products are not designed for use in life support

appliances, devices, or systems where malfunction of these products can

reasonably be expected to result in personal injury. Philips Semiconductors

[1]

customers using or selling these products for use in such applications do so

at their own risk and agree to fully indemnify Philips Semiconductors for any

damages resulting from such application.

Right to make changes — Philips Semiconductors reserves the right to

make changes, without notice, in the products, including circuits, standard

cells, and/or software, described or contained herein in order to improve

design and/or performance. Philips Semiconductors assumes no