NSC SCAN18541TMDA Datasheet

SCAN18541T

Non-Inverting Line Driver with TRI-STATE

®

Outputs

General Description

The SCAN18541T is a high speed, low-power line driver featuring separate data inputs organized into dual 9-bit bytes

with byte-oriented paired output enable control signals. This

device is compliant with IEEE 1149.1 Standard Test Access

Port and Boundary Scan Architecture with the incorporation

of the defined boundary-scan test logic and test access port

consisting of Test Data Input (TDI), Test Data Out (TDO),

Test Mode Select (TMS), and Test Clock (TCK).

Features

n IEEE 1149.1 (JTAG) Compliant

n Dual output enable signals per byte

n TRI-STATE outputs for bus-oriented applications

n 9-bit data busses for parity applications

n Reduced-swing outputs source 24 mA/sink 48 mA (Mil)

n Guaranteed to drive 50Ω transmission line to TTL input

levels of 0.8V and 2.0V

n TTL compatible inputs

n 25 mil pitch Cerpack packaging

n Includes CLAMP and HIGHZ instructions

n Standard Microcircuit Drawing (SMD) 5962-9311601

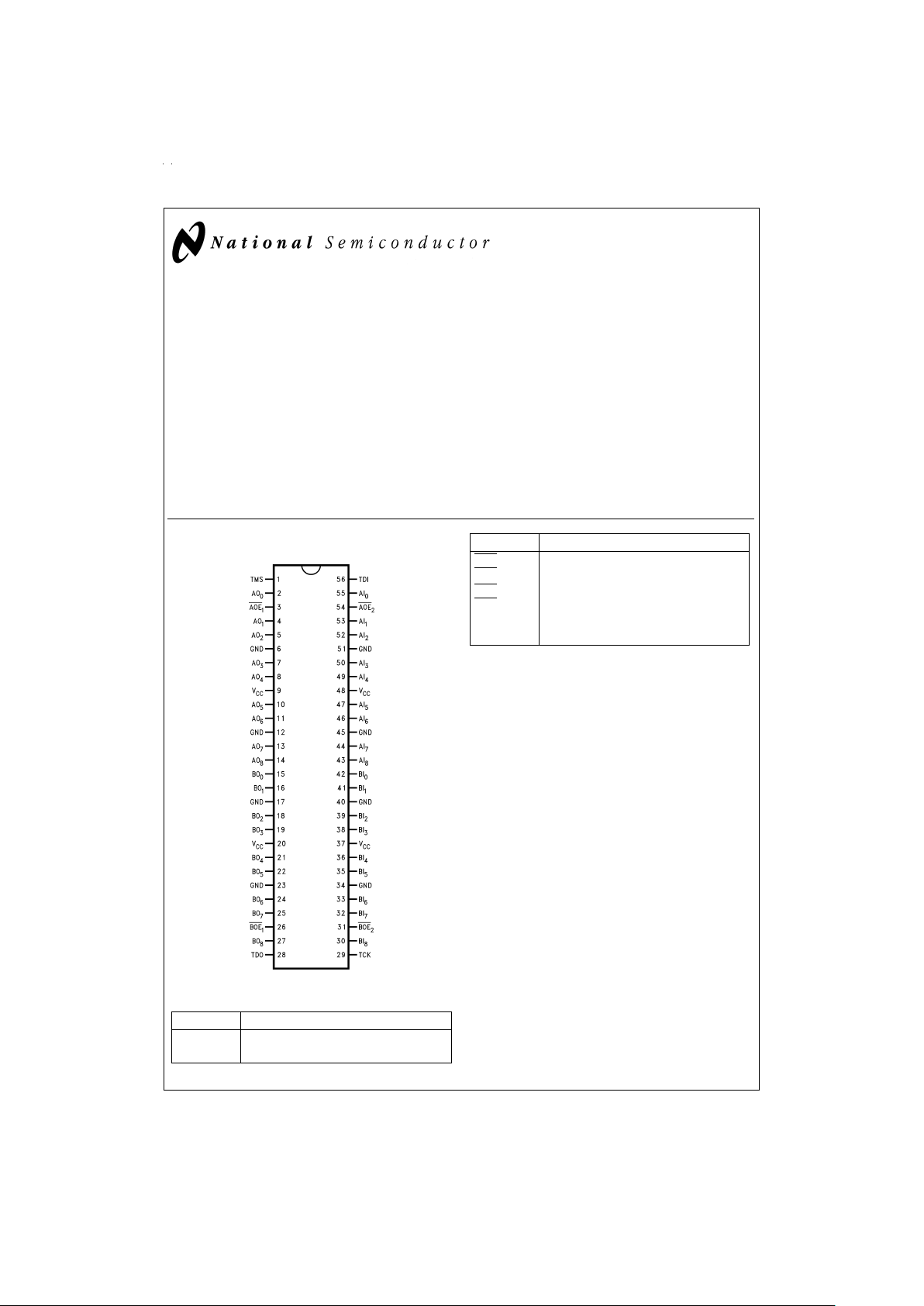

Connection Diagram

Pin Names

Pin Names Description

AI

(0–8)

Input Pins, A Side

BI

(0–8)

Input Pins, B Side

Pin Names Description

AOE

1

,

AOE

2

TRI-STATE Output Enable Input Pins,

A Side

BOE

1

,

BOE

2

TRI-STATE Output Enable Input Pins,

B Side

AO

(0–8)

Output Pins, A Side

AO

(0–8)

Output Pins, B Side

TRI-STATE®is a registered trademarkof National Semiconductor Corporation.

DS100324-1

September 1998

SCAN18541T Non-Inverting Line Driver with TRI-STATE Outputs

© 1998 National Semiconductor Corporation DS100324 www.national.com

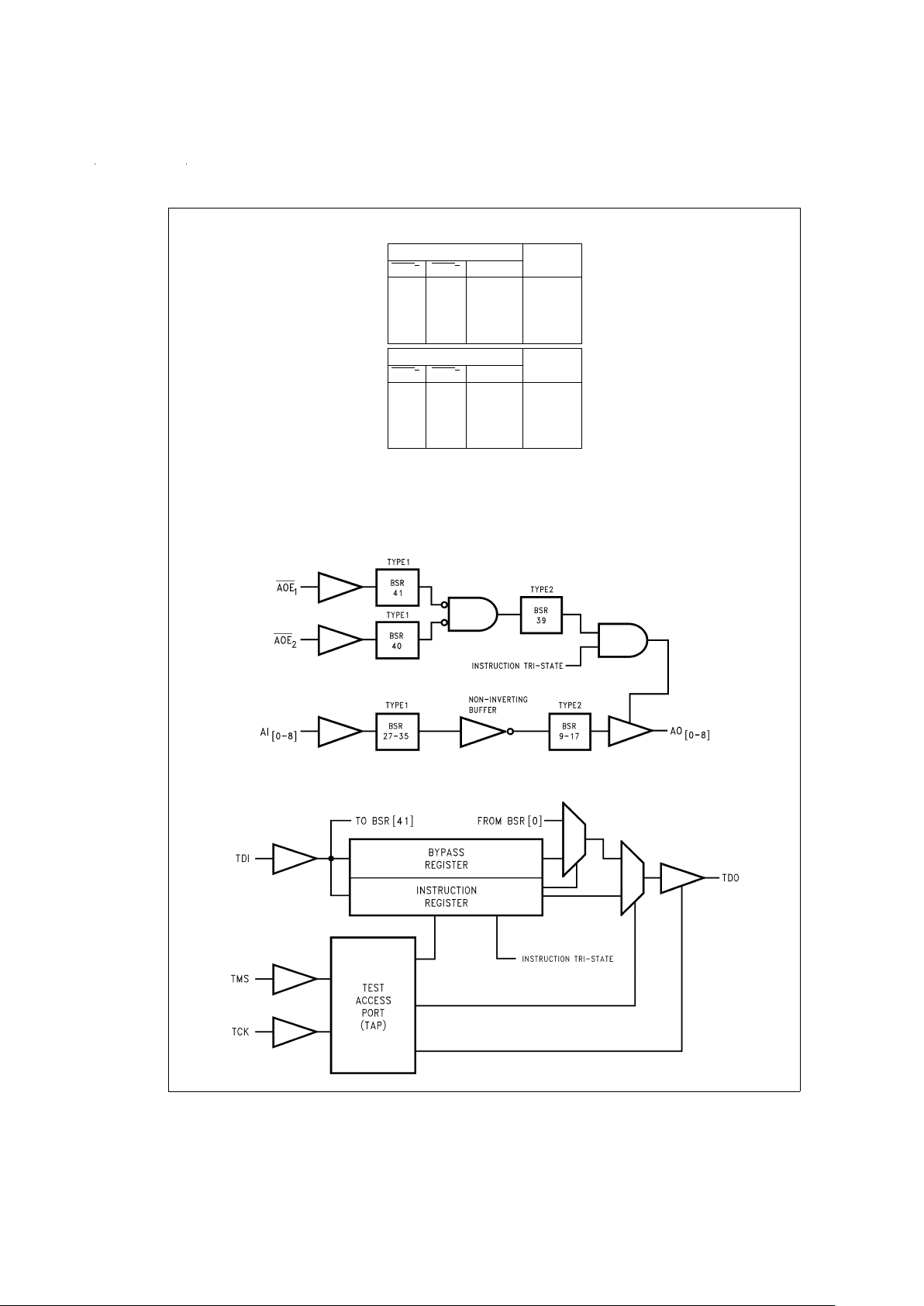

Truth Tables

Inputs AO (0–8)

AOE

1

AOE2AI (0–8)

LL H H

HX X Z

XH X Z

LL L L

Inputs BO (0–8)

BOE

1

BOE2BI (0–8)

LL H H

HX X Z

XH X Z

LL L L

H

=

HIGH Voltage Level

L=LOW Voltage Level

X=Immaterial

Z=High Impedance

Block Diagrams

Byte A

DS100324-2

Tap Controller

DS100324-3

www.national.com 2

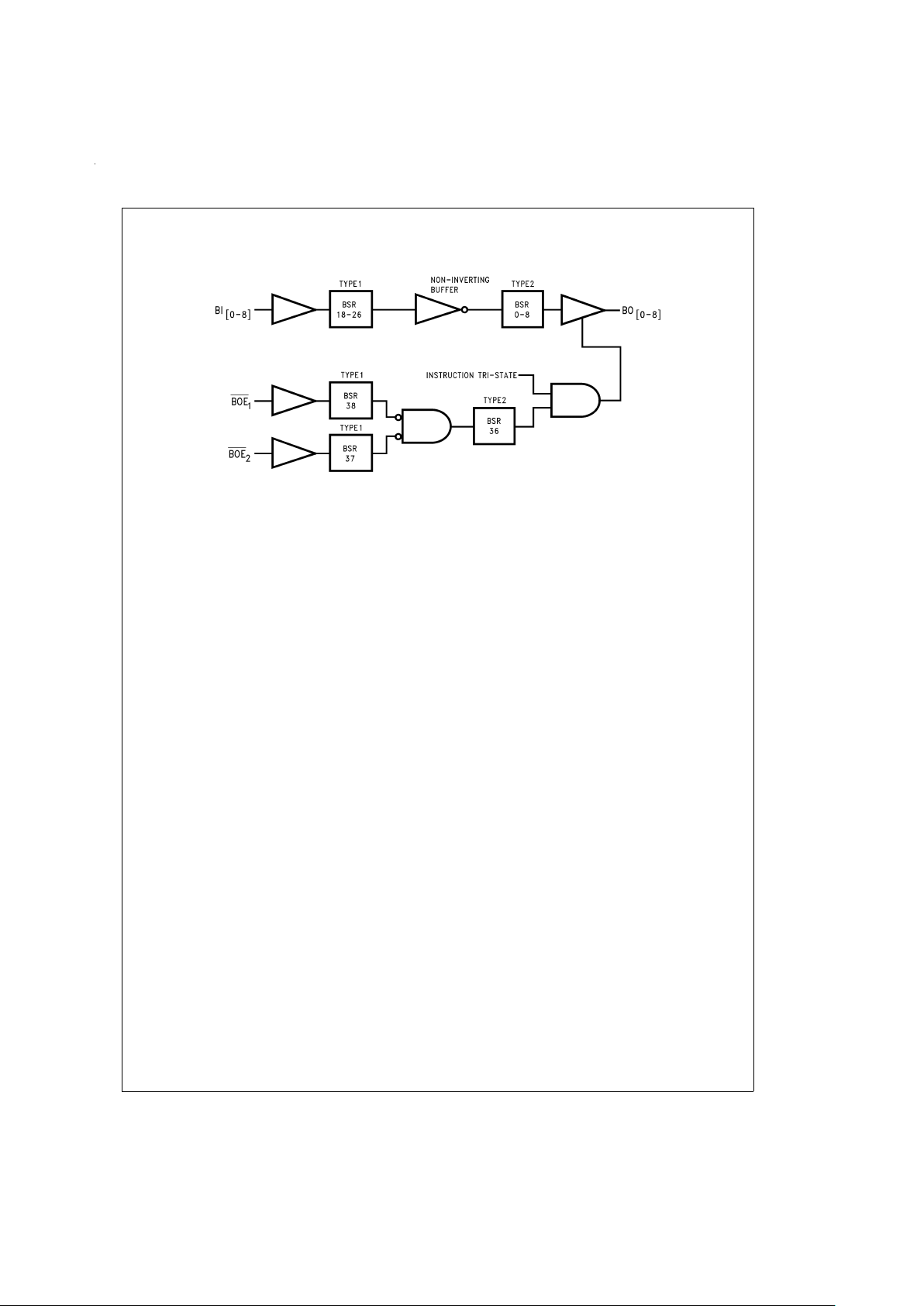

Block Diagrams (Continued)

Byte B

DS100324-4

Note: BSR stands for Boundary Scan Register.

www.national.com3

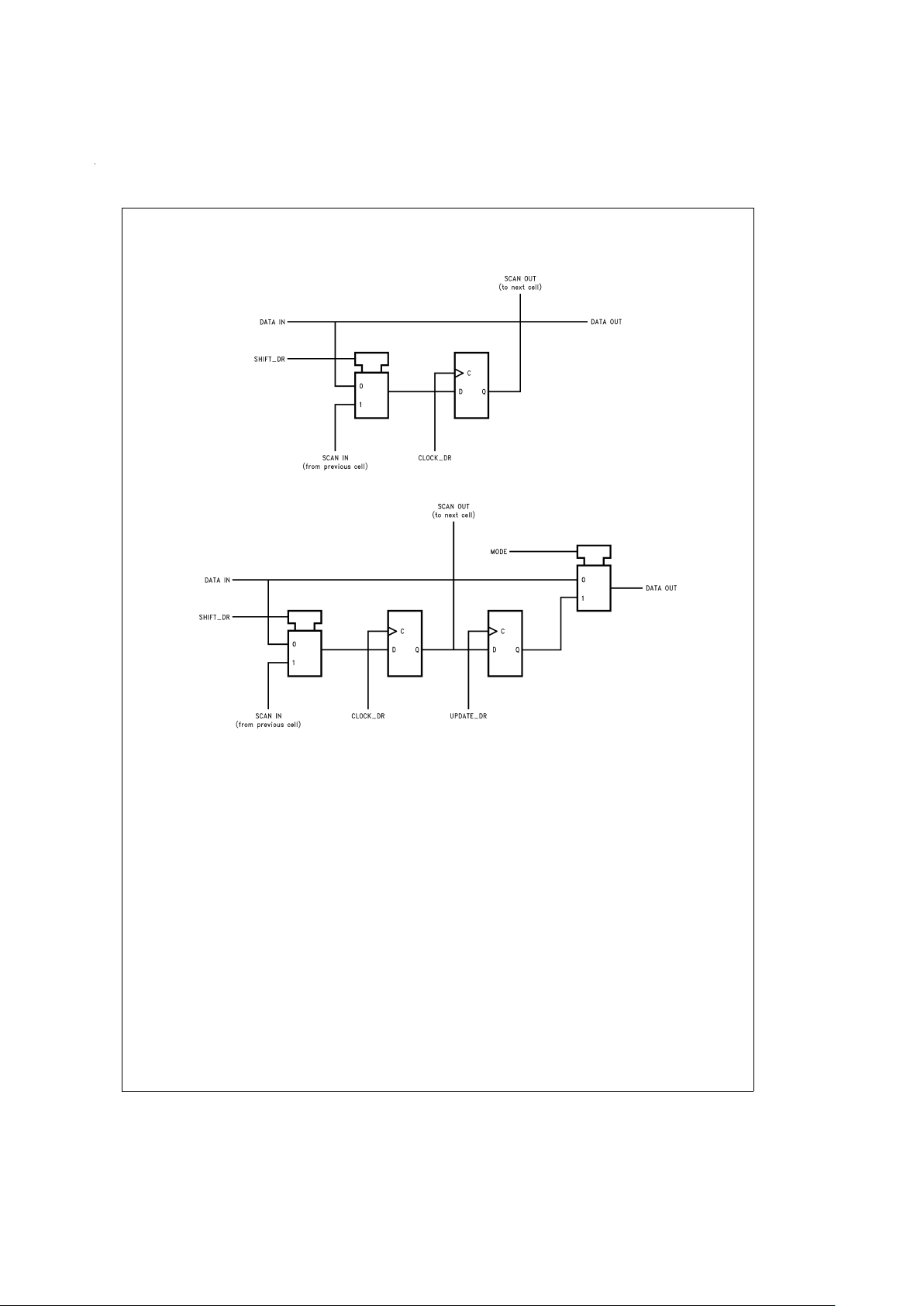

Description of Boundary-Scan Circuitry

The scan cells used in the BOUNDARY-SCAN register are

one of the following two types depending upon their location.

Scan cell TYPE1 is intended to solely observe system data,

while TYPE2 has the additional ability to control system

data. (See IEEE Standard 1149.1

Figure10–11

for a further

description of scan cell TYPE1 and

Figure 10–12

for a fur-

ther description of scan cell TYPE2.)

Scan cell TYPE1 is located on each system input pin while

scan cell TYPE2 is located at each system output pin as well

as at each of the two internal active-high output enable signals. AOE controls the activity of the A-outputs while BOE

controls the activity of the B-outputs. Each will activate their

respective outputs by loading a logic high.

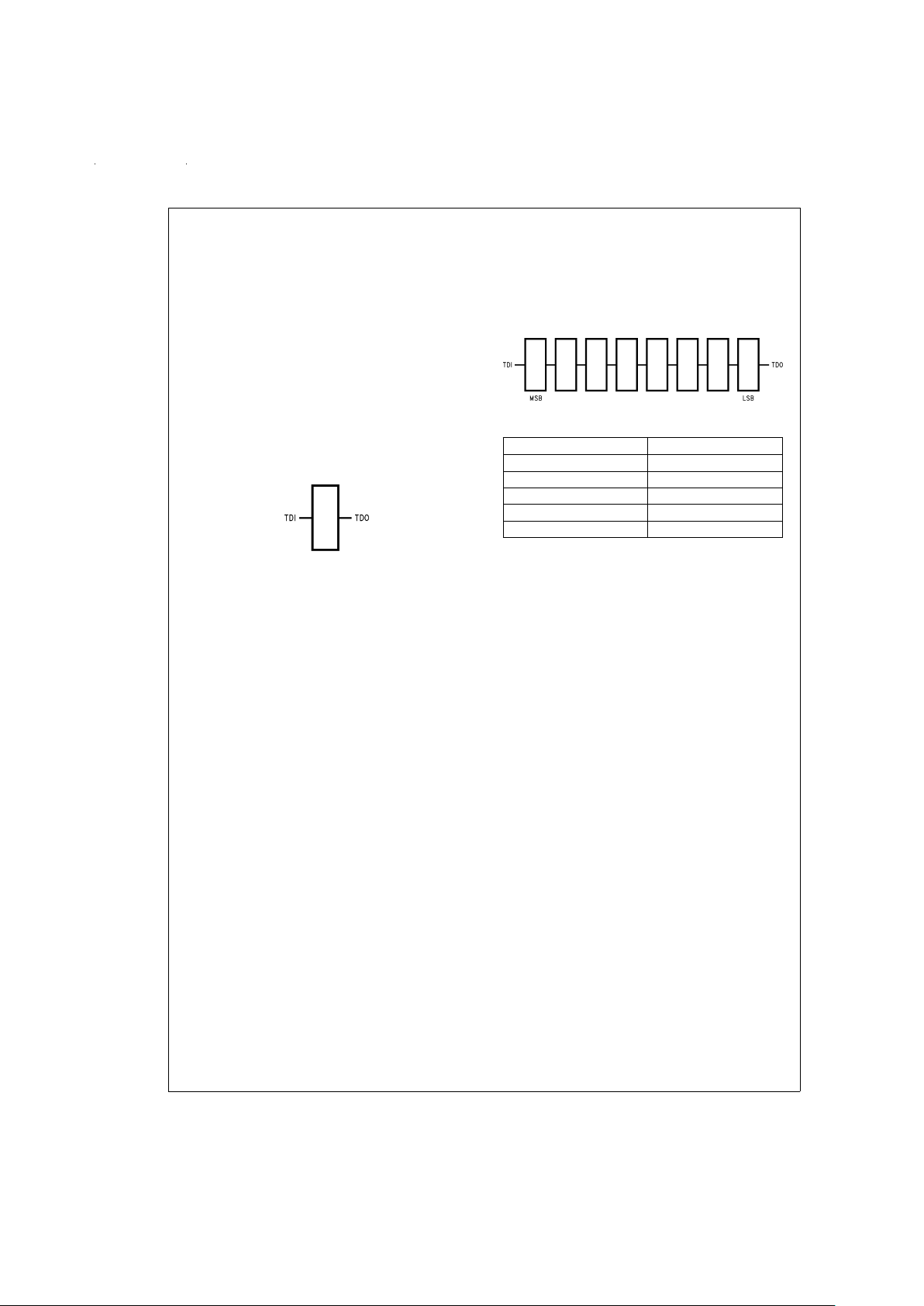

The BYPASS register is a single bit shift register stage identical to scan cell TYPE1. It captures a fixed logic low.

The INSTRUCTION register is an 8-bit register which captures the default value of 10000001. The two least significant

bits of this captured value (01) are required by IEEE Std

1149.1. The upper six bits are unique to the SCAN18541T

device. SCAN CMOS Test Access Logic devices do not include the IEEE 1149.1 optional identification register. Therefore, this unique captured value can be used as a “pseudo

ID” code to confirm that the correct device is placed in the

appropriate location in the boundary scan chain.

MSB→LSB

Instruction Code Instruction

00000000 EXTEST

10000001 SAMPLE/PRELOAD

10000010 CLAMP

00000011 HIGH-Z

All Others BYPASS

Bypass Register Scan Chain Definition

Logic 0

DS100324-9

Instruction Register Scan Chain Definition

DS100324-10

www.national.com 4

Description of Boundary-Scan Circuitry (Continued)

Scan Cell TYPE1

DS100324-7

Scan Cell TYPE2

DS100324-8

www.national.com5

Loading...

Loading...