NSC PC87309-IBW-EB, PC87309-IBW-VLJ, PC87309-ICK-EB, PC87309-ICK-VLJ Datasheet

PRELIMINARY

April 1998

PC87309 SuperI/O Plug and Play Compatible Chip in Compact 100-Pin VLJ Packaging

Highlights

General Description

The PC87309 is a single-chip solution to the most commonly used ISA, EISA and MicroChannel® peripherals in a compact, 100-pin VLJ packaging. This fully Plug and Play (PnP) and PC97 compatible chip conforms to the Plug and Play ISA Specification Version 1.0a, May 5, 1994, and meets specifications defined in the PC97 Hardware Design Guide.

The PC87309 incorporates: a Floppy Disk Controller (FDC), a Mouse and Keyboard Controller (KBC), two enhanced UARTs, one of which is with Infrared (IR) support, a full IEEE 1284 parallel port and support for Power Management (PM). The chip also provides a separate configuration register set for each module.

The Infrared (IR) interface complies with the HP-SIR and SHARP-IR standards, and supports all four basic protocols for Consumer Remote Control circuitry (RC-5, RC-6, NEC, RCA and RECS 80).

For flexible UART and IR support, the PC87309 offers two operation modes:

●Mode 1: Full-IR Mode

UART1 works as UART; UART2 works as fully IRcompliant device

●Mode 2: Two-UART Mode

Either both UARTs work as UARTs, or UART1 works as UART and UART2 works as partially IR-compliant device, providing only IRRX and IRTX support

Outstanding Features

●Full SuperI/O functionality in compact, cost-effective 100-pin VLJ packaging

●PC97 compliant

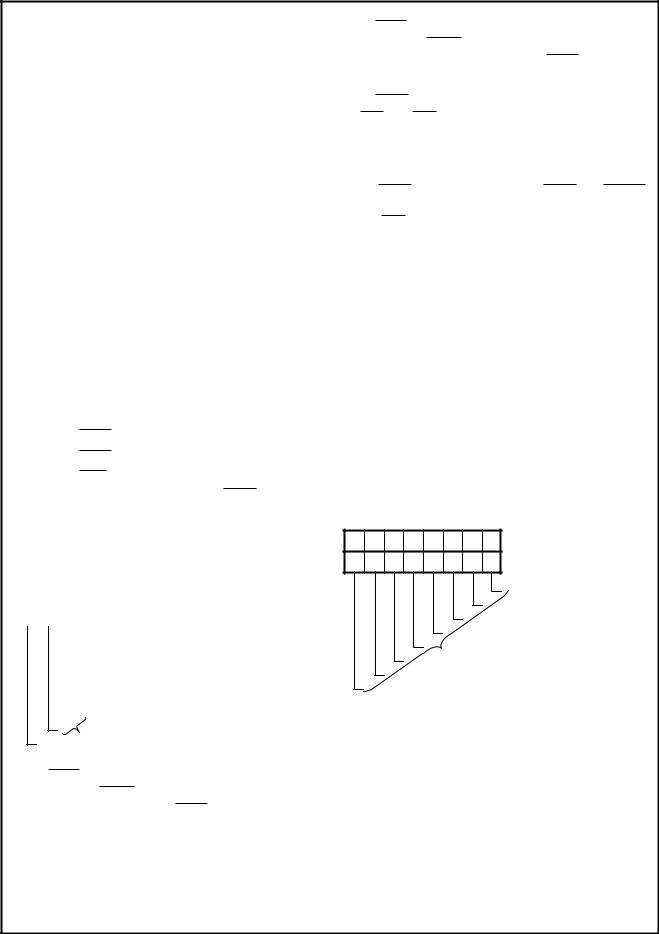

PC87309 Block Diagram

|

DMA |

Floppy Drive |

|

Data Handshake |

|||||

IRQ Channels |

Interface |

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Plug and Play |

|

Floppy Disk |

|

High Current Driver |

|||||

|

|

|

|

|

|||||

|

|

|

IEEE 1284 |

||||||

|

Controller (FDC) |

|

|

||||||

|

(PnP) |

|

|

|

|||||

|

|

|

|

Parallel Port |

|||||

|

|

(Logical Device 0) |

|

|

|||||

|

|

|

|

|

(Logical Device 1) |

||||

|

|

|

|

|

|

|

|||

μP Address

Data and

Control

|

Serial Port |

|

|

|

|

Power Management |

|

Mouse and Keyboard |

|||||

|

|

Serial Port |

|

|

|||||||||

with IR (UART2) |

|

(UART1) |

|

(PM) Logic |

|

Controller (KBC) |

|||||||

(Logical Devices 2) |

|

(Logical Devices 3) |

|

(Logical Device 4) |

|

(Logical Devices 5 & 6) |

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Serial Infrared |

|

|

|

|

|

|

|

Data and |

Ports |

||||

|

Serial |

Control |

|

||||||||||

|

|

|

|

Interface |

|

|

|

Control |

|

|

|||

TRI-STATE® is a registered trademark of National Semiconductor Corporation.

IBM®, MicroChannel®, PC-AT® and PS/2® are registered trademarks of International Business Machines Corporation. Microsoft® and Windows® are registered trademarks of Microsoft Corporation.

Highlights

© 1998 National Semiconductor Corporation |

www.national.com |

Highlights

Features

●100% compatibility with PnP requirements specified in the “Plug and Play ISA Specification”, PC97, ISA, EISA, and MicroChannel architectures

●A special PnP module that includes:

—Flexible IRQs, DMAs and base addresses that meet the PnP requirements specified by Microsoft® in their 1995 hardware design guide for Windows® and PnP ISA Revision 1.0A

—PnP ISA mode (with isolation mechanism – Wait for Key state Motherboard PnP mode

●A Floppy Disk Controller (FDC) that provides:

—A relocatable address that is referenced by an 11-bit programmable register

—Software compatibility with the PC8477, which con-

tains a superset of the floppy disk controller functions in the μDP8473, the NEC μPD765A and the N82077

—7 IRQ channel options

—Three 8-bit DMA channel options

—16-byte FIFO

—Burst and non-burst modes

—A new high-performance, on-chip, digital data separator that does not require any external filter components

—Support for standard 5.25" and 3.5" floppy disk drives

—Perpendicular recording drive support

—Three-mode Floppy Disk Drive (FDD) support

—Full support for the IBM Tape Drive Register (TDR) implementation of AT and PS/2 drive types

●A Keyboard and mouse Controller (KBC) with:

—A relocatable address that is referenced by an 11-bit programmable register, reported as a fixed address in resource data

—7 IRQ options for the keyboard controller

—7 IRQ options for the mouse controller

—An 8-bit microcontroller

—Software compatibility with the 8042AH and PC87911 microcontrollers

—2 KB of custom-designed program ROM

—256 bytes of RAM for data

—Three programmable dedicated open drain I/O lines for keyboard controller applications

—Asynchronous access to two data registers and one status register during normal operation

—Support for both interrupt and polling

—93 instructions

—An 8-bit timer/counter

—Support for binary and BCD arithmetic

—Operation at 8 MHz,12 MHz or 16 MHz (programmable option)

—Customizing by using the PC87323VUL, which includes a RAM-based KBC, as a development platform for keyboard controller code for the PC87309

●Two UARTs that provide:

—Software compatibility with the 16550A and the 16450

—A relocatable address that is referenced by an 11-bit programmable register

—7 IRQ channel options

—Shadow register support for write-only bit monitoring

—UART data rates up to 1.5 Mbaud

●An enhanced UART and Infrared (IR) interface on the UART2 that supports:

—HP-SIR

—ASK-IR option of SHARP-IR

—DASK-IR option of SHARP-IR

—Consumer Remote Control circuitry

—A PnP compatible external transceiver

—Three 8-bit DMA options for the UART with Slow Infrared support (UART2)

●A bidirectional parallel port that includes:

—A relocatable address that is referenced by an 11-bit programmable register

—Software or hardware control

—7 IRQ channel options

—Three 8-bit DMA channel options

—Demand mode DMA support

—An Enhanced Parallel Port (EPP) that is compatible with the new version EPP 1.9, and is IEEE 1284 compliant

—An Enhanced Parallel Port (EPP) that also supports version EPP 1.7 of the Xircom specification.

—Support for an Enhanced Parallel Port (EPP) as mode 4 of the Extended Capabilities Port (ECP)

—An Extended Capabilities Port (ECP) that is IEEE 1284 compliant, including level 2

—Selection of internal pull-up or pull-down resistor for Paper End (PE) pin

—Reduction of PCI bus utilization by supporting a demand DMA mode mechanism and a DMA fairness mechanism

—A protection circuit that prevents damage to the parallel port when a printer connected to it powers up or is operated at high voltages

—Output buffers that can sink and source 14 mA

●Enhanced Power Management (PM), including:

—Reduced current leakage from pins

—Low-power CMOS technology

—Ability to shut off clocks to all modules

●Clock source:

—Source is a 48 MHz clock input signal.

●General features include:

—Access to all configuration registers is through an Index and a Data register, which can be relocated within the ISA I/O address space

—100-pin Plastic Quad Flatpack (PQFP) package

www.national.com |

2 |

|

Highlights |

|

|

Basic Configuration |

|

|

|

|

|

P12 |

|

|

|

P21,20 |

|

|

|

|

Keyboard I/O |

48 MHz |

CLKIN |

KBCLK |

Interface |

Clock |

|

KBDAT |

|

|

|

|

|

|

|

MDAT |

|

|

|

MCLK |

|

|

MR |

SIN1 |

|

|

AEN |

|

|

|

SOUT1 |

|

|

|

A11-0 |

|

|

|

RTS1 |

|

|

|

D7-0 |

EIA |

|

|

DTR1/BOUT1 |

||

|

RD |

||

|

Drivers |

||

|

CTS1 |

||

|

WR |

||

|

|

||

|

IOCHRDY |

DSR1 |

|

|

|

DCD1 |

|

Bus |

IRQ1 |

RI1 |

|

IRQ7-3 |

IRRX2,1 |

|

|

IRQ12 |

|

||

ISA |

DRQ3-1 |

IRTX |

Infrared (IR) |

DACK3-1 |

IRSL2-0 |

Interface |

|

|

TC |

|

|

|

ID3-0 |

|

|

|

PC87309 |

|

|

|

SIN2 |

|

|

|

|

|

|

|

|

SOUT2 |

|

|

PD7-0 |

RTS2 |

EIA |

|

DTR2/BOUT2 |

||

|

SLIN/ASTRB |

Drivers |

|

|

CTS2 |

||

|

STB/WRITE |

|

|

|

DSR2 |

|

|

Parallel |

AFD/DSTRB |

|

|

DCD2 |

|

||

INIT |

|

||

Port |

RI2 |

|

|

|

|

||

Connector |

ACK |

RDATA |

|

|

ERR |

|

|

|

WDATA |

|

|

|

SLCT |

|

|

|

WGATE |

|

|

|

PE |

|

|

|

HDSEL |

|

|

|

BUSY/WAIT |

Floppy |

|

|

DIR |

||

|

|

Disk |

|

|

|

STEP |

|

|

|

TRK0 |

Controller |

|

|

(FDC) |

|

|

|

INDEX |

|

|

|

Connector |

|

|

|

DSKCHG |

|

Configuration |

BADDR1,0 |

|

|

WP |

|

||

Select Logic |

CFG0 |

|

|

MTR1,0 |

|

||

|

|

|

|

|

|

DR1,0 |

|

|

|

DENSEL |

|

|

|

DRATE0 |

|

|

3 |

|

www.national.com |

Table of Contents

Table of Contents

Highlights....................................................................................................................................................... |

1 |

1.0Signal/Pin Connection and Description

1.1 |

CONNECTION DIAGRAM ......................................................................................................... |

12 |

1.2 |

SIGNAL/PIN DESCRIPTIONS ................................................................................................... |

13 |

2.0Configuration

2.1 |

HARDWARE CONFIGURATION ............................................................................................... |

19 |

|

|

2.1.1 |

Wake Up Options ........................................................................................................ |

19 |

|

2.1.2 The Index and Data Register Pair ............................................................................... |

19 |

|

2.2 |

SOFTWARE CONFIGURATION ............................................................................................... |

20 |

|

|

2.2.1 Accessing the Configuration Registers ........................................................................ |

20 |

|

|

2.2.2 |

Address Decoding ....................................................................................................... |

20 |

2.3 |

THE CONFIGURATION REGISTERS ....................................................................................... |

21 |

|

|

2.3.1 Standard Plug and Play (PnP) Register Definitions .................................................... |

21 |

|

|

2.3.2 |

Configuration Register Summary ................................................................................ |

25 |

2.4 |

CARD CONTROL REGISTERS ................................................................................................ |

28 |

|

|

2.4.1 |

SID Register ................................................................................................................ |

28 |

|

2.4.2 SuperI/O Configuration 1 Register (SIOCF1) .............................................................. |

28 |

|

|

2.4.3 SuperI/O Configuration 2 Register (SIOCF2) .............................................................. |

29 |

|

|

2.4.4 |

SRID Register .............................................................................................................. |

29 |

2.5 |

FDC CONFIGURATION REGISTERS (LOGICAL DEVICE 0) .................................................. |

30 |

|

|

2.5.1 SuperI/O FDC Configuration Register ......................................................................... |

30 |

|

|

2.5.2 |

Drive ID Register ......................................................................................................... |

30 |

2.6 |

SUPERI/O PARALLEL PORT CONFIGURATION REGISTER (LOGICAL DEVICE 1) ............. |

30 |

|

2.7 |

SUPERI/O UART2 AND INFRARED CONFIGURATION REGISTER (LOGICAL DEVICE 2) .. |

31 |

|

2.8 |

SUPERI/O UART1 CONFIGURATION REGISTER (LOGICAL DEVICE 3) .............................. |

32 |

|

2.9 |

SUPERI/O KBC CONFIGURATION REGISTER (LOGICAL DEVICE 6) .................................. |

32 |

|

2.10 |

CONFIGURATION REGISTER BITMAPS ................................................................................ |

32 |

|

3.0The Floppy Disk Controller (FDC) (Logical Device 0)

3.1 |

FDC FUNCTIONS ..................................................................................................................... |

34 |

|

|

3.1.1 |

Microprocessor Interface ............................................................................................. |

34 |

|

3.1.2 |

System Operation Modes ............................................................................................ |

34 |

3.2 |

DATA TRANSFER ..................................................................................................................... |

35 |

|

|

3.2.1 |

Data Rates ................................................................................................................... |

35 |

|

3.2.2 |

The Data Separator ..................................................................................................... |

35 |

|

3.2.3 Perpendicular Recording Mode Support ..................................................................... |

36 |

|

|

3.2.4 |

Data Rate Selection ..................................................................................................... |

36 |

|

3.2.5 |

Write Precompensation ............................................................................................... |

37 |

|

3.2.6 FDC Low-Power Mode Logic ....................................................................................... |

37 |

|

|

3.2.7 |

Reset ........................................................................................................................... |

37 |

3.3 |

THE REGISTERS OF THE FDC ............................................................................................... |

37 |

|

www.national.com |

4 |

Table of Contents

|

3.3.1 |

Status Register A (SRA) .............................................................................................. |

38 |

|

3.3.2 |

Status Register B (SRB) .............................................................................................. |

39 |

|

3.3.3 |

Digital Output Register (DOR) ..................................................................................... |

39 |

|

3.3.4 |

Tape Drive Register (TDR) .......................................................................................... |

41 |

|

3.3.5 |

Main Status Register (MSR) ........................................................................................ |

42 |

|

3.3.6 |

Data Rate Select Register (DSR) ................................................................................ |

43 |

|

3.3.7 |

Data Register (FIFO) ................................................................................................... |

43 |

|

3.3.8 |

Digital Input Register (DIR) .......................................................................................... |

44 |

|

3.3.9 |

Configuration Control Register (CCR) ......................................................................... |

45 |

3.4 THE PHASES OF FDC COMMANDS ....................................................................................... |

45 |

||

|

3.4.1 |

Command Phase ......................................................................................................... |

45 |

|

3.4.2 |

Execution Phase .......................................................................................................... |

45 |

|

3.4.3 |

Result Phase ............................................................................................................... |

47 |

|

3.4.4 |

Idle Phase .................................................................................................................... |

47 |

|

3.4.5 |

Drive Polling Phase ..................................................................................................... |

48 |

3.5 THE RESULT PHASE STATUS REGISTERS .......................................................................... |

48 |

||

|

3.5.1 |

Result Phase Status Register 0 (ST0) ......................................................................... |

48 |

|

3.5.2 |

Result Phase Status Register 1 (ST1) ......................................................................... |

49 |

|

3.5.3 |

Result Phase Status Register 2 (ST2) ......................................................................... |

49 |

|

3.5.4 |

Result Phase Status Register 3 (ST3) ......................................................................... |

50 |

3.6 |

FDC REGISTER BITMAPS ....................................................................................................... |

51 |

|

|

3.6.1 |

Standard ...................................................................................................................... |

51 |

|

3.6.2 |

Result Phase Status .................................................................................................... |

52 |

3.7 |

COMMAND SET ....................................................................................................................... |

53 |

|

|

3.7.1 |

Abbreviations Used in FDC Commands ...................................................................... |

54 |

|

3.7.2 |

The CONFIGURE Command ...................................................................................... |

55 |

|

3.7.3 |

The DUMPREG Command ......................................................................................... |

55 |

|

3.7.4 |

The FORMAT TRACK Command ............................................................................... |

56 |

|

3.7.5 |

The INVALID Command .............................................................................................. |

58 |

|

3.7.6 |

The LOCK Command .................................................................................................. |

60 |

|

3.7.7 |

The MODE Command ................................................................................................. |

60 |

|

3.7.8 |

The NSC Command .................................................................................................... |

62 |

|

3.7.9 |

The PERPENDICULAR MODE Command ................................................................. |

62 |

|

3.7.10 |

The READ DATA Command ....................................................................................... |

64 |

|

3.7.11 |

The READ DELETED DATA Command ...................................................................... |

66 |

|

3.7.12 |

The READ ID Command ............................................................................................. |

67 |

|

3.7.13 |

The READ A TRACK Command ................................................................................. |

68 |

|

3.7.14 |

The RECALIBRATE Command ................................................................................... |

68 |

|

3.7.15 |

The RELATIVE SEEK Command ................................................................................ |

69 |

3.7.16The SCAN EQUAL, the SCAN LOW OR EQUAL and the SCAN HIGH OR EQUAL

|

Commands .................................................................................................................. |

69 |

3.7.17 |

The SEEK Command .................................................................................................. |

70 |

3.7.18 The SENSE DRIVE STATUS Command .................................................................... |

71 |

|

3.7.19 The SENSE INTERRUPT Command .......................................................................... |

71 |

|

3.7.20 The SET TRACK Command ........................................................................................ |

72 |

|

3.7.21 |

The SPECIFY Command ............................................................................................ |

73 |

3.7.22 |

The VERIFY Command ............................................................................................... |

74 |

5 |

www.national.com |

Table of Contents

3.7.23 |

The VERSION Command ............................................................................................ |

76 |

3.7.24 The WRITE DATA Command ...................................................................................... |

76 |

|

3.7.25 |

The WRITE DELETED DATA Command .................................................................... |

77 |

3.8 EXAMPLE OF A FOUR-DRIVE CIRCUIT USING THE PC87309 ............................................. |

78 |

|

4.0Parallel Port (Logical Device 1)

4.1 |

PARALLEL PORT CONFIGURATION ...................................................................................... |

79 |

|

|

4.1.1 |

Parallel Port Operation Modes .................................................................................... |

79 |

|

4.1.2 |

Configuring Operation Modes ...................................................................................... |

79 |

|

4.1.3 |

Output Pin Protection .................................................................................................. |

79 |

4.2 STANDARD PARALLEL PORT (SPP) MODES ........................................................................ |

79 |

||

|

4.2.1 |

SPP Modes Register Set ............................................................................................. |

80 |

|

4.2.2 |

SPP Data Register (DTR) ............................................................................................ |

80 |

|

4.2.3 |

Status Register (STR) ................................................................................................. |

81 |

|

4.2.4 |

SPP Control Register (CTR) ........................................................................................ |

81 |

4.3 ENHANCED PARALLEL PORT (EPP) MODES ........................................................................ |

82 |

||

|

4.3.1 |

EPP Register Set ......................................................................................................... |

82 |

|

4.3.2 |

SPP or EPP Data Register (DTR) ............................................................................... |

83 |

|

4.3.3 |

SPP or EPP Status Register (STR) ............................................................................. |

83 |

|

4.3.4 |

SPP or EPP Control Register (CTR) ........................................................................... |

83 |

|

4.3.5 |

EPP Address Register (ADDR) ................................................................................... |

83 |

|

4.3.6 |

EPP Data Register 0 (DATA0) .................................................................................... |

84 |

|

4.3.7 |

EPP Data Register 1 (DATA1) .................................................................................... |

84 |

|

4.3.8 |

EPP Data Register 2 (DATA2) .................................................................................... |

84 |

|

4.3.9 |

EPP Data Register 3 (DATA3) .................................................................................... |

84 |

|

4.3.10 |

EPP Mode Transfer Operations .................................................................................. |

85 |

|

4.3.11 |

EPP 1.7 and 1.9 Data Write and Read Operations ..................................................... |

85 |

4.4 EXTENDED CAPABILITIES PARALLEL PORT (ECP) ............................................................. |

86 |

||

|

4.4.1 |

ECP Modes ................................................................................................................. |

86 |

|

4.4.2 |

Software Operation ...................................................................................................... |

86 |

|

4.4.3 |

Hardware Operation .................................................................................................... |

87 |

4.5 |

ECP MODE REGISTERS .......................................................................................................... |

87 |

|

|

4.5.1 |

Accessing the ECP Registers ...................................................................................... |

87 |

|

4.5.2 |

Second Level Offsets .................................................................................................. |

88 |

|

4.5.3 |

ECP Data Register (DATAR) ....................................................................................... |

88 |

|

4.5.4 |

ECP Address FIFO (AFIFO) Register ......................................................................... |

88 |

|

4.5.5 |

ECP Status Register (DSR) ......................................................................................... |

88 |

|

4.5.6 |

ECP Control Register (DCR) ....................................................................................... |

89 |

|

4.5.7 |

Parallel Port Data FIFO (CFIFO) Register ................................................................... |

90 |

|

4.5.8 |

ECP Data FIFO (DFIFO) Register ............................................................................... |

90 |

|

4.5.9 |

Test FIFO (TFIFO) Register ........................................................................................ |

90 |

|

4.5.10 |

Configuration Register A (CNFGA) ............................................................................. |

90 |

|

4.5.11 |

Configuration Register B (CNFGB) ............................................................................. |

91 |

|

4.5.12 |

Extended Control Register (ECR) ............................................................................... |

91 |

|

4.5.13 |

ECP Extended Index Register (EIR) ........................................................................... |

92 |

|

4.5.14 |

ECP Extended Data Register (EDR) ........................................................................... |

93 |

www.national.com |

6 |

Table of Contents

4.5.15 |

ECP Extended Auxiliary Status Register (EAR) .......................................................... |

93 |

4.5.16 |

Control0 Register ......................................................................................................... |

93 |

4.5.17 |

Control2 Register ......................................................................................................... |

93 |

4.5.18 |

Control4 Register ......................................................................................................... |

94 |

4.5.19 |

PP Confg0 Register ..................................................................................................... |

94 |

4.6 DETAILED ECP MODE DESCRIPTIONS ................................................................................. |

95 |

|

4.6.1 |

Software Controlled Data Transfer (Modes 000 and 001) ........................................... |

95 |

4.6.2 |

Automatic Data Transfer (Modes 010 and 011) .......................................................... |

95 |

4.6.3 |

Automatic Address and Data Transfers (Mode 100) ................................................... |

97 |

4.6.4 |

FIFO Test Access (Mode 110) .................................................................................... |

97 |

4.6.5 |

Configuration Registers Access (Mode 111) ............................................................... |

97 |

4.6.6 |

Interrupt Generation .................................................................................................... |

97 |

4.7 PARALLEL PORT REGISTER BITMAPS ................................................................................. |

98 |

|

4.7.1 |

EPP Modes .................................................................................................................. |

98 |

4.7.2 |

ECP Modes ................................................................................................................. |

99 |

4.8 PARALLEL PORT PIN/SIGNAL LIST ...................................................................................... |

101 |

|

5.0Enhanced Serial Port with IR -UART2 (Logical Device 2)

5.1 |

FEATURES .............................................................................................................................. |

102 |

|

5.2 |

FUNCTIONAL MODES OVERVIEW ....................................................................................... |

102 |

|

|

5.2.1 |

UART Modes: 16450 or 16550, and Extended .......................................................... |

102 |

|

5.2.2 |

Sharp-IR, IrDA SIR Infrared Modes ........................................................................... |

102 |

|

5.2.3 |

Consumer IR Mode ................................................................................................... |

102 |

5.3 |

REGISTER BANK OVERVIEW ............................................................................................... |

102 |

|

5.4 |

UART MODES – DETAILED DESCRIPTION .......................................................................... |

104 |

|

|

5.4.1 |

16450 or 16550 UART Mode ..................................................................................... |

104 |

|

5.4.2 |

Extended UART Mode ............................................................................................... |

104 |

5.5 |

SHARP-IR MODE – DETAILED DESCRIPTION ..................................................................... |

105 |

|

5.6 |

SIR MODE – DETAILED DESCRIPTION ................................................................................ |

105 |

|

5.7 |

CONSUMER-IR MODE – DETAILED DESCRIPTION ............................................................ |

105 |

|

|

5.7.1 |

Consumer-IR Transmission ....................................................................................... |

105 |

|

5.7.2 |

Consumer-IR Reception ............................................................................................ |

106 |

5.8 |

FIFO TIME-OUTS .................................................................................................................... |

106 |

|

|

5.8.1 |

UART, SIR or Sharp-IR Mode Time-Out Conditions ................................................. |

106 |

|

5.8.2 |

Consumer-IR Mode Time-Out Conditions ................................................................. |

106 |

|

5.8.3 |

Transmission Deferral ............................................................................................... |

107 |

5.9 |

AUTOMATIC FALLBACK TO A NON-EXTENDED UART MODE .......................................... |

107 |

|

5.11 |

BANK 0 – GLOBAL CONTROL AND STATUS REGISTERS ................................................. |

107 |

|

|

5.11.1 |

Receiver Data Port (RXD) or the Transmitter Data Port (TXD) ................................. |

108 |

|

5.11.2 |

Interrupt Enable Register (IER) ................................................................................. |

108 |

|

5.11.3 |

Event Identification Register (EIR) ............................................................................ |

110 |

|

5.11.4 |

FIFO Control Register (FCR) ..................................................................................... |

112 |

|

5.11.5 |

Link Control Register (LCR) and Bank Selection Register (BSR) ............................. |

112 |

|

5.11.6 |

Bank Selection Register (BSR) ................................................................................. |

113 |

|

5.11.7 |

Modem/Mode Control Register (MCR) ...................................................................... |

114 |

7 |

www.national.com |

Table of Contents

5.11.8 |

Link Status Register (LSR) ........................................................................................ |

115 |

5.11.9 |

Modem Status Register (MSR) .................................................................................. |

116 |

5.11.10 |

Scratchpad Register (SPR) ....................................................................................... |

117 |

5.11.11 |

Auxiliary Status and Control Register (ASCR) .......................................................... |

117 |

5.12 BANK 1 – THE LEGACY BAUD GENERATOR DIVISOR PORTS ......................................... |

117 |

|

5.12.1Legacy Baud Generator Divisor Ports (LBGD(L) and LBGD(H)), .............................. 118

5.12.2 Link Control Register (LCR) and Bank Select Register (BSR) .................................. |

118 |

|

5.13 BANK 2 – EXTENDED CONTROL AND STATUS REGISTERS ............................................ |

118 |

|

5.13.1 Baud Generator Divisor Ports, LSB (BGD(L)) and MSB (BGD(H)) ........................... |

119 |

|

5.13.2 Extended Control Register 1 (EXCR1) ...................................................................... |

120 |

|

5.13.3 Link Control Register (LCR) and Bank Select Register (BSR) .................................. |

121 |

|

5.13.4 Extended Control and Status Register 2 (EXCR2) .................................................... |

121 |

|

5.13.5 |

Reserved Register ..................................................................................................... |

121 |

5.13.6 TX_FIFO Current Level Register (TXFLV) ................................................................ |

121 |

|

5.13.7 RX_FIFO Current Level Register (RXFLV) ............................................................... |

122 |

|

5.14 BANK 3 – MODULE REVISION ID AND SHADOW REGISTERS .......................................... |

122 |

|

5.14.1 Module Revision ID Register (MRID) ........................................................................ |

122 |

|

5.14.2 Shadow of Link Control Register (SH_LCR) ............................................................. |

122 |

|

5.14.3 Shadow of FIFO Control Register (SH_FCR) ............................................................ |

123 |

|

5.14.4 Link Control Register (LCR) and Bank Select Register (BSR) .................................. |

123 |

|

5.15 BANK 4 – IR MODE SETUP REGISTER ................................................................................ |

123 |

|

5.15.1 |

Reserved Registers ................................................................................................... |

123 |

5.15.2 Infrared Control Register 1 (IRCR1) .......................................................................... |

123 |

|

5.15.3 Link Control Register (LCR) and Bank Select Register (BSR) .................................. |

123 |

|

5.15.4 |

Reserved Registers ................................................................................................... |

123 |

5.16 BANK 5 – INFRARED CONTROL REGISTERS ..................................................................... |

123 |

|

5.16.1 |

Reserved Registers ................................................................................................... |

124 |

5.16.2 |

(LCR/BSR) Register .................................................................................................. |

124 |

5.16.3 Infrared Control Register 2 (IRCR2) .......................................................................... |

124 |

|

5.16.4 |

Reserved Registers ................................................................................................... |

124 |

5.17 BANK 6 – INFRARED PHYSICAL LAYER CONFIGURATION REGISTERS ......................... |

124 |

|

5.17.1 Infrared Control Register 3 (IRCR3) .......................................................................... |

124 |

|

5.17.2 |

Reserved Register ..................................................................................................... |

124 |

5.17.3 SIR Pulse Width Register (SIR_PW) ......................................................................... |

124 |

|

5.17.4 Link Control Register (LCR) and Bank Select Register (BSR) .................................. |

125 |

|

5.17.5 |

Reserved Registers ................................................................................................... |

125 |

5.18BANK 7 – CONSUMER-IR AND OPTICAL TRANSCEIVER CONFIGURATION REGISTERS 125

5.18.1 Infrared Receiver Demodulator Control Register (IRRXDC) ..................................... |

125 |

5.18.2 Infrared Transmitter Modulator Control Register (IRTXMC) ...................................... |

126 |

5.18.3 Consumer-IR Configuration Register (RCCFG) ........................................................ |

128 |

5.18.4 Link Control/Bank Select Registers (LCR/BSR) ........................................................ |

129 |

5.18.5 Infrared Interface Configuration Register 1 (IRCFG1) ............................................... |

129 |

5.18.6 Reserved Register ..................................................................................................... |

129 |

5.18.7 Infrared Interface Configuration 3 Register (IRCFG3) ............................................... |

129 |

5.18.8 Infrared Interface Configuration Register 4 (IRCFG4) ............................................... |

130 |

5.19 UART2 WITH IR REGISTER BITMAPS .................................................................................. |

131 |

www.national.com |

8 |

Table of Contents

6.0Enhanced Serial Port - UART1 (Logical Device 3)

6.1 |

REGISTER BANK OVERVIEW ............................................................................................... |

136 |

|

6.2 |

DETAILED DESCRIPTION ...................................................................................................... |

136 |

|

|

6.2.1 |

16450 or 16550 UART Mode ..................................................................................... |

137 |

|

6.2.2 |

Extended UART Mode ............................................................................................... |

137 |

6.3 |

FIFO TIME-OUTS .................................................................................................................... |

137 |

|

6.4 |

AUTOMATIC FALLBACK TO A NON-EXTENDED UART MODE .......................................... |

138 |

|

|

6.4.1 |

Transmission Deferral ............................................................................................... |

138 |

6.5 |

BANK 0 – GLOBAL CONTROL AND STATUS REGISTERS ................................................. |

138 |

|

|

6.5.1 |

Receiver Data Port (RXD) or the Transmitter Data Port (TXD) ................................. |

138 |

|

6.5.2 |

Interrupt Enable Register (IER) ................................................................................. |

139 |

|

6.5.3 |

Event Identification Register (EIR) ............................................................................ |

140 |

|

6.5.4 |

FIFO Control Register (FCR) ..................................................................................... |

142 |

|

6.5.5 |

Line Control Register (LCR) and Bank Selection Register (BSR) ............................. |

142 |

|

6.5.6 |

Bank Selection Register (BSR) ................................................................................. |

143 |

|

6.5.7 |

Modem/Mode Control Register (MCR) ...................................................................... |

143 |

|

6.5.8 |

Line Status Register (LSR) ........................................................................................ |

144 |

|

6.5.9 |

Modem Status Register (MSR) .................................................................................. |

145 |

|

6.5.10 |

Scratchpad Register (SPR) ....................................................................................... |

146 |

|

6.5.11 |

Auxiliary Status and Control Register (ASCR) .......................................................... |

146 |

6.6 |

BANK 1 – THE LEGACY BAUD GENERATOR DIVISOR PORTS ......................................... |

146 |

|

6.6.1Legacy Baud Generator Divisor Ports (LBGD(L) and LBGD(H)), .............................. 147

6.6.2 Line Control Register (LCR) and Bank Select Register (BSR) .................................. |

147 |

6.7 BANK 2 – EXTENDED CONTROL AND STATUS REGISTERS ............................................ |

148 |

6.7.1 Baud Generator Divisor Ports, LSB (BGD(L)) and MSB (BGD(H)) ........................... |

148 |

6.7.2 Extended Control Register 1 (EXCR1) ...................................................................... |

149 |

6.7.3 Line Control Register (LCR) and Bank Select Register (BSR) .................................. |

149 |

6.7.4 Extended Control and Status Register 2 (EXCR2) .................................................... |

149 |

6.7.5 Reserved Register ..................................................................................................... |

150 |

6.7.6 TX_FIFO Current Level Register (TXFLV) ................................................................ |

150 |

6.7.7 RX_FIFO Current Level Register (RXFLV) ............................................................... |

150 |

6.8 BANK 3 – MODULE REVISION ID AND SHADOW REGISTERS .......................................... |

150 |

6.8.1 Module Revision ID Register (MRID) ........................................................................ |

151 |

6.8.2 Shadow of Line Control Register (SH_LCR) ............................................................. |

151 |

6.8.3 Shadow of FIFO Control Register (SH_FCR) ............................................................ |

151 |

6.8.4 Line Control Register (LCR) and Bank Select Register (BSR) .................................. |

151 |

6.9 UART1 REGISTER BITMAPS ................................................................................................. |

151 |

7.0Power Management (Logical Device 4)

7.1 |

POWER MANAGEMENT OPTIONS ....................................................................................... |

155 |

7.2 |

THE POWER MANAGEMENT REGISTERS .......................................................................... |

155 |

|

7.2.1 Power Management Index Register .......................................................................... |

155 |

|

7.2.2 Power Management Data Register ........................................................................... |

155 |

|

7.2.3 Function Enable Register 1 (FER1) ........................................................................... |

155 |

|

7.2.4 Power Management Control Register (PMC1) .......................................................... |

156 |

9 |

www.national.com |

Table of Contents

7.2.5 Power Management Control 3 Register (PMC3) ....................................................... |

156 |

7.3 POWER MANAGEMENT REGISTER BITMAPS .................................................................... |

157 |

8.0Mouse and Keyboard Controller (KBC) (Logical Devices 5 and 6)

8.1 |

SYSTEM ARCHITECTURE ..................................................................................................... |

158 |

|

8.2 |

FUNCTIONAL OVERVIEW ..................................................................................................... |

159 |

|

8.3 |

DEVICE CONFIGURATION .................................................................................................... |

159 |

|

|

8.3.1 |

I/O Address Space .................................................................................................... |

159 |

|

8.3.2 |

Interrupt Request Signals .......................................................................................... |

159 |

|

8.3.3 |

KBC Clock ................................................................................................................. |

161 |

|

8.3.4 Timer or Event Counter ............................................................................................. |

161 |

|

8.4 |

EXTERNAL I/O INTERFACES ................................................................................................ |

161 |

|

|

8.4.1 Keyboard and Mouse Interface ................................................................................. |

161 |

|

|

8.4.2 General Purpose I/O Signals ..................................................................................... |

162 |

|

8.5 |

INTERNAL KBC - PC87309 INTERFACE ............................................................................... |

163 |

|

|

8.5.1 The KBC DBBOUT Register, Offset 60h, Read Only ................................................ |

163 |

|

|

8.5.2 The KBC DBBIN Register, Offset 60h (F1 Clear) or 64h (F1 Set), Write Only .......... |

163 |

|

|

8.5.3 The KBC STATUS Register ...................................................................................... |

163 |

|

8.6 |

INSTRUCTION TIMING ........................................................................................................... |

163 |

|

9.0Interrupt and DMA Mapping

9.1 |

IRQ MAPPING ......................................................................................................................... |

164 |

9.2 |

DMA MAPPING ....................................................................................................................... |

164 |

10.0 Device Specifications

10.1 GENERAL DC ELECTRICAL CHARACTERISTICS ............................................................... |

165 |

|

10.1.1 |

Recommended Operating Conditions ....................................................................... |

165 |

10.1.2 |

Absolute Maximum Ratings ....................................................................................... |

165 |

10.1.3 |

Capacitance ............................................................................................................... |

165 |

10.1.4 |

Power Consumption under Recommended Operating Conditions ............................ |

165 |

10.2 DC CHARACTERISTICS OF PINS, BY GROUP .................................................................... |

166 |

|

10.2.1 |

Group 1 ...................................................................................................................... |

166 |

10.2.2 |

Group 2 ...................................................................................................................... |

166 |

10.2.3 |

Group 3 ...................................................................................................................... |

166 |

10.2.4 |

Group 4 ...................................................................................................................... |

167 |

10.2.5 |

Group 5 ...................................................................................................................... |

167 |

10.2.6 |

Group 6 ...................................................................................................................... |

167 |

10.2.7 |

Group 7 ...................................................................................................................... |

168 |

10.2.8 |

Group 8 ...................................................................................................................... |

168 |

10.2.9 |

Group 9 ...................................................................................................................... |

169 |

10.2.10 |

Group 10 .................................................................................................................... |

169 |

10.2.11 |

Group 11 .................................................................................................................... |

169 |

10.2.12 |

Group 12 .................................................................................................................... |

169 |

10.2.13 |

Group 13 .................................................................................................................... |

170 |

10.2.14 |

Group 14 .................................................................................................................... |

170 |

www.national.com |

10 |

Table of Contents

10.2.15 |

Group 15 .................................................................................................................... |

170 |

10.2.16 |

Group 18 .................................................................................................................... |

170 |

10.3 AC ELECTRICAL CHARACTERISTICS .................................................................................. |

171 |

|

10.3.1 |

AC Test Conditions .................................................................................................... |

171 |

10.3.2 |

Clock Timing .............................................................................................................. |

171 |

10.3.3 |

Microprocessor Interface Timing ............................................................................... |

172 |

10.3.4 |

Baud Output Timing ................................................................................................... |

174 |

10.3.5 |

Transmitter Timing ..................................................................................................... |

175 |

10.3.6 |

Receiver Timing ......................................................................................................... |

176 |

10.3.7 |

UART, Sharp-IR, SIR and Consumer Remote Control Timing .................................. |

178 |

10.3.8 |

IRSLn Write Timing ................................................................................................... |

179 |

10.3.9 |

Modem Control Timing .............................................................................................. |

179 |

10.3.10 |

FDC DMA Timing ...................................................................................................... |

180 |

10.3.11 |

ECP DMA Timing ...................................................................................................... |

181 |

10.3.12 |

UART2 DMA Timing .................................................................................................. |

182 |

10.3.13 |

Reset Timing ............................................................................................................. |

183 |

10.3.14 |

FDC - Write Data Timing ........................................................................................... |

183 |

10.3.15 |

FDC - Drive Control Timing ....................................................................................... |

184 |

10.3.16 |

FDC - Read Data Timing ........................................................................................... |

184 |

10.3.17 |

Standard Parallel Port Timing .................................................................................... |

185 |

10.3.18 |

Enhanced Parallel Port 1.7 Timing ............................................................................ |

186 |

10.3.19 |

Enhanced Parallel Port 1.9 Timing ............................................................................ |

187 |

10.3.20 |

Extended Capabilities Port (ECP) Timing .................................................................. |

188 |

Glossary ..................................................................................................................................................... |

|

189 |

11 |

www.national.com |

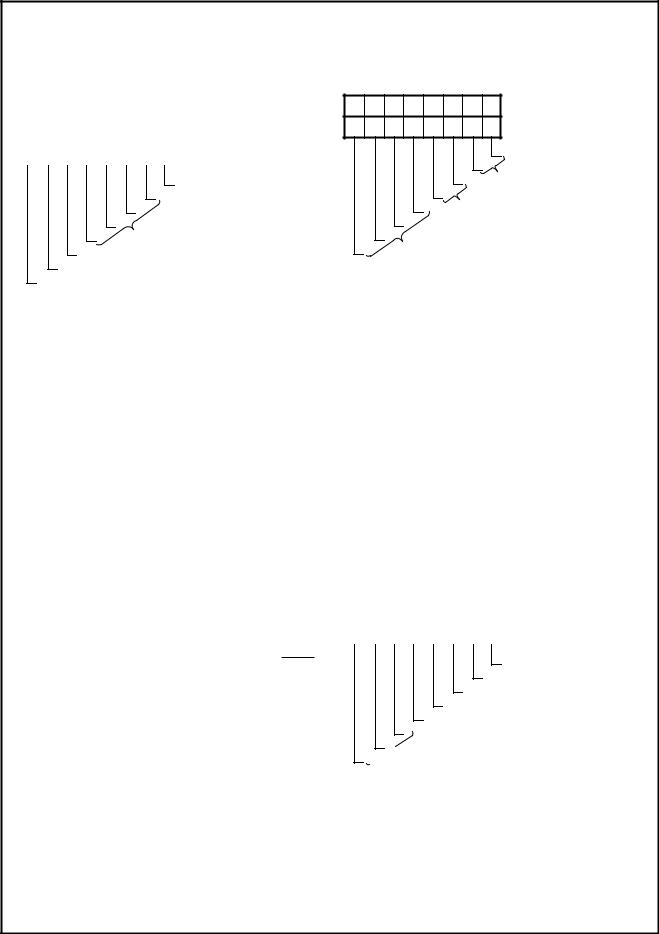

Signal/Pin Connection and Description

0.1 |

1.0 Signal/Pin Connection and Description |

|

|

|

|

|

|

|

||||||||||

Connection Signal/Pin |

|

|

|

|

|

|

|

|||||||||||

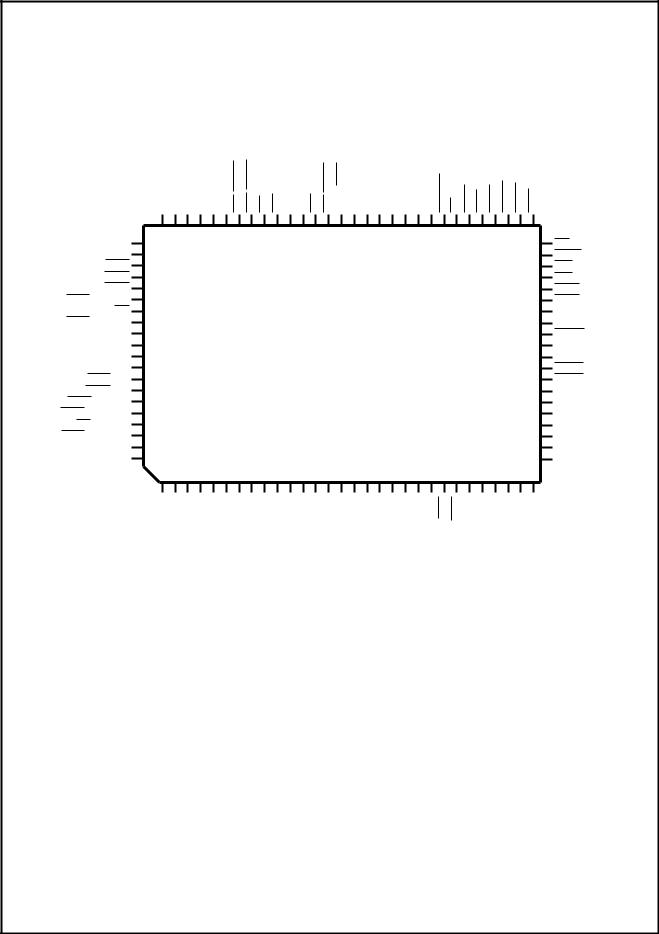

1.1 |

CONNECTION DIAGRAM |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

PD5 |

PD4 |

PD3 |

PD2 |

PD1 |

PD0 |

AFD/DSTRB |

SLIN/ASTRB |

INIT ERR PE SLCT ACK STB/WRITE BUSY/WAIT VSS P21 P20 MDAT MCLK KBDAT |

KBCLK |

DSKCHG WP |

INDEX TRK0 RDATA |

WGATE |

HDSEL |

STEP |

|

|

and |

|

PD6 |

80 79 78 77 76 75 74 73 72 71 70 69 68 67 66 65 64 63 62 61 60 59 58 57 56 55 54 53 52 51 |

|

||||||||||||||

|

81 |

|

|

|

|

|

|

|

|

|

|

|

|

|

50 |

DIR |

||

Description |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

PD7 |

82 |

|

|

|

|

|

|

|

|

|

|

|

|

|

49 |

WDATA |

|

|

CTS1 |

83 |

|

|

|

|

|

|

|

|

|

|

|

|

|

48 |

DR1/DENSEL |

|

|

DCD1 |

84 |

|

|

|

|

|

|

|

|

|

|

|

|

|

47 |

DR0 |

|

|

DSR1 |

85 |

|

|

|

|

|

|

|

|

|

|

|

|

|

46 |

MTR1/P12 |

|

|

BOUT1/DTR1/BADDR0 |

86 |

|

|

|

|

|

|

|

|

|

|

|

|

|

45 |

MTR0/DRATE0 |

|

|

RI1 |

87 |

|

|

|

|

|

|

|

|

|

|

|

|

|

44 |

IRTX/DENSEL |

|

|

RTS1/BADDR1 |

88 |

|

|

|

|

|

|

|

|

|

|

|

|

|

43 |

IRRX1/P12/DRATE0 |

|

|

SIN1 |

89 |

|

|

|

|

|

|

|

PC87309VLJ |

|

|

|

|

|

42 |

DACK3 |

|

|

|

VDD |

90 |

|

|

|

|

|

|

|

|

|

|

|

|

41 |

VDD |

|

|

|

VSS |

91 |

|

|

|

|

|

|

|

|

|

|

|

|

40 |

VSS |

|

|

|

SOUT1/CGF0 |

92 |

|

|

|

|

|

|

|

|

|

|

|

|

|

39 |

DACK2 |

|

|

CTS2/A11 |

93 |

|

|

|

|

|

|

|

|

|

|

|

|

|

38 |

DACK1 |

|

|

DCD2/P12 |

94 |

|

|

|

|

|

|

|

|

|

|

|

|

|

37 |

DRQ3 |

|

|

DSR2/DRATE0 |

95 |

|

|

|

|

|

|

|

|

|

|

|

|

|

36 |

DRQ2 |

|

BOUT2/DTR2/IRSL2/ID2 |

96 |

|

|

|

|

|

|

|

|

|

|

|

|

|

35 |

DRQ1 |

|

|

|

RI2/DENSEL |

97 |

|

|

|

|

|

|

|

|

|

|

|

|

|

34 |

MR |

|

|

RTS2/IRSL1/ID1 |

98 |

|

|

|

|

|

|

|

|

|

|

|

|

|

33 |

CLKIN |

|

|

SIN2/ID3 |

99 |

|

|

|

|

|

|

|

|

|

|

|

|

|

32 |

IRQ12 |

|

SOUT2/IRSL0/IRRX2/ID0 |

100 |

|

|

|

|

|

|

|

|

|

|

|

|

|

31 |

IRQ7 |

|

|

|

|

1 |

2 |

3 |

4 |

5 |

6 |

7 |

8 |

9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 |

|

||||||

|

|

|

D0 |

D1 |

D2 |

D3 |

D4 |

D5 |

D6 |

D7 |

A0 A1 A2 A3 A4 A5 VSS A6 A7 A8 A9 A10 AEN |

IOCHRDY |

IORD IOWR |

TC IRQ1 IRQ3 |

IRQ4 |

IRQ5 |

IRQ6 |

|

|

www.national.com |

|

|

|

|

|

|

|

|

12 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Signal/Pin Connection and Description |

||||||||||||||

|

1.2 SIGNAL/PIN DESCRIPTIONS |

|

|

The Module column indicates the functional module that is |

||||||||||||||||||

|

TABLE 1-1 lists the signals of the PC87309 in alphabetical |

associated with these pins. In this column, the System label |

||||||||||||||||||||

|

indicates internal functions that are common to more than |

|||||||||||||||||||||

|

order and shows the pin(s) associated with each. TABLE |

|||||||||||||||||||||

|

one module. The I/O and Group # column describes wheth- |

|||||||||||||||||||||

|

1-2 on page 18 lists the signals that are multiplexed in Full- |

|||||||||||||||||||||

|

er the pin is an input, output, or bidirectional pin (marked as |

|||||||||||||||||||||

|

IR and Two-UART modes. TABLE 1-3 on page 18 lists the |

|||||||||||||||||||||

|

Input, Output or I/O, respectively). |

|||||||||||||||||||||

|

pins that have strap functions during reset. |

|

||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

TABLE 1-1. Signal/Pin Description Table |

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

Signal/Pin |

Pin |

Module |

I/O and |

|

|

|

|

|

|

Function |

|

|||||||||

|

|

Name |

Number |

Group # |

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|||||||||||||||

|

|

|

|

|

|

|

|

|||||||||||||||

|

|

A11-0 |

93, 20-16, |

ISA-Bus |

Input |

ISA-Bus Address –A11-0 are used for address decoding on any |

|

|||||||||||||||

|

|

|

|

|

|

14-9 |

|

Group 1 |

access except DMA accesses, on the condition that the AEN signal is |

|

||||||||||||

|

|

|

|

|

|

|

|

|

low. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

A11 is multiplexed with |

|

|

on pin 93 and available in Full-IR mode |

|

|||||||||

|

|

|

|

|

|

|

|

|

CTS2 |

|||||||||||||

|

|

|

|

|

|

|

|

|

only. Since A11 is required to support full ISA PnP mode (for |

|

||||||||||||

|

|

|

|

|

|

|

|

|

decoding A79h), this mode is not available in Two-UART mode. |

|

||||||||||||

|

|

|

|

|

|

|

|

|

See Section 2.2.2. |

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

68 |

Parallel Port |

Input |

Acknowledge –This input signal is pulsed low by the printer to |

|

||||||||||||

|

|

ACK |

||||||||||||||||||||

|

|

|

|

|

|

|

|

Group 3 |

indicate that it has received data from the parallel port. This pin is |

|

||||||||||||

|

|

|

|

|

|

|

|

|

internally connected to an internal weak pull-up. |

|

||||||||||||

|

|

|

|

|

74 |

Parallel Port |

I/O |

Automatic Feed –When this signal is low the printer should |

|

|||||||||||||

|

|

AFD |

||||||||||||||||||||

|

|

|

|

|

|

|

|

Group 8 |

automatically feed a line after printing each line. This pin is in TRI- |

|

||||||||||||

|

|

|

|

|

|

|

|

|

STATE after a 0 is loaded into the corresponding control register bit. |

|

||||||||||||

|

|

|

|

|

|

|

|

|

An external 4.7 KΩ pull-up resistor should be attached to this pin. |

|

||||||||||||

|

|

|

|

|

|

|

|

|

This signal is multiplexed with |

|

|

|

|

|

See TABLE 4-12 on page 101 |

|

||||||

|

|

|

|

|

|

|

|

|

DSTRB. |

|||||||||||||

|

|

|

|

|

|

|

|

|

for more information. |

|

||||||||||||

|

|

|

|

|

|

|

|

|||||||||||||||

|

|

AEN |

21 |

ISA-Bus |

Input |

DMA Address Enable –This input signal disables function selection |

|

|||||||||||||||

|

|

|

|

|

|

|

|

Group 1 |

via A11-0 when it is high. Access during DMA transfer is not affected |

|

||||||||||||

|

|

|

|

|

|

|

|

|

by this signal. This pin is used for external decoding of A11-15 in |

|

||||||||||||

|

|

|

|

|

|

|

|

|

Two-UART mode or A15-12 in Full-IR mode. |

|

||||||||||||

|

|

|

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

73 |

Parallel Port |

Output |

Address Strobe (EPP) –This signal is used in EPP mode as an |

|

||||||||||||

|

|

ASTRB |

||||||||||||||||||||

|

|

|

|

|

|

|

|

Group 8 |

address strobe. It is active low. |

|

||||||||||||

|

|

|

|

|

|

|

|

|

This signal is multiplexed with |

SLIN. |

|

See TABLE 4-12 on page 101 for |

|

|||||||||

|

|

|

|

|

|

|

|

|

more information. |

|

||||||||||||

|

|

|

|

|

|

|

||||||||||||||||

|

BADDR1,0 |

88,86 |

Configuration |

Input |

Base Address Strap Pins 0 and 1 –These pins determine the base |

|

||||||||||||||||

|

|

|

|

|

|

|

|

Group 4 |

addresses of the Index and Data registers, the value of the Plug and |

|

||||||||||||

|

|

|

|

|

|

|

|

|

Play ISA Serial Identifier and the configuration state immediately after |

|

||||||||||||

|

|

|

|

|

|

|

|

|

reset. These pins are pulled down by internal 30 KΩ resistors. |

|

||||||||||||

|

|

|

|

|

|

|

|

|

External 10 KΩ pull-up resistors to VDD should be employed. |

|

||||||||||||

|

|

|

|

|

|

|

|

|

BADDR1 is multiplexed with |

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

RTS1. |

|||||||||||||

|

|

|

|

|

|

|

|

|

BADDR0 is multiplexed with |

|

|

|

and BOUT1. |

|

||||||||

|

|

|

|

|

|

|

|

|

DTR1 |

|||||||||||||

|

|

|

|

|

|

|

|

|

See TABLE 2-1 and Section 2.1. |

|

||||||||||||

|

|

|

|

|

|

|

||||||||||||||||

|

BOUT2,1 |

96,86 |

UART1, |

Output |

Baud Output –This multi-function pin provides the associated serial |

|

||||||||||||||||

|

|

|

|

|

|

|

UART2 |

Group 12 |

channel Baud Rate generator output signal if test mode is selected, |

|

||||||||||||

|

|

|

|

|

|

|

|

|

i.e., bit 7 of the EXCR1 register is set. See “Bit 7 - Baud Generator |

|

||||||||||||

|

|

|

|

|

|

|

|

|

Test (BTEST)” on page 121. |

|

||||||||||||

|

|

|

|

|

|

|

|

|

After Master Reset this pin provides the DTR function. |

|

||||||||||||

|

|

|

|

|

|

|

|

|

BOUT2 is multiplexed with DTR2, IRSL2 and ID2. |

|

||||||||||||

|

|

|

|

|

|

|

|

|

BOUT1 is multiplexed with DRT1 and BADDR0. |

|

||||||||||||

|

|

|

|

|

|

|

||||||||||||||||

|

BUSY |

66 |

Parallel Port |

Input |

Busy –This pin is set high by the printer when it cannot accept |

|

||||||||||||||||

|

|

|

|

|

|

|

|

Group 2 |

another character. It is internally connected to a weak pull-down |

|

||||||||||||

|

|

|

|

|

|

|

|

|

resistor. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

This signal is multiplexed with |

|

See TABLE 4-12 on page 101 for |

|

||||||||||

|

|

|

|

|

|

|

|

|

WAIT. |

|||||||||||||

|

|

|

|

|

|

|

|

|

more information. |

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

DESCRIPTIONS SIGNAL/PIN

13 |

www.national.com |

SIGNAL/PIN |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Signal/Pin Connection and Description |

||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Signal/Pin |

Pin |

Module |

I/O and |

|

|

|

|

|

|

Function |

|

||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||||||

|

|

|

Name |

Number |

Group # |

|

|

|

|

|

|

|

|||||||||||||||||||||||||

|

|

|

|

|

|