TL/F/11669

PCM16C00 Configurable Multiple Function PCMCIA Interface Chip

October 1994

PCM16C00

Configurable Multiple Function PCMCIA Interface Chip

General Description

National’s PCM16C00 acts as a standard interface between

the PCMCIA bus and card-side local bus for I/O and memory PCMCIA cards. This device allows the card designer to

focus on the design of the dual I/O functions while providing

a one-chip solution for I/O memory window control, concurrent interrupt control, EEPROM interfacing, and power management. In addition to being configurable to interface to

any two ISA compatible I/O functions, the PCM16C00 supports logic necessary to simplify a design that uses the National DP83902A ST-NIC Ethernet Controller as one of the

functions.

The PCM16C00 is fully compliant with PCMCIA version 2.1

and is compatible with serial 4-kbit and 16-kbit EEPROMs

with 8-bit and 16-bit organizations that use the MICROWIRE

TM

protocol. This multi-function interface IC allows the

system software to setup I/O decode windows and provides

the Attribute memory decode control that allow attribute

read and write data transfers.

Features

Y

PCMCIA Bus Interface

Y

Compliant with multi-function extension to PCMCIA

Standards 3.X

Y

PCMCIA version 2.1 configuration registers

Y

Serial EEPROM interface compatible with MICROWIRE

EEPROM protocol

Y

2-kbyte on chip RAM for attribute memory which shadows the CIS and is used for loading static registers

Y

Address decoding and control for 2 I/O functions

Y

Logic to support any two interrupt capable I/O functions on a PCMCIA card

Y

Power management and clock control

Y

Programmable arbitration unit for PCMCIA host and two

functions

Y

Common memory logic

Y

National DP83902A Ethernet LAN support logic

Y

4 Bit, direction programmable, generic digital port

Y

ISA-like interface to card function

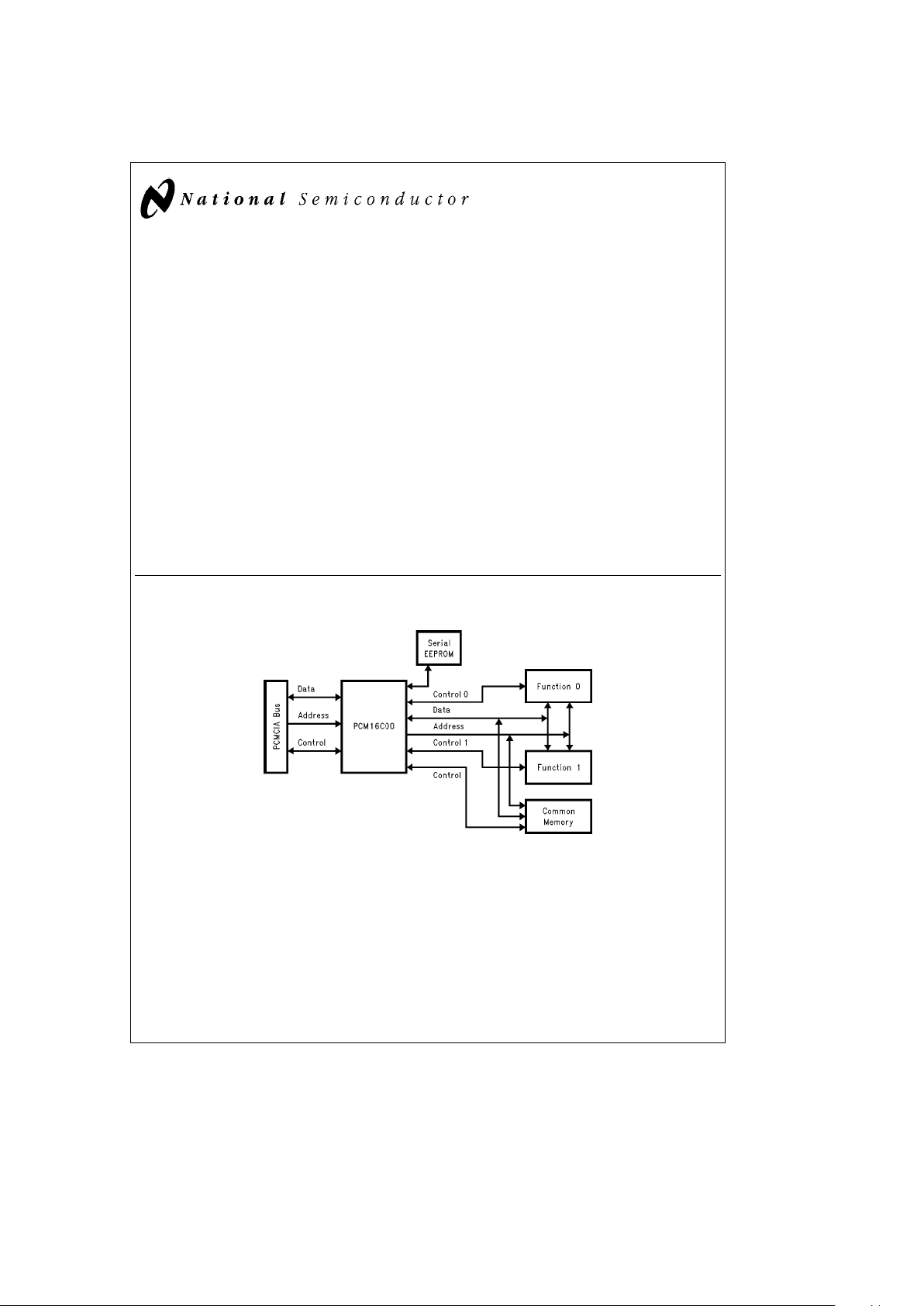

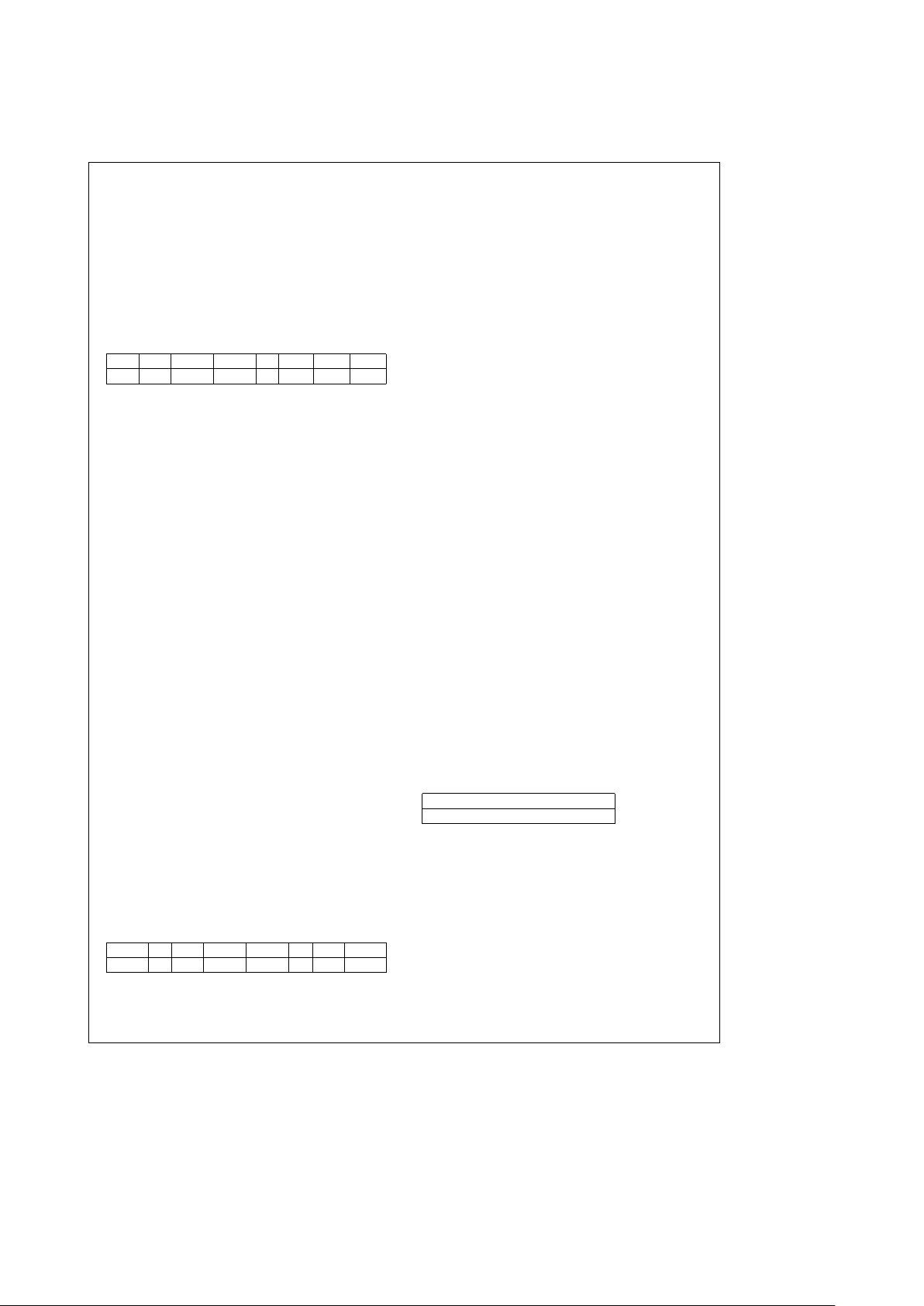

1.0 System Diagram

TL/F/11669– 1

FIGURE 1-1

TRI-STATEÉis a registered trademark of National Semiconductor Corporation.

MICROWIRE

TM

is a trademark of National Semiconductor Corporation.

C

1995 National Semiconductor Corporation RRD-B30M75/Printed in U. S. A.

Table of Contents

GENERAL DESCRIPTION AND PRODUCT FEATURES ААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА1

1.0 SYSTEM DIAGRAMАААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА1

2.0 CONNECTION DIAGRAM АААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА3

3.0 PINOUT DESCRIPTION AND DETAILED TABLES АААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА4

4.0 BLOCK DIAGRAM ААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА7

5.0 FUNCTIONAL DESCRIPTIONААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА8

5.1 Address Maps ААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА8

5.1.1 Attribute Memory Addressing АААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА8

5.1.2 I/O Memory Addressing ААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА9

5.1.3 Common Memory Addressing АААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА9

5.2 Registers ААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА9

5.2.1 PCMCIA Registers АААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА9

5.2.2 PCM16C00 Specific Registers АААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА10

5.2.2.1 Standard Mode Register Set ААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА10

5.2.2.2 LAN (National ST-NIC) Mode Register Set ААААААААААААААААААААААААААААААААААААААААААААААААААААААА14

5.3 Logic Descriptions АААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА17

5.3.1 I/O Card Interface Logic for PCMCIA Host I/O Accesses ААААААААААААААААААААААААААААААААААААААААААААААААА17

5.3.2 EEPROM Interface АААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА17

5.3.2.1 CIS Data Security АААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА18

5.3.3 Power Management ААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА18

5.3.4 Bus Arbitration АААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА19

5.3.5 Common Memory Management ААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА19

6.0 OPERATIONAL MODES АААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА19

6.1 Initial Setup (reset) and Configuration АААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА19

6.2 Reset Conditions ААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА19

6.3 Interrupt Control АААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА19

6.4 Functional Concurrency ААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА20

6.5 16-Bit/8-Bit Operation ААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА20

6.6 Special Testability Modes АААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА20

SOFTWARE ААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА20

ABSOLUTE MAXIMUM RATINGSАААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА22

RECOMMENDED OPERATING CONDITIONS ААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА22

RELIABILITY REQUIREMENTS ААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА22

DC ELECTRICAL CHARACTERISTICS ААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА22

TYPICAL APPLICATIONS АААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА38

REFERENCES ААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААААА38

2

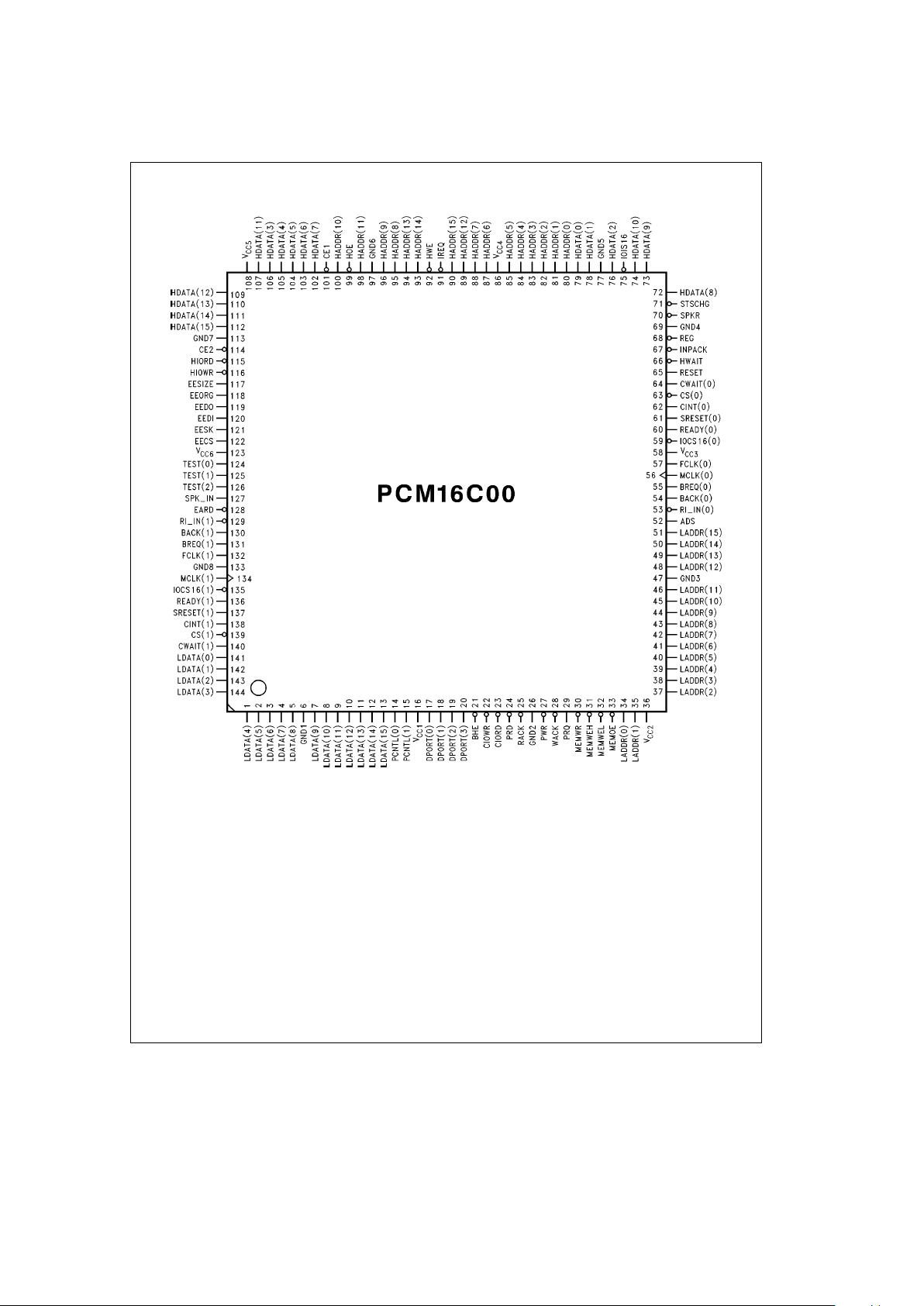

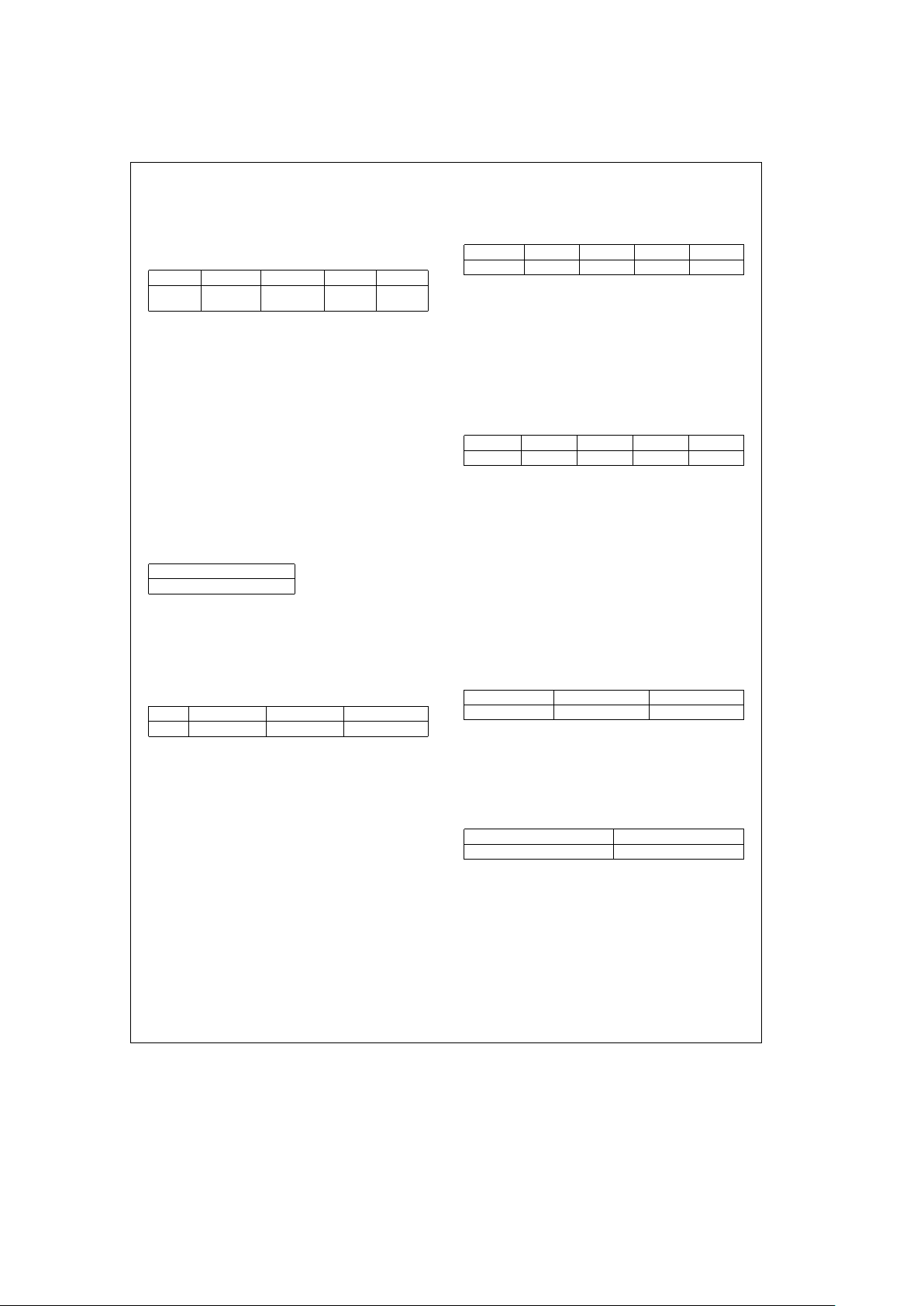

2.0 Connection Diagram

TL/F/11669– 2

Order Number PCM16C00VNG

See NSC Package Number VNG144A

3

3.0 Pinout Description

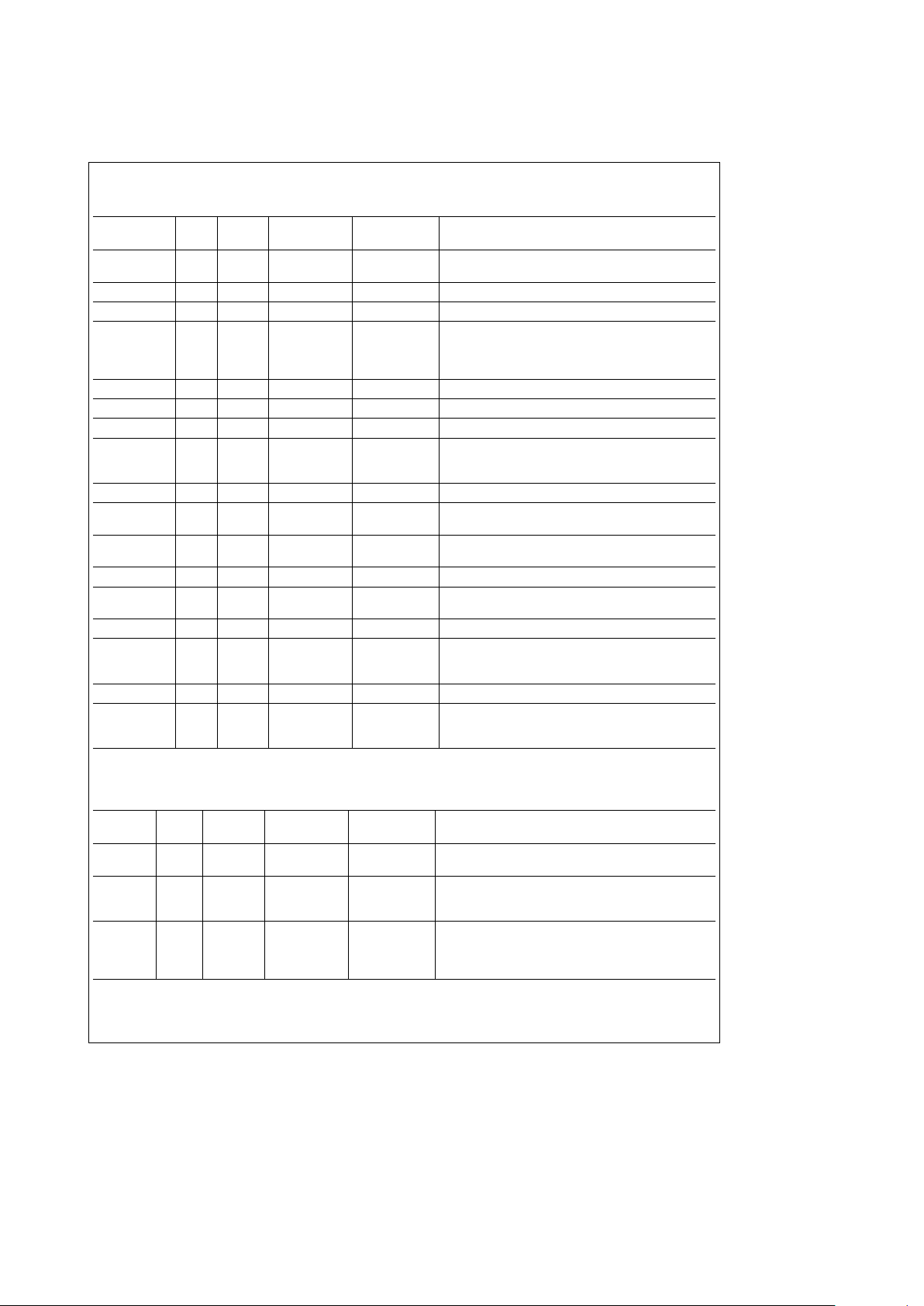

TABLE 3-1. PCMCIA Host-Side Pins

Pin Pin Pin Level Internal

Description

Name Type No. Compatibility Resistor

HDATA(15:0) I/O 112–109, TTL 6 mA

l

100k to GND PCMCIA Host Data Bus.

107, 74–72,

102–106,

76, 78, 79

HADDR(15:0) I 90, 93, 94, TTL

l

100k to GND PCMCIA Host Address Bus.

89, 98, 100,

96, 95, 88,

87, 85–80

HOE

Ý

I 99 TTL

l

100k to V

CC

PCMCIA Host uses this pin to read common or

attribute memory space.

HWE

Ý

I 92 TTL

l

100k to V

CC

PCMCIA Host uses this pin to write common or

attribute memory space.

HIORD

Ý

I 115 TTL

l

100k to V

CC

PCMCIA Host uses this pin to read I/O memory

space.

HIOWR

Ý

I 116 TTL

l

100k to V

CC

PCMCIA Host uses this pin to write I/O

memory space.

IREQ

Ý

O 91 CMOS 6 mA Interrupt Request signal to PCMCIA Host.

HWAIT

Ý

O 66 CMOS 6 mA This pin allows the PCM16C00 to insert wait

states in a PCMCIA transaction.

IOIS16

Ý

O 75 CMOS 6 mA Low indicates this I/O access to the card is

capable of 16-bit access. Function 0 and 1 may

use their IOCS16(1:0)

Ý

respectively to control

this signal and inform the host if a 16-bit access

to the target is feasible.

INPACK

Ý

O 67 CMOS 6 mA Signals a valid I/O read.

CE1

Ý

I 101 TTL

l

100k to V

CC

Indicates even address byte. Odd addresses

are not released. CE1

Ý

and CE2Ýassertion

encodings are specified by the PCMCIA

Specification.

CE2

Ý

I 114 TTL

l

100k to V

CC

Indicates odd addressing only. CE1Ýand

CE2

Ý

assertion encodings are specified by the

PCMCIA Specification.

REG

Ý

I 68 TTL

l

100k to V

CC

Indicates access to attribute memory space or

I/O address space. REG

Ý

must be high to

access common memory space.

RESET I 65 TTL Schmitt

l

100k to V

CC

Asynchronously resets the PCM16C00.

SPKR

Ý

O 70 CMOS 6 mA If Audio bits are set in the Card Configuration

Status Register and in either of the Function

Configuration Status Registers 0,1, then

SPKR

Ý

is invert of SPK IN pin, else SPKRÝis

high.

STSCHG

Ý

O 71 CMOS 6 mA STSCHGÝis asserted when the Changed bit

and SigChg bit are set in the Card

Configuration Status Register.

4

3.0 Pinout Description (Continued)

TABLE 3-2. Serial EEPROM Interface Pins

Pin Pin Pin Level Internal

Description

Name Type No. Compatibility Resistor

EEDO I 119 TTL Serial Data in from EEPROM.

EEDI O 120 CMOS 6 mA Serial Data out to EEPROM.

EECS O 122 CMOS 6 mA EEPROM Chip Select.

EESK O 121 CMOS 6 mA EEPROM Clock. FreqeMCLK(0)/32.

EESize I 117 TTL

l

100k to V

CC

EEPROM Size. If high, the EEPROM size is 16-kbit, else the

size is 4-kbit.

EEORG I 118 TTL

l

100k to V

CC

EEPROM Organization pin. If high, the EEPROM is organized

as 16-bit words, else organization is 8 bits.

Note: The Enable EEPROM function is performed in software by writing to the EEPROM Control Register. The Enable EEPROM bit will default to low (disabled)

upon power on.

TABLE 3-3. Card-Side Interface Pins

Pin Pin Pin Level Internal

Description

Name Type No. Compatibility Resistor

LDATA(15:0) I/O 13– 7, TTL 6 mA Hold Circuit Card-side Data Bus.

5–1,

(Note 1)

144–141

DPORT(3:0) I/O 20, 19, TTL 6 mA Generic, Direction programmable function port for

18, 17 additional user signals. In LAN Mode, these signals are

assigned specific meaning for use with an Ethernet LAN

IC.

EARD

Ý

O 128 CMOS 6 mA Chip select for external attribute memory not shadowed

in PCM16C00 IC.

SPK IN I 127 TTL Schmitt Input Audio Signal.

RIÐIN(0)

Ý

I 53 TTL Schmitt Ring Indicator for function 0. In LAN Mode, this is a

packet indicator input.

RIÐIN(1)

Ý

I 129 TTL Schmitt Ring Indicator for function 1.

CIORD

Ý

O 23 CMOS 6 mA I/O read signals are passed through from HIORD

Ý

according to the expression shown below when a valid

address is decoded.

(CIORD

Ý

e

HIORD

Ý

a

REG

Ý

a

(CE1Ý* CE2Ý)

CIOWR

Ý

O 22 CMOS 6 mA I/O write signals are passed through from HIOWR

Ý

according to the expression shown below when a valid

address is decoded.

CIOWR

Ý

e

HIOWR

Ý

a

REG

Ý

a

(CE1Ý* CE2Ý)

CWAIT(1:0) I 140, 64 TTL Card-side transaction wait state inputs.

CS(1:0)

Ý

O 139, 63 CMOS 6 mA Chip select for each function.

BHE

Ý

O 21 CMOS 6 mA Byte high enable. When de-asserted and CS( )

Ý

asserted, an 8-bit access on LDATA(7:0) is in progress.

This holds for both odd and even addresses. When

asserted and CS( )

Ý

asserted, a 16-bit access on

LDATA(15:0) is in progress.

READY(1:0) I 136, 60 TTL

l

100k to VCCIndicates that the function is either READY orEREADY

(i.e. - Busy). This signal is used to assert the Rdy/Bsy

Ý

bit in Pin Replacement Registers.

CINT(1:0) I 138, 62 TTL Schmitt Card-side interrupt input signals.

SRESET(1:0) O 137, 61 CMOS 6 mA Signals reset to Card-side functions.

5

3.0 Pinout Description (Continued)

TABLE 3-3. Card-Side Interface Pins (Continued)

Pin Pin Pin Level Internal

Description

Name Type No. Compatibility Resistor

IOCS16(1:0)

Ý

I 135, 59 TTL This pin is asserted during an access to a function if that

function is capable of a 16-bit access.

BREQ(1:0) I 131, 55 TTL Bus requests for local and remote DMA.

BACK(1:0) O 130, 54 CMOS 6 mA Bus grants for local and remote DMA.

LA(15:0) O Tri 51–48, CMOS 6 mA Hold Circuit Local Address Bus. This may be equivalent to the

46–37, HADDR(15:0) bus for PCMCIA Host reads/writes or a

(Note 1)

35, 34 latched address from a DMA controller such as a LAN

controller.

ADS I 52 TTL Address Strobe to latch LDATA(15:0) onto LA(15:0).

PCNTL(1:0) O 15, 14 CMOS 6 mA Power management control signals or general outputs.

MCLK(1:0) I 134, 56 TTL Schmitt Input clocks for function 0 and function 1.

FCLK(1:0) O 132, 57 CMOS 6 mA Output clock signals for function 0 and function 1.

These may be gated on/off or be a divided value of

MCLK(1:0).

MEMWR

Ý

I 30 TTL

l

100k to V

CC

Common Memory write input for one function.

MEMWEH

Ý

O Tri 31 CMOS 6 mA

l

10k to V

CC

Common Memory write output for upper byte of data

word.

MEMWEL

Ý

O Tri 32 CMOS 6 mA

l

10k to V

CC

Common Memory write output for lower byte of data

word.

MEMOE

Ý

O Tri 33 CMOS 6 mA

l

10k to V

CC

Common Memory read signal.

PRQ I 29 TTL

l

100k to GND Port Request from LAN Device for Remote DMA

Access mode to I/O Register.

PRD

Ý

I 24 TTL

l

100k to V

CC

Port Read from LAN Device to I/O Register.

RACK

Ý

O 25 CMOS 6 mA Read Acknowledge from the PCM16C00 signaling to

the LAN that the PCMCIA Host has read the entire I/O

Register.

PWR

Ý

I 27 TTL

l

100k to V

CC

Port Write from LAN Device to I/O Register.

WACK

Ý

O 28 CMOS 6 mA Write Acknowledge from the PCM16C00 signaling to

the LAN that the PCMCIA Host has placed data in the

entire I/O Register.

Note 1: The Hold Circuit will hold the signal to the logic value it was last set to when the line is TRI-STATEÉ. This will insure that inputs do not float during a

TRI-STATE condition.

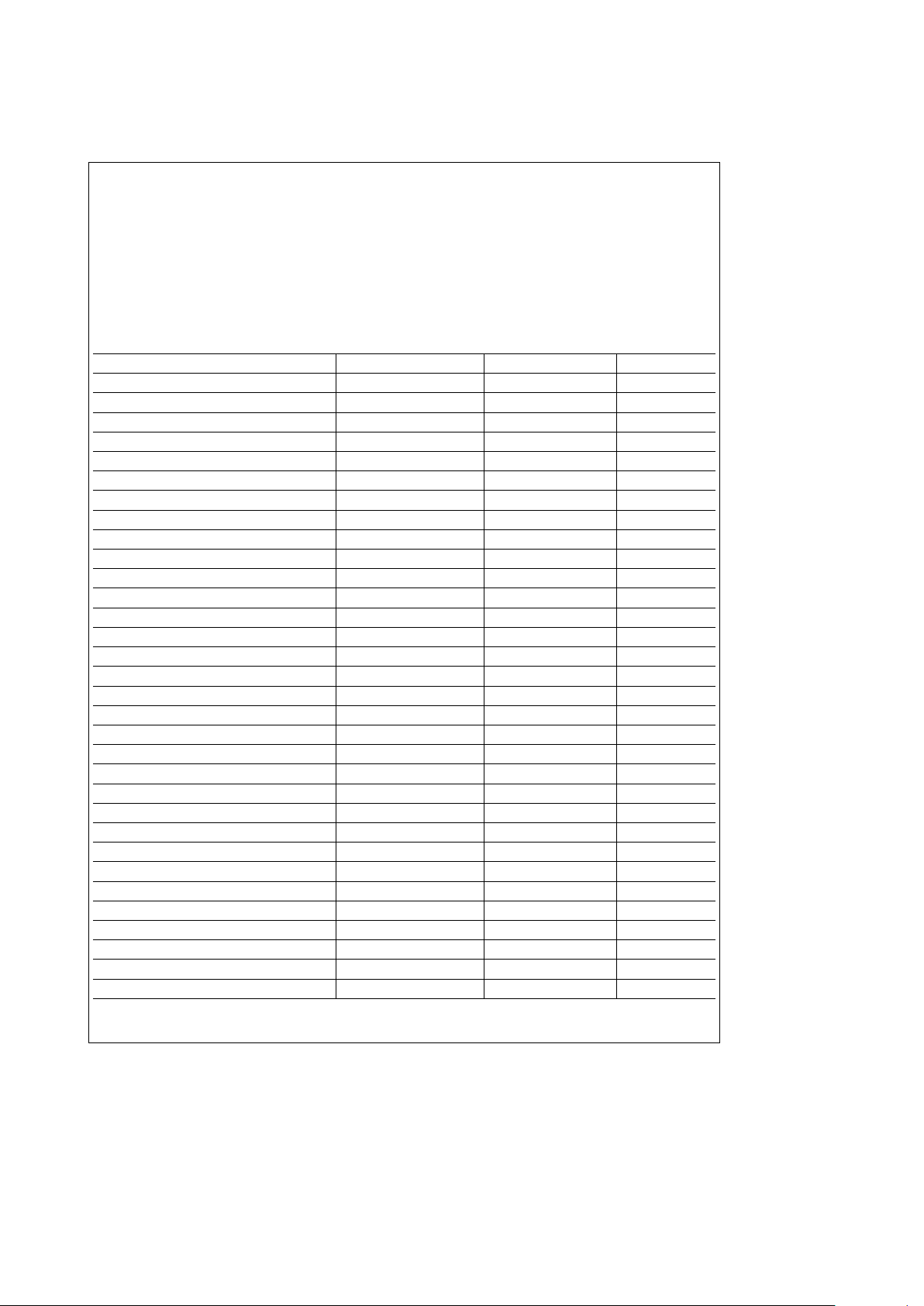

TABLE 3-4. Miscellaneous Pins

Pin Pin Pin Level Internal

Description

Name Type No. Compatibility Resistor

TEST(2:0) I 126, 125, TTL

l

100k to GND Test pins. These pins should be left disconnected for

124 normal operation.

VCC(5:0) Power 16, 36, Power Voltage.

58, 86,

108, 123

GND(7:0) Power 6, 26, 47, Return Voltage.

69, 77,

97, 113,

133

6

3.0 Pinout Description (Continued)

Pin Total:

Host-Side Interface Pins 46

EEPROM Interface Pins 6

Card-Side Interface Pins 75

Miscellaneous Pins 17

Total Pins 144

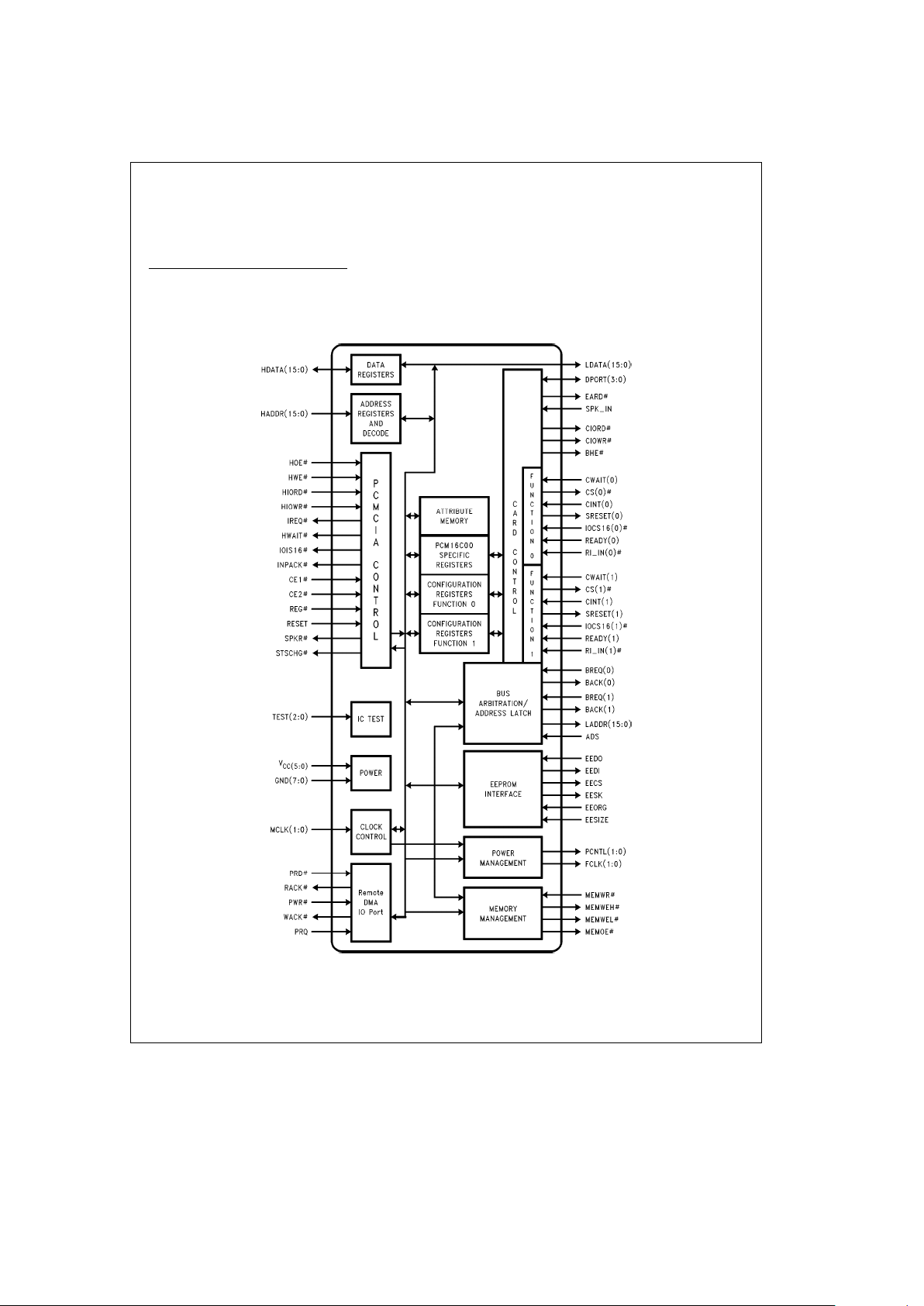

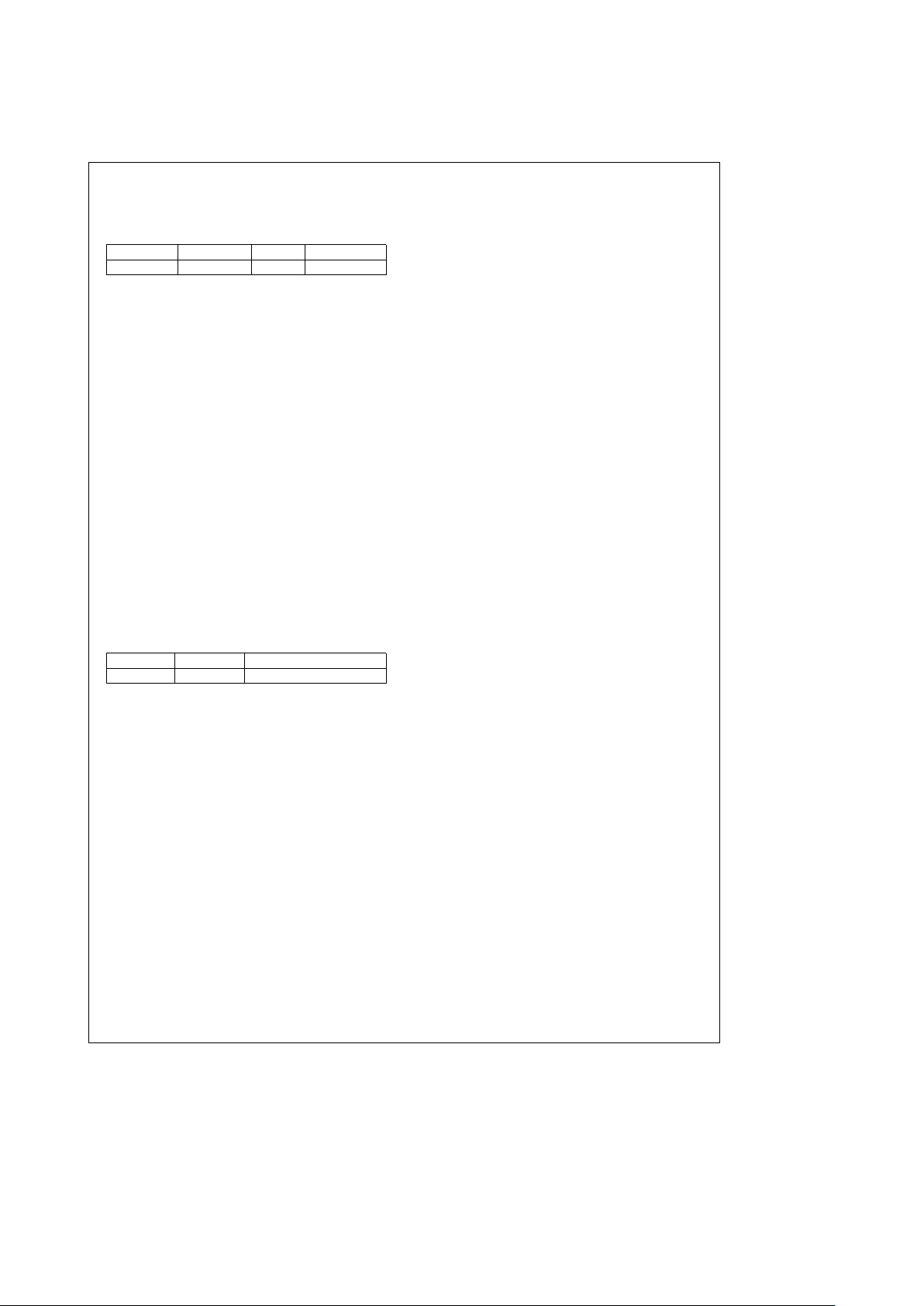

4.0 Block Diagram

TL/F/11669– 3

FIGURE 4-1

7

5.0 Functional Description

The Multi-function PCMCIA card interface IC (integrated circuit) provides an integrated solution to interfacing dual function I/O cards with the PCMCIA Bus. The part has a continguous 2-kbyte RAM block to store attribute memory. The IC

also provides an EEPROM interface to serial EEPROMs

that use the MICROWIRE protocol. At a minimum, a 4-kbit

serial EEPROM is required. The 16-kbit EEPROM is optional. The part allows I/O address windows to be programmed

independently for each function.

5.1 ADDRESS MAPS

5.1.1 Attribute Memory Addressing

The Attribute Memory space contains both the Card Information Structure (CIS), PCMCIA Registers for both functions, and PCM16C00 implementation specific registers.

Note that PCMCIA specifies that Attribute memory may only

be accessed on even address byte boundaries. The Attribute Memory space fragmentation is shown in Table 5-1.

TABLE 5-1. Attribute Memory Map

Register Description Register Type Address (Hex) EEPROM

Card Information Structure PCMCIA CIS 0x000-0x03E2 Yes

Pin Polarity Register PCM16C00 Specific 0x03E4 Yes

PMGR and Clock Register PCM16C00 Specific 0x03E6 Yes

CTERM 0 Register PCM16C00 Specific 0x03E8 Yes

CTERM 1 Register PCM16C00 Specific 0x03EA Yes

Arbiter Priority Register PCM16C00 Specific 0x03EC Yes

Arbiter Latency Register PCM16C00 Specific 0x03EE Yes

Miscellaneous Register PCM16C00 Specific 0x03F0 Yes

Digital Port Direction Register PCM16C00 Specific 0x03F2 Yes

Digital Port Register PCM16C00 Specific 0x03F4 Yes

Wait State Timer Register PCM16C00 Specific 0x03F6 Yes

Reserved for Future Use Registers PCM16C00 Specific 0x03F8 –0x03FE Yes

Card Information Structure PCMCIA CIS 0x0400–0x0FFE Optional

ID Register PCM16C00 Specific 0x1000 No

EEPROM Control Register PCM16C00 Specific 0x1002 No

Reserved for Future Use Registers PCM16C00 Specific 0x1004 –0x101E No

Function 0 Configuration Option Register PCMCIA 0x1020 No

Function 0 Configuration Status Register PCMCIA 0x1022 No

Function 0 Pin Replacement Register PCMCIA 0x1024 No

Unused PCMCIA 0x1026 No

Function 0 I/O Event Register PCMCIA 0x1028 No

Function 0 Base A Register PCMCIA Extension 0x102A No

Function 0 Base B Register PCMCIA Extension 0x102C No

Unused PCMCIA Extension 0x102E – 0x1030 No

Function 0 Limit Register PCMCIA Extension 0x1032 No

Reserved for Future Use Registers PCMCIA Extension 0x1034 – 0x103E No

Function 1 Configuration Option Register PCMCIA 0x1040 No

Function 1 Configuration Status Register PCMCIA 0x1042 No

Function 1 Pin Replacement Register PCMCIA 0x1044 No

Unused PCMCIA 0x1046 No

Function 1 I/O Event Register PCMCIA 0x1048 No

Function 1 Base A Register PCMCIA Extension 0x104A No

8

5.0 Functional Description (Continued)

TABLE 5-1. Attribute Memory Map (Continued)

Register Description Register Type Address (Hex) EEPROM

Function 1 Base B Register PCMCIA Extension 0x104C No

Unused PCMCIA Extension 0x104E – 0x1050 No

Function 1 Limit Register PCMCIA Extension 0x1052 No

Reserved for Future Use Registers PCMCIA Extension 0x1054–0x105E No

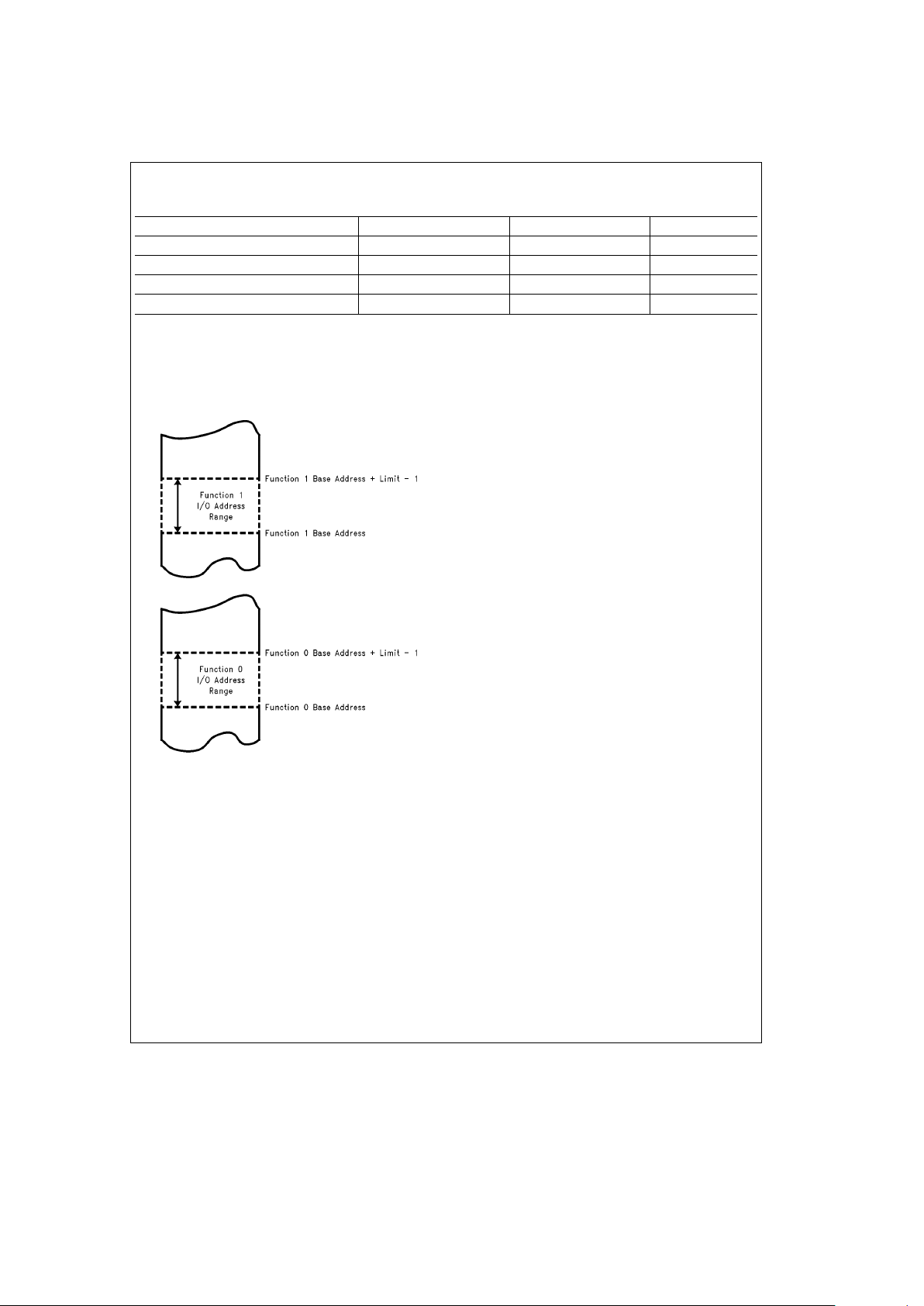

5.1.2 I/O Memory Addressing

National’s PCM16C00 uses a pair of address base and limit

registers to fragment the I/O Address space. This allows I/

O transactions from the PCMCIA Host to be steered to the

appropriate function.

TL/F/11669– 4

I/O Address Space

FIGURE 5-1. I/O Address Decoding for

two functions on a PCMCIA Card

5.1.3 Common Memory Addressing

National’s PCM16C00 does not specifically decode common memory address accesses initiated by the host. Rather, it will pass host accesses HADDR(15:0) through to

LADDR(15:0) and HDATA(15:0) through to LDATA(15:0)

once the host is granted access to the card using the arbiter. In addition, the PCM16C00 will pass the HOE

Ý

signal

assertion through to the MEMOE

Ý

signal and the host

HWE

Ý

signal assertion to the MEMWEHÝ/MEMWEL

Ý

signals appropriately. The assertion of MEMWEHÝ, MEMWEL

Ý

, or both is determined by an 8-bit or 16-bit access

and the address boundary as specified in the PCMCIA

Specification. The functions are free to use common memory by arbitrating for the card local bus. If granted, the

PCM16C00 will relinquish the LADDR(15:0) and LDATA(15:0) bus to the function.

If a function is mapped to common memory, such as a

FLASH device, and requires further address lines, it may

use the HADDR(25:16) lines from the PCMCIA socket as

appropriate even though these signals do not go into the

PCM16C00. These signals can be considered to be sideband to the PCM16C00. The card design is free to use external decoding logic for common memory.

For an Ethernet LAN card that desires to have a FLASH

device, HADDR(16) may be used to fragment the Common

Memory space into 2 pieces. When HADDR(16) is zero (0),

the LAN SRAM buffers (up to 64-kbyte max) may be selected. When HADDR(16) is one (1), a 64-kbyte FLASH device

may be selected. This use of one address line does not

require an additional IC. If a FLASH device greater than 64k

is desired, minimal decoding logic would become necessary.

5.2 REGISTERS

5.2.1 PCMCIA Registers

The PCMCIA register’s context is for its respective function.

Each function (0,1) has its own set of Configuration Registers so that each function may be configured and operated

on independently from a programming model viewpoint.

CIS (CARD INFORMATION STRUCTURE)

[

0x000–0x03E2

]

When the PCM16C00 powers on, the contents of the lower

2.0/0.5-kbyte of the EEPROM are loaded into the device’s

shadow RAM. This not only allows attribute memory accesses to the CIS, but, it also provides defaults for 10

PCM16C00 specific registers to be loaded. This allows default loading of parameters that are transparent to system or

device software. The best use is for the card manufacturer

to determine what values these should be and program

them into the EEPROM when the CIS is programmed. Either

system software such as Card Services/Socket Services or

device software may read and parse the CIS by accessing

attribute memory on the PC Card. If desired, this software

agent may write to the CIS or default EEPROM registers

and, if desired, have these new values saved to the EEPROM. The actual contents of the CIS and the static registers is PC Card design dependent.

9

5.0 Functional Description (Continued)

5.2.2 PCM16C00 Specific Registers

These registers are defined specifically for National’s

PCM16C00 IC and are not part of the PCMCIA specification.

5.2.2.1 Standard Mode Register Set

These registers allow the PCM16C00 IC to perform its base

functionality of supporting two general functions on a PC

Card.

Pin Polarity Register

[

0x03E4

]

This register sets the polarity of the card side interface signals.

D7 D6 D5 D4 D3 D2 D1 D0

CIOWR CIORD SRESET1 SRESET0 BHE Memls8 CWAIT1 CWAIT0

CIOWR, CIORDÐSets the polarity of the CIOWRÝand

CIORD

Ý

pins respectively. A high indicates active high. The

default polarity is active-low.

SRESET1, SRESET0ÐSets the polarity of the SRESET(1)

and SRESET(0) pins respectively. When this bit is set to a

zero (0), the output signal is asserted in the high (1) state.

When this bit is set to a one (1), the output signal is asserted

in the low (0) state. The bit default is zero (0), i.e. the

SRESET( ) signal is active high.

BHEÐSets the polarity of the BHE

Ý

pin. A high indicates

active-high. The default polarity is active-low.

Memls8ÐThis bit is set to one (1) if common memory is

organized for 8-bit access. This bit is set to zero (0) if common memory is organized for 16-bit access. The default value is zero (0). This information allows the PCM16C00 to

properly access memory using the MEMWEH

Ý

,

MEMWEL

Ý

, and MEMOEÝsignals.

CWAIT1, CWAIT0ÐWhen this bit is set to one (1), the

PCM16C00 interprets this input signal active when it is low

(0). When this bit is set to zero (0), the PCM16C00 interprets

this input signal as active when it is high (1). The default bit

value is zero (0), i.e. the CWAIT( ) input signal is asserted

high (1).

PMGR and Clock Register

[

0x03E6

]

The Power Manager (PMGR) and Clock Register is used for

controlling the PCNTL(1:0) pins for either power management purposes or general purpose digital output only. Unlike

the Digital Port Register, there is no associated direction

register since only outputs are allowed.

Hardware power management is enabled using the Function Configuration Option Register’s Function Configuration

Index values. Its use is intended for functions that can be

sequenced on/off or into idle or sleep states with a quick

(

k

10 ms) response time when powered on again. That is,

the function may use its CWAIT( ) signal to extend a transaction that caused the PCM16C00 to turn it on. Use of the

READY( ) signal in a dynamic hardware power managed environment to set the RRdy/Bsy bits in order to achieve

l

10 m s response times for power on is not guaranteed to

work since system software may not inspect the RRdy/Bsy

bit in all such instances.

D7 D6 D5 D4 D3 D2 D1 D0

F1CLKEN DIV1 PPOL1 PCNTL(1) F0CLKEN DIV0 PPOL0 PCNTL(0)

F1CLKEN, F0CLKENÐIf set, these enable the pins

FCLK(1:0) to receive a clock out. If clear, the respective

pins FCLK(1:0) will be forced low. These are set and

cleared by software if desired or statically loaded upon card

power up from the EEPROM.

DIV1, DIV0ÐIf set, the respective clock output from

FCLK(1:0) will be divided by 32 from the input clocks

MCLK(1:0). If clear, the clock output FCLK(1:0) will equal

the respective clock input MCLK(1:0). These are set and

cleared by software if desired or statically loaded upon card

power up from the EEPROM.

PPOL1, PPOL0ÐSets the active polarity of the PCNTL(1)

and PCNTL(0) signals such that the function is asserted. If

PPOL is set to zero (0), PCNTL( ) is asserted when in the

high state. If set to one (1), PCNTL( ) is asserted when in

the low state. The default is set to zero (0), i.e. PCNTL( )

defaults to active high.

PCNTL(1), PCNTL(0)ÐThese bits control the pins

PCNTL(1) and PCNTL(0) respectively. If hardware power

management is not selected in the Function Configuration

Option Register’s Function Configuration Index, then these

bits may be used as output signals by software for general

purposes. If the hardware power management configuration

is selected, these bits are de-asserted (defined by PPOL1,

0) when the PCM16C00’s CTERM 1 or 0 counter expires.

These bits will be asserted if a transaction occurs to the

function through an I/O window, the function requests the

card-side bus using BREQ( ) or the function issues a RI

Ð

IN( ). In either strategy, software may always write and read

back these bits. These bits default to zero (0) during poweron until the PMGR and Clock Register can be loaded from

the EEPROM.

CTERM Registers 0, 1

[

0x03E8, 0x03EA

]

These registers are used to define the value of function 0’s

and function 1’s power time-out counters respectively. If a

function’s power time-out counter expires, the PCNTL bit for

that function in the PMGR and Clock Register is de-asserted. This will occur if a function is in-active long enough for

it’s power time-out counter to expire. Active is defined as

having either an I/O access from the host, receiving a

BREQ( ) or a RIÐIN( )

Ý

. Devices that may operate for long

periods of time without a host I/O access and that do not

use BREQ( ) should follow a software controlled power

management strategy that uses the PwrDn bits in the Function Configuration Status Registers 0, 1.

D7–D0

NeTime-Out Counter Terminal Count Value

Each function’s terminal counter is 8 bits wide and counts at

a rate of MCLK(0)/(2

17

). For example, if the MCLK(0) frequency is 30 MHz the device can be programmed to timeout between 0.0s to 1.114s. The general formula is:

Time

e

(1/mclk(0)) * 217* N,

where NeÀ0, 1, 2, . . . , 255

Ó

For a 5 MHz MCLK(0) frequency, the equation is:

Time

e

N (26.2144 ms) where NeÀ0,1,2, . . . ,255

Ó

Note: A value of zero implies the function is powered down.

10

5.0 Functional Description (Continued)

Arbiter Priority Register

[

0x03EC

]

This register controls the priority (from the set

À

00,01,10,11Ó) for each possible card-bus master from the

set

À

PCMCIA Host, Function 0, Function 1Ó. The value of

À3Ó

is the highest priority whereasÀ0Óis the lowest priority.

D7 D6 D5–D4 D3–D2 D1–D0

ArbiterCLK PreemptEnb PCMCIA Host Function 1 Function 0

Priority Priority Priority

ArbiterCLKÐThis bit is set to one (1) to increment the Arbiter Latency Register using MCLK(0)/16. This bit is set to

zero (0) to increment the Arbiter Latency Register using

MCLK(0)/1.

PreemptEnbÐIf this bit is set to one (1), the arbiter will

allow pre-emption of bus masters. If this bit is set to zero (0),

the arbiter will allow a bus master to complete before granting the bus to another master as determined by the priority

scheme used.

Arbiter Latency Register

[

0x03EE

]

This register programs a latency timer such that when a

card-bus master is in control of the bus and another unit

requests and wins access to the bus (following priority

scheme), the timer will allow the current bus owner to retain

the bus until the timer expires. This is useful when pre-emptions are allowed using the PreemptEnb bit in the Arbiter

Priority Register. The timer does not start counting down

until the arbiter queues another device for bus ownership.

D7-D0

NeArbiter Latency Timer Value

Arbiter Latency Timer Value (N)ÐThis value is used by an

arbiter counter. Therefore, the latency time until the

BREQ( ) is relinquished (or internal host BREQ) when

PreemptEnb is set to one (1) is:

Latency Time

e

16(N)/f

MCLK(0)

when ArbiterCLKe(1)

Latency Time

e

(N)/f

MCLK(0)

when ArbiterCLKe(0)

Miscellaneous Register

[

0x03F0

]

D7 D6 D5 D4– D0

FastEE LAÐTRIÐFunc1 LAÐTRIÐFunc0 EEPROMStartAddr

FastEEÐIf this bit is set to one (1), then the clock used to

access the EEPROM shall be MCLK(0)/2. If this bit is set to

zero (0), the clock used to access the EEPROM shall be

MCLK(0)/32.

LAÐTRIÐFunc1, LAÐTRIÐFunc0ÐThis bit should be

set to one (1) when a bus master function will multiplex

address and data on the LDATA( ) bus and will use ADS to

strobe the address phase on this bus to the LADDR( ) bus.

In this case, the PCM16C00 will drive the LADDR( ) bus and

latch the LDATA( ) bus to the LADDR( ) bus on an ADS

strobe. This bit should be set to a zero (0) when a bus

master function will drive the LADDR( ) bus directly. In this

case, the PCM16C00 will TRI-STATE (not drive) the

LADDR( ) bus when it is granted to function 0 or function 1

in expectation that the function will control the LADDR( )

bus.

EEPROMStartAddrÐThis field contains a starting address

for EEPROM read or write access. This is ordinarily set to

zero and is used for debug/test purposes.

Digital Port Direction Register

[

0x03F2

]

This register is a read/write register that controls the direction for each individual bit in the Digital Port Register.

D7–D4D3D2D1D0

Reserved DPDIR3 DPDIR2 DPDIR1 DPDIR0

DPDIR3,2,1,0ÐDPDIRi defines the direction of the corresponding DPORT(i) pin and, hence, the direction of the

DPORTi bit in the Digital Port Register. If DPDIRi is set to

zero (0)(default), then the DPORT(i) pin is a digital input. If

DPDIRi is set to one (1), then the DPORT(i) pin is a digital

output.

Digital Port Register

[

0x03F4

]

The Digital Port Register is a read/write register connected

to the DPORT(3:0) pins of the PCM16C00 chip. Each bit is

direction programmable through software using the Digital

Port Direction Register.

D7–D4D3D2D1D0

Reserved DPORT3 DPORT2 DPORT1 DPORT0

DPORT3,2,1,0ÐIf DPDIR is set to one (1) then DPORT may

be written to. The value written will be sourced by the corresponding DPORT pin. When DPORT is read, the value returned will be the last value written to DPORT. If DPDIR is

reset to zero (0) then DPORT will assume the value externally driven into the corresponding DPORT pin. Therefore,

when DPORT is read, it returns the value being driven into

the DPORT pin. When written, the value is unaffected and

retains the value driven on DPORT.

Wait State Timer Register

[

0x03F6

]

This register allows the insertion of default wait states from

the PCM16C00 using HWAIT

Ý

. It is intended to be used in

situations where either the function is too slow to respond

with a CWAIT( ) or the unique wait timing constraints between the system and PC Card design necessitate a default

wait state.

D7–D4 D3–D2 D1–D0

Reserved Func1Wait Func0Wait

Func1Wait, Func0WaitÐThis value is the number (0, 1, 2,

or 3) of MCLK(0) time periods that the PCM16C00 will assert HWAIT

Ý

during a valid access to a particular function.

For Zero wait states, program these values to 00b.

ID Register

[

0x1000

]

This read only register provides the software with IC revision

information.

D7–D3 D2–D0

PCM16C00 Codee00000b Revision Codee000b

National PCM16C00 CodeÐThis code may be used to

identify the PCM16C00 IC. The value of this register is

00000b.

Revision CodeÐThis will uniquely identify the silicon version of the PCM16C00 IC as 000b.

11

5.0 Functional Description (Continued)

EEPROM Control Register

[

0x1002

]

This register controls reading and writing the EEPROM as

well as the EEPROM enable.

D7 D6 D5– D1 D0

WriteEEPROM ReadEEPROM Reserved Enable EEPROM

WriteEEPROMÐWhen set, this tells the EEPROM controller to copy the contents of the PCM16C00 Shadow RAM to

the EEPROM. Once done, the EEPROM controller clears

this bit.

ReadEEPROMÐWhen set, this tells the EEPROM controller to copy the contents of the EEPROM to the shadow

RAM. Once done, the EEPROM controller clears this bit.

Any data modified in the Shadow RAM that has not first

been written back to the EEPROM will be lost.

Enable EEPROMÐThis must be set to allow EEPROM

writes. If clear, the EEPROM may not be written. The default

value at reset is low. The EEPROM may be read independent of the value of this bit.

Note 1: Upon power-up, the Cobra EEPROM controller copies the entire

contents of the EEPROM (size dependent) into the Shadow RAM.

Note 2: The PCM16C00 EEPROM controller stores data in a 16-bit orga-

nized EEPROM in low/high format. Although Attribute Memory is

on even byte boundaries only, the entire EEPROM’s address space

is used. This eliminates waste of EEPROM memory. Therefore the

Attribute space used by the Shadow RAM is double the actual size

of the EEPROM. For example, if a 16-bit EEPROM is pre-programmed, the low byte at word 0 in the EEPROM will be shadowed

at Attribute location 0x0000 and the high byte will be shadowed at

Attribute location 0x0002. The low byte at EEPROM word 1 will be

shadowed to Attribute location 0x0004, etc. For EEPROM organizations of 8 bits, EEPROM byte 0 will be shadowed to Attribute location 0x0000 and byte 1 will be shadowed to Attribute location

0x0002.

Function Configuration Option Registers 0,1

[

0x1020,0x1040

]

D7 D6 D5– D0

SRESET LevIREQ Function Configuration Index

SRESETÐIf the host sets this field to one (1), the

PCM16C00 shall place the given function in the reset state.

When the host returns this field to zero (0), the function

shall enter the same unconfigured, reset state as it does

following a power-up and hardware reset.

LevIREQÐWhen the PCM16C00 is being used as a

PCMCIA I/O interface and this field is set to one (1), the

PCM16C00 shall generate Level Mode interrupts for the

function using the IREQ

Ý

signal. If the PCM16C00 is being

used as a PCMCIA I/O interface and this field is set to zero

(0), the PCM16C00 shall generate Pulse Mode interrupts for

the function. Use of Level Mode interrupts for both functions

when the PCM16C00 is configured for multi-function operation is strongly recommended. Since there is only one

PCMCIA Bus interface, the LevIREQ bits for Function 0

Configuration Option Register and Function 1 Configuration

Option Register are aliased. The PCM16C00 will also only

allow a write to the LevIREQ bit value to change the interfaces Interrupt level mode if the given function is configured

using ConfFunc and interrupts are enabled using EnbIREQ.

In addition, the PCM16C00 provides an enhanced interrupt

protocol scheme described by the IntrReset bit in the Function Configuration Status Registers 0, 1. The PCM16C00

implements a shared interrupt scheme in multi-function operation. Single function configurations may use Level Mode

or Pulse Mode interrupt schemes. Pulsed Mode interrupt

width is given by:

TwidthIREQ

e

16/(FreqMCLK(0))

Using MCLK(0) from 5 MHz–30 MHz will insure pulse widths

from 0.53 ms –3.2 ms which exceed the 0.5 ms minimum

requirement for PCMCIA.

Function Configuration IndexÐWhen the host system

sets this field to the value of the Configuration Entry Number

field of a Configuration Table Entry Tuple, the function shall

enter the configuration described by that tuple. This field

shall be reset to zero (0) by the PCM16C00 when the host

sets the SRESET field to one (1) or the host asserts

RESET. If this field is set to zero (0) explicitly by the host or

implicitly by SRESET or RESET, the function shall use the

Memory Only interface and I/O cycles from the host shall

be ignored by the function.

The following configurations are supported by the Function

Configuration Index 0, 1:

ConfFunc (D0)ÐIf this is set to one (1), then the Card is

configured for that function.

EnbBaseÐLimit (D1)ÐIf this is set to a one (1), the base

and limit register pair for the function is enabled. That is, the

PCM16C00 will only pass I/O transactions whose address

falls within the I/O window specified by the base and limit

pair. If this is set to a zero (0), the PCM16C00 will not test

transactions’ addresses against the base and limit pair for

that function and will, therefore, pass all I/O transactions to

the function. For single function operation, the EnbBase

Ð

Limit would be enabled for operation with host controllers

that support overlapping windowing and the INPACK

Ý

sig-

nal. For host controllers that do not support INPACK

Ý

but

are capable of windowing granularity required for the function, EnbBaseÐLimit may be set to zero (0) so that all I/O

transactions are passed to the function. For multifunction

operation, the EnbBaseÐLimit bits for both functions

should be set to one (1).

EnbIREQ (D2)ÐWhen the PCM16C00 is being used as a

PCMCIA I/O interface and this field is set to one (1), the

PCM16C00 shall enable this function to interrupt the host

using the IREQ

Ý

signal. Normally this bit would be set to

one (1). In environments where the function’s software driver will use a polling technique for status information, this bit

could be set to zero (0) to disable interrupts from that function.

PMGMTÐEN (D3)ÐThis bit, if set to a one (1), enables the

hardware power management controller to control the

PCNTL( ) pin for that function. See the PMGR and Clock

Register description.

LAN Mode (D4 for Function 0 Configuration Option Register only)ÐWhen this bit is set to a one (1), the Function 0

interface on the PCM16C00 will fully support National’s

DP83902AVJG Ethernet LAN IC. Function 0 is said to be in

LAN Mode.

12

Loading...

Loading...