NSC PC97338VJG Datasheet

PC87338 /PC97338

ACPI 1.0 and PC98/9 9 Co mp l iant Sup erI/O

PC87338/PC97338 ACPI 1.0 and PC98/99 Compliant SuperI/O

November 1998

General D escription

The PC97338 is a fully ACPI 1.0 and PC98/99 c ompliant, ISA based Super I/O. It is functionally compatible with the PC87338. It includes a Floppy Disk

Controller (FDC), two Serial Communication Con trollers (SCC) for UART and Infrared support, one

IEEE1284 compatible Parallel Port, and two g eneral

purpose Chip Select signals for game port support.

The device supports powe r management as well as

3.3V and 5V mixed operation making it particularly

suitable for notebook and sub-notebook applications.

The PC87338 and PC97338 are fully compliant to the

Plug and Play specifications included in the "Hardware Design Guide for Microsoft Windows 95".

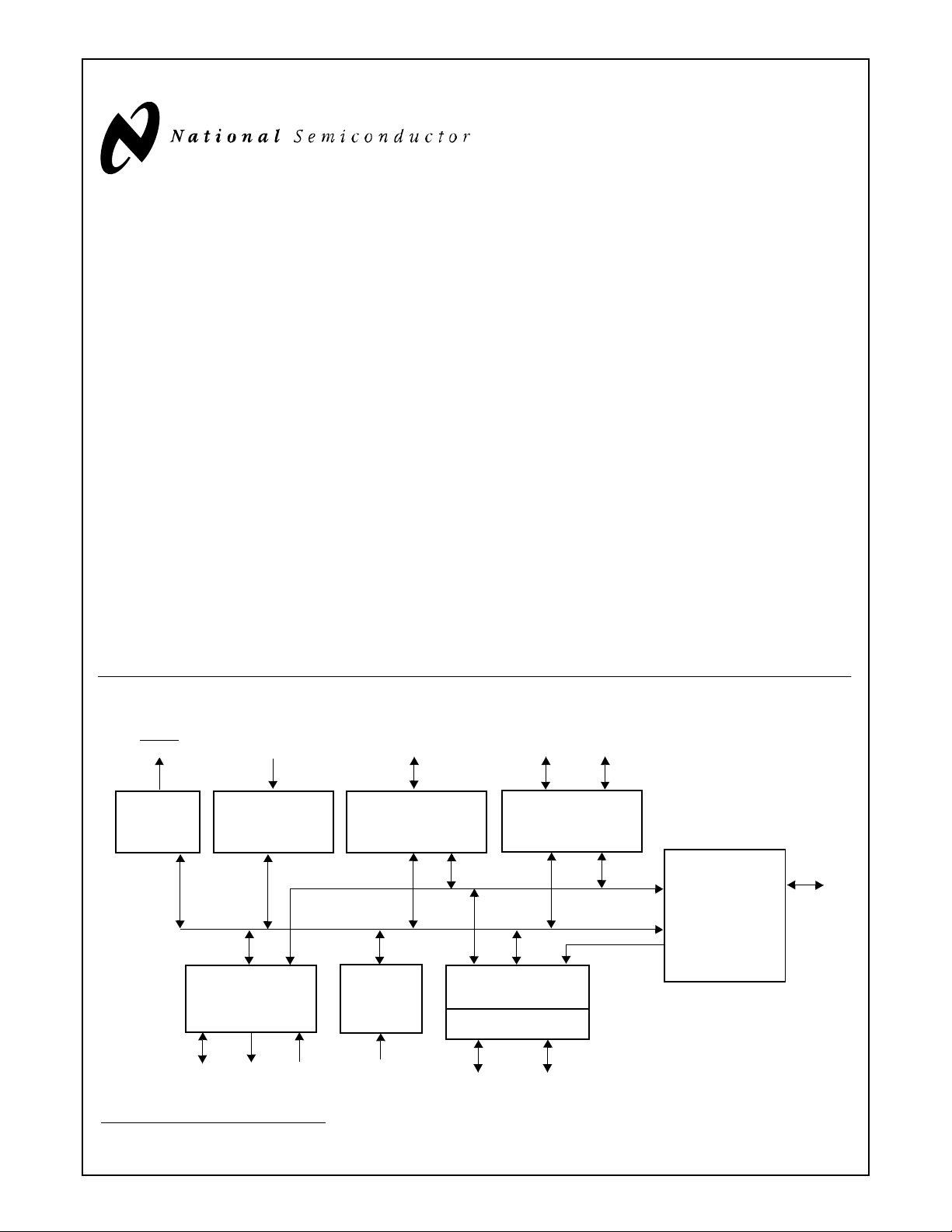

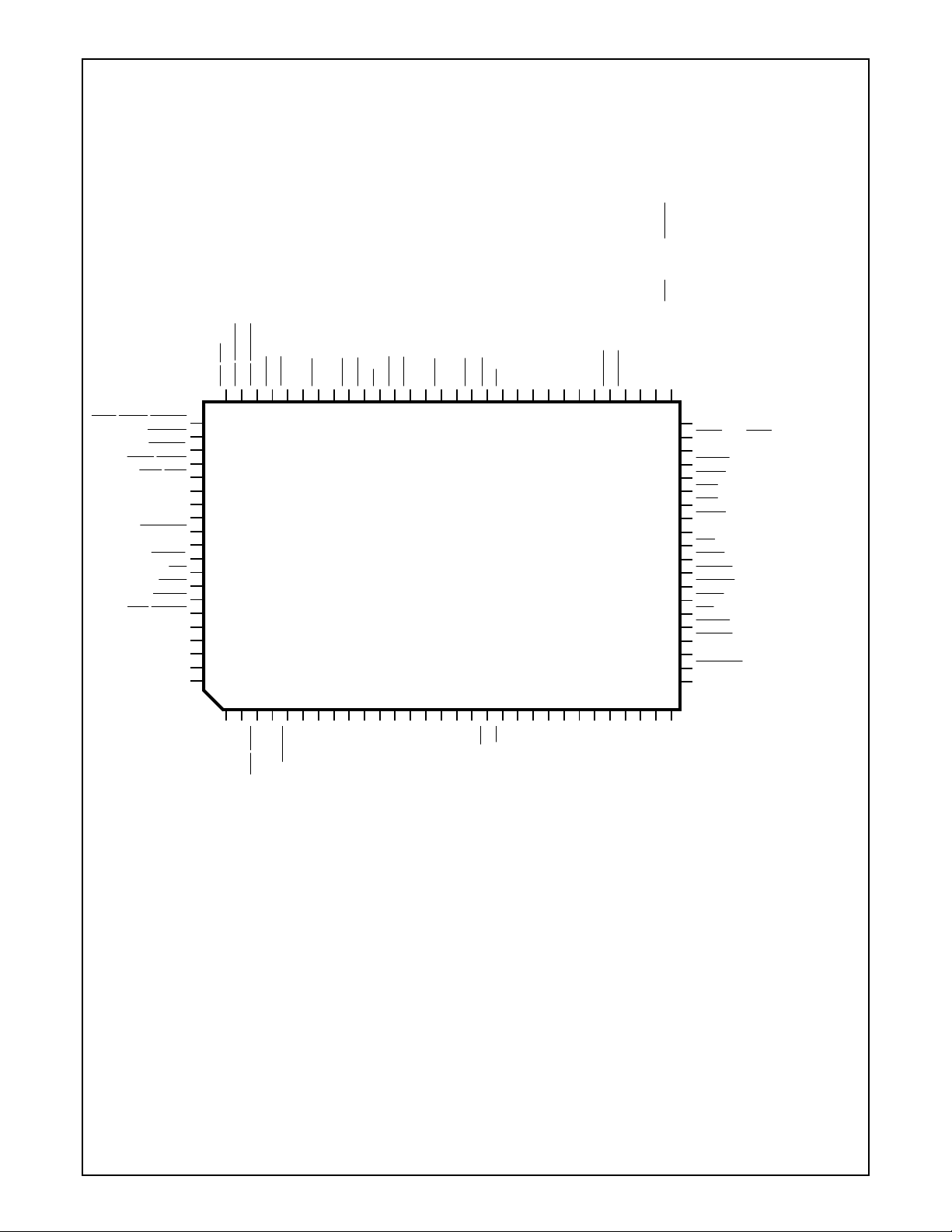

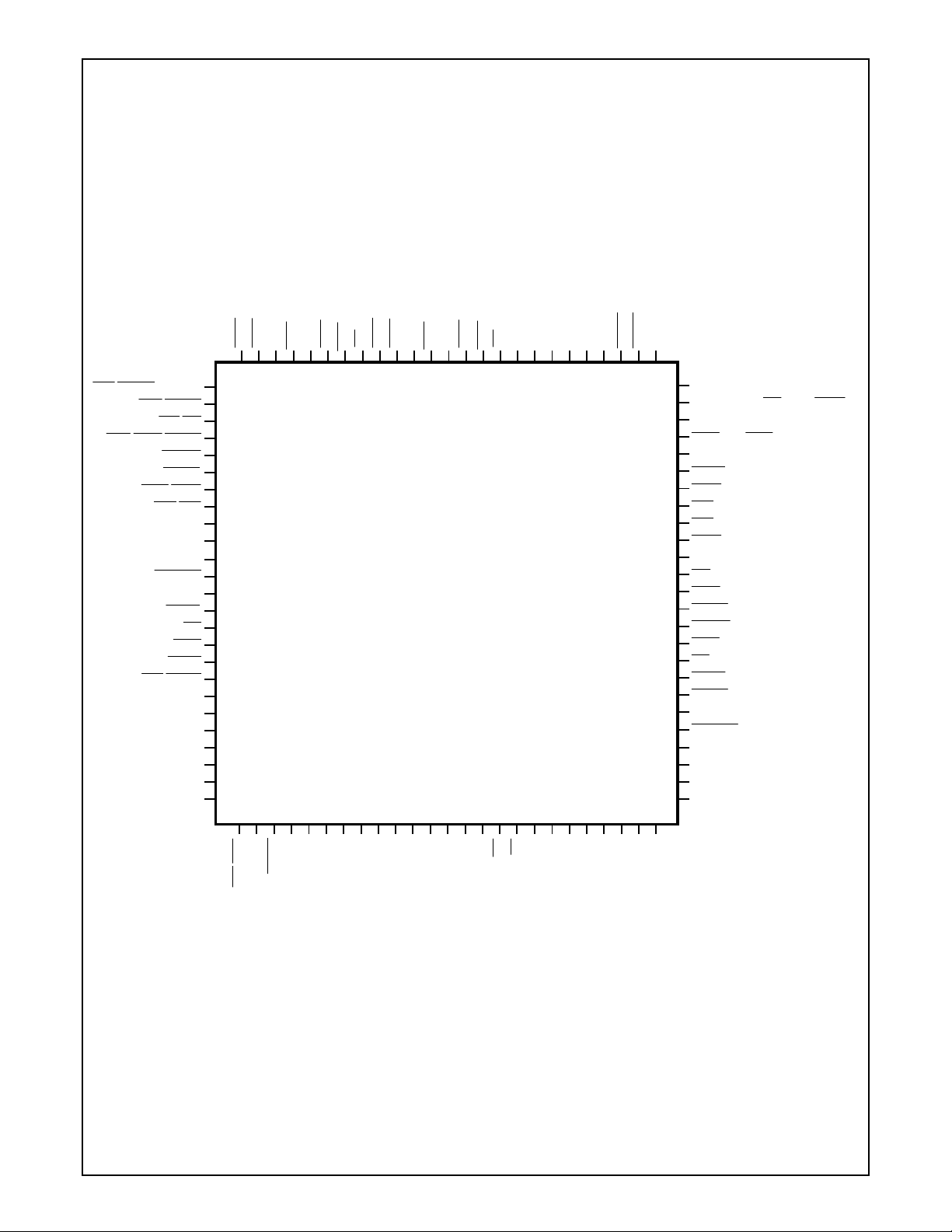

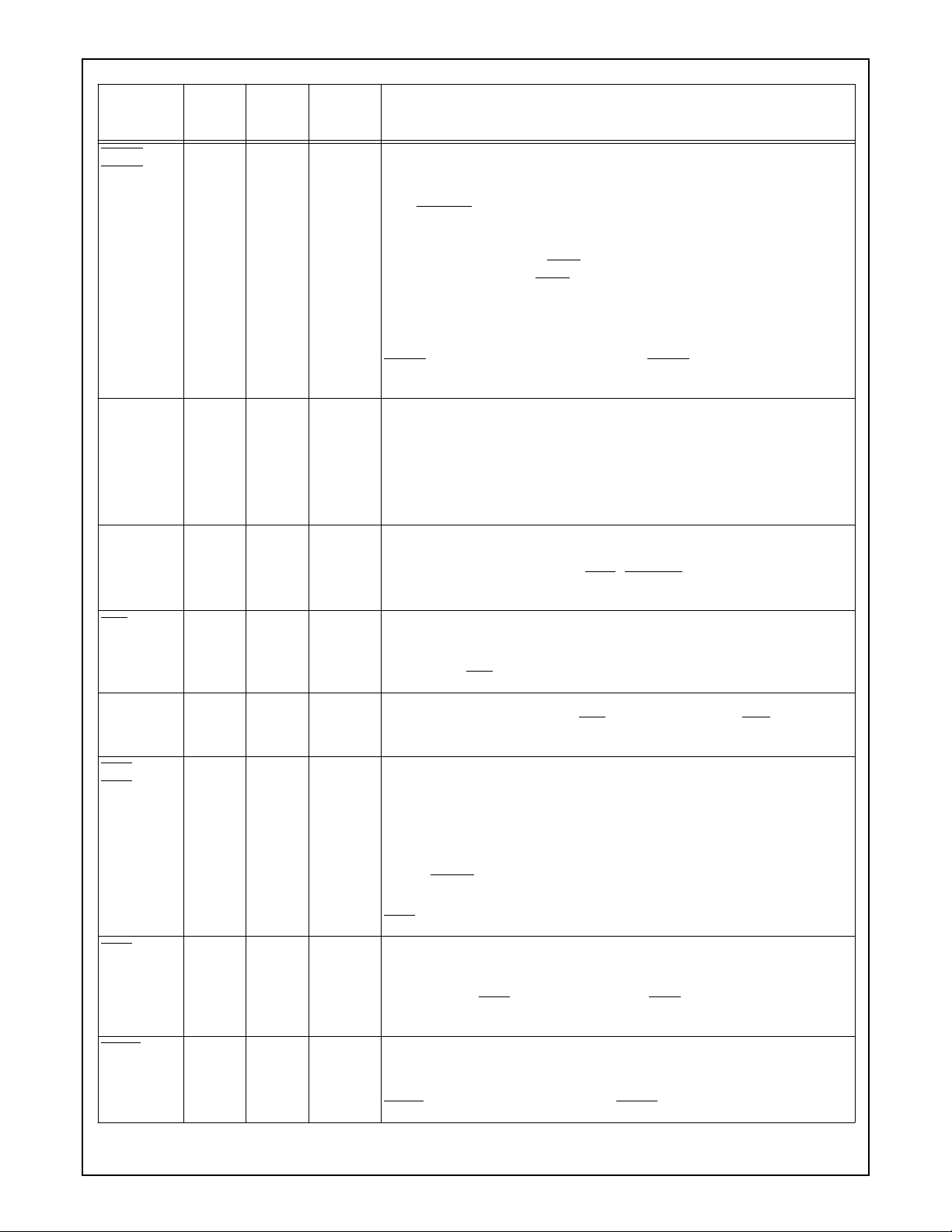

Block Diagram

Configuration Input

CS1,0

Signals

Serial Interfac e

Differences between the PC873 38 and PC97338 are

indicated in italics. These differences are summarized

in Appendix A.

Features

■ Meets ACPI 1.0 and PC98/99 requirements

■ Backward compatible with PC87338

■ 100% compatibility with Plug and Play require-

ments specified in the “

Microsoft Windows 95

Channel architectures

■ A special Plug and Play module includes:

Flexible IRQs, DMAs and base addresses

—

General Interrupt Requests (IRQs) that can be

—

multiplexed to the ten supported IRQs

Serial

Interface

Fast IR

Interface

Hardware Design Guide for

”, ISA, EISA, and Micro-

General

Chip Select

Microprocessor

Address

Data and

Control

©

1998 National Semiconductor Corporation

Channels

TRI-STATE® is a registered trademark of National Semiconductor Corporation.

®

IBM

, MicroChannel®, PC-AT® and PS/2® are registered trademarks of International Business Machines Corporation.

®

Microsoft

and Windows® are registered trademarks of Microsoft Corporation.

Configuration

Plug and Play

Support

DMA

IRQ

Registers

IRQ Input

Signals

SCC1

(16550 UART)

Interrupt

and DMA

Power-

Down

Logic

Control

SCC2

(16550 UART +

INFRARED)

IEEE1284

Parallel Port

High Current Driver

Data Handshake

1

Floppy

Drive

Interface

Floppy Disk

Control ler (FDC)

with

Digital Data

Separator (DDS)

(Enhanced 8477)

www.national.com

Floppy

Drive

Interface

■ A new, high performance, on-chip Floppy Disk

Controller (FDC) provides:

— Software compatibility with the PC8477, which

contains a superset of the floppy disk controller

functions in the µDP8473, the NEC µP D 765A

and the N82077

— A modifiable 13-bit address

— Ten IRQ channel options

— Four 8-bit DMA channel options

— 16-byte FIFO

— Burst and non-burst modes

— Low-power CMOS with enhanced power-down

mode

— A new, high-performance, on-chip, digital data

separator without external filter components

— Support for 5.25"/3.5" floppy disk drives

— Automatic media sense support

— Perpendicular recording drive support

— Three mode Floppy Disk Drive (FDD) support

— Full support for IBM’s Tape Drive Register

(TDR) implementation

— Support for new fast tape drives (2 Mbps) and

standard tape drives (1 Mbps, 500 Kbps and

250 Kbps)

— Support for both

FM

and MFM modes

.

■ Two Serial Communication Controllers provide:

— Software compatibility with the 16550A and the

16450

— A modifiable 13-bit address

— Ten IRQ channel options

— MIDI baud rate support

— Four 8-bit DMA channel options on SCC2

— Shadow register support UART write-only bits

■ A fast universal Infrared interface on SCC2 supports the following:

— Data rates of up to 115.2 Kbps (SIR)

— A data rate of 1.152 Mbps (MIR)

— A data rate of 4.0 Mbps (FIR)

— Selectable internal or external modulation /de-

modulation (Shar p-IR)

— Consumer Electronic IR mode

■ A bidirectional parallel port that includes:

— A modifiable 13-bit address

— Ten IRQ channel options

— Four 8-bit DMA channel options

— An Enhanced Parallel Port (EPP) compatible

with version EPP 1.9 (IEEE1284 compliant),

that also supports version EPP 1.7 of the Xircom specification.

— An Extended Capabilities Port (ECP) that is

IEEE1284 compliant, including level 2

— Bidirectional data transfer under either soft-

ware or hardware control

— Compatib ility with ISA, EISA , and M icroChan-

nel parallel ports

— Multiplexing of additional external FDC signals

on parallel port pins that enables use of an external Floppy Disk Drive (FDD)

— A protection circuit that prevents damage to the

parallel port when an external printer powers

up or operates at high voltages

— 14 mA output drivers

■ Two general purpose pins for two programm able

chip select signals can be program med for game

port control.

■ An address decoder that:

— Selects all primary and secondary ISA ad-

dresses, including COM1-4 and LPT1-3

— Decodes up to 16 address bits

■ Clock source:

— An internal clock multiplier generates all re-

quired internal frequencies.

— A clock input source 14.318 M Hz, 24 MHz, or

48 MHz may be selected

■ Enhanced power managem ent features:

— Special power-down configuration registers

— Enhanced programmable FDC command to

trigger power down

— Programmable power-down and wake-up

modes

— Two dedicated pins for FDC power manage-

ment

— Low power-down current consumption (typical-

ly for PC97338, 400 µA for 3.3V and 600 µA for

5V application)

— Reduced pin leakage current

— Low power CMOS technology

— The ability to shut off clocks to either the entire

chip or only to specific modules

■ Mixed voltage support provides:

— Standard 5 V operation

— Low voltage 3.3 V operation

— Simultaneous internal 3.3 V operation and re-

ception or transmission to devices that have either 3.3 V or 5 V power supply

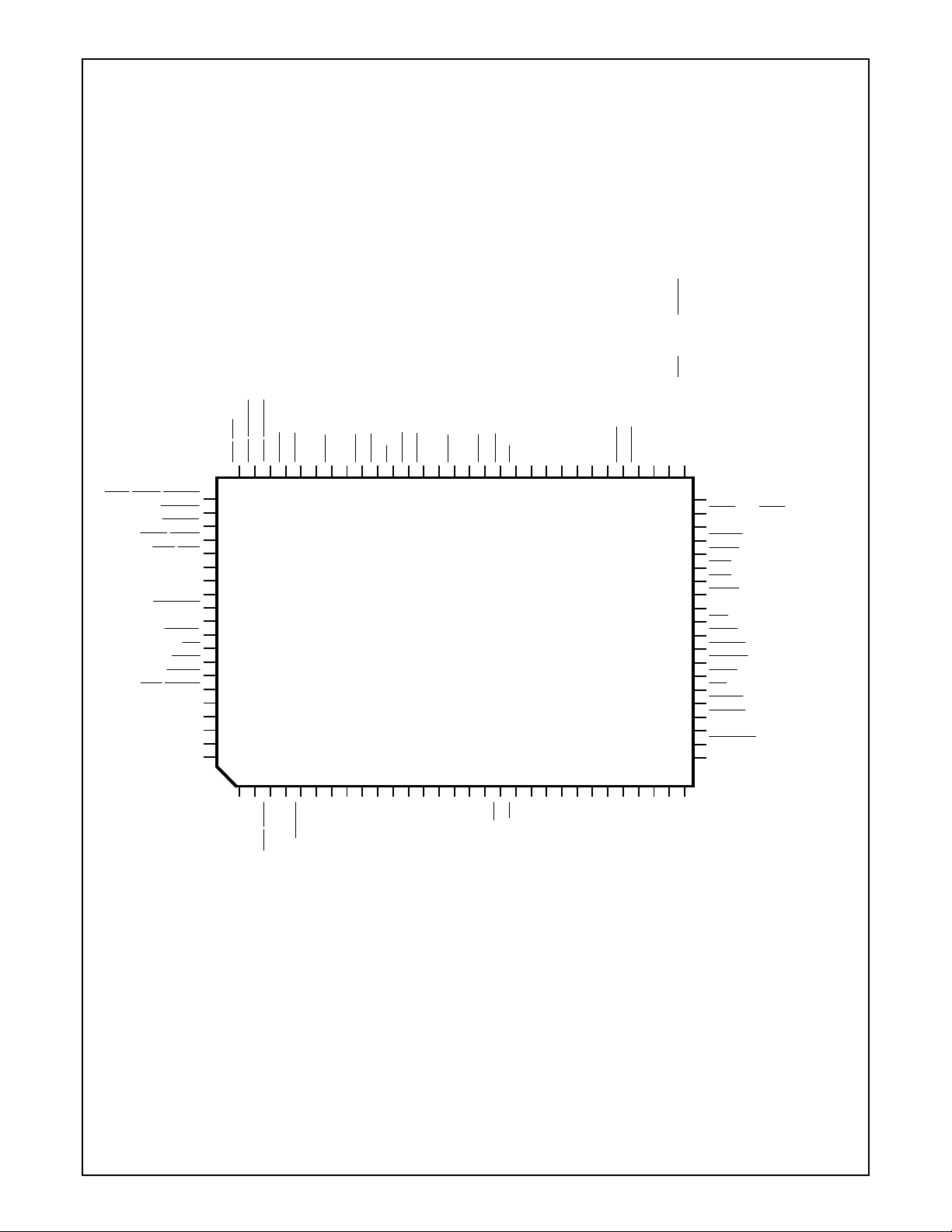

■ 100-pin TQFP VJG package - PC87338/PC97338

■ 100-pin PQFP VLJ package - PC87338/PC 97338

2

www.national.com

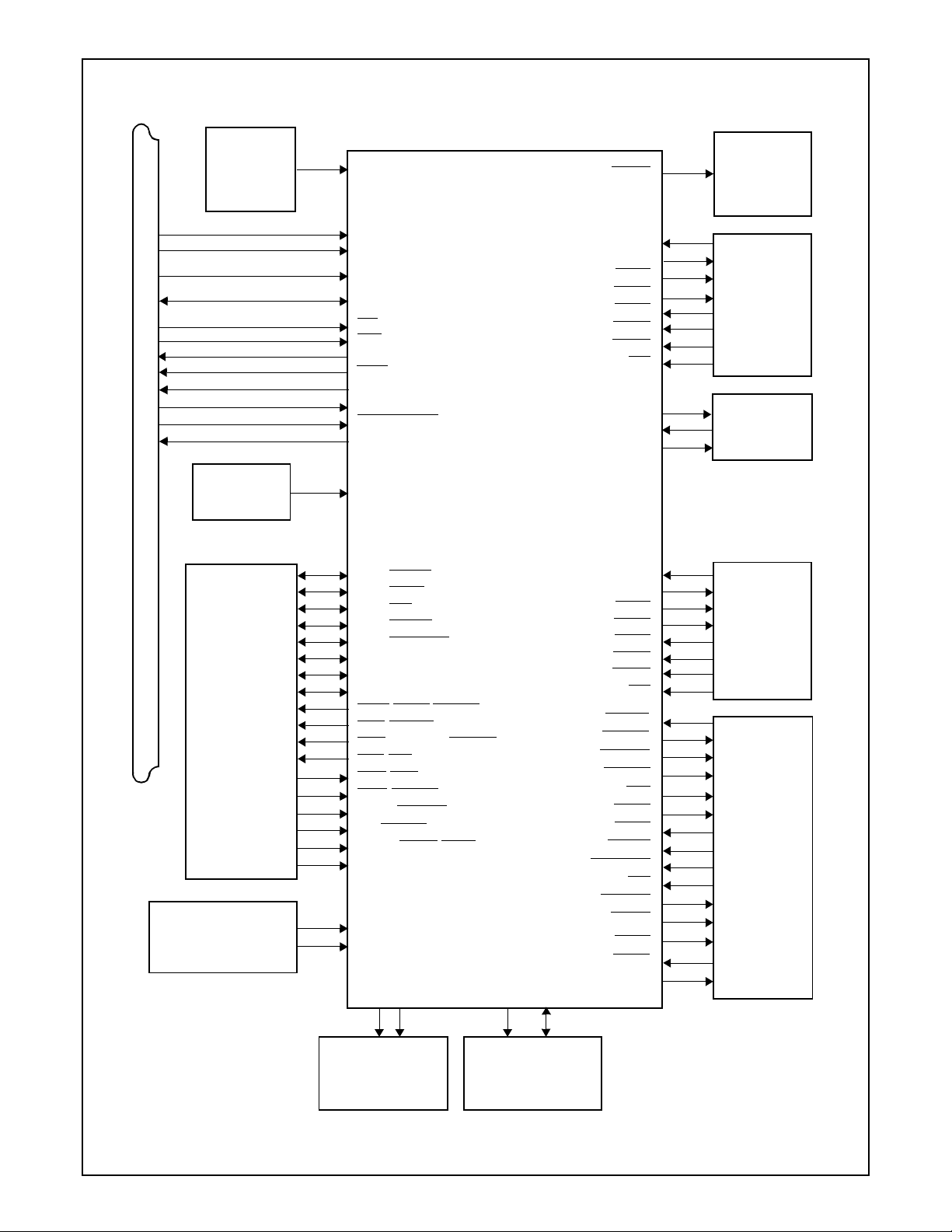

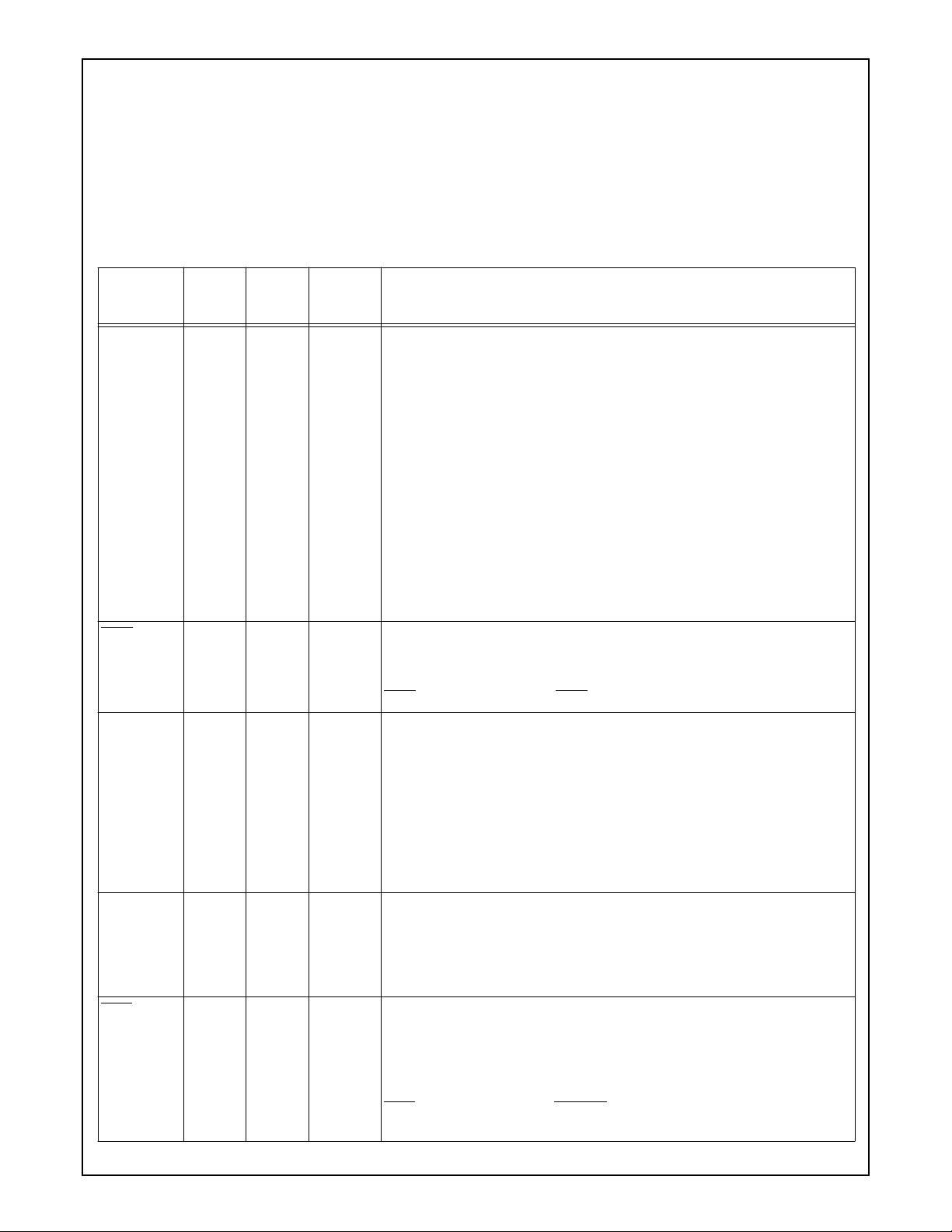

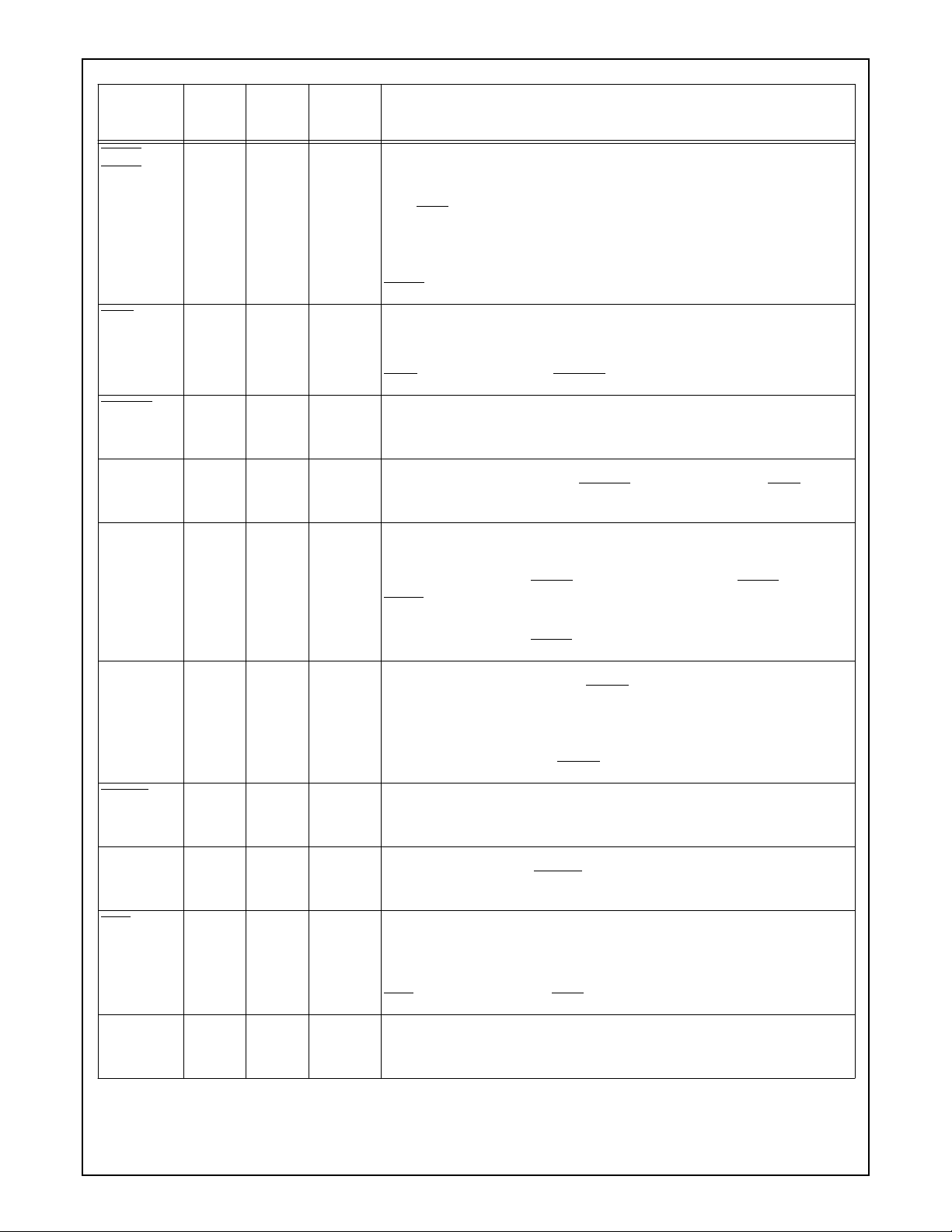

Basic Configuration

Clock

External

ISA Bus

Device

Parallel

Port

Connector

Configuration

Selectio n Logic

X1(CLKIN)

MR

AEN

A0-A15

D0-D7

RD

WR

IOCHRDY

ZWS

IRQ3-7, 9-12, 15

TC

DACK0,1,2,3

DRQ0,1,2,3

SIRQI1,2,3

PC87338VLJ

PC87338VJG

Super I/O

PD0/INDEX

PD1/TRK0

PD2/WP

PD3/RDATA

PD4/DSKCHG

PD5/MSEN0

PD6/DRATE0

PD7/MSEN1

SLIN

/STEP/ASTRB

STB/WRITE

AFD/DENSEL/DSTRB

INIT/DIR

ACK/DR1

ERR/HDSEL

SLCT/WGATE

PE/WDATA

BUSY/MTR1/WAIT

PNF

BADDR0,1

CFG0

IDLE

PD

BOUT1/SOUT1

BOUT2/SOUT2

DRATE0,1/MSEN0,1

ADRATE0,1

CS0,1

SIN1

RTS1

DTR1

CTS1

DSR1

DCD1

RI1

IRTX

IRRX1,2

IRSL0-2

SIN2

RTS2

DTR2

CTS2

DSR2

DCD2

RI2

RDATA

WDATA

WGATE

HDSEL

DIR

STEP

TRK0

INDEX

DSKCHG

WP

IDLE/MTR0,1

DR0,1

DR23

DRV2

DENSEL

Game

Port

EIA

Drivers

IR

Interface

EIA

Drivers

FDC

Connector

External

Power Dow n

Control

FDC

Configuration

Logic

3

www.national.com

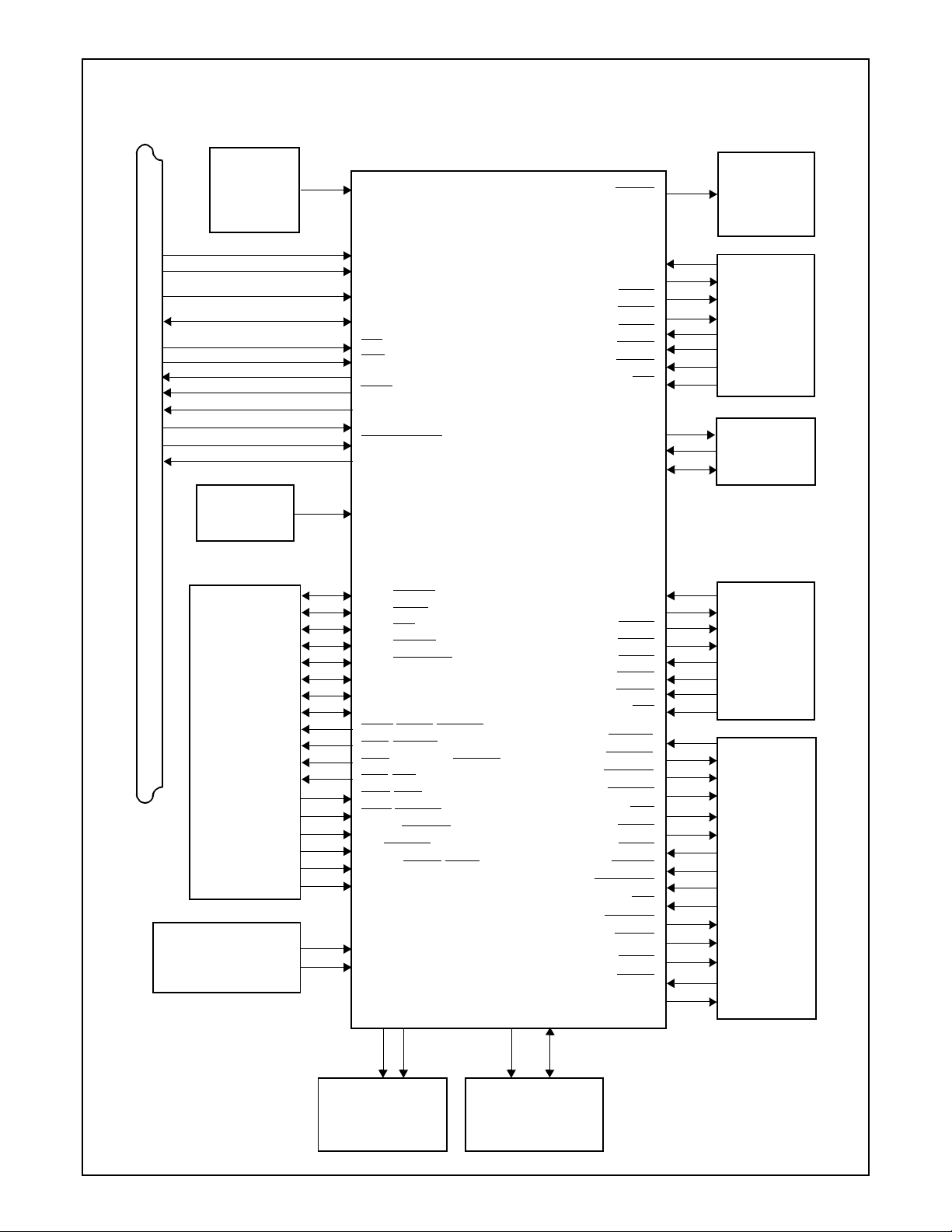

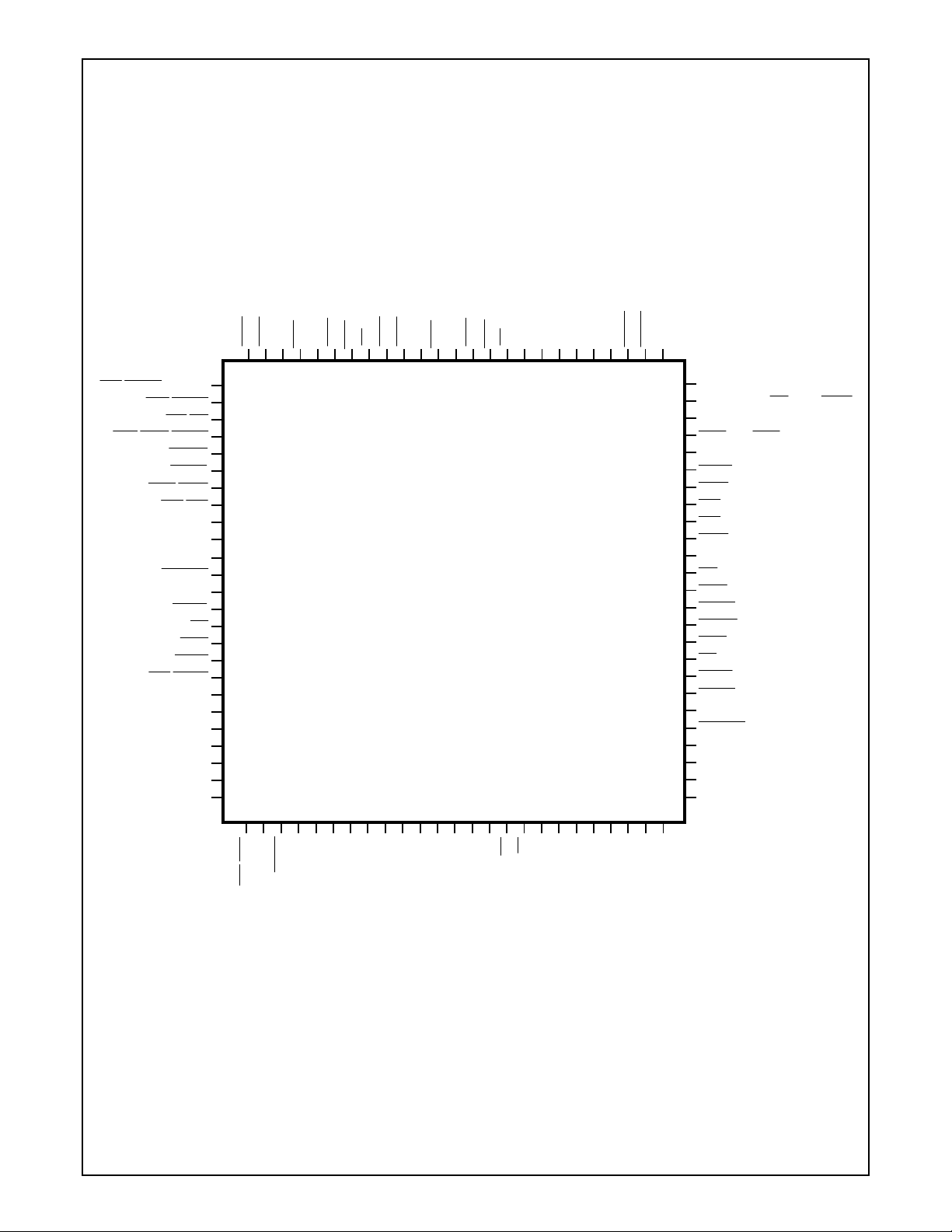

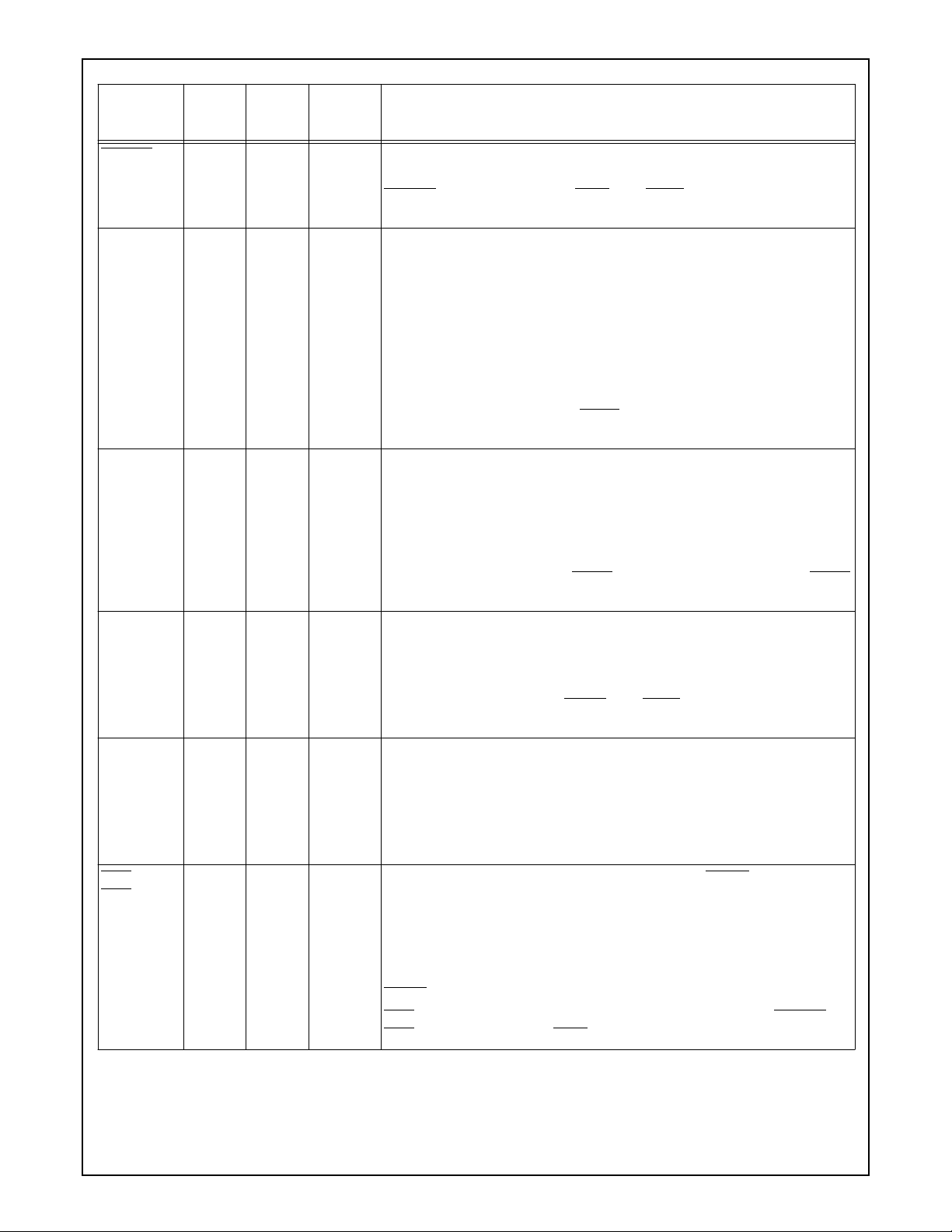

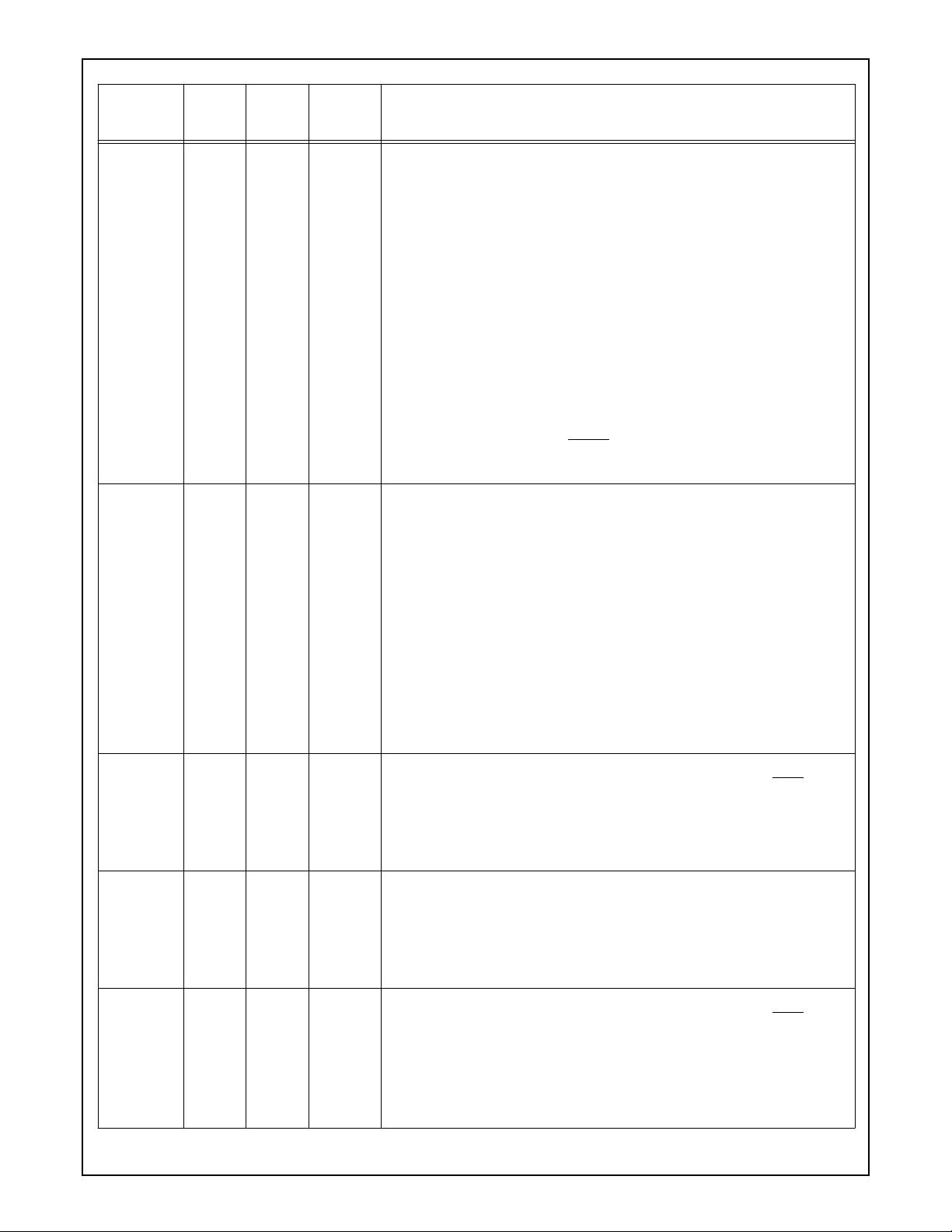

Basic Configuration

Clock

External

ISA Bus

Device

Parallel

Port

Connector

Configuration

Selectio n Logic

X1(CLKIN)

MR

AEN

A0-A15

D0-D7

RD

WR

IOCHRDY

ZWS

IRQ3-7, 9-12, 15

TC

DACK0,1,2,3

DRQ0,1,2,3

SIRQI1,2,3

PC97338VLJ

PC97338VJG

Super I/O

PD0/INDEX

PD1/TRK0

PD2/WP

PD3/RDATA

PD4/DSKCHG

PD5/MSEN0

PD6/DRATE0

PD7/MSEN1

SLIN

/STEP/ASTRB

STB/WRITE

AFD/DENSEL/DSTRB

INIT/DIR

ACK/DR1

ERR/HDSEL

SLCT/WGATE

PE/WDATA

BUSY/MTR1/WAIT

PNF

BADDR0,1

CFG0

IDLE

PD

CS0,1

SIN1

SOUT1

RTS1

BOUT1/DTR1

CTS1

DSR1

DCD1

RI1

IRTX

IRRX1,2

IRSL0-2/ID0-2

SIN2

SOUT2

RTS2

BOUT2/DTR2

CTS2

DSR2

DCD2

RI2

RDATA

WDATA

WGATE

HDSEL

DIR

STEP

TRK0

INDEX

DSKCHG

WP

IDLE/MTR0,1

DR0,1

DR23

DRV2

DENSEL

DRATE0,1/MSEN0,1

ADRATE0,1

Port

EIA

Drivers

IR

Interface

EIA

Drivers

FDC

Connec t or

Game

Exter n al

Power Down

Control

FDC

Configuration

Logic

4

www.national.com

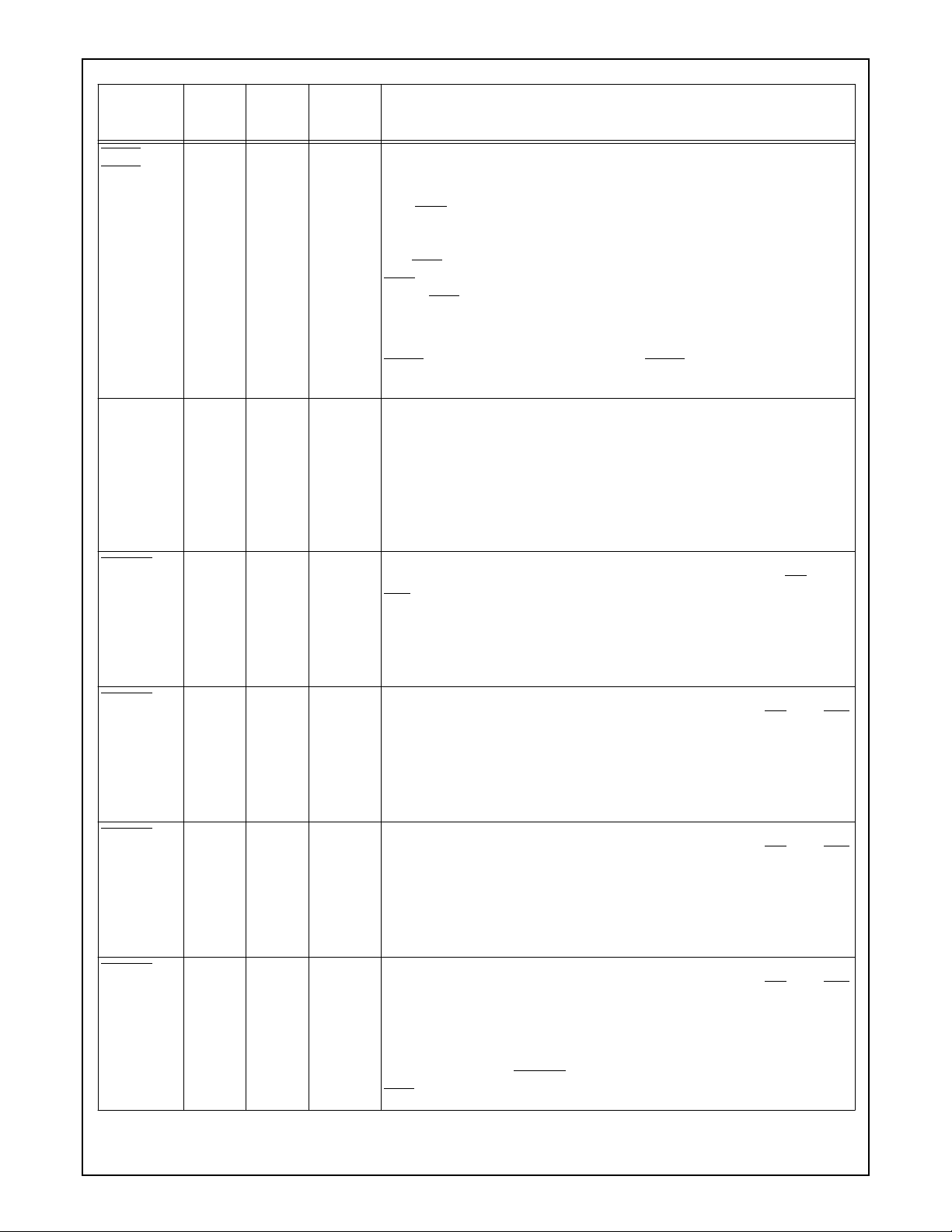

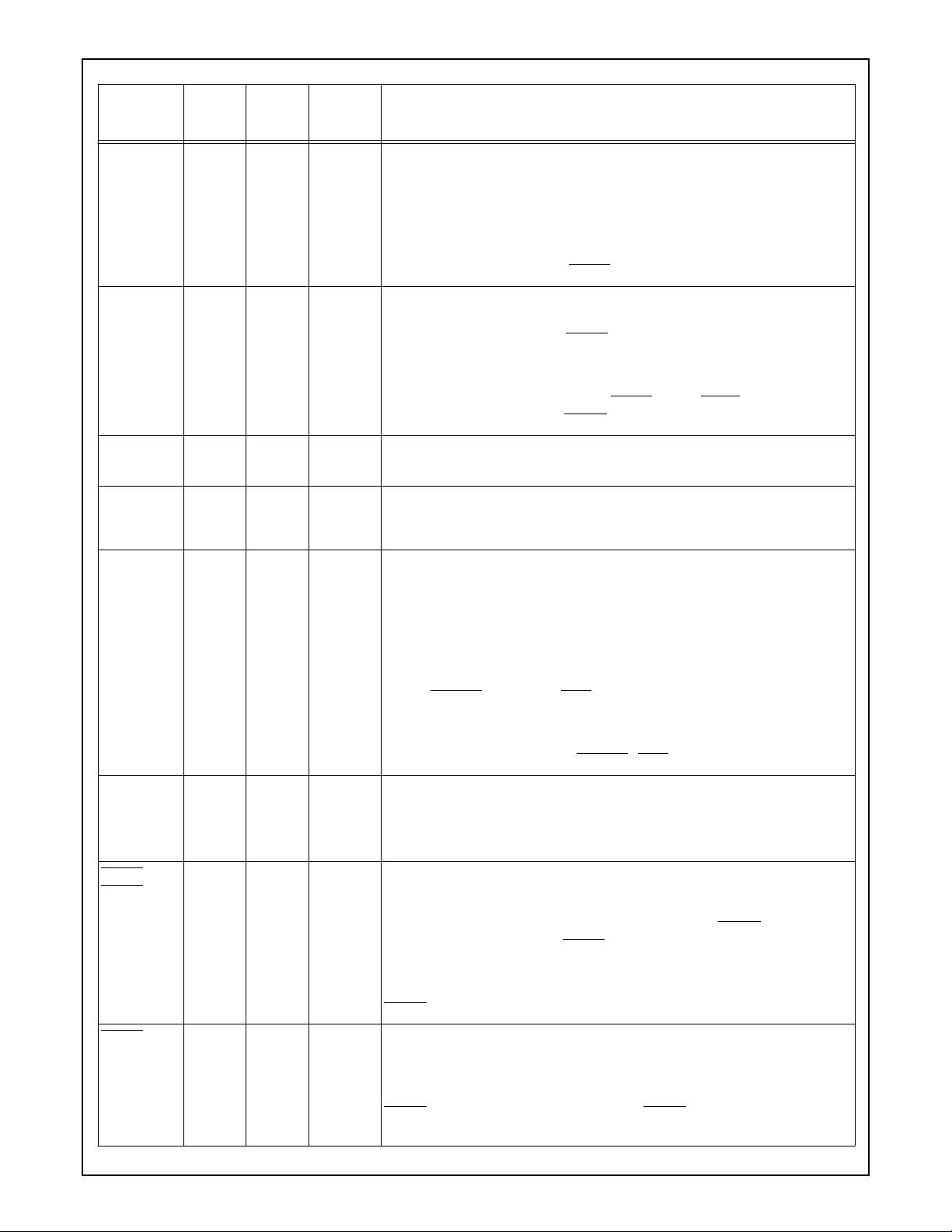

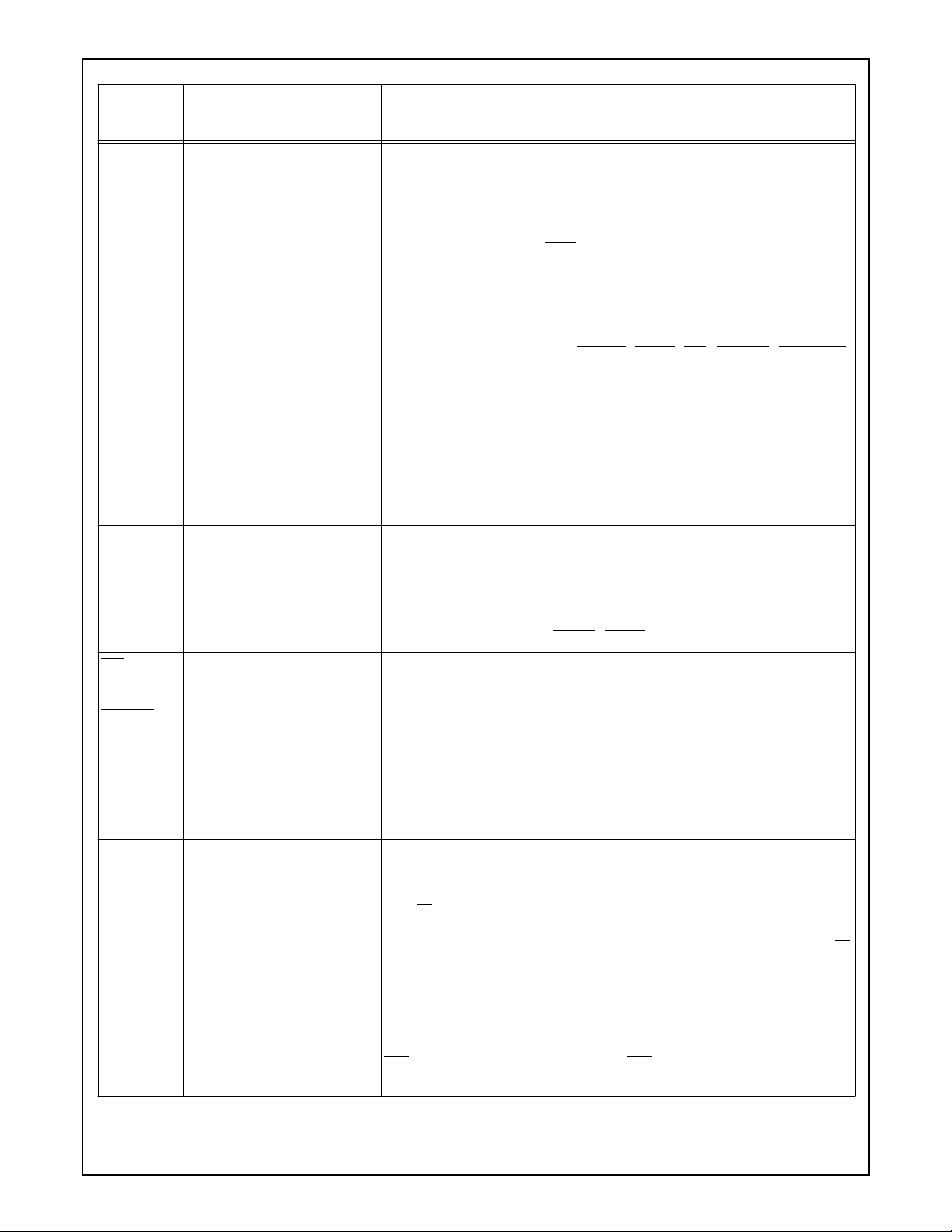

Table of Contents

1.0 Pin Descriptions

1.1 CONNECTION DIAGRAMS .............................................................................................................18

1.2 SIGNAL/PIN DESCRIPTIONS ..........................................................................................................22

2.0 Configuration

2.1 OVERVIEW ......................................................................................................................................36

2.2 CONFIGURATION REGISTER SETUP ...........................................................................................36

2.2.1 Hardware Device Confi guration ..............................................................................................36

2.2.2 Software Device Configurat io n ............... ........................ ........................ ....................... ..........38

2.2.3 Updating Configuration Registers ........................................................................................... 38

2.2.4 Reserved Bits in Configurat ion Registers .... .......... ....................... ........................ ...................38

2.2.5 INDEX and DATA Register Locations .....................................................................................38

2.2.6 Plug and Play Protocol ............................................................................................................39

2.3 THE CONFIGURATION REGISTERS ..............................................................................................40

2.3.1 Configuration Register Bitmaps ...............................................................................................41

2.3.2 Function Enable Register (FER), Index 00h ............................................................................45

2.3.3 Function Address Register (FAR), Index01h .......................................................................... 47

2.3.4 Power and Test Register (PTR), Index 02h ........................................ ..... ....... ....... ....... ..... .....47

2.3.5 Function Control Register (FCR), Index03h ...........................................................................48

2.3.6 Printer Control Register (PCR), Index04h .............................................................................. 49

2.3.7 Power Management Control Register (PMC), Index 06h ........................................................50

2.3.8 Tape, SCCs and Parallel Port Configuration Register (TUP), Index 07h ................................51

2.3.9 SuperI/O Chip Identification Register (SID), Index 08h ...........................................................52

2.3.10 Advanced SuperI/O Chip Configuration Register (ASC), Index 09h .....................................52

2.3.11 Chip Select 0 Low Address Register (CS0LA), Index 0Ah ....................................................53

2.3.12 Chip Select 0 Configuration Register (CS0CF), Index 0B h ...................................................53

2.3.13 Chip Select 1 Low Address Register (CS1LA), Index 0Ch ....................................................54

2.3.14 Chip Select 1 Configuration Register (CS1CF), Index 0Dh ...................................................54

2.3.15 Chip Select 0 High Address Register (CS0HA), Index 10h ...................................................55

2.3.16 Chip Select 1 High Address Register (CS1HA), Index 11h ...................................................55

2.3.17 SuperI/O Chip Configuration Register 0 (SCF0), Index 1 2h .................................................55

2.3.18 SuperI/O Chip Configuration Register 1 (SCF1), Index 1 8h .................................................56

2.3.19 Plug and Play Configuration 0 Register (PNP0), Index 1Bh .................................................57

2.3.20 Plug and Play Configuration 1 Register (PNP1), Index 1Ch .................................................58

2.3.21 SuperI/O Chip Configuration Register 2 (SCF2), Index 4 0h .................................................58

2.3.22 Plug and Play Configuration 2 Register (PNP2), Index 41h ..................................................59

2.3.23 Parallel Port Base Address Low Byte Register (PBAL), Index42h .......................................60

2.3.24 Parallel Port Base Address High Byte Register (PBAH), Index 43h .....................................60

2.3.25 SCC1 Base Address Low Byte Register (S1BAL), Index 44h ...............................................61

2.3.26 SCC1 Base Address High Byte Register (S1BAH), Index 45h .............................................61

2.3.27 SCC2 Base Address Low Byte Register (S2BAL), Index 46h ...............................................61

2.3.28 SCC2 Base Address High Byte Register (S2BAH), Index 47h .............................................62

2.3.29 FDC Base Address Low Byte Register (FBAL), Index 48h ...................................................62

2.3.30 FDC Base Address High Byte Register (FBAH,) Index 49h . .................................................62

5

www.national.com

2.3.31 SIO Base Address Low Byte Register (SBAL), Index 4Ah ....................................................63

2.3.32 SIO Base Address High Byte Register (SBAH), Index4Bh .................................................. 63

2.3.33 System IRQ Input 1 Configuration Register (SIRQ1), Index 4Ch ..........................................63

2.3.34 System IRQ Input 2 Configuration Register (SIRQ2), Index 4Dh ..........................................64

2.3.35 System IRQ Input 3 Configuration Register (SIRQ3), Index 4Eh . .........................................65

2.3.36 Plug-and-Play Configuration 3 Register (PNP3), Index 4Fh .................................................66

2.3.37 SuperI/O Configuration 3 Register (SCF3), Index 50h ..........................................................67

2.3.38 Clock Co ntrol Register (CLK), Index 51h ..............................................................................68

2.3.39 Manufacturing Test Register (MTEST), Index 52h ................................................................68

3.0 The Digital Floppy Disk Controller (FDC)

3.1 FDC FUNCTIONS ............................................................................................................................69

3.1.1 Microprocessor Interface .........................................................................................................69

3.1.2 System Operation Modes ........................................................................................................ 70

3.2 DATA TRANSFER ............................................................................................................................70

3.2.1 Data Rates ..............................................................................................................................70

3.2.2 The Data Separator .................................................................................................................70

3.2.3 Perpendicular Recording Mode Support ........................................................... .......... ....... .....71

3.2.4 Data Rate Selection ................................................................................................................72

3.2.5 Write Precompensation ...........................................................................................................72

3.2.6 FDC Low-Power Mode Logic ..................................................................................................73

3.2.7 Reset .................. ....................... ........................ ........................ ....................... ............... .......73

3.3 THE REGISTERS OF THE FDC ......................................................................................................74

3.3.1 FDC Register Bitmaps .............................................................................................................74

3.3.2 Status Register A (SRA), Offset 000 .......................................................................................75

3.3.3 Status Register B (SRB), Offset 001 .......................................................................................76

3.3.4 Digital Output Re gister (DOR), Offset 010 ..............................................................................77

3.3.5 Tape Drive Register (TDR), Offset 011 ...................................................................................79

3.3.6 Main Status Register (MSR), Offset 100 .. ...............................................................................80

3.3.7 Data Rate Select Register (DSR), Offset 100 .........................................................................82

3.3.8 Data Register (FIFO), Offset 101 ............................................................................................83

3.3.9 Digital Input Register (DIR), Offset 111 ...................................................................................83

3.3.10 Configuration Control Register (CCR), Offset 111 ................................................................84

3.4 THE PHASES OF FDC COMMANDS ..............................................................................................85

3.4.1 Command Phase .............. ......... ........................ ........................ ....................... ......................85

3.4.2 Execution Phase .....................................................................................................................85

3.4.3 Result Phase ........................................................................................................................... 87

3.4.4 Idle Phase ........ ........................ ........................ ....................... ........................ ........................88

3.4.5 Drive Polling Phase .................................................................................................................88

3.5 THE RESULT PHASE STATUS REGIST ER S ....... .......... ........................ ....................... .................88

3.5.1 Result Phase Status Register 0 (ST0) ....................................................................................88

3.5.2 Result Phase Status Register 1 (ST1) ....................................................................................89

3.5.3 Result Phase Status Register 2 (ST2) ....................................................................................90

3.5.4 Result Phase Status Register 3 (ST3) ....................................................................................91

3.6 THE FDC COMMAND SET ..............................................................................................................91

3.6.1 Abbreviations Used in FDC Commands ................................................... .. ....... .......... .. ....... ...92

6

www.national.com

3.6.2 The CONFIGURE Command ....................................................... ....... ....... ..... ....... ....... ..... .....94

3.6.3 The DUMPREG Command ............................................ .. ....... .......... ....... .. ....... .......... .. ....... ...95

3.6.4 The FORMAT TRACK Command ................................................................... .. .......... ....... .....96

3.6.5 The INVALID Command .................................................. ..... ....... ....... ....... ..... ....... ....... ..... .....99

3.6.6 The LOCK Command ............................................................................................................100

3.6.7 The MODE Command ........................................................... ....... ....... ..... ....... ....... ....... ..... .. .100

3.6.8 The NSC Command ................... ..... ..... ..... .... ..... ..... .. ..... .. ..... .. ..... ..... .. ..... .. ..... .. ..... ..... .. ... .....103

3.6.9 The PERPENDICULAR MODE Command .......................................................................... .103

3.6.10 The READ DATA Command ...............................................................................................105

3.6.11 The READ DELETED DATA Command .............................................................................108

3.6.12 The READ ID Command .....................................................................................................109

3.6.13 The READ A TRACK Command .........................................................................................110

3.6.14 The RECALIBRATE Command ...........................................................................................110

3.6.15 The RELATIVE SEEK Command ........................................................................................111

3.6.16 The SCAN EQUAL, the SCAN LO W OR EQUAL and the SCAN HI GH

OR EQUAL Commands ......................................................................................................112

3.6.17 The SEEK Command ..........................................................................................................113

3.6.18 The SENSE DRIVE STATUS Command ............................................................................114

3.6.19 The SENSE INTERRUPT Command ..................................................................................114

3.6.20 The SET TRACK Command ...............................................................................................115

3.6.21 The SPECIFY Command ....................................................................................................116

3.6.22 The VERIFY Command ......................................................................................................118

3.6.23 The VERSION Comm and ...................................................................................................119

3.6.24 The WRITE DATA Command .............................................................................................120

3.6.25 The WRITE DELETED DATA Command ............................................................................121

3.7 EXAMPLE OF A FOUR-DRIVE CIRCUIT USING THE PC87338/PC97338 ..................................121

4.0 Parallel Port

4.1 INTRODUCTION ............................................................................................................................123

4.1.1 The Chip Parallel Port Modes ...............................................................................................123

4.1.2 Device Conf igu r a tion ......... ......... ........................ ........................ ....................... ............... .....123

4.2 STANDARD PARALLEL PORT MODES ........................................................................................123

4.2.1 Standard Parallel Port (SPP) Modes Register Set . ...............................................................124

4.2.2 SPP Mode Parallel Port Register Bitmaps ....... ......... ........................ ........................ ............124

4.2.3 Data Register (DTR), Offset 0 ...............................................................................................124

4.2.4 Status Register (STR), Offset 1 .............................................................................................125

4.2.5 Control Register (CTR), Offset 2 ...........................................................................................126

4.3 ENHANCED PARALLEL POR T (EPP) MO D ES ........................... ....................... ........................ ... 127

4.3.1 Enhanced Parallel Port (EPP) Modes Register Set ..............................................................128

4.3.2 EPP Modes Parallel Port Regist e r Bitm a ps ................... ........................ ....................... ........128

4.3.3 SPP or EPP Data Register (DTR), Offset 0 ..........................................................................129

4.3.4 SPP or EPP Status Regi ste r ( ST R ), Offset 1 ............................... ........................ .................129

4.3.5 SPP or EPP Control Register (CTR), Offset 2 ......................................................................129

4.3.6 EPP Address Register, Offset 3 ............................................................................................130

4.3.7 EPP Data Port 0, Offse t 4 ........ ........................ ....................... ........................ ......................130

4.3.8 EPP Data Port 1, Offse t 5 ........ ........................ ....................... ........................ ......................130

4.3.9 EPP Data Port 2, Offse t 6 ........ ........................ ....................... ........................ ......................130

7

www.national.com

4.3.10 EPP Data Port 3, Offset 7 ...................................................................................................131

4.3.11 EPP Mode Transfer Operations ..........................................................................................131

4.4 EXTENDED CAPABILITIES PARALLEL PORT (ECP) MODES ....................................................133

4.4.1 Accessing the ECP Registers ...............................................................................................134

4.4.2 Software Operation in ECP Modes .......................................................................................134

4.4.3 Hardware Operation in ECP Modes ......................................................................................134

4.4.4 ECP Modes Parallel Port Register Bitmaps ..........................................................................135

4.4.5 ECP Data Register (DATAR), Bits 7-5 of ECR = 000 or 001, Offset 000h ............................136

4.4.6 ECP Address FIFO (AFIFO) Register, Bits 7-5 of ECR = 011, Offset 000h ..........................137

4.4.7 ECP Status Register (DSR), Offset 001h ..............................................................................137

4.4.8 ECP Control Register (DCR), Offset 002h ........................................................................... .137

4.4.9 Parallel Port Data FIFO (CFIFO) Register, Bits 7-5 of ECR = 010, Offset 400h ...................138

4.4.10 ECP Data FIFO (DFIFO) Register, Bits 7-5 of ECR = 011, Offset 400h .............................138

4.4.11 Test FIFO (TFIFO) Register, Bits 7-5 of ECR = 110, Offset 400h ......................................139

4.4.12 Configuration Register A (CNFGA), Bits 7-5 of ECR = 111, Offset 400h ............................139

4.4.13 Configuration Register B (CNFGB), Bits 7-5 of ECR = 111, Offset 401h ............................139

4.4.14 Extended Control Register (ECR), Offset 402h ...................................................................140

4.5 ECP MODE DESCRIPTIONS .........................................................................................................142

4.5.1 Software Controlled Data Transfer (Modes 000 and 001) .....................................................142

4.5.2 Automatic Data Transfer (Modes 010 and 011) ................................................ .......... ....... .. .142

4.5.3 FIFO Test Access (Mode 110) ................................................ ..... ....... ....... ..... ....... ....... ........143

4.5.4 Configuration Registers Access (Mode 111) ... ......................................................................143

4.5.5 Interrupt Generation ..............................................................................................................143

4.6 THE PARALLEL PORT MULTIPLEXER (PPM) ............................................................................. 144

4.7 PARALLEL PORT PIN/SIGNAL LIST .............................................................................................144

5.0 Serial Communications Controllers (SCC1 and SCC2)

5.1 FEATURES .....................................................................................................................................146

5.2 FUNCTIONAL MODES OVERVIEW .............................................................................................. 146

5.3 UART MODE ..................................................................................................................................146

5.4 SHARP-IR MODE ...........................................................................................................................147

5.5 IRDA 1.0 SIR MODE ...................................................................................................................... 147

5.6 IRDA 1.1 M IR AND FIR MODES ....................................................................................................147

5.6.1 High Speed Infrared Transmit Operation ..............................................................................148

5.6.2 High Speed Infrared Receive Operation ...............................................................................149

5.7 CONSUMER ELECTRONIC IR (CEIR) MODE ..............................................................................149

5.7.1 CEIR Transmit Operation ......................................................................................................149

5.7.2 CEIR Receive Operation .......................................................................................................150

5.8 FIFO TIME-OUTS ...........................................................................................................................150

5.9 TRANSMIT DEFERRAL .................................................................................................................151

5.10 AUTOMATIC FALLBACK TO 16550 COMP A TIBILITY MO DE ....................................................151

5.11 PIPELINING ..................................................................................................................................152

5.12 OPTICAL TRANSCEIVER INTERFACE ......................................................................................152

8

www.national.com

5.13 ARCHITECTURAL DESCRIPTION ..............................................................................................153

5.14 BANK 0 ......................................................................................................................................... 153

5.14.1 TXD/RXD – Transmit/Receive Data Ports ...........................................................................153

5.14.2 IER – Interrupt Enable Register ..........................................................................................154

5.14.3 EIR/FCR – Event Identification/FIFO Control Registers ......................................................154

5.14.4 LCR/BSR – Link Control/Bank Select Register ...................................................................157

5.14.5 MCR – Modem/Mode Control Register .. .............................................................................159

5.14.6 LSR – Link Status Register .................................................................................................160

5.14.7 MSR – Modem Status Register ...........................................................................................162

5.14.8 SPR/ASCR – Scratchpad/Auxiliary Status and Control Register ........................................162

5.15 BANK 1 ......................................................................................................................................... 163

5.15.1 LBGD – Legacy Baud Generator Divisor Port . ....................................................................164

5.15.2 LCR/BSR – Link Control/Bank Select Registers .................................................................164

5.16 BANK 2 ......................................................................................................................................... 164

5.16.1 BGD – Baud Generator Divisor Port ...................................................................................164

5.16.2 EXCR1 – Extended Control Register 1 ...............................................................................166

5.16.3 LCR/BSR – Link Control/Bank Select Registers .................................................................167

5.16.4 EXCR2 – Extended Control Register 2 ...............................................................................167

5.16.5 TXFLV – TX_FIFO Level, Read-Only ..................................................................................168

5.16.6 RXFLV – RX_FIFO Level, Read-Only .................................................................................168

5.17 BANK 3 ......................................................................................................................................... 168

5.17.1 MID – Module Identification Register, Read Only ...............................................................168

5.17.2 SH_LCR – Link Control Register Shadow, Read Only .................................... .......... .. ....... .168

5.17.3 SH_FCR – FIFO Control Register Shadow, Read-Only ......................................................168

5.17.4 LCR/BSR – Link Control/Bank Select Registers .................................................................168

5.18 BANK 4 ......................................................................................................................................... 169

5.18.1 TMR – Timer Register .........................................................................................................169

5.18.2 IRCR1 – Infrared Control Register 1 ...................................................................................169

5.18.3 LCR/BSR – Link Control/Bank Select Registers .................................................................169

5.18.4 TFRL/TFRCC – Transmitter Frame-Length/Current-Count .................................................170

5.18.5 RFRML/RFRCC – Receiver Frame Maximum-Length/Current-Count ................................170

5.19 BANK 5 ......................................................................................................................................... 170

5.19.1 P_BGD – Pipelined Baud Generator Divisor Register ........................................................170

5.19.2 P_MDR – Pipelined Mode Register .....................................................................................170

5.19.3 LCR/BSR – Link Control/Bank Select Registers .................................................................171

5.19.4 IRCR2 – Infrared Control Register 2 ...................................................................................171

5.19.5 ST_FIFO – Status FIFO ......................................................................................................172

5.20 BANK 6 ......................................................................................................................................... 173

5.20.1 IRCR3 – Infrared Control Register 3 ...................................................................................173

5.20.2 MIRPW – MIR Pulse Width Register ...................................................................................173

5.20.3 SIR_PW – SIR Pulse Width Registe r ..................................................................................174

5.20.4 LCR/BSR – Link Control/Bank Select Registers .................................................................174

5.20.5 BFPL – Beginning Flags/P reamble Length Register ...........................................................174

5.21 BANK 7 ......................................................................................................................................... 175

5.21.1 IRRXDC – Infrared Receiver Demodulator Control Register ..............................................175

9

www.national.com

5.21.2 IRTXMC – Infrared Transmitter Modulator Control Register ...............................................178

5.21.3 RCCFG – CEIR Configuration Register ..............................................................................179

5.21.4 LCR/BSR – Link Control/Bank Select Registers .................................................................179

5.21.5 IRCFG [1–4] – Infrared Interface Configuration Registers ..................................................179

5.22 SERIAL COMMUNICATION CONTROLLER2 REGISTER BITMAPS .........................................182

6.0 DMA and Interrupt Mapping

6.1 DMA SUPPORT .............................................................................................................................190

6.1.1 Legacy Mode .............................................................................................. ...........................190

6.1.2 Plug and Play Mode .......................................................................................... ............ ........190

6.2 INTERRUPT SUPPORT .................................................................................................................191

6.2.1 Legacy Mode .............................................................................................. ...........................191

6.2.2 Plug and Play Mode .......................................................................................... ............ ........192

7.0 Power Management

7.1 POWER-DOWN STATE .................................................................................................................194

7.1.1 Recommended Power-Down Methods - Group 1 ................... .......... .. ....... ....... .......... .. ....... .194

7.1.2 Recommended Power-Down Methods - Group 2 ................... .......... .. ....... ....... .......... .. ....... .195

7.1.3 Special Power-Down Cases ..................................................................................................195

7.2 POWER-UP ....................................................................................................................................195

7.2.1 The Clock Multiplier ...............................................................................................................195

7.2.2 Chip Power-Up Procedure ...................................................... .......... ....... .. ....... .......... .. ....... .195

7.2.3 SCC1 and SCC2 Power-Up ..................................................................................................196

7.2.4 FDC Power-Up ......................................................................................................................196

8.0 Device Description

8.1 GENERAL ELECTRICAL CHARACTERISTICS ............................................................................197

8.1.1 Absolute Maximum Ratings ................................................................................................... 197

8.1.2 Capacitance ..................................................................... ................... .............. ....................197

8.1.3 Electrical Characteristics .......................................................................................................197

8.2 DC CHARACTERISTICS OF PINS, BY GROUP ...........................................................................198

8.2.1 Group 1 ................................................................................... ................... ...........................198

8.2.2 Group 2 ................................................................................... ................... ...........................198

8.2.3 Group 3 ................................................................................... ................... ...........................198

8.2.4 Group 4 ................................................................................... ................... ...........................199

8.2.5 Group 5 ................................................................................... ................... ...........................199

8.2.6 Group 6 ................................................................................... ................... ...........................199

8.2.7 Group 7 ................................................................................... ................... ...........................200

8.2.8 Group 8 ................................................................................... ................... ...........................200

8.2.9 Group 9 ................................................................................... ................... ...........................201

8.2.10 Group 10 .............................................................................................................................201

8.2.11 Group 11 .............................................................................................................................201

8.2.12 Group 12 .............................................................................................................................202

8.2.13 Group 13 .............................................................................................................................202

10

www.national.com

8.3 AC ELECTRICAL CHARACTERISTICS .........................................................................................202

8.3.1 AC Test Conditions T

= 0° C to 70° C, VDD = 5.0 V ± 10%, 3.3 V ± 10% ...........................202

A

8.4 SWITCHING CHARACTERISTICS ................................................................................................203

8.4.1 Timing Table .........................................................................................................................203

8.4.2 Timing Diagrams ..................................................................................................................207

9.0 Appendix A

COMPARISON OF PC87338 A ND PC97338 .......................................................................................216

11

www.national.com

List of Figures

FIGURE 1 Plug and Play Protocol Flowchart ..................................................................................................39

FIGURE 2 LFSR Circuit ...................................................................................................................................40

FIGURE 3 FER Register Bitmap .....................................................................................................................45

FIGURE 4 FAR Register Bitmap .....................................................................................................................47

FIGURE 5 PTR Register Bitmap .....................................................................................................................48

FIGURE 6 FCR Register Bitmap .....................................................................................................................48

FIGURE 7 PCR Register Bitmap .....................................................................................................................49

FIGURE 8 PMC Register Bitmap .....................................................................................................................50

FIGURE 9 TUP Register Bitmap .....................................................................................................................51

FIGURE 10 SID Register Bitmap .....................................................................................................................52

FIGURE 11 ASC Register Bitmap ...................................................................................................................52

FIGURE 12 CS0LA Register Bitmap ............................................................................................................... 53

FIGURE 13 CS0CF Register Bitmap ...............................................................................................................53

FIGURE 14 CS1LA Register Bitmap ............................................................................................................... 54

FIGURE 15 CS1CF Register Bitmap ...............................................................................................................54

FIGURE 16 CS0HA Register Bitmap ...............................................................................................................55

FIGURE 17 CS1HA Register Bitmap ...............................................................................................................55

FIGURE 18 SCF0 Register Bitmap .................................................................................................................55

FIGURE 19 SCF1 Register Bitmap .................................................................................................................56

FIGURE 20 PNP0 Register Bitmap .................................................................................................................57

FIGURE 21 PNP1 Register Bitmap .................................................................................................................58

FIGURE 22 SCF2 Register Bitmap .................................................................................................................58

FIGURE 23 Busy Flag Timing .........................................................................................................................59

FIGURE 24 PNP2 Register Bitmap .................................................................................................................59

FIGURE 25 PBAL Register Bitmap .................................................................................................................60

FIGURE 26 PBAH Register Bitmap .................................................................................................................61

FIGURE 27 S1BAL Register Bitmap ...............................................................................................................61

FIGURE 28 S1BAH Register Bitmap ...............................................................................................................61

FIGURE 29 S2BAL Register Bitmap ...............................................................................................................61

FIGURE 30 S2BAH Register Bitmap ...............................................................................................................62

FIGURE 31 FBAL Register Bitmap ..................................................................................................................62

FIGURE 32 FBAH Register Bitmap .................................................................................................................62

FIGURE 33 SBAL Register Bitmap .................................................................................................................63

FIGURE 34 SBAH Register Bitmap .................................................................................................................63

FIGURE 35 SIRQ1 Register Bitmap ................................................................................................................63

FIGURE 36 SIRQ2 Register Bitmap ................................................................................................................64

FIGURE 37 SIRQ3 Register Bitmap ................................................................................................................65

FIGURE 38 PNP3 Register Bitmap .................................................................................................................66

FIGURE 39 SCF3 Register Bitmap .................................................................................................................67

FIGURE 40 CLK Register Bitmap ....................................................................................................................68

FIGURE 41 FDC Functional Block Diagram ........................................... .. ..... .. ..... ..... .. ..... .. ..... .. ..... .................69

FIGURE 42 PC87338/PC97338 D ynamic Window Ma rgin Performance ........................................................70

FIGURE 43 Read Algorithm State Diagram ....................................................................................................71

FIGURE 44 Perpendicular Recording Drive Read/Write Head and Pre-Erase Head . .....................................72

FIGURE 45 SRA Register Bitmap ...................................................................................................................75

FIGURE 46 SRB Register Bitmap ...................................................................................................................76

FIGURE 47 DOR Register Bitmap ...................................................................................................................78

FIGURE 48 TDR Register Bitmap ...................................................................................................................79

FIGURE 49 MSR Register Bitmap ...................................................................................................................81

12

www.national.com

FIGURE 50 DSR Register Bitmap ................................................................................................................... 82

FIGURE 51 FDC Data Register Bitmap ...........................................................................................................83

FIGURE 52 DIR Register Bitmap ....................................................................................................................84

FIGURE 53 CCR Register Bitmap ...................................................................................................................84

FIGURE 54 ST0 Result Phase Register Bitmap ..............................................................................................88

FIGURE 55 ST1 Result Phase Register Bitmap ..............................................................................................89

FIGURE 56 ST2 Result Phase Register Bitmap ..............................................................................................90

FIGURE 57 ST3 Result Phase Register ..........................................................................................................91

FIGURE 58 IBM, Perpendicular, and ISO Formats Supported by FORMAT TRACK Command ....................99

FIGURE 59 PC87338/PC97338 Four Floppy Disk Drive Circuit ...................................................................122

FIGURE 60 DTR Register Bitmap (SPP Mode) .............................................................................................125

FIGURE 61 STR Register Bitmap (SPP Mode) .............................................................................................125

FIGURE 62 CTR Register Bitmap (SPP Mode) in PC87338 .........................................................................126

FIGURE 63 CTR Register Bitmap (SPP Mode) in PC97338 .........................................................................126

FIGURE 64 DTR Register Bitmap (EPP Mode) .............................................................................................129

FIGURE 65 STR Register Bitmap (EPP Mode) .............................................................................................129

FIGURE 66 CTR Register Bitmap (EPP Mode) .............................................................................................130

FIGURE 67 DTR Register Bitmap (EPP Mode) .............................................................................................130

FIGURE 68 DTR Register Bitmap (EPP Mode) .............................................................................................130

FIGURE 69 DTR Register Bitmap (EPP Mode) .............................................................................................130

FIGURE 70 EPP Data Port 2 Bitmap .............................................................................................................130

FIGURE 71 EPP Data Port 3 Bitmap .............................................................................................................131

FIGURE 72 EPP 1.7 Address Write ..............................................................................................................131

FIGURE 73 EPP 1.7 Address Read ..............................................................................................................132

FIGURE 74 EPP Write with Zero Wait States ...............................................................................................132

FIGURE 75 EPP 1.9 Address Write ..............................................................................................................133

FIGURE 76 EPP 1.9 Address Read ..............................................................................................................133

FIGURE 77 DATAR Register Bitmap ............................................................................................................136

FIGURE 78 AFIFO Register Bitmap ..............................................................................................................137

FIGURE 79 ECP DSR Register Bitmap .........................................................................................................137

FIGURE 80 DCR Register Bitmap .................................................................................................................137

FIGURE 81 CFIFO Register Bitmap ..............................................................................................................138

FIGURE 82 DFIFO Register Bitmap ..............................................................................................................139

FIGURE 83 TFIFO Register Bitmap ..............................................................................................................139

FIGURE 84 CNFGA Register Bitmap ............................................................................................................ 139

FIGURE 85 CNFGB Register Bitmap ............................................................................................................ 140

FIGURE 86 ECR Register Bitmap ................................................................................................................. 140

FIGURE 87 ECP Forward Write Cycle ..........................................................................................................142

FIGURE 88 ECP (Reverse) Read Cycle .......................................................................................................143

FIGURE 88 Composite Serial Data ...............................................................................................................146

FIGURE 88 Register Bank Architecture ........................................................................................................153

FIGURE 88 Interrupt Enable Register .... .......................................................................................................154

FIGURE 88 Event Identification Register, Non-Extended Mode ...................................................................155

FIGURE 88 Event Identification Register, Extended Mode ...........................................................................156

FIGURE 88 FIFO Control Register ................................................................................................................157

FIGURE 88 Link Control Register ..................................................................................................................158

FIGURE 88 Modem Control Register, Non-Extended Mode ...................................................................... .. .159

FIGURE 88 Modem Control Register, Extended Modes .................................................. ....... .. .......... ....... ...159

FIGURE 88 Link Status Register ...................................................................................................................160

FIGURE 88 Modem Status Register ......................................................... ....... .......... .. ....... ....... ..... ...............162

FIGURE 88 Auxillary Status and Control Register .......................................................................................162

13

www.national.com

FIGURE 88 Extended Control Register 1 . .....................................................................................................166

FIGURE 88 DMA Control Signals Routing ............................ ..... ..... .. ..... .. ..... ..... ..... .... ..... .. ..... .. ..... ...............167

FIGURE 88 Extended Control Register 2 . .....................................................................................................167

FIGURE 88 Transmit FIFO Level .................................................................................................................168

FIGURE 88 Receive FIFO Level ..................................................................................................................168

FIGURE 88 Infrared Control Register 1 .........................................................................................................169

FIGURE 88 Pipelined Mode Register ...........................................................................................................171

FIGURE 88 IInfrared Control Register 2 ........................................................................................................171

FIGURE 88 Frame Status Byte Register .......................................................................................................172

FIGURE 88 Infrared Control Register 3 .........................................................................................................173

FIGURE 88 MIR Pulse Width Register ..........................................................................................................173

FIGURE 88 SIR Pulse Width Register ..........................................................................................................174

FIGURE 88 Beginning Flags/Preamble Length Register . .............................................................................174

FIGURE 88 Intrared Receiver Demodulator Control Register ......................................................................175

FIGURE 88 Intrared Transmitter Modulator Control Register .................................................. ....... ....... ........178

FIGURE 88 CEIR Configuration Register .....................................................................................................179

FIGURE 88 Infrared Configuration Register 1 ...............................................................................................180

FIGURE 88 Infrared Configuration Register 2 ...............................................................................................180

FIGURE 88 Infrared Configuration Register 3 ...............................................................................................181

FIGURE 88 Infrared Configuration Register 4 ...............................................................................................181

FIGURE 89 Load Circuit ................................................................................................................................202

FIGURE 90 Testing Specification Standard ..................................................................................................203

FIGURE 91 Clock Timing ..............................................................................................................................207

FIGURE 92 CPU Read Timing ......................................................................................................................208

FIGURE 93 CPU Write Timing ......................................................................................................................208

FIGURE 94 DMA Access Timing ...................................................................................................................209

FIGURE 95 UART, Sharp-IR and CEIR Timing ............................................................................................209

FIGURE 96 SIR, MIR and FIR Timing ...........................................................................................................210

FIGURE 97 IRSLn Write Timing ....................................................................................................................210

FIGURE 98 Modem Control Timing ................................................... ....... ..... ....... ....... ....... ..... ....... ...............211

FIGURE 99 FDC Write Data Timing ..............................................................................................................211

FIGURE 100 FDC Read Data Timing ............................................................................................................211

FIGURE 101 FDC Control Signal s Ti mi n g ............................. ........................ ........................ ........................212

FIGURE 102 Parallel Port Interrupt Timing (Compatible Mode) ....................................................................212

FIGURE 103 Parallel Port Interrupt Timing (Extended Mode) .......................................... .. ....... .......... ....... .. .212

FIGURE 104 Parallel Port Data Transfer Timing (Compatible Mode) ......................... ....... ....... .......... .. ....... .213

FIGURE 105 Parallel Port Data Transfer Timing (EPP 1.7 Mode) ...............................................................213

FIGURE 106 Parallel Port Data Transfer Timing (EPP 1.9 Mode) ...............................................................214

FIGURE 107 Parallel Port Forward Transfer Timing (ECP Mode) ...............................................................214

FIGURE 108 Parallel Port Reverse Transfer Timing (ECP Mode) ......................................... .. ..... ..... .. ..... .. .215

FIGURE 109 System Interrupts Timing .........................................................................................................215

FIGURE 110 CS1-0 Signals Timing ................................................ ....... ....... .. .......... ....... .. ....... ....................215

FIGURE 111 Reset Timing ............................................................................................................................ 215

14

www.national.com

List of Tables

TABLE 1 Signal/Pin Description Table ............................................................................................................22

TABLE 2 Multi-Function Pins (Excluding Strap Pins) ...................................................................................... 34

TABLE 3 IRQ12, A15-11 / SCC2 / Infrared Pin Allocation ...............................................................................35

TABLE 4 SCC2 Mode Configurations 1 . ..........................................................................................................35

TABLE 5 SCC2 Mode Configurations 2 .......................................................................................................... 35

TABLE 6 Default Configurations Controlled by Hardware .............................................................................. 36

TABLE 7 Configuration Registers ...................................................................................................................36

TABLE 8 IND E X a nd DA T A R egister Addre s s Op tio n s and Con figuration Re gis te r Ac cessibility .......... .... ... . 38

TABLE 9 Primary and Secondary Drive Address Selection ............................................................................ 46

TABLE 10 Encoded Drive and Motor Pin Information (Bit 4 of FER = 1) .........................................................46

TABLE 11 Parallel Port Addresses ..................................................................................................................47

TABLE 12 COM Port Selection for SCC1 ........................................................................................................47

TABLE 13 COM Port Selection for SCC2 ........................................................................................................47

TABLE 14 Address Selection for COM3 and COM4 ......................................................................................47

TABLE 15 Parallel Port Mode ..........................................................................................................................49

TABLE 16 Bit Settings to Enable MRT 1

TABLE 17 Bit Settings to Enable DR1

TABLE 18 ECP DMA Option Selection ...........................................................................................................56

TABLE 19 Parallel Port Plug and Play DMA Settings .....................................................................................56

TABLE 20 Parallel Port Plug and Play Interrupt Assignment ..........................................................................57

TABLE 21 Parallel Port Plug and Play Interrupt Mapping .............................................................................57

TABLE 22 TDR Bit 5 Values ............................................................................................................................58

TABLE 23 FDC Plug and Play Interrupt Mapping ...........................................................................................59

TABLE 24 FDC Plug and Play DMA Settings ..................................................................................................60

TABLE 25 SBAL Reset Values .......................................................................................................................63

TABLE 26 SBAH Reset Values ......................................................................................................................63

TABLE 27 SIRQI1 Plug and Play Interrupt Mapping .......................................................................................64

TABLE 28 SIRQ1 Interrupt Settings 64

TABLE 29 SIRQI2 Plug and Play Interrupt Mapping .................................................................................... 65

TABLE 30 Selecting MSEN1, DRATE1, CS0

TABLE 31 SIRQI3 Plug and Play Interrupt Mapping ......................................................................................66

TABLE 32 Selecting DRV2

TABLE 33 SCC2 Receiver Channel Selection ...............................................................................................67

TABLE 34 SCC2 Transmission Channel Selection .........................................................................................67

TABLE 35 The FDC Registers and Their Addresses ......................................................................................74

TABLE 36 Drive and Motor Pin Encoding When FER 4 = 1 ...................................................................... .....77

TABLE 37 Drive Enable Hexadecimal Values .................................................................................................77

TABLE 38 TDR Bit Utiliz at ion and Reset Val ues in Different Drive M odes .......................... ....... ............ ........ 79

TABLE 39 Media Type Bit Settings ................................................................................................................80

TABLE 40 Data Transfer Rate Encoding .........................................................................................................82

TABLE 41 Write Precompensation Dela ys ......................................................................................................82

TABLE 42 Default Precompensat ion Delays ...................................................................................................82

TABLE 43 FDC Command Set Summary ........................................................................................................92

TABLE 44 Bytes per Sector Codes ................................................................................................................. 97

TABLE 45 Typical Values for PC Compati ble Diskette Media .........................................................................97

TABLE 46 Typical Gap Values ........................................................................................................................98

TABLE 47 Multipliers and Head Settle Time Ranges for Different Data Transfer Rates ..............................102

TABLE 48 DENSEL Encoding ......................................................................................................................102

TABLE 49 Effect of Drive Mode and Data Rate on FORMAT TRACK and WRITE DATA Commands .........104

, DR23, PNF or SIRQI3 ..................................................................................66

, IDLE or IRSL2 ................................................................................51

or PD ..................................................................................................51

or SIRQI2 .................................................................................65

15

www.national.com

TABLE 50 Effect of GDC Bits on FORMAT TRACK and WRITE DATA Commands ....................................104

TABLE 51 Skip Control Effect on READ DATA Command ...........................................................................107

TABLE 52 Result Phase Termination Values with No Error ..........................................................................108

TABLE 53 SK Effect on READ DELETED DATA Command .. ......................................................................108

TABLE 54 Maximum RECALIBRATE Step P ulses for Values of R255 and ETR ..........................................111

TABLE 55 The Effect of Scan Commands on the ST2 Register ...................................................................113

TABLE 56 Interrupt Causes Reported by SENSE INTERRUPT .......... ......... .......................... .......... ............ 114

TABLE 57 Defining Bytes to Read or Write Using SET TRACK ....................................................................116

TABLE 58 Constant Multipliers for Delay After Processing Factor and Delay Ranges ................................117

TABLE 59 Constant Multipliers for Delay Before Processing Factor and Delay Ranges . ............................117

TABLE 60 STEP

Time Interval Calculation .................................................................................................. 117

TABLE 61 VERIFY Command Termination Condi tions .... ............................................................................. 119

TABLE 62 Parallel Port Reset States ...........................................................................................................124

TABLE 63 Standard Parallel Port Registers ................................................................................................124

TABLE 64 SPP Data Register Read and Write Modes .................................................................................125

TABLE 65 EPP Revision Selection ................................................................................................................127

TABLE 66 Parallel Po rt Registers in EPP Mod es ........... .......... ....................... ........................ ......................128

TABLE 67 ECP Modes Encoding ..................................................................................................................133

TABLE 68 Parallel Port Registers in ECP Modes ..........................................................................................134

TABLE 69 ECP Mode DMA Selection ..........................................................................................................140

TABLE 70 ECP Mode Interrupt Selection ......................................................................................................140

TABLE 71 ECP Modes .................................................................................................................................141

TABLE 72 Parallel Port Pin Out .....................................................................................................................144

TABLE 73 Register Bank Summary ............................................................................................................. 153

TABLE 74 Bank 0 Serial Controller Base Registers þ ...................................................................................153

TABLE 75 Non-Extended Mode Interrupt Priorities .......................................................................................155

TABLE 76 TX_FIFO Level Selection ............................................................................................................157

TABLE 77 RX_FIFO Level Selection .............................................................................................................157

TABLE 78 Word Length Select Encoding ......................................................................................................158

TABLE 79 Bit Settings for Parity Control .......................................................................................................158

TABLE 80 Bank Selection Encoding .............................................................................................................159

TABLE 81 The Module Operation Mod es ......................................................................................................160

TABLE 82 Bank 1 Register Set .....................................................................................................................163

TABLE 83 Bank 2 Register Set .....................................................................................................................164

TABLE 84 Baud Generator Divisor Settings ..................................................................................................165

TABLE 85 Bank 3 Register Set .....................................................................................................................168

TABLE 86 Bank 4 Register Set .....................................................................................................................169

TABLE 87 Bank 5 Register ............................................................................................................................170

TABLE 88 Bank 6 Register Set .....................................................................................................................173

TABLE 89 MIR Pulse Width Settings .............................................................................................................174