NSC PC87364-IBW-VLA, PC87364-ICK-VLA, PC87364EB-GEODE Datasheet

www.national.com

PC87364 128-Pin LPC SuperI/O with Extended Wake-Up and Protection Support

PRELIMINARY

January 10, 1999

PC87364

128-Pin LPC SuperI/O with Extended Wake-Up and

Protection Support

General Description

The PC87364, a member of National Semiconductor’s 128pin LPC SuperI/O family, introduces wake-up support for a

wide range of wake-up events, and new hardware and sofware features to protect the system design. The PC87364

provides support for 51 GPIO ports, many with Assert

IRQ/

SMI/PWUREQ capability. It is PC99 and ACPI compliant, and offers a single-chip solution to the most commonly

used PC I/O peripherals.

The PC87364 also incorporates: Fan Speed Control and

Monitor (FSCM) for three fans, a Floppy Disk Controller

(FDC), aKeyboard and Mouse Controller (KBC), a full IEEE

1284 ParallelPort, two enhanced Serial Ports (UARTs), one

with Infrared (IR) support, an ACCESS.bus

®

Interface

(ACB), System Wake-Up Control (SWC), General-Purpose

Input/Output (GPIO) support for 51 ports, Interrupt Serializer

for Parallel IRQs and an enhanced WATCHDOG timer.

Outstanding Features

• Extended Wake-Up support, including legacy/ACPI

power button support, direct power supply control in

response to wake-up events, power-fail recovery

• Protection features, including I/O access lock, chassis

hood lock/unlock, chassis intrusion detection, GPIO pin

attribute lock and pin configuration lock

• Fan Speed Control and Monitor for three fans

• Serial IRQ support (15 options)

• Interrupt Serializer (11 Parallel IRQs to Serial IRQ)

• Bus interface, based on Intel’s

LPC Interface Specifi-

cation

Revision 1.0, September 29th, 1997

• ACCESS .bus Interface, SMBus physical layer compatible

●

51 GPIO Ports (39 standard, including 23 with Assert

IRQ/

SMI/PWUREQs interrupts; 12 VSB-powered)

• Blinking LEDs

• 128-pin PQFP Package

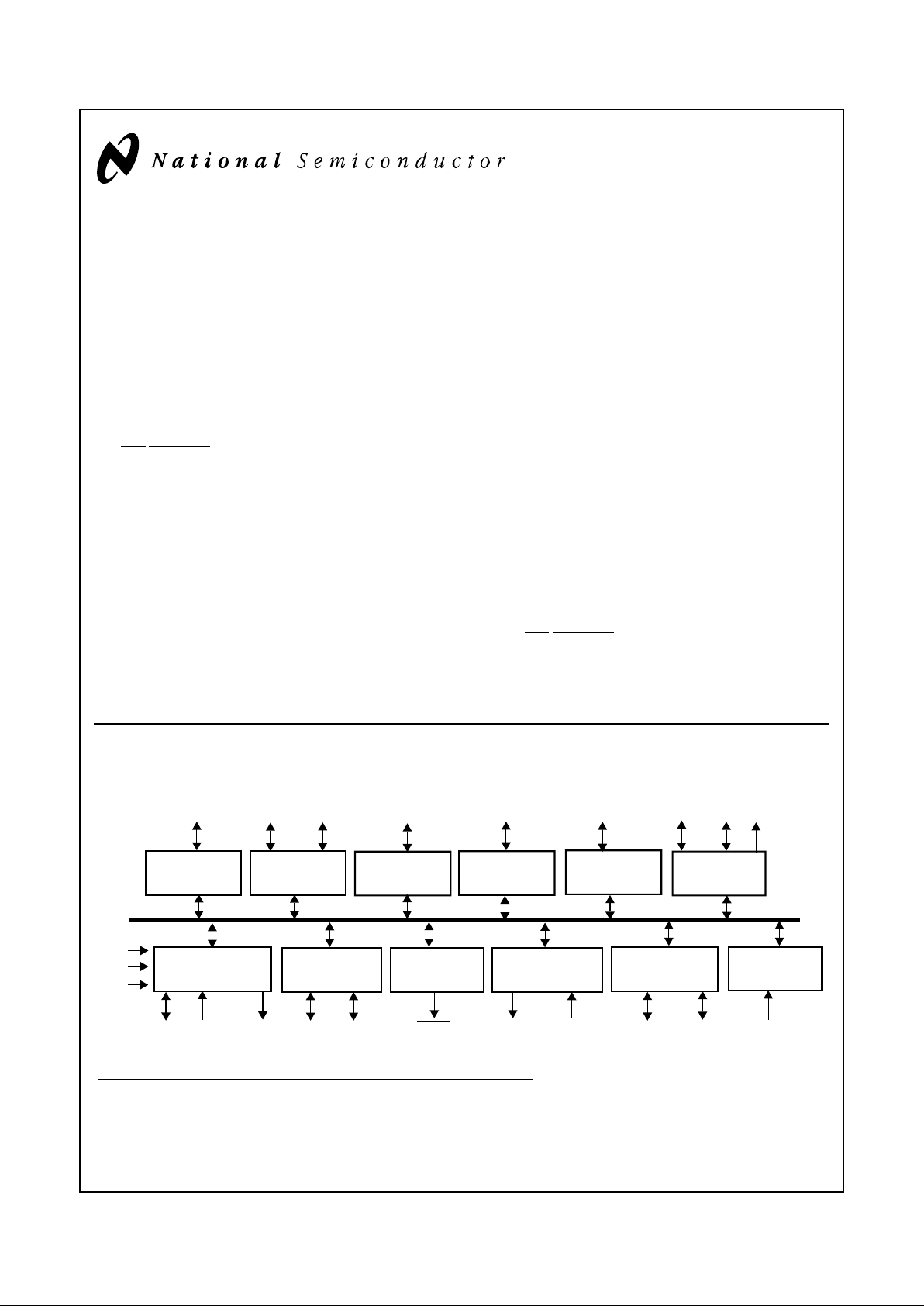

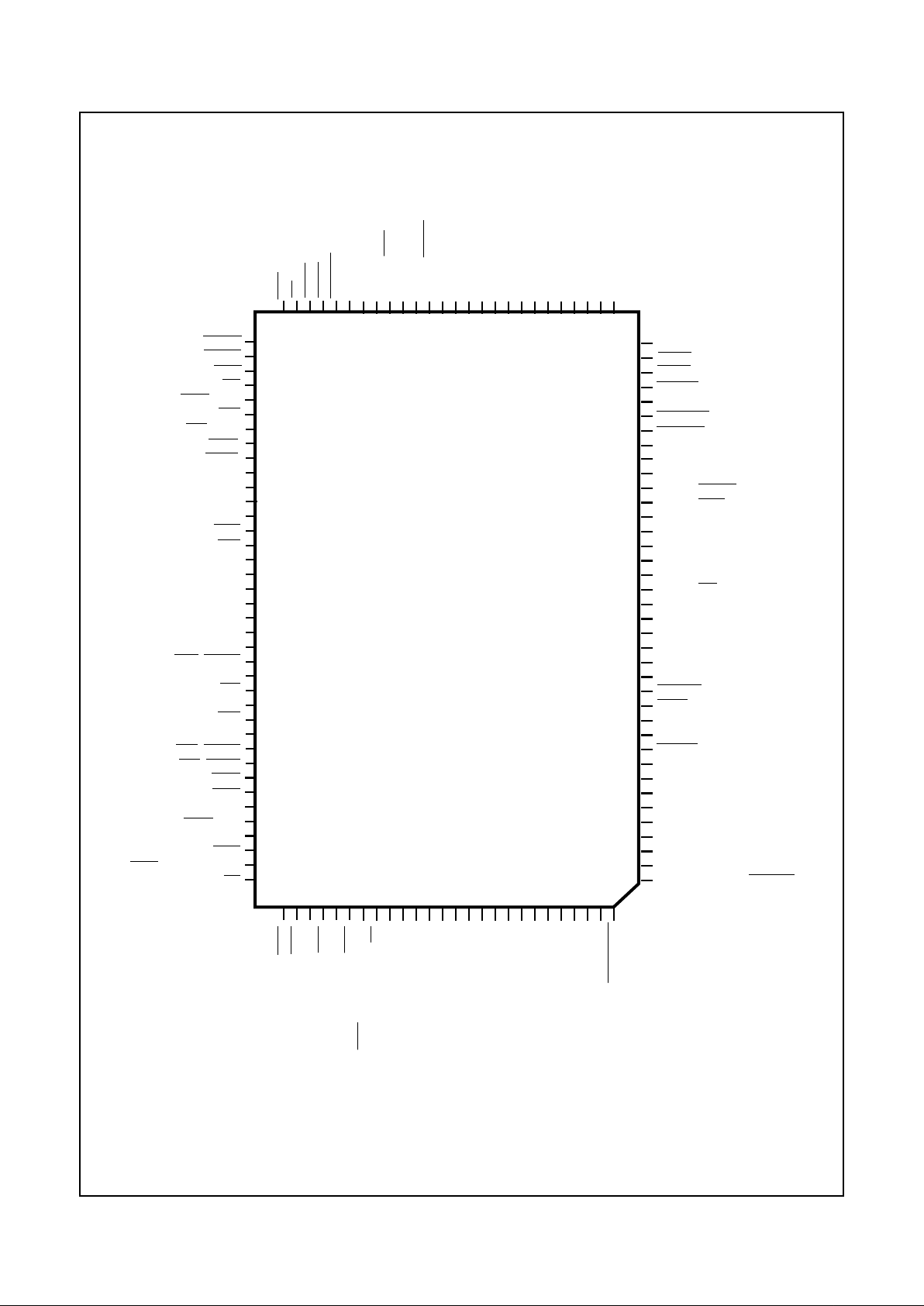

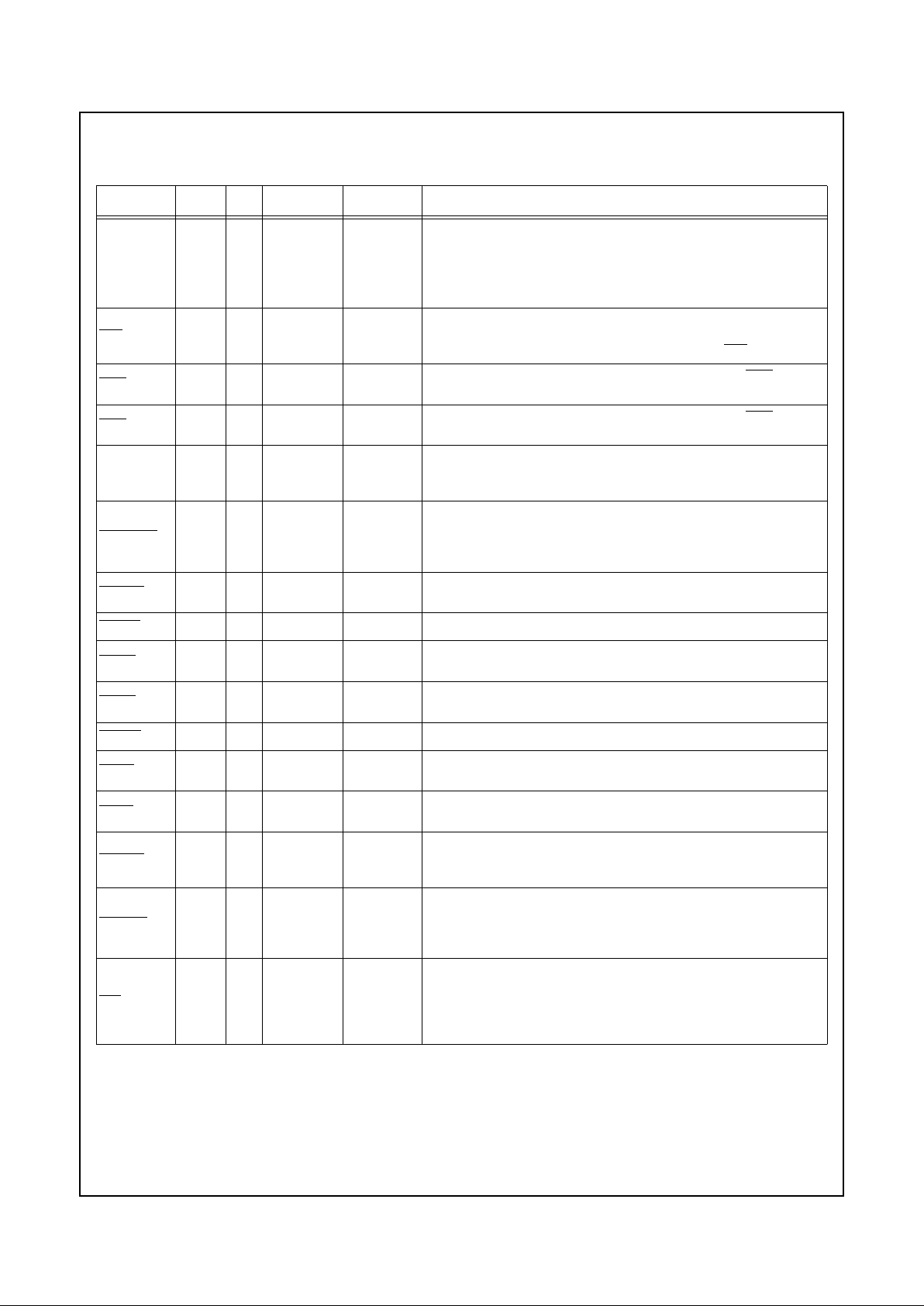

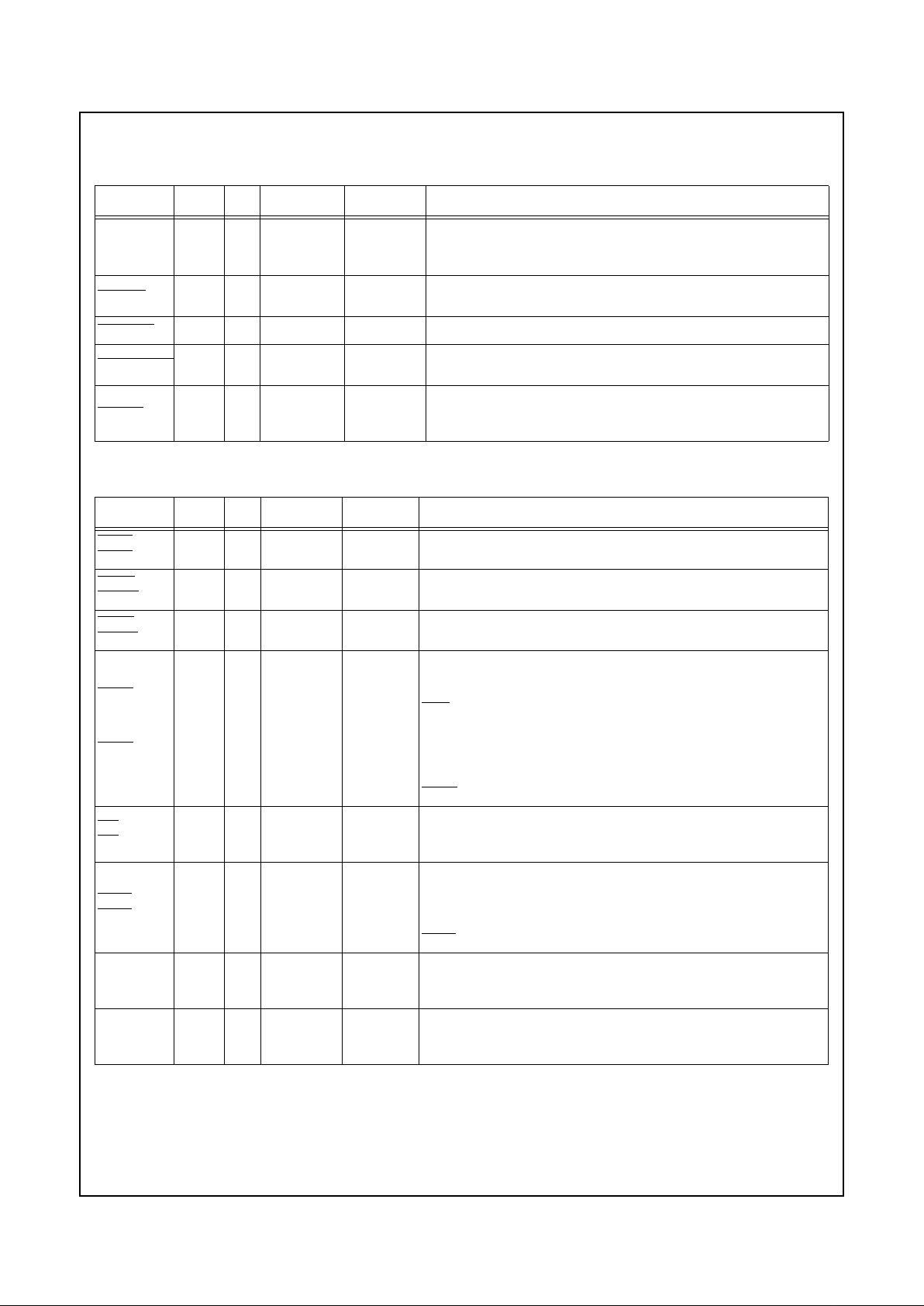

Block Diagram

System Wake-Up

Serial Port 2

IEEE 1284

Wake-Up

Parallel Port

Ports

Keyboard

& Mouse I/F

SCL

ACCESS.bus

Floppy Disk

Controller

Floppy Drive

Interface

Keyboard &

Serial Infrared

Interface Interface

Control

Events

Bus

Interface

LPC

Interface

I/O

3 Control

WATCHDOG

Timer

WDO

PWUREQ

Serial Port 1

Serial

Interface

Outputs

Fan Speed

Control & Monitor

Interface

Mouse Controller

with IR

GPIO Ports

3 Monitor

Inputs

SDA

Serial

IRQ

Parallel

IRQs

Interrupt

Parallel Port

Interface

SMI

Ports

Serializer

Power

Control

V

DD

V

BAT

V

SB

© 1999 National Semiconductor Corporation

ACCESS.bus® is a registered trademark of Digital Equipment Corporation.

I2C® is a registered trademark of Philips Corporation.

IBM®, MicroChannel®, PC-AT® and PS/2® are registered trademarks of International Business Machines Corporation.

Microsoft® and Windows® are registered trademarks of Microsoft Corporation.

TRI-STATE® is a registered trademark of National Semiconductor Corporation.

WATCHDOG‰ is a trademark of National Semiconductor Corporation.

SMBus® is a registered trademark of Intel Corporation.

2

www.national.com

Features

• Extended Wake-Up

— Legacy and ACPI power button support

— Direct power supply control in response to wake-up

events

— Power-fail recovery

• Protection

— Chassis intrusion detection (CHASI, CHASO)

— Chassis hood lock and unlock control

— Access lock to I/O ports (

XLOCK)

— GPIO pin attribute lock

— Pin configuration lock

• 51 General-Purpose I/O (GPIO) Ports

— 39 standard, with Assert IRQ/

SMI/PWUREQ for 23

ports

— 12 V

SB

-powered

— Programmable drive type for each output pin (open-

drain, push-pull or output disable)

— Programmable option for internal pull-up resistor on

each input pin

— Output lock option

— Input debounce mechanism

• Fan Speed Control and Fan Speed Monitor (FSCM)

— Supports different fan types

— Speed monitoring for three fans

❏ Digital filtering of the tachometer input signal

❏ Alarm for fan slower than programmable thresh-

old speed

❏ Alarm for fan stop

— Three speed control lines with Pulse Width Modula-

tion (PWM)

❏ Output signal in the range of 6 Hz to 93.75 KHz

❏ Duty cycle resolution of 1/256

• Interrupt Serializer

— 11 Parallel IRQs to Serial IRQ

— IRQ sharing with internal IRQs

• LPC System Interface

— Synchronous cycles, up to 33 MHz bus clock

— 8-bit I/O cycles

— Up to four DMA channels

— 8-bit DMA cycles

— Basic read, write and DMA bus cycles are 13 clock

cycles long

• PC99 and ACPI Compliant

— PnP Configuration Register structure

— Flexible resource allocation for all logical devices

❏ Relocatable base address

❏ 15 IRQ routing options

❏ 4 optional 8-bit DMA channels (where applicable)

• Floppy Disk Controller (FDC)

— Programmable write protect

— FM and MFM mode support

— Enhanced mode command for three-mode Floppy

Disk Drive (FDD) support

— Perpendicular recording drive support for 2.88 MB

— Burst and non-burst modes

— Full support for IBM Tape Drive register (TDR) im-

plementation of AT and PS/2 drive types

— 16-byte FIFO

— Software compatible with the PC8477, which con-

tains a superset of the FDC functions in the

microDP8473, the NEC microPD765A and the

N82077

— High-performance, digital separator

— Standard 5.25” and 3.5” FDD support

• Parallel Port

— Software or hardware control

— Enhanced Parallel Port (EPP) compatible with new

version EPP 1.9 and IEEE 1284 compliant

— EPP supportforversionEPP1.7 of the Xircom spec-

ification

— EPP supportas mode 4 of the Extended Capabilities

Port (ECP)

— IEEE 1284 compliant ECP, including level 2

— Selection of internal pull-up or pull-down resistor for

Paper End (PE) pin

— PCI bus utilization reduction by supporting a de-

mand DMA mode mechanism and a DMA fairness

mechanism

— Protection circuit that prevents damage to the paral-

lel port when a printer connected to it powers up or

is operated at high voltages, even if the device is in

power-down

— Output buffers that can sink and source 14 mA

• Serial Port 1 (UART1)

— Software compatible with the 16550A and the 16450

— Shadow register support for write-only bit monitoring

— UART data rates up to 1.5 Mbaud

• Serial Port 2 with Infrared (UART2)

— Software compatible with the 16550A and the 16450

— Shadow register support for write-only bit monitoring

— UART data rates up to 1.5 Mbaud

— HP-SIR

— ASK-IR option of SHARP-IR

— DASK-IR option of SHARP-IR

— Consumer Remote Control supports RC-5, RC-6,

NEC, RCA and RECS 80

— Non-standard DMA support − 1 or 2 channels

— PnP dongle support

3

Features (Continued)

www.national.com

• Keyboard and Mouse Controller (KBC)

— 8-bit microcontroller

— Software compatible with the 8042AH and PC87911

microcontrollers

— 2 KB custom-designed program ROM

— 256 bytes RAM for data

— Five programmable dedicated open-drain I/O lines

— Asynchronous access to two data registers and one

status register during normal operation

— Support for both interrupt and polling

— 93 instructions

— 8-bit timer/counter

— Support for binary and BCD arithmetic

— Operation at 8 MHz,12 MHz or 16 MHz (programma-

ble option)

— Can be customized by using the PC87323, which in-

cludes a RAM-based KBC as a development platform for KBC code

• ACCESS.bus Interface (ACB)

— Serial interfacecompatiblewith SMBus physical layer

— Compatible with Philips’ I2C

®

— ACB master and slave

— Supports polling and interrupt controlled operation

— Optional internal pull-up on SDA and SCL pins

• WATCHDOG Timer

— Times out the system based on user-programmable

time-out period

— System power-down capability for power saving

— User-defined trigger events to restart WATCHDOG

— Optional routing of WATCHDOG output on IRQ

and/or SMI lines

• System Wake-Up Control (SWC)

— Power-up request upon detection of Keyboard,

Mouse, RI1, RI2, RING activity and General-Purpose Input Events, as follows:

❏ Preprogrammed Keyboard or Mouse sequence

❏ External modem ring on serial port

❏ Ring pulse or pulse train on the

RING input signal

❏ Preprogrammed CEIR address in a preselected

standard (NEC, RCA or RC-5)

❏ General-Purpose Input Events

❏ IRQs of internal logical devices

— Optional routing of power-up request on IRQ, SMI

and/or

PWBTOUT

— Battery-backed event configuration

— Programmable V

SB

-powered output for blinking

LEDs (LED1, LED2) control

• Clock Sources

— 48 MHz clock input

— LPC clock, up to 33 MHz

— On-chip low frequency clock generator for wake-up

• Power Supplies

— 3.3V supply operation

— Main (V

DD

)

— Standby (V

SB

)

— Battery backup (V

BAT

)

— All pins are 5V tolerantand back-drive protected, ex-

cept LPC bus pins

• Strap Configuration

— Base Address (BADDR) strap to determine the base

address of the Index-Data register pair

— Test strap to force the device into test mode (re-

served for National Semiconductor use)

— Power Supply and LED Configuration (PSLDC0,1)

straps to determine the power suppy control functions and the V

SB

power-up defaults of LED2

— Power Supply On Polarity (PSONPOL) strap to set

PSON active state and output type

4

www.national.com

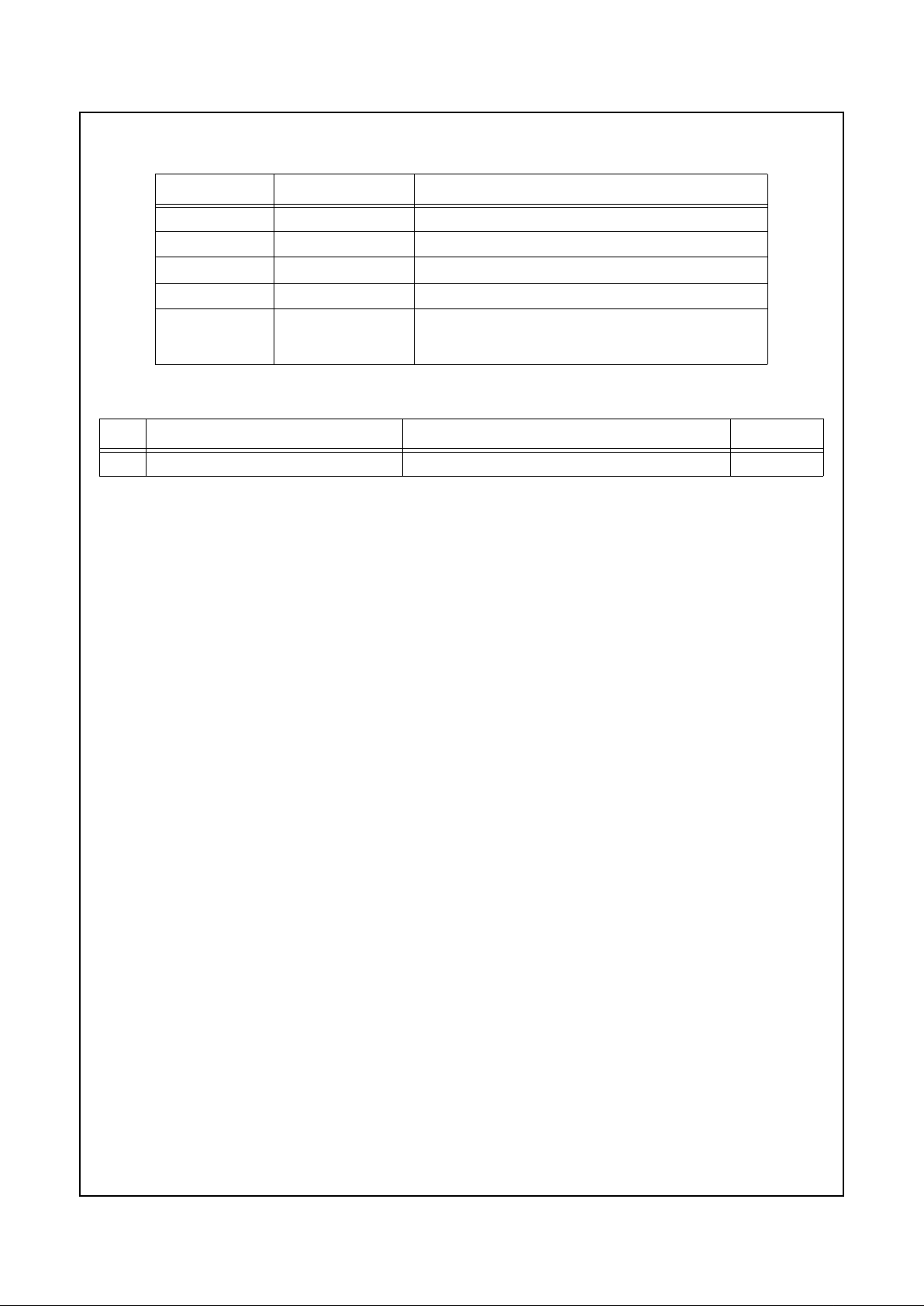

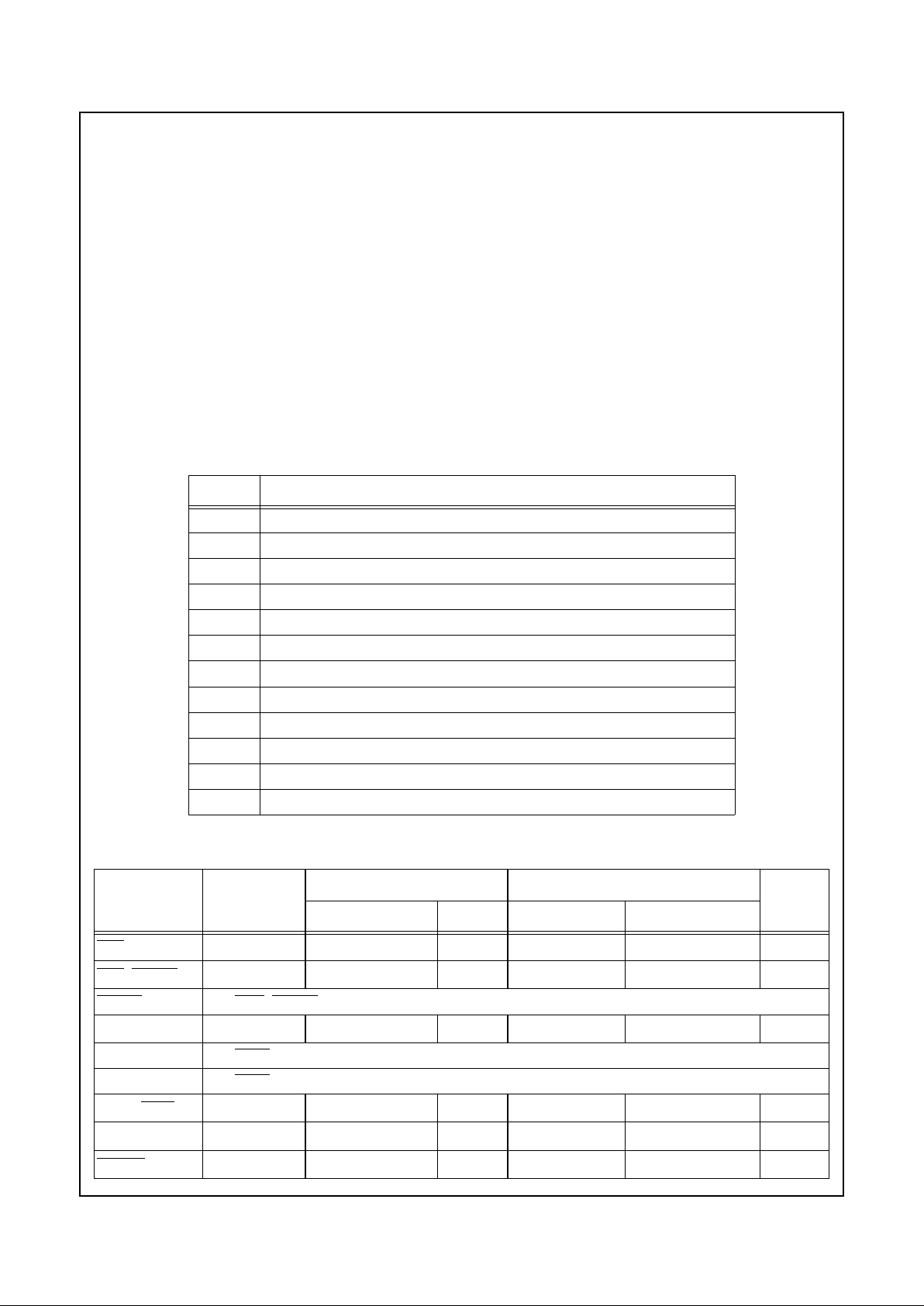

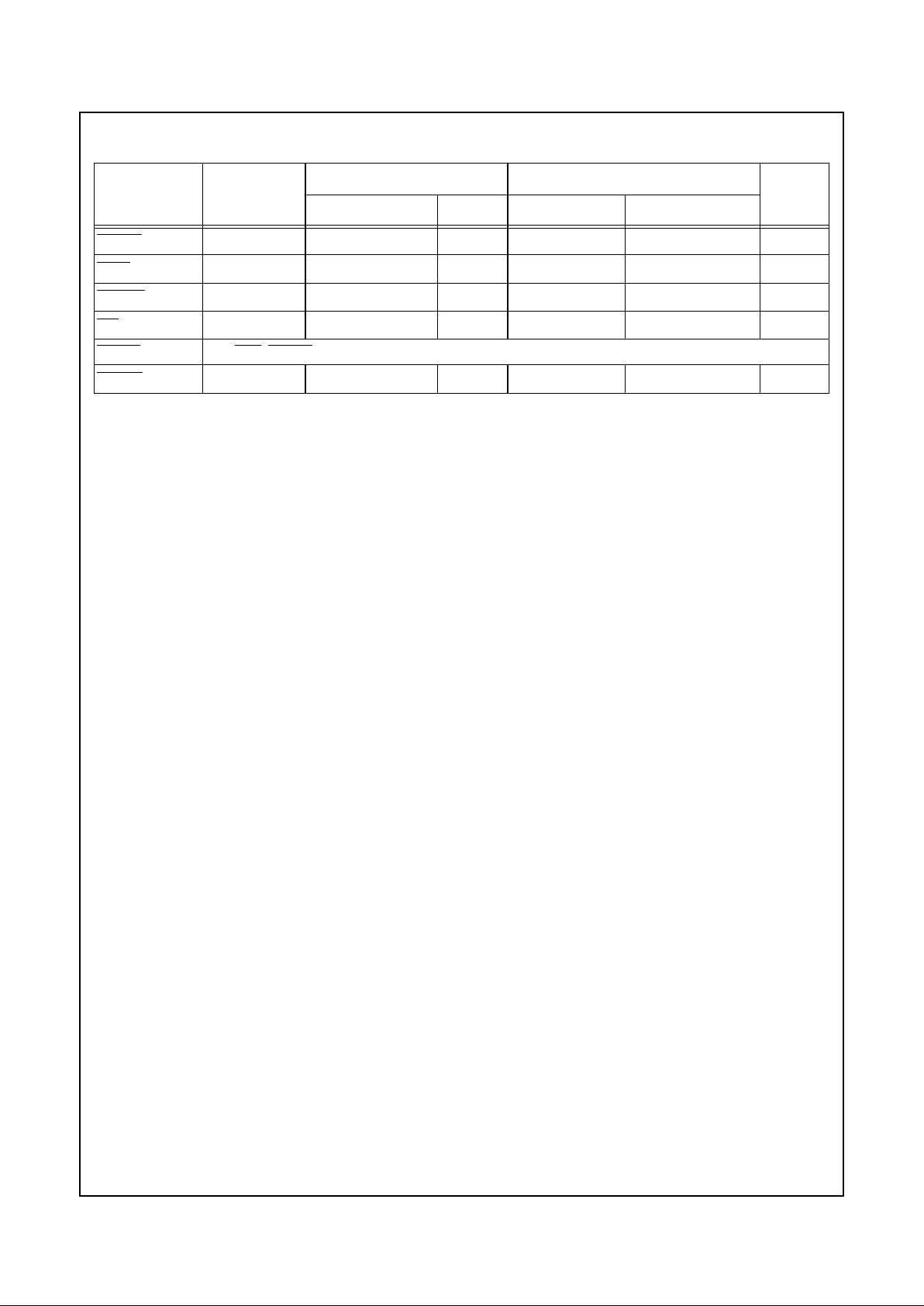

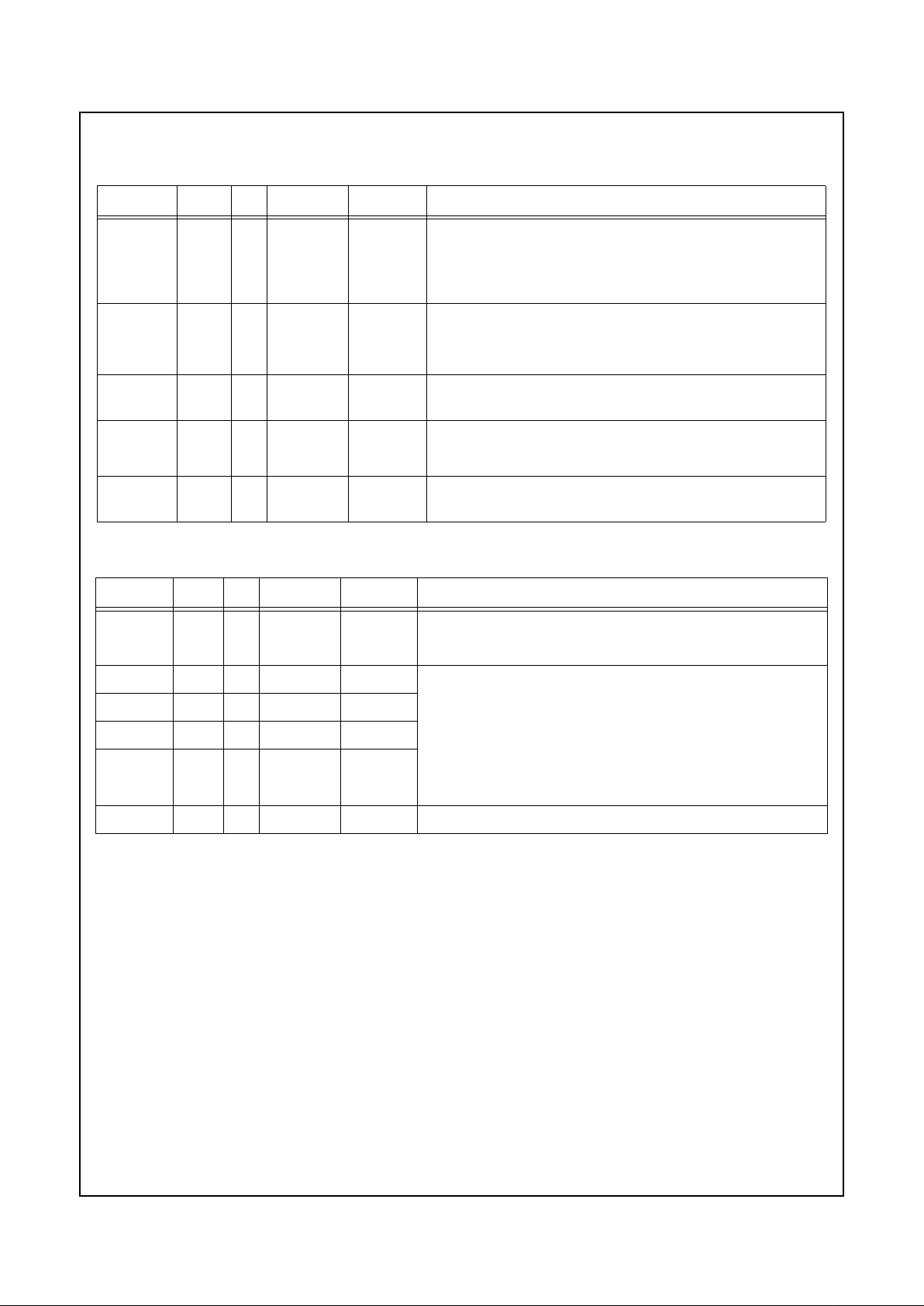

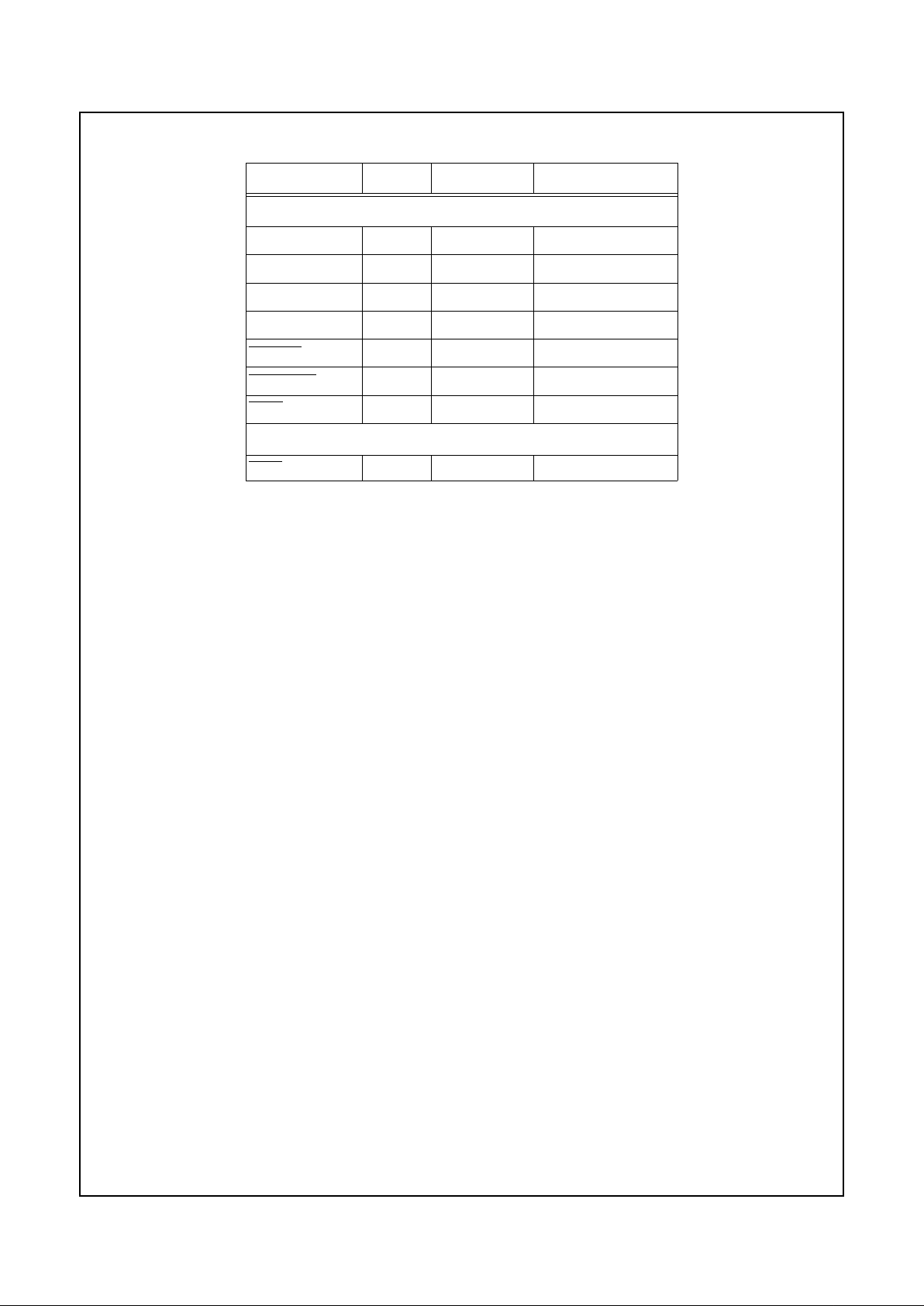

Datasheet Revision Record

Revision Date Status Comments

September 1998 Draft 0.1 Specifcation subject to change without notice

September 1998 Draft 0.2 Specifcation subject to change without notice

October 1988 Draft 0.3 Specification subject to change without notice

October 1998 Draft 0.4 Specification subject to change without notice

January 1999 Preliminary 1.0 Specification subject to change without notice; Power

Supply Control and LED sections in Chapter 2 are

incomplete

Item Topic Change/Correction Location

5

www.national.com

Table of Contents

Datasheet Revision Record....................................................................................................................4

1.0 Signal/Pin Connection and Description

1.1 CONNECTION DIAGRAM .........................................................................................................12

1.2 BUFFER TYPES AND SIGNAL/PIN DIRECTORY ....................................................................13

1.3 PIN MULTIPLEXING .................................................................................................................18

1.4 DETAILED SIGNAL/PIN DESCRIPTIONS ................................................................................20

1.4.1 ACCESS.bus Interface (ACB) ....................................................................................20

1.4.2 Bus Interface ...............................................................................................................20

1.4.3 Clock ............................................................................................................................20

1.4.4 Fan Speed Control and Monitor (FSCM) .....................................................................20

1.4.5 Floppy Disk Controller (FDC) ......................................................................................21

1.4.6 Game Port ..................................................................................................................22

1.4.7 General-Purpose Input/Output (GPIO) Ports ...............................................................22

1.4.8 Infrared (IR) .................................................................................................................22

1.4.9 Keyboard and Mouse Controller (KBC) .....................................................................23

1.4.10 Musical Instrument Digital Interface (MIDI) Port ..........................................................23

1.4.11 Parallel Port ...............................................................................................................24

1.4.12 Power and Ground .....................................................................................................25

1.4.13 Protection ....................................................................................................................25

1.4.14 Serial Port 1 and Serial Port 2 .....................................................................................25

1.4.15 Strap Configuration ......................................................................................................26

1.4.16 System Wake-Up Control ............................................................................................26

1.4.17 WATCHDOG Timer (WDT) .........................................................................................27

1.5 INTERNAL PULL-UP AND PULL-DOWN RESISTORS ............................................................28

2.0 Device Architecture and Configuration

2.1 OVERVIEW ...............................................................................................................................30

2.2 CONFIGURATION STRUCTURE AND ACCESS .....................................................................30

2.2.1 The Index-Data Register Pair ......................................................................................30

2.2.2 Banked Logical Device Registers Structure ................................................................32

2.2.3 Standard Logical Device Configuration Register Definitions .......................................33

2.2.4 Standard Configuration Registers ...............................................................................35

2.2.5 Default Configuration Setup ........................................................................................36

2.2.6 Power States ...............................................................................................................36

2.2.7 Address Decoding .......................................................................................................37

2.3 PROTECTION ...........................................................................................................................37

2.3.1 Chassis Intrusion Detection .........................................................................................37

2.3.2 Pin Configuration Lock ................................................................................................37

2.3.3 GPIO Pin Function Lock ..............................................................................................38

2.4 POWER SUPPLY CONTROL (PSC) .........................................................................................38

2.5 LED OPERATION AND STATES ..............................................................................................40

2.6 POWER SUPPLY CONTROL AND LED CONFIGURATION ....................................................40

2.7 REGISTER TYPE ABBREVIATIONS ........................................................................................41

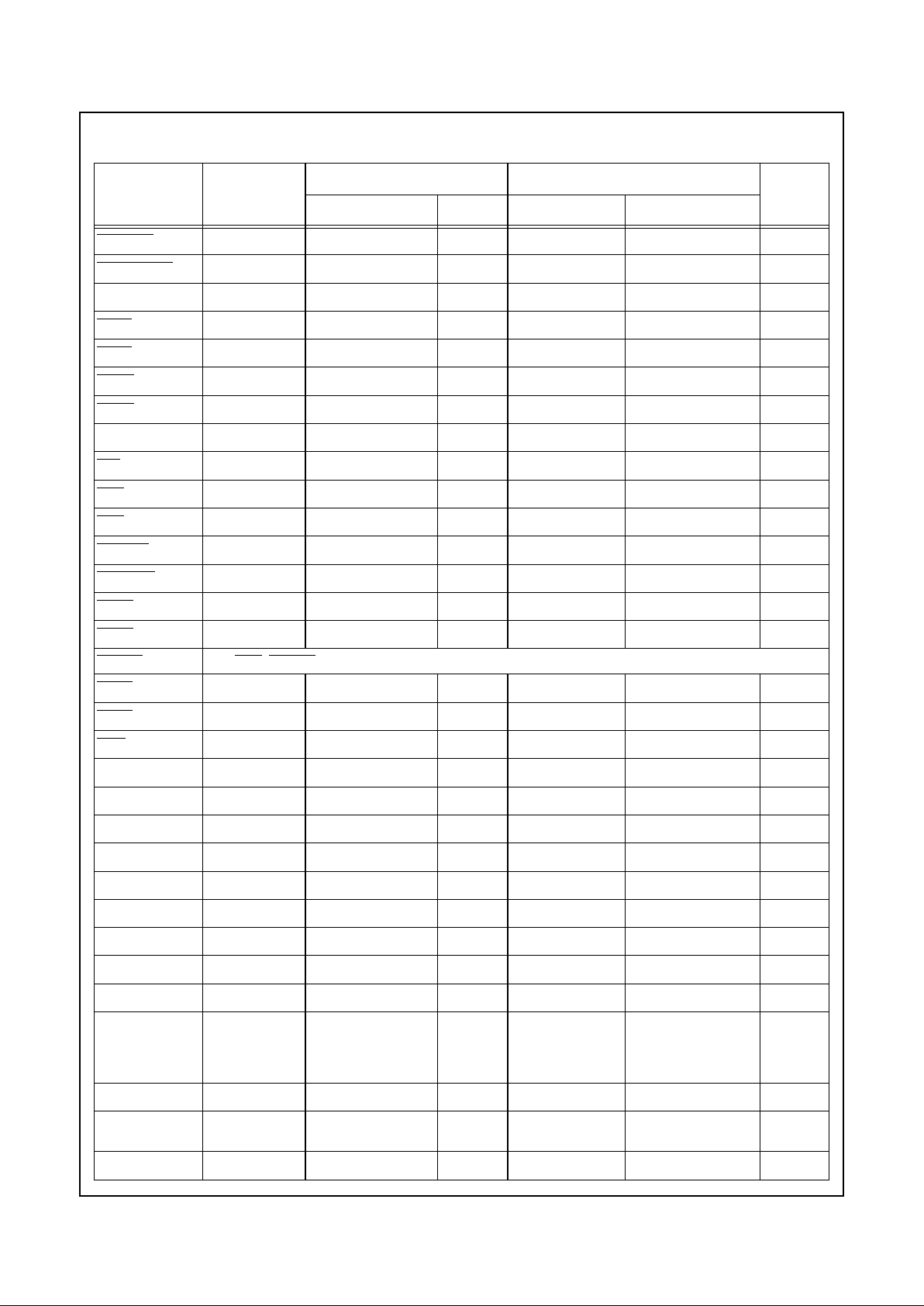

Table of Contents (Continued)

6

www.national.com

2.8 SUPERI/O CONFIGURATION REGISTERS .............................................................................41

2.8.1 SuperI/O ID Register (SID) ..........................................................................................42

2.8.2 SuperI/O Configuration 1 Register (SIOCF1) ..............................................................42

2.8.3 SuperI/O Configuration 2 Register (SIOCF2) ..............................................................43

2.8.4 SuperI/O Configuration 3 Register (SIOCF3) ..............................................................44

2.8.5 SuperI/O Configuration 4 Register (SIOCF4) ..............................................................45

2.8.6 SuperI/O Configuration 5 Register (SIOCF5) ..............................................................46

2.8.7 SuperI/O Revision ID Register (SRID) ........................................................................46

2.8.8 SuperI/O Configuration 8 Register (SIOCF8) ..............................................................47

2.8.9 SuperI/O Configuration A Register (SIOCFA) .............................................................48

2.8.10 SuperI/O Configuration B Register (SIOCFB) .............................................................49

2.8.11 SuperI/O Configuration C Register (SIOCFC) .............................................................50

2.8.12 SuperI/O Configuration D Register (SIOCFD) .............................................................51

2.9 FLOPPY DISK CONTROLLER (FDC) CONFIGURATION ........................................................52

2.9.1 General Description .....................................................................................................52

2.9.2 Logical Device 0 (FDC) Configuration .........................................................................52

2.9.3 FDC Configuration Register ........................................................................................53

2.9.4 Drive ID Register .........................................................................................................54

2.10 PARALLEL PORT CONFIGURATION ......................................................................................55

2.10.1 General Description .....................................................................................................55

2.10.2 Logical Device 1 (PP) Configuration ............................................................................56

2.10.3 Parallel Port Configuration Register ............................................................................56

2.11 SERIAL PORT 2 CONFIGURATION .........................................................................................57

2.11.1 General Description .....................................................................................................57

2.11.2 Logical Device 2 (SP2) Configuration ..........................................................................57

2.11.3 Serial Port 2 Configuration Register ............................................................................57

2.12 SERIAL PORT 1 CONFIGURATION .........................................................................................58

2.12.1 Logical Device 3 (SP1) Configuration ..........................................................................58

2.12.2 Serial Port 1 Configuration Register ............................................................................58

2.13 SYSTEM WAKE-UP CONTROL (SWC) CONFIGURATION .....................................................59

2.13.1 Logical Device 4 (SWC) Configuration ........................................................................59

2.14 KEYBOARD AND MOUSE CONTROLLER (KBC) CONFIGURATION .....................................60

2.14.1 General Description .....................................................................................................60

2.14.2 Logical Devices 5 and 6 (Mouse and Keyboard) Configuration ..................................61

2.14.3 KBC Configuration Register ........................................................................................62

2.15 GENERAL-PURPOSE INPUT/OUTPUT (GPIO) PORTS CONFIGURATION ..........................63

2.15.1 General Description .....................................................................................................63

2.15.2 Implementation ............................................................................................................63

2.15.3 Logical Device 7 (GPIO) Configuration .......................................................................64

2.15.4 GPIO Pin Select Register ............................................................................................65

2.15.5 GPIO Pin Configuration Register .................................................................................66

2.15.6 GPIO Event Routing Register ......................................................................................67

2.16 ACCESS.BUS INTERFACE (ACB) CONFIGURATION ............................................................68

2.16.1 General Description .....................................................................................................68

2.16.2 Logical Device 8 (ACB) Configuration .........................................................................68

Table of Contents (Continued)

7

www.national.com

2.16.3 ACB Configuration Register ........................................................................................69

2.17 FAN SPEED CONTROL AND MONITOR (FSCM) CONFIGURATION .....................................70

2.17.1 General Description .....................................................................................................70

2.17.2 Logical Device 9 (FSCM) Configuration ......................................................................70

2.17.3 Fan Speed Control and Monitor Configuration 1 Register ...........................................71

2.18 WATCHDOG TIMER (WDT) CONFIGURATION ......................................................................72

2.18.1 Logical Device 10 (WDT) Configuration ......................................................................72

2.18.2 WATCHDOG Timer Configuration Register ................................................................72

2.19 GAME PORT (GMP) CONFIGURATION ..................................................................................73

2.19.1 Logical Device 11 (GMP) Configuration ......................................................................73

2.19.2 Game Port Configuration Register ..............................................................................73

2.20 MIDI PORT (MIDI) CONFIGURATION ......................................................................................74

2.20.1 Logical Device 12 (MIDI) Configuration .......................................................................74

2.20.2 MIDI Port Configuration Register .................................................................................74

3.0 System Wake-Up Control (SWC)

3.1 OVERVIEW ...............................................................................................................................75

3.2 FUNCTIONAL DESCRIPTION ..................................................................................................76

3.3 EVENT DETECTION .................................................................................................................77

3.3.1 Modem Ring ................................................................................................................77

3.3.2 Telephone Ring ...........................................................................................................77

3.3.3 Keyboard and Mouse Activity ......................................................................................78

3.3.4 CEIR Address ..............................................................................................................78

3.3.5 Standby General-Purpose Input Events ......................................................................78

3.3.6 GPIO-Triggered Events ...............................................................................................78

3.3.7 Software Event ............................................................................................................78

3.3.8 Module IRQ Wake-Up Event .......................................................................................79

3.4 SWC REGISTERS .....................................................................................................................79

3.4.1 SWC Register Map ......................................................................................................79

3.4.2 Wake-Up Events Status Register 0 (WK_STS0) .........................................................82

3.4.3 Wake-Up Events Status Register (WK_STS1) ............................................................83

3.4.4 Wake-Up Events Enable Register (WK_EN0) .............................................................84

3.4.5 Wake-Up Events Enable Register 1 (WK_EN1) ..........................................................85

3.4.6 Wake-Up Configuration Register (WK_CFG) ..............................................................86

3.4.7 Wake-Up Events Routing to SMI Enable Register 0 (WK_SMIEN0) ...........................87

3.4.8 Wake-Up Events Routing to SMI Enable Register 1 (WK_SMIEN1) ...........................88

3.4.9 Wake-Up Events Routing to IRQ Enable Register 0 (WK_IRQEN0) ...........................89

3.4.10 Wake-Up Events Routing to IRQ Enable Register 1 (WK_IRQEN1) ...........................90

3.4.11 Wake-Up Extension 1 Enable Register 0 (WK_X1EN0) ..............................................91

3.4.12 Wake-Up Extension 1 Enable Register 1 (WK_X1EN1) ..............................................92

3.4.13 Wake-Up Extension 2 Enable Register 0 (WK_X2EN0) ..............................................93

3.4.14 Wake-Up Extension 2 Enable Register 1 (WK_X2EN1) ..............................................94

3.4.15 Wake-Up Extension 3 Enable Register 0 (WK_X3EN0) ..............................................95

3.4.16 Wake-Up Extension 3 Enable Register 1 (WK_X3EN1) ..............................................96

3.4.17 PS/2 Keyboard and Mouse Wake-Up Events ..............................................................97

Table of Contents (Continued)

8

www.national.com

3.4.18 PS/2 Protocol Control Register (PS2CTL) ...................................................................98

3.4.19 Keyboard Data Shift Register (KDSR) .........................................................................98

3.4.20 Mouse Data Shift Register (MDSR) .............................................................................99

3.4.21 PS/2 Keyboard Key Data Registers (PS2KEY0 - PS2KEY7) ......................................99

3.4.22 CEIR Wake-Up Control Register (IRWCR) ...............................................................100

3.4.23 CEIR Wake-Up Address Register (IRWAD) ..............................................................101

3.4.24 CEIR Wake-Up Address Mask Register (IRWAM) ....................................................101

3.4.25 CEIR Address Shift Register (ADSR) ........................................................................102

3.4.26 CEIR Wake-Up Range 0 Registers ...........................................................................102

3.4.27 CEIR Wake-Up Range 1 Registers ...........................................................................103

3.4.28 CEIR Wake-Up Range 2 Registers ...........................................................................103

3.4.29 CEIR Wake-Up Range 3 Registers ...........................................................................104

3.4.30 Standby General-Purpose I/O (SBGPIO) Register Overview ....................................105

3.4.31 Standby GPIO Pin Select Register (SBGPSEL) ........................................................108

3.4.32 Standby GPIO Pin Configuration Register (SBGPCFG) ...........................................109

3.4.33 Standby GPIOE/GPIE Data Out Register 0 (SB_GPDO0) ........................................111

3.4.34 Standby GPIOE/GPIE Data In Register 0 (SB_GPDI0) ............................................111

3.4.35 Standby GPOS Data Out Register 1 (SB_GPDO1) ..................................................112

3.4.36 Standby GPIS Data In Register 1 (SB_GPDI1) .........................................................112

3.5 SWC REGISTER BITMAP .......................................................................................................113

4.0 Fan Speed Control

4.1 OVERVIEW .............................................................................................................................117

4.2 FUNCTIONAL DESCRIPTION ................................................................................................117

4.3 FAN SPEED CONTROL REGISTERS ....................................................................................118

4.3.1 Fan Speed Control Register Map ..............................................................................118

4.3.2 Fan Speed Control Pre-Scale Register (FCPSR) ......................................................118

4.3.3 Fan Speed Control Duty Cycle Register (FCDCR) ....................................................119

4.4 FAN SPEED CONTROL BITMAP ...........................................................................................119

5.0 Fan Speed Monitor

5.1 OVERVIEW .............................................................................................................................120

5.2 FUNCTIONAL DESCRIPTION ................................................................................................120

5.3 FAN SPEED MONITOR REGISTERS .....................................................................................121

5.3.1 Fan Speed Monitor Register Map ..............................................................................121

5.3.2 Fan Monitor Threshold Register (FMTHR) ................................................................122

5.3.3 Fan Monitor Speed Register (FMSPR) ......................................................................122

5.3.4 Fan Monitor Control and Status Register (FMCSR) ..................................................122

5.4 FAN SPEED MONITOR BITMAP ............................................................................................123

6.0 General-Purpose Input/Output (GPIO) Port

6.1 OVERVIEW .............................................................................................................................124

6.2 BASIC FUNCTIONALITY ........................................................................................................125

6.2.1 Configuration Options ................................................................................................125

Table of Contents (Continued)

9

www.national.com

6.2.2 Operation ...................................................................................................................125

6.3 EVENT HANDLING AND SYSTEM NOTIFICATION ..............................................................126

6.3.1 Event Configuration ...................................................................................................126

6.3.2 System Notification ....................................................................................................126

6.4 GPIO PORT REGISTERS .......................................................................................................127

6.4.1 GPIO Pin Configuration (GPCFG) Register ..............................................................128

6.4.2 GPIO Pin Event Routing (GPEVR) Register .............................................................129

6.4.3 GPIO Port Runtime Register Map .............................................................................129

6.4.4 GPIO Data Out Register (GPDO) ..............................................................................130

6.4.5 GPIO Data In Register (GPDI) ..................................................................................130

6.4.6 GPIO Event Enable Register (GPEVEN) ..................................................................131

6.4.7 GPIO Event Status Register (GPEVST) ....................................................................131

7.0 WATCHDOG Timer (WDT)

7.1 OVERVIEW .............................................................................................................................132

7.2 FUNCTIONAL DESCRIPTION ................................................................................................132

7.3 WATCHDOG TIMER REGISTERS .........................................................................................133

7.3.1 WATCHDOG Timer Register Map .............................................................................133

7.3.2 WATCHDOG Timeout Register (WDTO) ..................................................................133

7.3.3 WATCHDOG Mask Register (WDMSK) ....................................................................134

7.3.4 WATCHDOG Status Register (WDST) ......................................................................135

7.4 WATCHDOG TIMER REGISTER BITMAP .............................................................................135

8.0 ACCESS.bus Interface (ACB)

8.1 OVERVIEW .............................................................................................................................136

8.2 FUNCTIONAL DESCRIPTION ................................................................................................136

8.2.1 Data Transactions .....................................................................................................136

8.2.2 Start and Stop Conditions ..........................................................................................136

8.2.3 Acknowledge (ACK) Cycle ........................................................................................137

8.2.4 Acknowledge after Every Byte Rule ..........................................................................138

8.2.5 Addressing Transfer Formats ....................................................................................138

8.2.6 Arbitration on the Bus ................................................................................................138

8.2.7 Master Mode ..............................................................................................................139

8.2.8 Slave Mode ................................................................................................................141

8.2.9 Configuration .............................................................................................................141

8.3 ACB REGISTERS ....................................................................................................................142

8.3.1 ACB Register Map .....................................................................................................142

8.3.2 ACB Serial Data Register (ACBSDA) ........................................................................142

8.3.3 ACB Status Register (ACBST) ..................................................................................143

8.3.4 ACB Control Status Register (ACBCST) ...................................................................144

8.3.5 ACB Control Register 1 (ACBCTL1) ..........................................................................145

8.3.6 ACB Own Address Register (ACBADDR) .................................................................146

8.3.7 ACB Control Register 2 (ACBCTL2) ..........................................................................146

8.4 ACB REGISTER BITMAP ........................................................................................................147

Table of Contents (Continued)

10

www.national.com

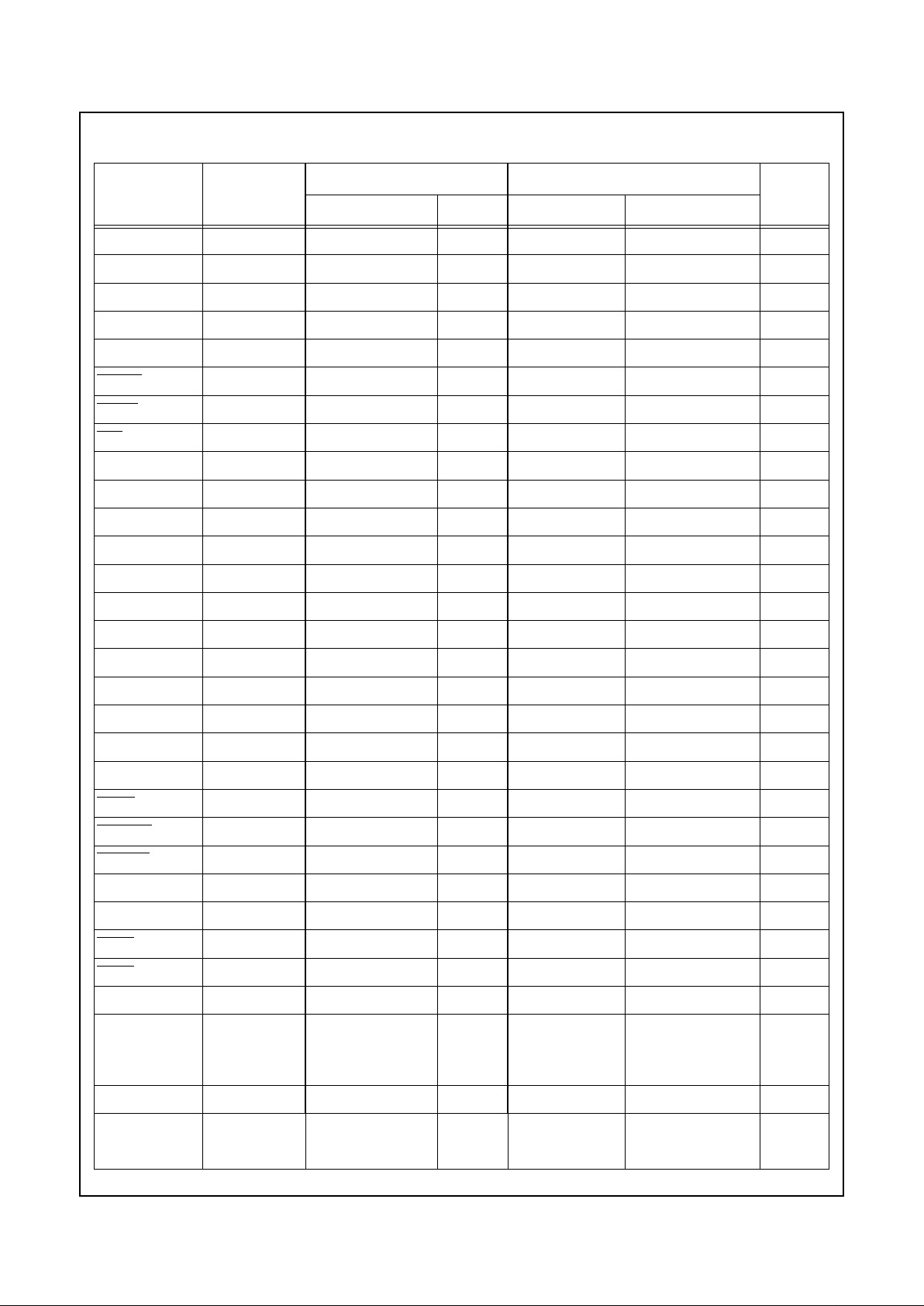

9.0 Legacy Functional Blocks

9.1 KEYBOARD AND MOUSE CONTROLLER (KBC) ..................................................................149

9.1.1 General Description ...................................................................................................149

9.1.2 KBC Register Map .....................................................................................................149

9.1.3 KBC Bitmap Summary ...............................................................................................149

9.2 FLOPPY DISK CONTROLLER (FDC) .....................................................................................150

9.2.1 General Description ...................................................................................................150

9.2.2 FDC Register Map .....................................................................................................150

9.2.3 FDC Bitmap Summary ...............................................................................................151

9.3 PARALLEL PORT ....................................................................................................................152

9.3.1 General Description ...................................................................................................152

9.3.2 Parallel Port Register Map .........................................................................................152

9.3.3 Parallel Port Bitmap Summary ..................................................................................153

9.4 UART FUNCTIONALITY (SP1 AND SP2) ...............................................................................155

9.4.1 General Description ...................................................................................................155

9.4.2 UART Mode Register Bank Overview .......................................................................155

9.4.3 SP1 and SP2 Register Maps for UART Functionality ................................................156

9.4.4 SP1 and SP2 Bitmap Summary for UART Functionality ...........................................158

9.5 IR FUNCTIONALITY (SP2) .....................................................................................................160

9.5.1 General Description ...................................................................................................160

9.5.2 IR Mode Register Bank Overview .............................................................................160

9.5.3 SP2 Register Map for IR Functionality ......................................................................161

9.5.4 SP2 Bitmap Summary for IR Functionality ................................................................162

10.0 Device Characteristics

10.1 GENERAL DC ELECTRICAL CHARACTERISTICS ...............................................................164

10.1.1 Recommended Operating Conditions .......................................................................164

10.1.2 Absolute Maximum Ratings .......................................................................................164

10.1.3 Capacitance ..............................................................................................................164

10.1.4 Power Consumption under Recommended Operating Conditions ............................165

10.2 DC CHARACTERISTICS OF PINS, BY I/O BUFFER TYPES ................................................165

10.2.1 Input, CMOS Compatible ...........................................................................................165

10.2.2 Input, PCI 3.3V ..........................................................................................................165

10.2.3 Input, SMBus Compatible ..........................................................................................166

10.2.4 Input, Strap Pin ..........................................................................................................166

10.2.5 Input, TTL Compatible ...............................................................................................166

10.2.6 Input, TTL Compatible with Schmitt Trigger ..............................................................166

10.2.7 Output, PCI 3.3V .......................................................................................................167

10.2.8 Output, Totem-Pole Buffer .........................................................................................167

10.2.9 Output, Open-Drain Buffer .........................................................................................167

10.2.10 Exceptions .................................................................................................................167

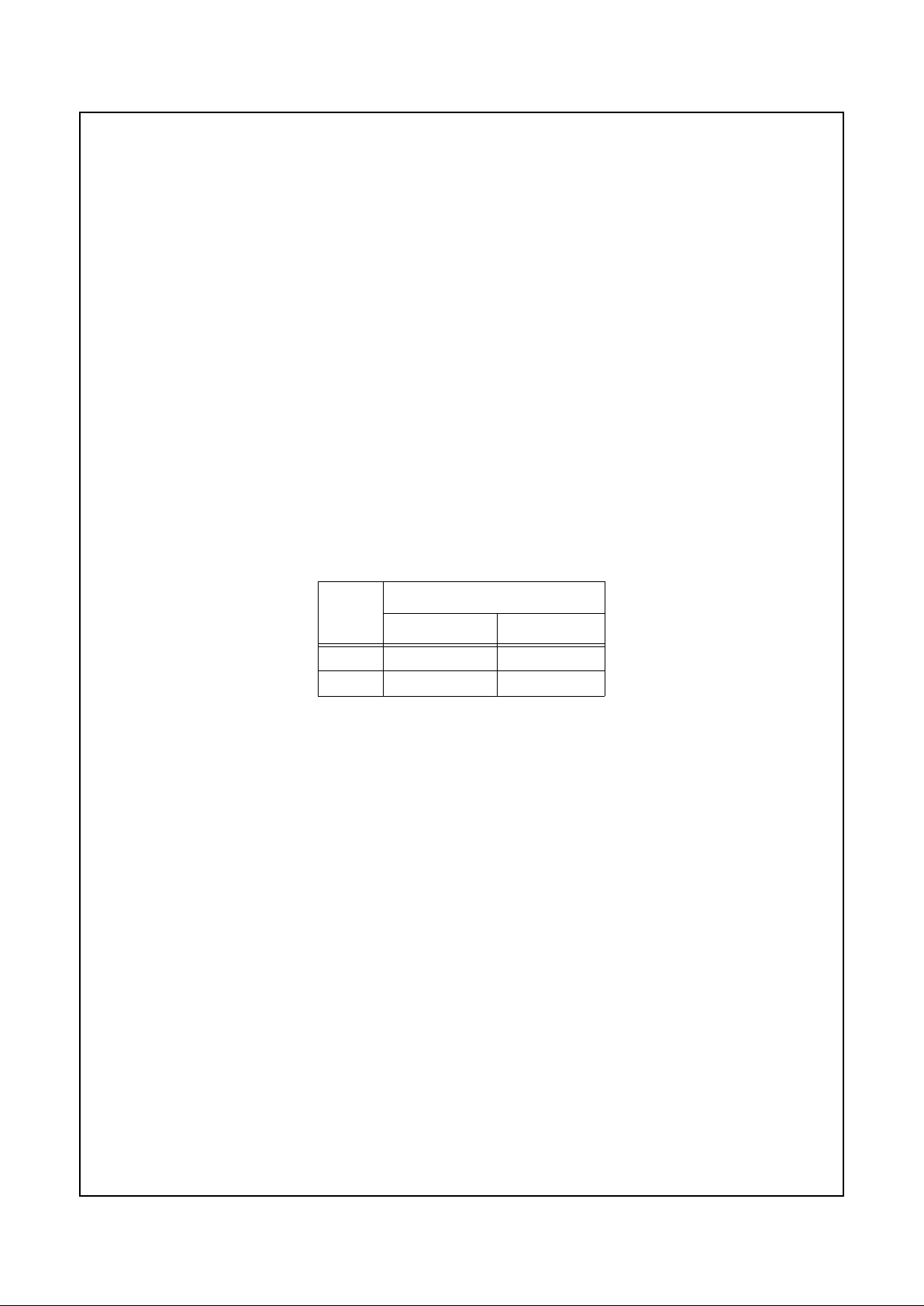

10.3 INTERNAL RESISTORS .........................................................................................................168

10.3.1 Pull-Up Resistor .........................................................................................................168

10.3.2 Pull-Down Resistor ....................................................................................................168

Table of Contents (Continued)

11

www.national.com

10.4 AC ELECTRICAL CHARACTERISTICS ..................................................................................169

10.4.1 AC Test Conditions ....................................................................................................169

10.4.2 Clock Timing ..............................................................................................................169

10.4.3 LCLK and LRESET ....................................................................................................170

10.4.4 LPC and SERIRQ Signals .........................................................................................171

10.4.5 Serial Port, Sharp-IR, SIR and Consumer Remote Control Timing ...........................172

10.4.6 Modem Control Timing ..............................................................................................173

10.4.7 FDC Write Data Timing .............................................................................................173

10.4.8 FDC Drive Control Timing .........................................................................................174

10.4.9 FDC Read Data Timing .............................................................................................174

10.4.10 Standard Parallel Port Timing ....................................................................................175

10.4.11 Enhanced Parallel Port Timing ..................................................................................175

10.4.12 Extended Capabilities Port (ECP) Timing ..................................................................176

12

www.national.com

1.0 Signal/Pin Connection and Description

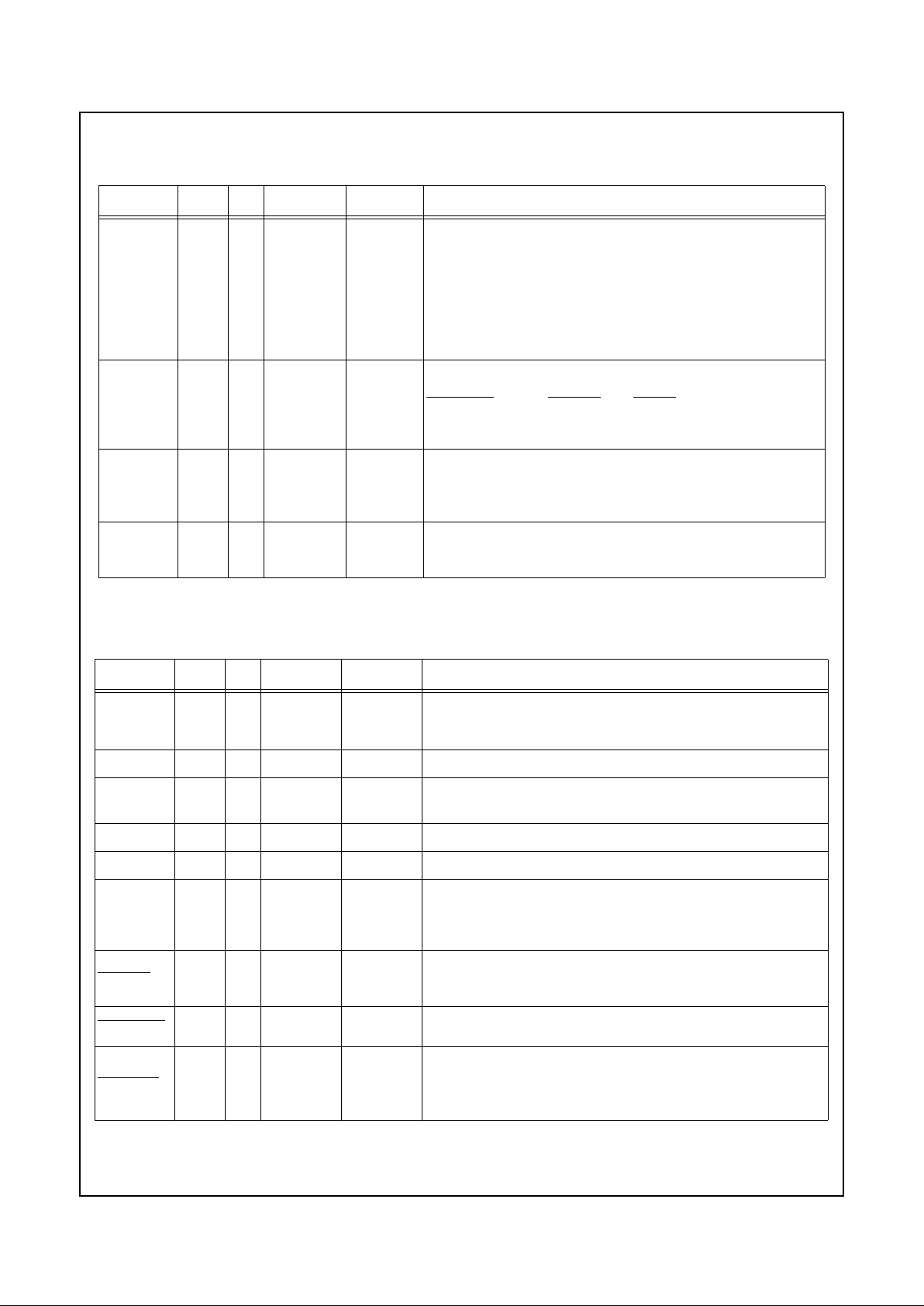

1.1 CONNECTION DIAGRAM

Plastic Quad Flatpack (PQFP), JEDEC

xxx =Three character identifier for National data, and keyboard ROM and/or customer identification code

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

109

110

111

112

113

114

115

116

117

118

119

120

121

122

123

124

125

126

127

128

59585756555453525150494847464544424140

39

PC87364-xxx/VLA

PD7

VSS

VBAT

MTR0

SLCT

DIR

STEP

WDATA

DRATE0

TRK0

PE

WGATE

RDATA

WP

DENSEL

INDEX

GPIO17/

DR1/IRSL3

636261

60

43

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

101

102

103

104

105

106

107

108

31

32

33

34

35

36

37

38

GPIO43

GPIO42

VDD

VSB

PWUREQ

GPIO16/

MTR1/IRSL2

DR0

GPIO34/FANOUT2/

CHLOCK

GPIO01/FANOUT1

GPIO47

GPIO46

GPIO45

BUSY_WAIT

HDSEL

DSKCHG

GPIO44

ACK

ERR

AFD_DSTRB

PD1

STB_WRITE

INIT

PD6

PD5

PD4

PD3

SLIN_ASTRB

PD2

VSS

PD0

GPIO00/FANIN1

GPIO33/FANIN2/CHUNLOCK

VDD

VSS

VDD

VSS

VDD

CHASI

Note 1.

GPIOE1

GPIOE2/LED1

LAD1

LAD3

LAD2

LRESET

LCLK

LFRAME

LAD0

LDRQ

SERIRQ

GPIO32/PIRQ15/P16/IRSL1

DTR1_BOUT1/BADDR

RI1

DCD1

SOUT1/PSLDC0

DSR1

SIN1

RTS1/TEST

CTS1

DTR2_BOUT2/PSONPOL

RI2

DCD2

SOUT2/PSLDC1

DSR2

SIN2

RTS2

CTS2

GPIO13/SDA

GPIO14/WDO

KBDAT

KBCLK

MCLK

MDAT

KBRST/GPIO06

GA20/GPIO07

Order Number PC87364-xxx/VLA

See NS Package Number VLA128A

GPIO41

GPIOE3/LED2

GPIOE5/

CHASO

GPIO03/FANOUT0

GPIO02/FANIN0

GPIE6/IRRX2_IRSL0

GPIE7/IRRX1

GPO15/IRTX

GPIO10/SMI

GPIOE4/

RING

GPIO05/P17

GPIO04/P12

GPIO11/XLOCK

GPIO12/SCL

CLKIN

GPIOE0

SLPS5

GPIO40

NC

NC

GPO37

GPO36

GPIO27/PIRQ11

GPIO25/PIRQ9

GPIO26/PIRQ10

GPIO24/PIRQ7

GPIO23/PIRQ6

GPIO21/PIRQ4

GPIO22/PIRQ5

GPIO20/PIRQ3

GPIO30/PIRQ12

GPIO31/PIRQ14

PSON

/GPOS1

PWBTOUT/GPOS0

PWBTIN/GPIS2

SLPS3/GPIS3

NC

Note 1. For correct operation, this pin must be tied to VSS when not used.

1.0 Signal/Pin Connection and Description (Continued)

13

www.national.com

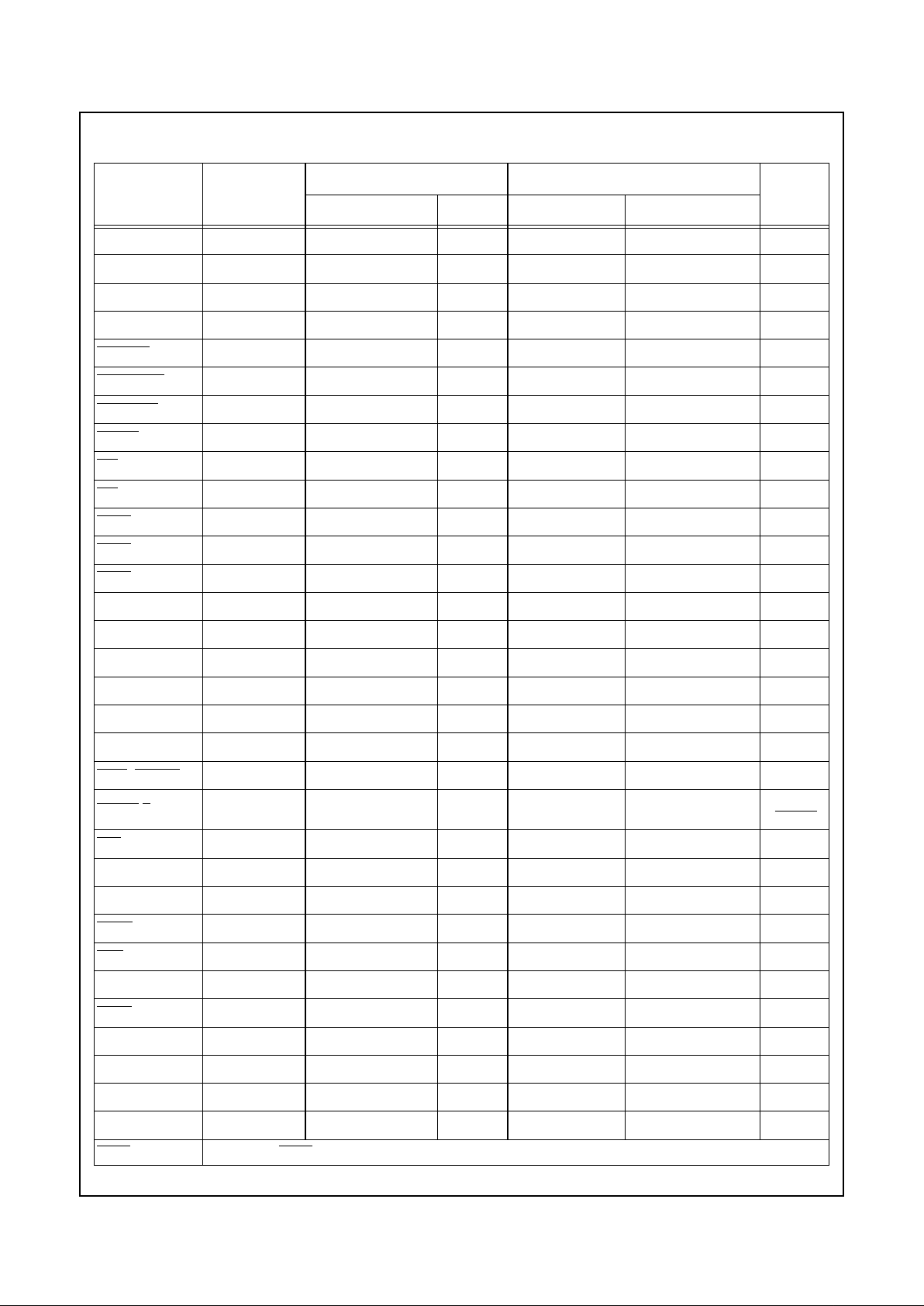

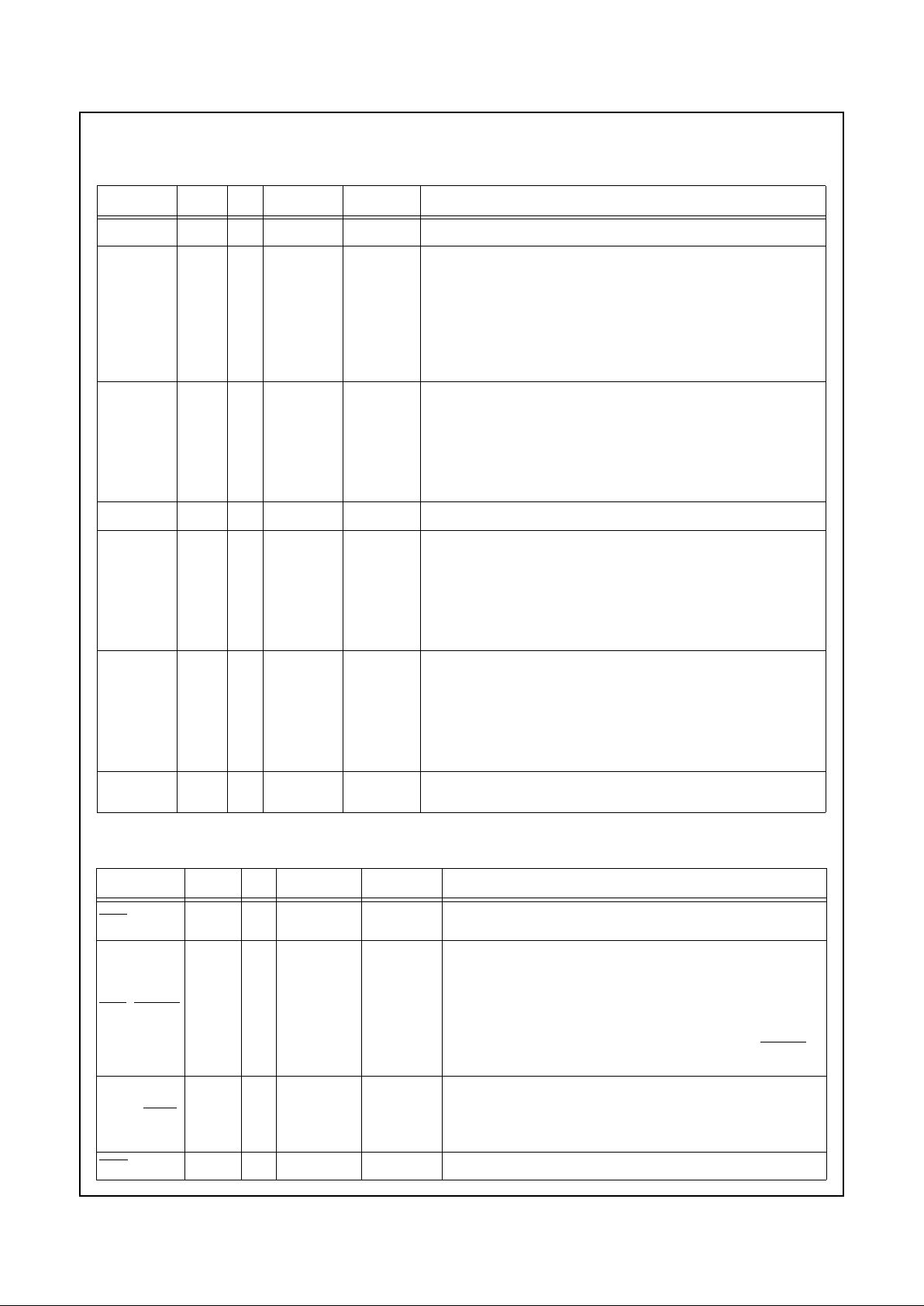

1.2 BUFFER TYPES AND SIGNAL/PIN DIRECTORY

Table 2 is an alphabetical list of all signals, cross-referenced to additional information for detailed functional descriptions,

electrical DC characteristics, and pin multiplexing. The signal DC characteristics are denoted by a buffer type symbol, described briefly below and in further detail in Section 10.2. The pin multiplexing information refers to two different types of

multiplexing:

●

MUX - Multiplexed, denoted by a slash (/) between pins in the diagram in Section 1.1. Pins are shared between two

different functions. Each function is associated with different board connectivity, and normally, the function selection

is determined by the board design and cannot be changed dynamically. The multiplexing options must be configured

by the BIOS upon power-up, in order to comply with the board implementation.

●

MM - Multiple Mode, denoted by an underscore (_) between pins in the diagram in Section 1.1. Pins have two or

more modes of operation within the same function. These modes are associated with the same external (board) connectivity. Mode selection may be controlled by the device driver, through the registers of the functional block, and do

not require a special BIOS setup upon power-up. These pins are not considered multiplexed pins from the SuperI/O

configuration perspective. The mode selection method (registers and bits) as well as the signal specification in each

mode, are described within the functional description of the relevant functional block.

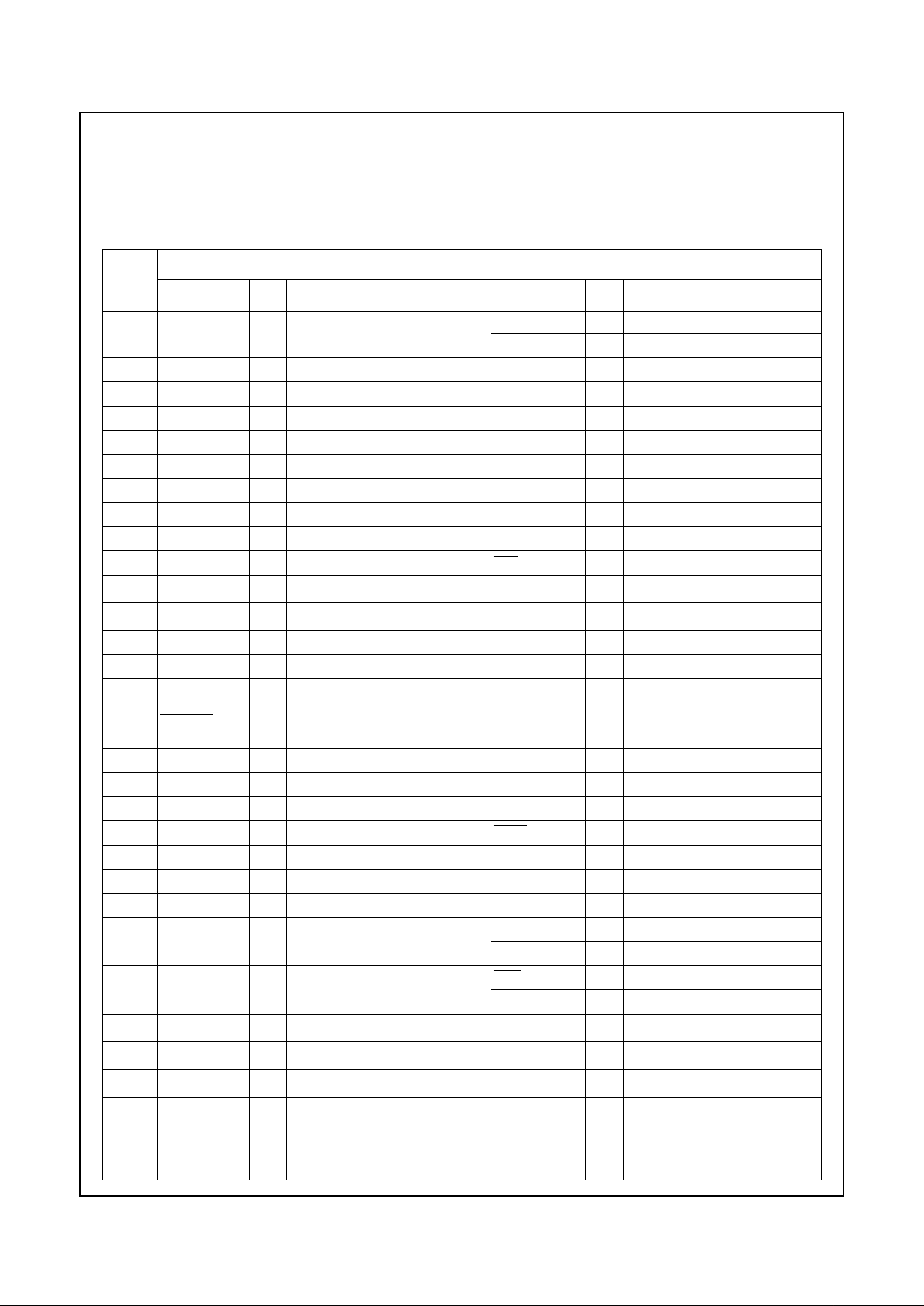

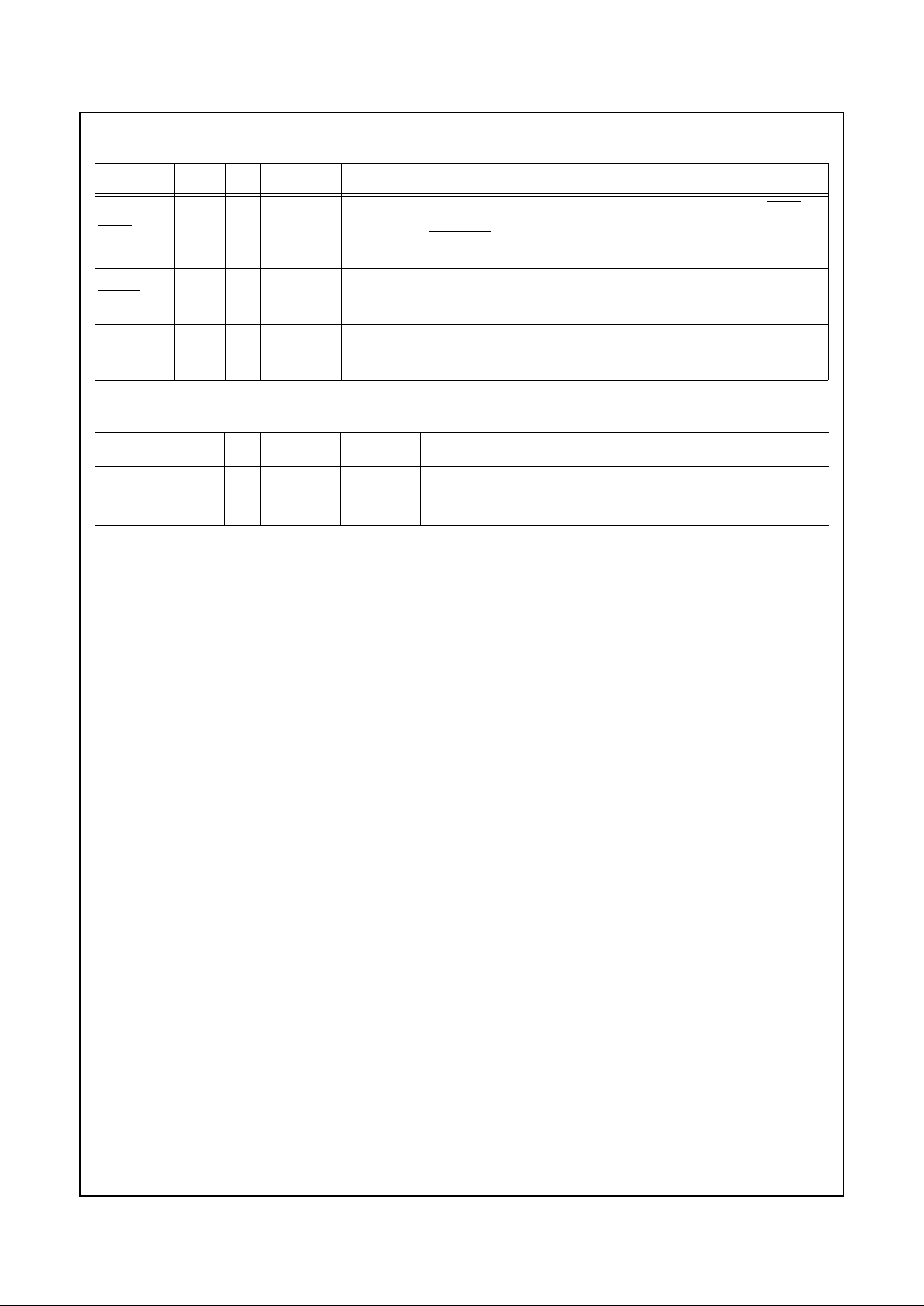

Table 2. SIgnal/Pin Directory

Table 1. Buffer Types

Symbol Description

IN

C

Input, CMOS compatible

IN

PCI

Input, PCI 3.3V

IN

SM

Input, SMBus compatible

IN

STRP

Input, Strap pin with weak pull-down during strap time

IN

T

Input, TTL compatible

IN

TS

Input, TTL compatible with Schmidt Trigger

IN

ULR

Input, with serial UL Resistor

O

PCI

Output, PCI 3.3V

O

p/n

Output, push-pull buffer that is capable of sourcingpmA and sinkingn mA

OD

n

Output, open-drain output buffer that is capable of sinkingn mA

PWR Power pin

GND Ground pin

Signal Pin(s)

Functional Group DC Characteristics

MUX

Name Section Buffer Type Section

ACK 79 Parallel Port 1.4.11

IN

T

10.2.5

AFD_DSTRB 93 Parallel Port 1.4.11

OD

14,O14/14

10.2.9, 10.2.8 MM

ASTRB See SLIN_ASTRB

BADDR 101 Strap Configuration 1.4.15

IN

STRP

10.2.4 MUX

BOUT1 See

DTR1_BOUT1

BOUT2 See

DTR2_BOUT2

BUSY_

WAIT 78 Parallel Port 1.4.11

IN

T

10.2.5 MM

CHASI 29 Protection 1.4.13

IN

C

10.2.1

CHASO 28 Protection 1.4.13

OD

6

10.2.9 MUX

1.0 Signal/Pin Connection and Description (Continued)

14

www.national.com

CHLOCK 1 Protection 1.4.11

O

12/12

14.2.9 MUX

CHUNLOCK 128 Protection 1.4.11

O

12/12

14.2.9 MUX

CLKIN 22 Clock 1.4.3

IN

T

10.2.5

CTS1 100 Serial Port 1 1.4.14

IN

TS

10.2.6

CTS2 108 Serial Port 2 1.4.14

IN

TS

10.2.6

DCD1 95 Serial Port 1 1.4.14

IN

TS

10.2.6

DCD2 103 Serial Port 2 1.4.14

IN

TS

10.2.6

DENSEL 75 FDC 1.4.5

O

2/12

10.2.8

DIR 68 FDC 1.4.5

OD

12,O2/12

10.2.9, 10.2.8

DR0 70 FDC 1.4.5

OD

12,O2/12

10.2.9, 10.2.8

DR1 71 FDC 1.4.5

OD

12,O2/12

10.2.9, 10.2.8 MUX

DRATE0 74 FDC 1.4.5

O

3/6

10.2.8

DSKCHG 60 FDC 1.4.5

IN

T

10.2.5

DSR1 96 Serial Port 1 1.4.14

IN

TS

10.2.6

DSR2 104 Serial Port 2 1.4.14

IN

TS

10.2.6

DSTRB See AFD_DSTRB

DTR1_BOUT1 101 Serial Port 1 1.4.14

O

3/6

10.2.8 MUX, MM

DTR2_BOUT2 109 Serial Port 2 1.4.14

O

3/6

10.2.8 MUX, MM

ERR 91 Parallel Port 1.4.11

IN

T

10.2.5

FANIN0 4 Fan Speed 1.4.4

IN

TS

10.2.6 MUX

FANIN1 2 Fan Speed 1.4.4

IN

TS

10.2.6 MUX

FANIN2 128 Fan Speed 1.4.4

IN

TS

14.2.6 MUX

FANOUT0 5 Fan Speed 1.4.4

O

2/14

10.2.8 MUX

FANOUT1 3 Fan Speed 1.4.4

O

2/14

10.2.8 MUX

FANOUT2 1 Fan Speed 1.4.4

O

2/14

14.2.8 MUX

GA20 (P21) 9 KBC 1.4.9

IN

T

,OD

2

10.2.5, 10.2.9 MUX

GPIE6-7 58-59 System Wake-Up 1.4.16

IN

TS

10.2.6 MUX

GPIO00-07 2-9 GPIO Port 1.4.7

IN

TS

,OD6,O

3/6

10.2.6, 10.2.9, 10.2.8 MUX

GPIO10

GPIO11-14

GPO15

GPIO16-17

21

53-56

57

69, 71

GPIO Port 1.4.7

IN

TS

,OD6,O

3/6

10.2.6, 10.2.9, 10.2.8 MUX

GPIO20-27 117-124 GPIO Port 1.4.7

IN

TS

,OD6,O

3/6

10.2.6, 10.2.9, 10.2.8 MUX

GPIO30-33

GPIO34

125-128

1

GPIO Port 1.4.7

IN

TS

,OD6,O

3/6

10.2.6, 10.2.9, 10.2.8 MUX

GP036-37 41-42 GPIO Port 1.4.6

OD

6,O3/6

12.2.9, 12.2.8

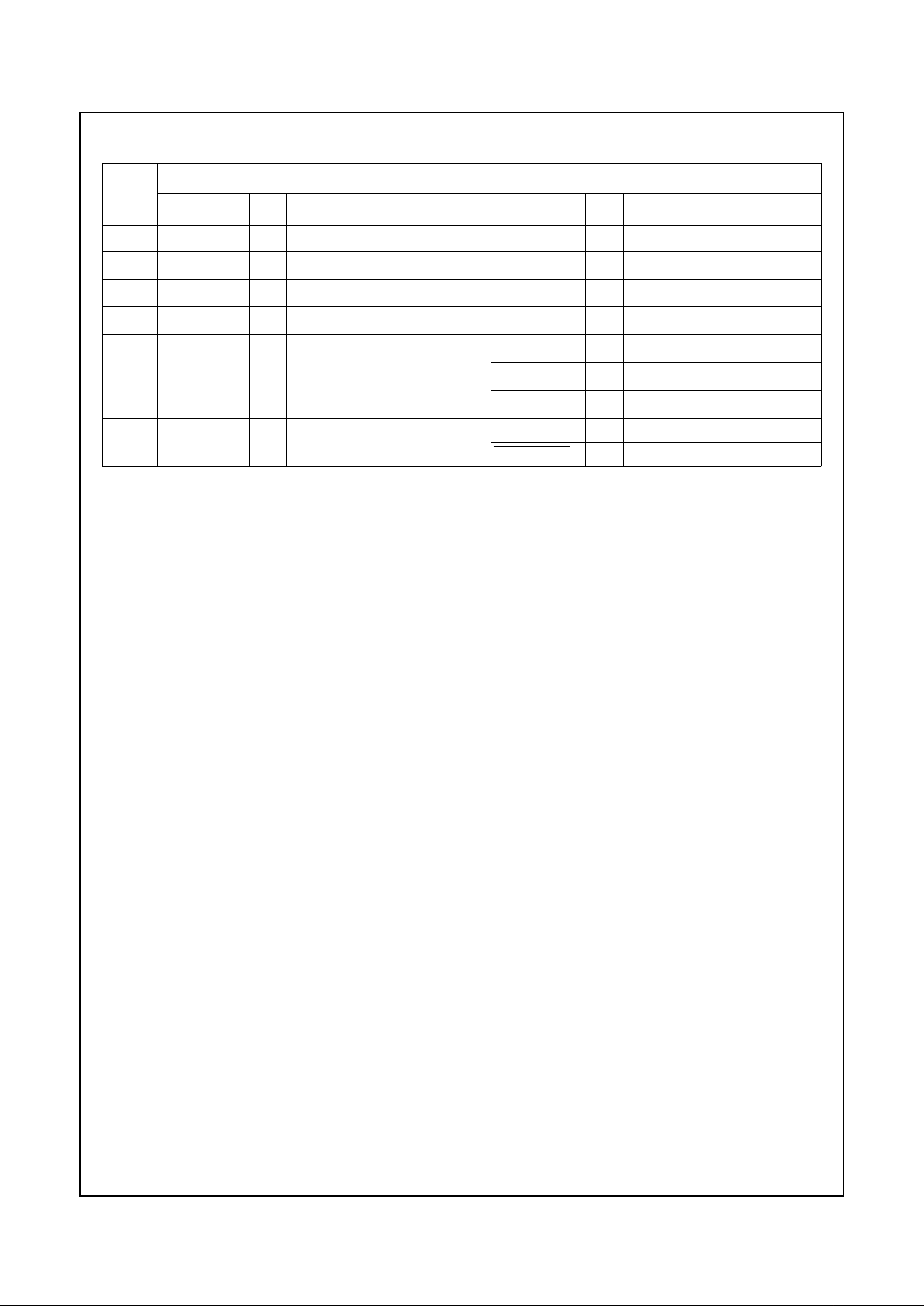

Signal Pin(s)

Functional Group DC Characteristics

MUX

Name Section Buffer Type Section

1.0 Signal/Pin Connection and Description (Continued)

15

www.national.com

GPIO40-47 43-50 GPIO Port 1.4.7

IN

TS

,OD6,O

3/6

10.2.6, 10.2.9, 10.2.8

GPIOE0-1 23-24 System Wake-Up 1.4.16

INTS,OD6,O

3/6

10.2.6, 10.2.9, 10.2.8

GPIOE2-5 25-28 System Wake-Up 1.4.16

IN

TS

,OD6,O

3/6

10.2.6, 10.2.9, 10.2.8 MUX

GPIS2-3 35-36 System Wake-Up 1.4.16

IN

TS

10.2.6 MUX

GPOS0-1 33-34 System Wake-Up 1.4.16

OD6,O

3/6

10.2.9, 10.2.8 MUX

HDSEL 61 FDC 1.4.5

OD

12,O2/12

10.2.9, 10.2.8

INDEX 73 FDC 1.4.5

IN

T

10.2.5

INIT 89 Parallel Port 1.4.11

OD

14,O14/14

10.2.9, 10.2.8

IRRX1 59 Infrared 1.4.8

IN

TS

10.2.6

MUX

IRRX2_IRSL0 58 Infrared 1.4.8

INTS,O

3/6

10.2.6, 10.2.8

MUX, MM

IRSL1 127 Infrared 1.4.8

IN

T,O3/6

10.2.5, 10.2.8 MUX

IRSL2 69 Infrared 1.4.8

INT,O

3/6

10.2.5, 10.2.8

MUX

IRSL3 71 Infrared 1.4.8

IN

T

10.2.5

MUX

IRTX 57 Infrared 1.4.8

O

6/12

10.2.8

MUX

KBCLK 111 KBC 1.4.9

IN

TS

,OD

14

10.2.6, 10.2.9

KBDAT 112 KBC 1.4.9

IN

TS

,OD

14

10.2.6, 10.2.9

KBRST (P20) 8 KBC 1.4.9

IN

TS

,OD

2

10.2.6, 10.2.9

MUX

LAD0-3 15-18 Bus Interface 1.4.2

IN

PCI,OPCI

10.2.2, 10.2.7

LED1, LED2 25, 26 System Wake-Up 1.4.16

O

12/12

10.2.8

MUX

LCLK 11 Bus Interface 1.4.2

IN

PCI

10.2.2

LDRQ 13 Bus Interface 1.4.2

O

PCI

10.2.7

LFRAME 14 Bus Interface 1.4.2

IN

PCI

10.2.2

LRESET 10 Bus Interface 1.4.2

IN

PCI

10.2.2

MCLK 13 KBC 1.4.9

IN

TS

,OD

14

10.2.6, 10.2.9

MDAT 114 KBC 1.4.9

IN

TS

,OD

14

10.2.6, 10.2.9

MTR0 72 FDC 1.4.5

OD

12,O2/12

10.2.9, 10.2.8

MTR1 69 FDC 1.4.5

OD

12,O2/12

10.2.9, 10.2.8

MUX

P12, P16, P17 6,127, 7 KBC 1.4.9

IN

T

,OD

2

10.2.5, 10.2.9

MUX

PD7-5

PD4-3,

PD2, PD1

PD0

80-82

85-86

88, 90

92

Parallel Port 1.4.11

IN

T

,OD14,O

14/14

10.2.5, 10.2.9, 10.2.8

PE 77 Parallel Port 1.4.11

IN

T

10.2.5

PIRQ3-7

PIRQ9-12

PIRQ14-15

117-121

122-125

126-127

Bus Interface 1.4.2

IN

TS

10.2.6 MUX

Signal Pin(s)

Functional Group DC Characteristics

MUX

Name Section Buffer Type Section

1.0 Signal/Pin Connection and Description (Continued)

16

www.national.com

PSLDC0 99 Strap Configuration 1.4.15

IN

STRP

10.2.4 MUX

PSLDC1 107 Strap Configuration 1.4.15

IN

STRP

10.2.4 MUX

PSON 34 System Wake-Up 1.4.16

OD

12,O4/4

10.2.9, 10.2.8

MUX

PSONPOL 109 Strap Configuration 1.4.15

IN

STRP

10.2.4 MUX

PWBTIN 35 System Wake-Up 1.4.16

IN

TS

10.2.6

MUX

PWBTOUT 33 System Wake-Up 1.4.16

OD

12

10.2.9

MUX

PWUREQ 32 System Wake-Up 1.4.16

OD

6

10.2.9

RDATA 62 FDC 1.4.5

IN

T

10.2.5

RI1 102 Serial Port 1 1.4.14

IN

TS

10.2.6

RI2 110 Serial Port 2 1.4.14

IN

TS

10.2.6

RING 27 System Wake-Up 1.4.16

IN

TS

10.2.6

MUX

RTS1 98 Serial Port 1 1.4.14

O

3/6

10.2.8

MUX

RTS2 106 Serial Port 2 1.4.14

O

3/6

10.2.8

SCL 54 ACB 1.4.1

IN

T

,OD6,O

3/6

10.2.5, 10.2.9, 10.2.8

MUX

SDA 55 ACB 1.4.1

IN

T

,OD6,O

3/6

10.2.5, 10.2.9, 10.2.8

MUX

SERIRQ 12 Bus Interface 1.4.2

IN

PCI,OPCI

10.2.2, 10.2.7

SIN1 97 Serial Port 1 1.4.14

IN

TS

10.2.6

SIN2 105 Serial Port 2 1.4.14

IN

TS

10.2.6

SLCT 76 Parallel Port 1.4.11

IN

T

10.2.5

SLIN_ASTRB 87 Parallel Port 1.4.11

OD

14,O14/14

10.2.9, 10.2.8

MM

SLPS3,5 36,37 System Wake-Up 1.4.16

IN

TS

10.2.6

MUX

(

SLPS3)

SMI 21 Bus Interface 1.4.2

OD

12

10.2.9

MUX

SOUT1 99 Serial Port 1 1.4.14

O

3/6

10.2.8

MUX

SOUT2 107 Serial Port 2 1.4.14

O

3/6

10.2.8

MUX

STEP 67 FDC 1.4.5

OD

12,O2/12

10.2.9, 10.2.8

STB_WRITE 94 Parallel Port 1.4.11

OD

14,O14/14

10.2.9, 10.2.8

MM

TEST 98 Strap Configuration 1.4.15

IN

STRP

10.2.4

MUX

TRK0 64 FDC 1.4.5

IN

T

10.2.5

V

BAT

30 Power and Ground 1.4.12

IN

ULR

N/A

V

DD

20, 52, 83, 115 Power and Ground 1.4.12 PWR N/A

V

SB

31 Power and Ground 1.4.12 PWR N/A

V

SS

19, 51, 84, 116 Power and Ground 1.4.12 GND N/A

WAIT See BUSY_WAIT

Signal Pin(s)

Functional Group DC Characteristics

MUX

Name Section Buffer Type Section

1.0 Signal/Pin Connection and Description (Continued)

17

www.national.com

WDATA 66 FDC 1.4.5

OD

12,O2/12

10.2.9, 10.2.8

WDO 56 WATCHDOG 1.4.17

OD

6,O3/6

10.2.9, 10.2.8

MUX

WGATE 65 FDC 1.4.5

OD

12,O2/12

10.2.9, 10.2.8

WP 63 FDC 1.4.5

IN

T

10.2.5

WRITE See STB_WRITE

XLOCK 53 Protection 1.4.11

IN

T

10.2.5

MUX

Signal Pin(s)

Functional Group DC Characteristics

MUX

Name Section Buffer Type Section

1.0 Signal/Pin Connection and Description (Continued)

18

www.national.com

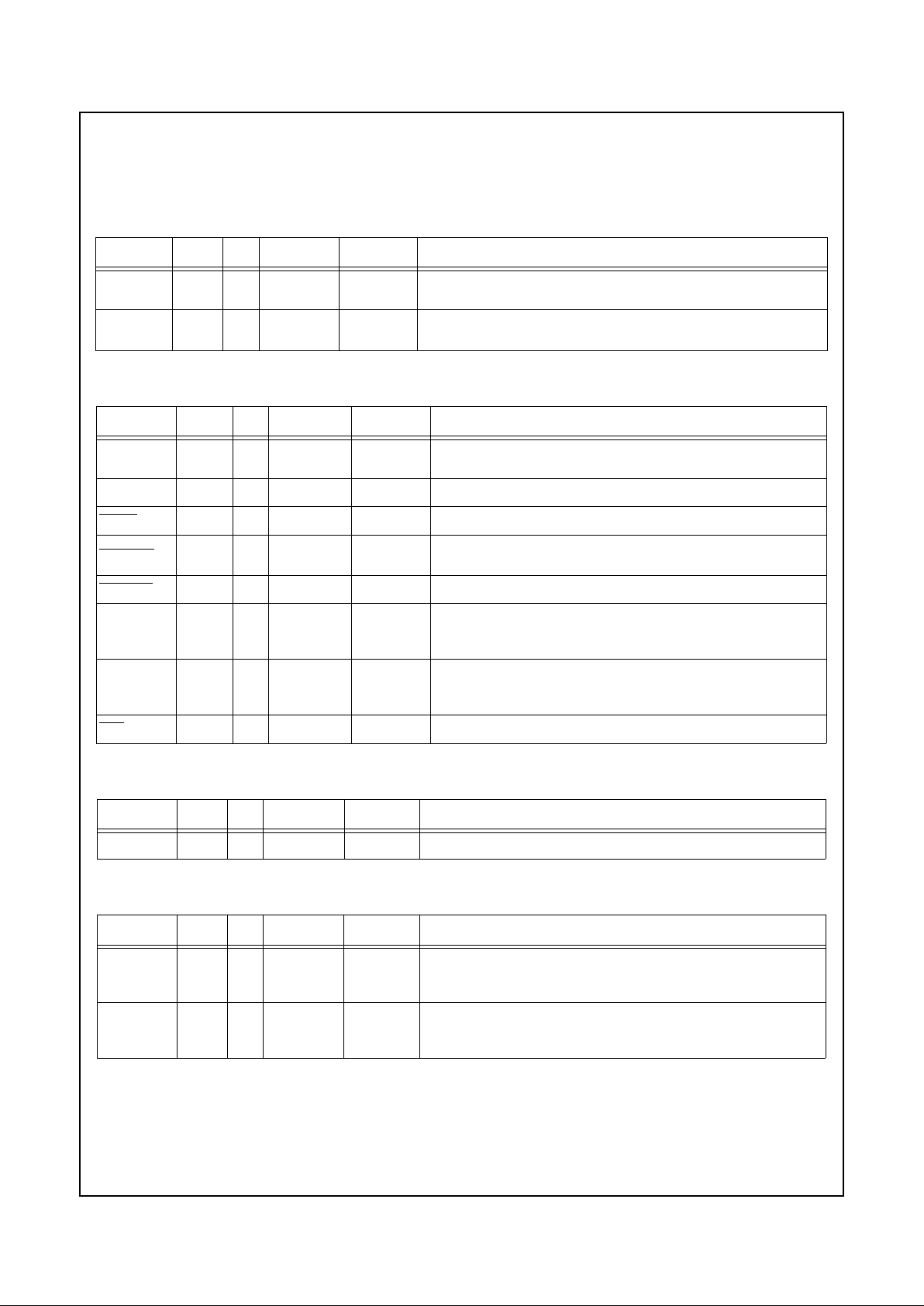

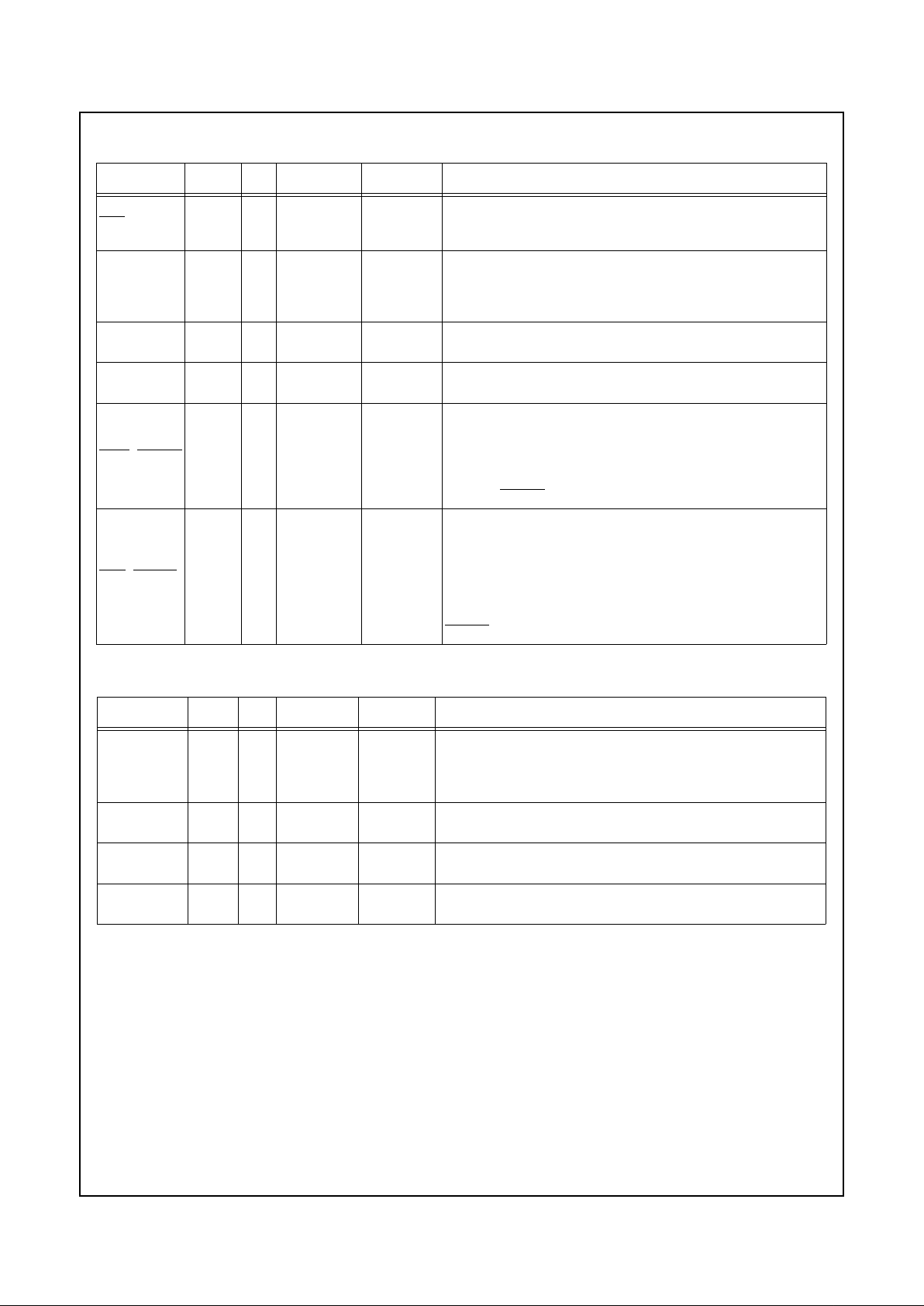

1.3 PIN MULTIPLEXING

The multiplexing options and the associated setup configuration for all pins are described in Table 3. A multiplexing option

can be chosen on one pin only per group.

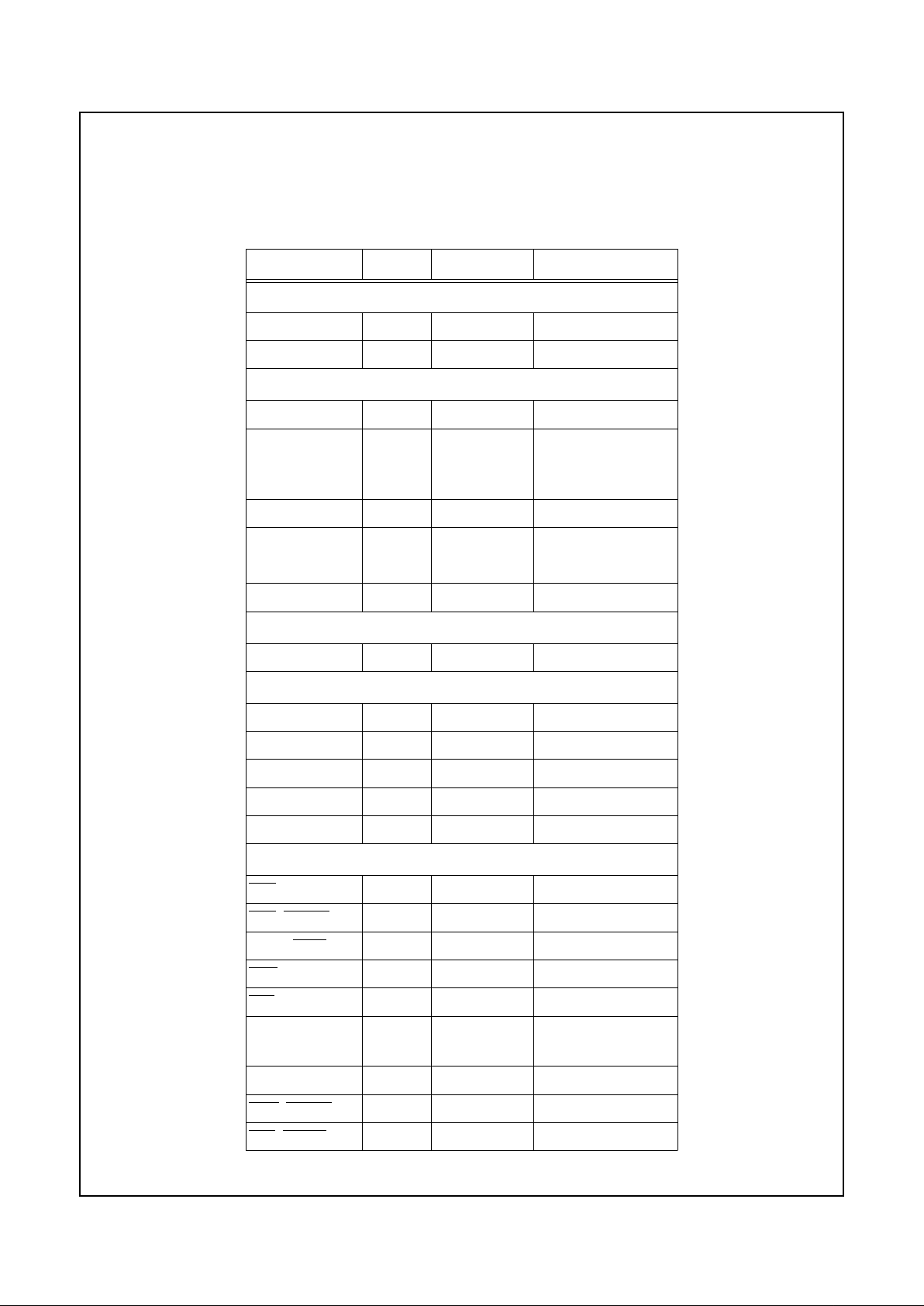

Table 3. Pin Multiplexing Configuration

Pin(s)

Default Alternate

Signal I/O Configuration Signal I/O Configuration

1 GPIO34 I/O SIOCF2, Bits 1-0 = 00 FANOUT2 O SIOCF2, Bits 1-0 = 01

CHLOCK O SIOCF2, Bits 1-0 = 10

2 GPIO00 I/O SIOCF2, Bit 2 = 0 FANIN1 I SIOCF2, Bit 2 = 1

3 GPIO01 I/O SIOCF2, Bit 3 = 0 FANOUT1 O SIOCF2, Bit 3 = 1

4 GPIO02 I/O SIOCF2, Bit 4 = 0 FANIN0 I SIOCF2, Bit 4 = 1

5 GPIO03 I/O SIOCF2, Bit 5 = 0 FANOUT0 O SIOCF2, Bit 5 = 1

6 GPIO04 I/O SIOCF2, Bit 6 = 0 P12 I/O SIOCF2, Bit 6 = 1

7 GPIO05 I/O SIOCF2, Bit 7 = 0 P17 I/O SIOCF2, Bit 7 = 1

8 KBRST (P20) SIOCF3, Bit 0 = 1 GPIO06 I/O SIOCF3, Bit 0 = 0

9 GA20 (P21) SIOCF3, Bit 1 = 1 GPIO07 I/O SIOCF3, Bit 1 = 0

21 GPIO10 I/O SIOCF3, Bit 2 = 0

SMI O SIOCF3, Bit 2 = 1

25 GPIOE2 I/O

SIOCFA, Bits 2-1 = 00

Note 1.

LED1 O SIOCFA, Bits 2-1 = 01

26 GPIOE3 I/O

SIOCFA, Bit 3 = 0

Note 1.

LED2 O SIOCFA, Bit 3 =1

27 GPIOE4 I/O SIOCFA, Bits 5-4 = 00

RING I SIOCFA, Bits 5-4 = 01

28 GPIOE5 I/O SIOCFA, Bit 6 = 0

CHASO O SIOCFA, Bit 6 =1

33-36

PWBTOUT

PSON

PWBTIN

SLPS3

O

O

I

I

SIOCFA, Bit 7 = 0

Note 1.

GPOS0

GPOS1

GPIS2

GPIS3

0

0

I

I

SIOCFA, Bit 7 = 1

Note 1.

53 GPIO11 I/O SIOCF3, Bit 4 = 0 XLOCK I SIOCF3, Bit 4 = 1

54 GPIO12 I/O SIOCF3, Bit 5 = 0 SCL I/O SIOCF3, Bit 5 = 1

55 GPIO13 I/O SIOCF3, Bit 5 = 0 SDA I/O SIOCF3, Bit 5 = 1

56 GPIO14 I/O SIOCF3, Bit 6 = 0

WDO O SIOCF3, Bit 6 = 1

57 GPO15 O SIOCF3, Bit 7 = 0 IRTX O SIOCF3, Bit 7 = 1

58 GPIE6 I SIOCFB, Bit 0 = 0 IRRX2_IRSL0 I/O SIOCFB, Bit 0 = 1

59 GPIE7 I SIOCFB, Bit 1 = 0 IRRX1 I SIOCFB, Bit 1 = 1

69 GPIO16 I/O SIOCF4, Bits 1-0 = 00

MTR1 O SIOCF4, Bits 1-0 = 01

IRSL2 I/O SIOCF4, Bits 1-0 = 10

71 GPIO17 I/O SIOCF4, Bits 3-2 = 00

DR1 O SIOCF4, Bits 3-2 = 01

IRSL3 I SIOCF4, Bits 3-2 = 10

117 GPIO20 I/O

SIOCF4, Bits 4,P

Note 2.

=00

PIRQ3 I SIOCF4, Bits 4,P = X1

118 GPIO21 I/O

SIOCF4, Bits 4,P

Note 1.

=00

PIRQ4 i SIOCF4, Bits 4,P = X1

119 GPIO22 I/O

SIOCF4, Bits 4,P

Note 1.

=00

PIRQ5 I SIOCF4, Bits 4,P = X1

120 GPIO23 I/O

SIOCF4, Bits 4,P

Note 1.

=00

PIRQ6 I SIOCF4, Bits 4,P = X1

121 GPIO24 I/O

SIOCF4, Bits 4,P

Note 1.

=00

PIRQ7 I SIOCF4, Bits 4,P = X1

122 GPIO25 I/O

SIOCF4, Bits 4,P

Note 1.

=00

PIRQ9 I SIOCF4, Bits 4,P = X1

1.0 Signal/Pin Connection and Description (Continued)

19

www.national.com

123 GPIO26 I/O

SIOCF4, Bits 4,P

Note 1.

=00

PIRQ10 I SIOCF4, Bits 4,P = X1

124 GPIO27 I/O

SIOCF4, Bits 4,P

Note 1.

=00

PIRQ11 I SIOCF4, Bits 4,P = X1

125 GPIO30 I/O

SIOCF4, Bits 5,P

Note 1.

=00

PIRQ12 I SIOCF4, Bits 5,P = X1

126 GPIO31 I/O

SIOCF4, Bits 5,P

Note 1.

=00

PIRQ14 I SIOCF4, Bits 5,P = X1

127 GPIO32 I/O

SIOCF4, Bits 7,6,P

Note 1.

= 000

P16 I/O

SIOCF4, Bits 7,6,P

Note 1.

= 010

IRSL1 I/O

SIOCF4, Bits 7,6,P

Note 1.

= 100

PIRQ15 I

SIOCF4, Bits 7,6,P

Note 1.

= XX1

128 GPIO33 I/O SIOCF5, Bits 1-0 = 00 FANIN2 I SIOCF5, Bits 1-0 = 10

CHUNLOCK O SIOCF5, Bits 1-0 = 11

Note 1. The signal selected on each pin is determined during V

SB

power-up by the PSLDC0,1 straps.

Note 2. P = SIOCF1, Bit 6 (Pins 117-127 Select PIRQ)

Pin(s)

Default Alternate

Signal I/O Configuration Signal I/O Configuration

1.0 Signal/Pin Connection and Description (Continued)

20

www.national.com

1.4 DETAILED SIGNAL/PIN DESCRIPTIONS

This section describes all signals, organized in functional groups.

1.4.1 ACCESS.bus Interface (ACB)

1.4.2 Bus Interface

1.4.3 Clock

1.4.4 Fan Speed Control and Monitor (FSCM)

Signal Pin(s) I/O Buffer Type Power Well Description

SCL 54 I/O

IN

SM

/OD

6

V

DD

ACCESS.bus Clock Signal. An internal pull-up is optional,

depending upon the ACCESS.bus configuration register.

SDA 55 I/O

IN

SM

/OD

6

V

DD

ACCESS.bus Data Signal. An internal pull-up is optional,

depending upon the ACCESS.bus configuration register.

Signal Pin(s) I/O Buffer Type Power Well Description

LAD0-3 15-18 I/O

IN

PCI/OPCI

V

DD

LPC Address-Data. Multiplexed command, address bidirectional data and cycle status.

LCLK 11 I

IN

PCI

V

DD

LPC Clock. Practically the PCI clock (up to 33 MHz)

LDRQ 13 O

O

PCI

V

DD

LPC DMA Request. Encoded DMA request for LPC I/F.

LFRAME 14 I

IN

PCI

V

DD

LPC Frame. Low pulse indicates the beginning of new LPC

cycle or termination of a broken cycle.

LRESET 10 I

IN

PCI

V

DD

LPC Reset. Practically the PCI system reset.

PIRQ3-7

PIRQ9-12

PIRQ14-15

117-121

122-125

126-127

I

IN

TS

V

DD

Parallel Interrupt. Converts Parallel Port interrupts into Serial

Interrupts by means of the Interrupt Serializer.

SERIRQ 12 I/O

IN

PCI/OPCI

V

DD

Serial IRQ. The interrupt requests are serialized over a single

pin, where each internal IRQ signal is delivered during a

designated time slot.

SMI 21 OD

OD

12

V

DD

System Management Interrupt

Signal Pin(s) I/O Buffer Type Power Well Description

CLKIN 22 I

IN

T

V

DD

Clock In. 48 MHz clock input.

Signal Pin(s) I/O Buffer Type Power Well Description

FANIN0

FANIN1

FANIN2

4

2

128

I

IN

TS

V

DD

Fan Inputs. Used to feed the fan’s tachometer pulse to the Fan

Speed Monitor. The rising edge indicates the completion of a half

(or full) revolution of the fan.

FANOUT0

FANOUT1

FANOUT2

5

3

1

O

O

2/14

V

DD

Fan Outputs. Pulse Width Modulation (PWM) signals, used to

control the speed of cooling fans by controlling the voltage

supplied to the fan’s motor.

1.0 Signal/Pin Connection and Description (Continued)

21

www.national.com

1.4.5 Floppy Disk Controller (FDC)

Signal Pin(s) I/O Buffer Type Power Well Description

DENSEL 75 O

O

2/12

V

DD

Density Select. Indicates that a high FDC density data rate (500

Kbps or 1 Mbps) or a low density data rate (250 or 300 Kbps) is

selected.

DENSEL polarity is controlled by bit 5 of the FDC Configuration

Register.

DIR 68 O

OD

12,O2/12

V

DD

Direction. Determines the direction of the Floppy Disk Drive

(FDD) head movement (active = step in, inactive = step out)

during a seek operation. During reads or writes,

DIR is inactive.

DR0 70 O

OD

12,O2/12

V

DD

Drive Select 0. Decoded drive select output signal. DR0 is

controlled by bit 0 of the Digital Output Register (DOR).

DR1 71 O

OD

12,O2/12

V

DD

Drive Select 1. Decoded drive select output signal. DR0 is

controlled by bit 1 of the Digital Output Register (DOR).

DRATE0 74 O

O

3/6

V

DD

Data Rate 0. Reflects the value of bit 0 of the Configuration Control

Register (CCR) or the Data Rate Select Register (DSR), whichever

was written to last. Output from the pin is push-pull buffered.

DSKCHG 60 I

IN

T

V

DD

Disk Change. Indicates if the drive door has been opened. The

state of this pin is stored in the Digital Input Register (DIR). This pin

can also be configured as the RGATE data separator diagnostic input

signal via the MODE command.

HDSEL 61 O

OD

12,O2/12

V

DD

Head Select. Determines which side of the FDD is accessed.

Active low selects side 1, inactive selects side 0.

INDEX 73 I

IN

T

V

DD

Index. Indicates the beginning of an FDD track.

MTR0 72 O

OD

12,O2/12

V

DD

Motor Select 0. Active low, motor enable line for drives 0, controlled

by bits D7-4 of the Digital Output Register (DOR).

MTR1 69 O

OD

12,O2/12

V

DD

Motor Select 1. Active low, motor enable lines for drives 1,

controlled by bits D7-4 of the Digital Output Register (DOR).

RDATA62 I

IN

T

V

DD

Read Data. Raw serial input data stream read from the FDD.

STEP 67 O

OD

12,O2/12

V

DD

Step. Issues pulses to the disk drive at a software programmable

rate to move the head during a seek operation.

TRK0 64 I

IN

T

V

DD

Track 0. Indicates to the controller that the head of the selected

floppy disk drive is at track 0.

WDATA66 O

OD

12,O2/12

V

DD

Write Data. Carries out the pre-compensated serial data that is

written to the floppy disk drive. Pre-compensation is software

selectable.

WGATE 65 O

OD

12,O2/12

V

DD

Write Gate. Enables the write circuitry of the selected disk drive.

WGATE is designed to prevent glitches during power up and

power down. This prevents writing to the disk when power is

cycled.

WP 63 I

IN

T

V

DD

Write Protected. Indicates that the disk in the selected drive is

write protected. A software programmable configuration bit (FDC

configuration at Index F0h, Logical Device 0) can force an active

write-protect indication to the FDC, regardless of the status of this

pin.

1.0 Signal/Pin Connection and Description (Continued)

22

www.national.com

1.4.6 General-Purpose Input/Output (GPIO) Ports

1.4.7 Infrared (IR)

Signal Pin/s I/O Buffer Type Power Well Description

GPIO00-07 2-9 I/O

IN

TS

/

OD

6,O3/6

V

DD

General-Purpose I/O Port 0, bits 0-7. Each pin is configured independently as input or I/O, with or without static pull-up, and with

either open-drain or push-pull output type. The port support interrupt assertion and each pin can be enabled or masked as an interrupt source.

GPIO10

GPIO11-14

GPO15

GPIO16-17

21

53-56

57

69, 71

I/O

IN

TS

/

OD

6,O3/6

V

DD

General-Purpose I/O Port 1, bits 0-7. Same as Port 0. Bit 5 is

output only with low output as default.

GPIO20-27 117-124 I/O

IN

TS

/

OD

6,O3/6

V

DD

General-Purpose I/O Port 2, bits 0-7. Similar to port 0, but

without the interrupt assertion capability.

GPIO30-33

GPIO34

GPO36-37

125-128

1

41-42

I/O

IN

TS

/

OD

6,O3/6

V

DD

General-Purpose I/O Port 3, bits 0-4,6,7. Similar to port 0, but

without the interrupt assertion capability. Bit 5 is not

implemented.

GPIO40-47 43-50 I/O

IN

TS

/

OD

6,O3/6

V

DD

General-Purpose I/O Port 4, bits 0-7. Same as Port 0.

Signal Pin/s I/O Buffer Type Power Well Description

IRRX1 59 I

IN

TS

VDD,V

SB

IR Receive 1. Primary input to receive serial data from the IR

transceiver. Monitored during power-off for wake-up event

detection.

IRRX2_IRSL0 58 I/O

IN

TS/O3/6

VDD,VSBIRRX2 - IR Receive 2. Auxiliary IR receiver input to support a

second transceiver. Monitored during power-off for wake-up event

detection.

IRSL3-0 IR Select. Output are used to control the IR transceivers.

Input for PnP identification of plug-in IR transceiver (dongle).

After reset, the dual-function IRSLX pins wake up in input mode.

After the ID is read by the IR driver, they may be put into output

mode. The output mode is controlled by Serial Port 2.

IRSL1 127 I/O

IN

T/O3/6

V

DD

IRSL2 69 I/O

IN

T/O3/6

V

DD

IRSL3 71 I

IN

T

V

DD

IRTX 57 O

O

6/12

V

DD

IR Transmit. IR serial output data.

1.0 Signal/Pin Connection and Description (Continued)

23

www.national.com

1.4.8 Keyboard and Mouse Controller (KBC)

1.4.9 Parallel Port

Signal Pin/s I/O Buffer Type Power Well Description

GA20 9 I/O

IN

T

/OD

2

V

DD

Gate A20. KBC gate A20 (P21) output.

KBCLK 111 I/O

IN

TS

/OD14VDD,V

SB

Keyboard Clock. Transfers the keyboard clock between the

SuperI/O chip and the external keyboard using the PS/2 protocol.

This pin is driven by the internal, inverted KBC P26 signal, and is

connected internally to the T0 signal of the KBC. External pull-up

resistor to 5V is required (for PS/2 compliance). The pin is

monitored for wake-up event detection. To enable the activity

during power off, it must be pulled up to Keyboard and Mouse

standby voltage.

KBDAT 112 I/O

IN

TS

/OD14VDD,V

SB

Keyboard Data. Tr ansfers the keyboard data between the SuperI/O

chip and the external keyboard using the PS/2 protocol.

This pin is driven by the internal, inverted KBC P27 signal, and is

connected internally to KBC P10. External pull-up resistor to 5V is

required (for PS/2 compliance). The pin is monitored for wake-up

event detection. To enable the activity during power off, it must be

pulled up to Keyboard and Mouse standby voltage.

KBRST 8 I/O

IN

T

/OD

2

V

DD

KBD Reset. Keyboard Reset (P20) output.

MCLK 113 I/O

IN

TS

/OD14VDD,V

SB

Mouse Clock. Transfers the mouse clock between the SuperI/O

chip and the external keyboard using the PS/2 protocol.

This pin is driven by the internal, inverted KBC P23 signal, and is

connected internally to KBC T1. External pull-up resistor to 5V is

required (for PS/2 compliance). The pin is monitored for wake-up

event detection. To enable the activity during power off, it must be

pulled up to Keyboard and Mouse standby voltage.

MDAT 114 I/O

IN

TS

/OD14VDD,V

SB

Mouse Data. Transfers the mouse data between the SuperI/O

chip and the external keyboard using the PS/2 protocol.

This pin is driven by the internal, inverted KBC P22 signal, and is

connected internally to KBC P11. External pull-up resistor to 5V is

required (for PS/2 compliance). The pin is monitored for wake-up

event detection. To enable the activity during power off, it must be

pulled up to Keyboard and Mouse standby voltage.

P12, P16,

P17

6,127,

7

I/O

IN

T

/OD

2

V

DD

I/O Port. KBC open-drain signal for general-purpose input and

output, controlled by KBC firmware.

Signal Pin/s I/O Buffer Type Power Well Description

ACK 79 I

IN

T

V

DD

Acknowledge. Pulsed low by the printer to indicate that it has

received data from the Parallel Port.

AFD_DSTRB 93 O

OD

14,O14/14

V

DD

AFD - Automatic Feed. When low, instructs the printer to

automatically feed a line after printing each line. This pin is in

TRI-STATE after a 0 is loaded into the corresponding control

register bit. An external 4.7 KΩ pull-up resistor should be

attached to this pin.

DSTRB - Data Strobe (EPP). Active low, used in EPP mode

to denote a data cycle. When the cycle is aborted,

DSTRB

becomes inactive (high).

BUSY_

WAIT 78 I

IN

T

V

DD

Busy. Set high by the printer when it cannot accept another

character.

Wait. In EPP mode, the Parallel Port device uses this active

low signal to extend its access cycle.

ERR 91 I

IN

T

V

DD

Error. Set active low by the printer when it detects an error.

1.0 Signal/Pin Connection and Description (Continued)

24

www.national.com

1.4.10 Power and Ground

INIT 89 O

OD

14,O14/14

V

DD

Initialize. When low, initializes the printer. This signal is in

TRI-STATE after a 1 is loaded into the corresponding control

register bit. Use an external 4.7 KΩ pull-up resistor.

PD7-5

PD4-3,

PD2, PD1

PD0

80-82

85-86

88, 90

92

I/O

IN

T

/

OD

14,O14/14

V

DD

Parallel Port Data. Transfer data to and from the peripheral

data bus and the appropriate Parallel Port data register. These

signals have a high current drive capability.

PE 77 I

IN

T

V

DD

Paper End. Set high by the printer when it is out of paper. This

pin has an internal weak pull-up or pull-down resistor.

SLCT 76 I

IN

T

V

DD

Select. Set active high by the printer when the printer is

selected.

SLIN_ASTRB 87 O

OD

14,O14/14

V

DD

SLIN - Select Input. When low, selects the printer. This signal

is in TRI-STATE after a 0 is loaded into the corresponding

control register bit. Uses an external 4.7 KΩ pull-up resistor.