NSC PC87109EB, PC87109VBE Datasheet

www.national.com

1

General Description

The PC87109 is a serial communication device with

infrared capability. It supports 6 modes of operation and is

backward compatible with the 16550 and 16450 (except for

the MODEM control functions). The operational modes are:

UART, Sharp-IR, IrDA 1.0 SIR, IrDA 1.1 MIR and FIR, and

Consumer Electronics IR (also referred to as TV Remote or

Consumer Remote Control).

In order to support existing legacy software based upon the

16550 UART, the PC87109 provides a special fallback

mechanism that automatically switches the device to 16550

compatibility mode when the baud generator divisor is

accessed through the legacy ports in bank 1.

The device architecture has been optimized to meet the

requirements of a variety of UART and infrared based

applications. DMA support for all operational modes has

been incorporated into the architecture.

The device uses one DMA channel. One channel is

required for infrared based applications since infrared

communications work in half duplex fashion.

To further ease driver design and simplify the

implementation of infrared protocols, a 12-bit timer with 125µs

resolution has also been included.

Features

■ Compatible with 16550 and 16450 devices

■ Extended UART mode

■ Sharp-IR with selectable internal or external

modulation

■ IrDA 1.0 SIR with up to 115.2 Kbaud data rate

■ IrDA 1.1 MIR and FIR with 0.576, 1.152 and 4.0 Mbps

data rates

■ Consumer Electronics IR mode

■ UART mode data rates up to 1.5 Mbps

■ Back-to-Back infrared frame transmission and

reception

■ Full duplex infrared frame transmission and reception

■ Transmit deferral

■ Automatic fallback to 16550 compatibility mode

■ Selectable 16 or 32 level FIFOs

■ 12-bit timer for infrared protocol support

■ Programmable IRQ and DMA signals polarity

■ Support for power management

■ 5V or 3.3V operation with back drive protection

■ 32-pin TQFP package

Preliminary

November 1997

PC87109VBE Advanced UART and Infrared Controller

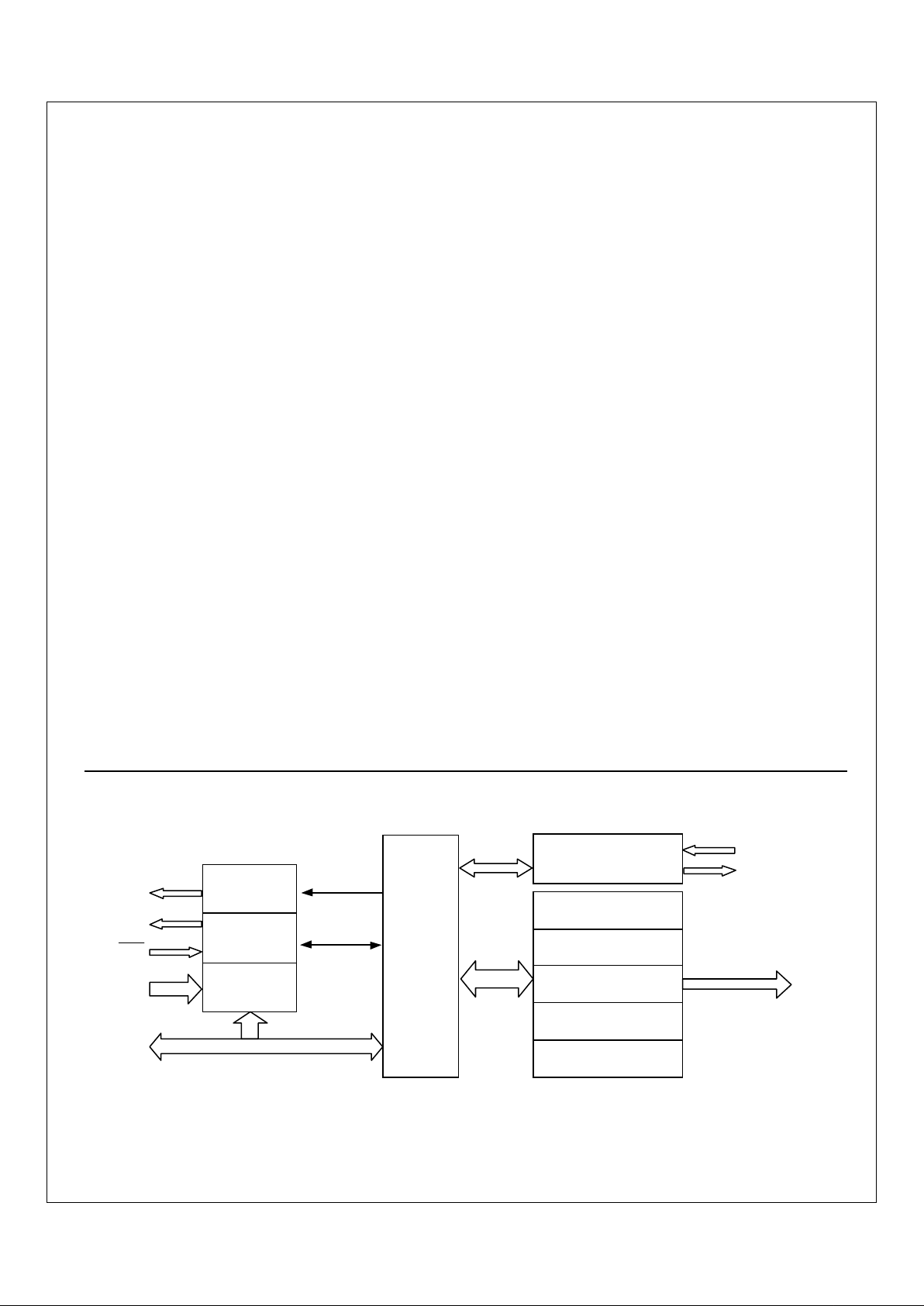

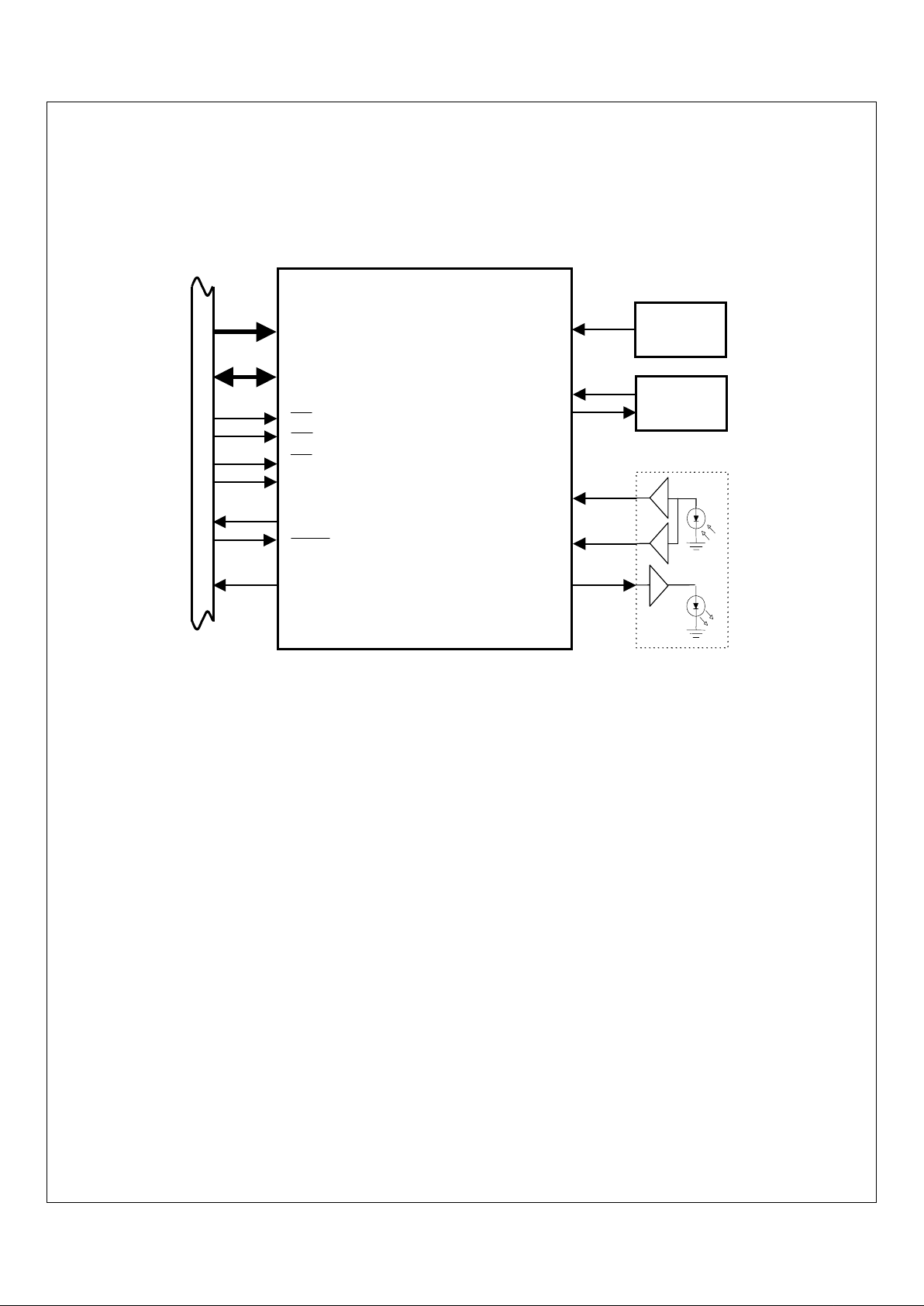

Block Diagram

P

71

VBE A

v

n

ART

n

Infr

r

n

r

ll

r

© 1997 National Semiconductor Corporation

TRI-STATE® is a registered trademark of National Semiconductor Corp.

WATCHDOG™ is a trademark of National Semiconductor Corp.

PC87109 Core

UART Module

Sharp -IR Mo du le

DASK

IrDA 1.0 Module

11 5.2 Kbps

SIR

Consumer Ele ctronics IR Module

CEI R

SOUT

IrDA 1.1 Module

0.576 & 1.152 Mbps

MIR

IrDA 1.1 Module

4.0 Mb ps

FIR

SIN

To IR Transceivers

D0-D7

Configuration

Registers

Interrupt

Request

Control

DMA Re quest

Control

A0-A3

DACK

TC

DRQ

IRQ

8 Bit Data Bus

www.national.com

2

Table Of Contents

1. Pin Description 7

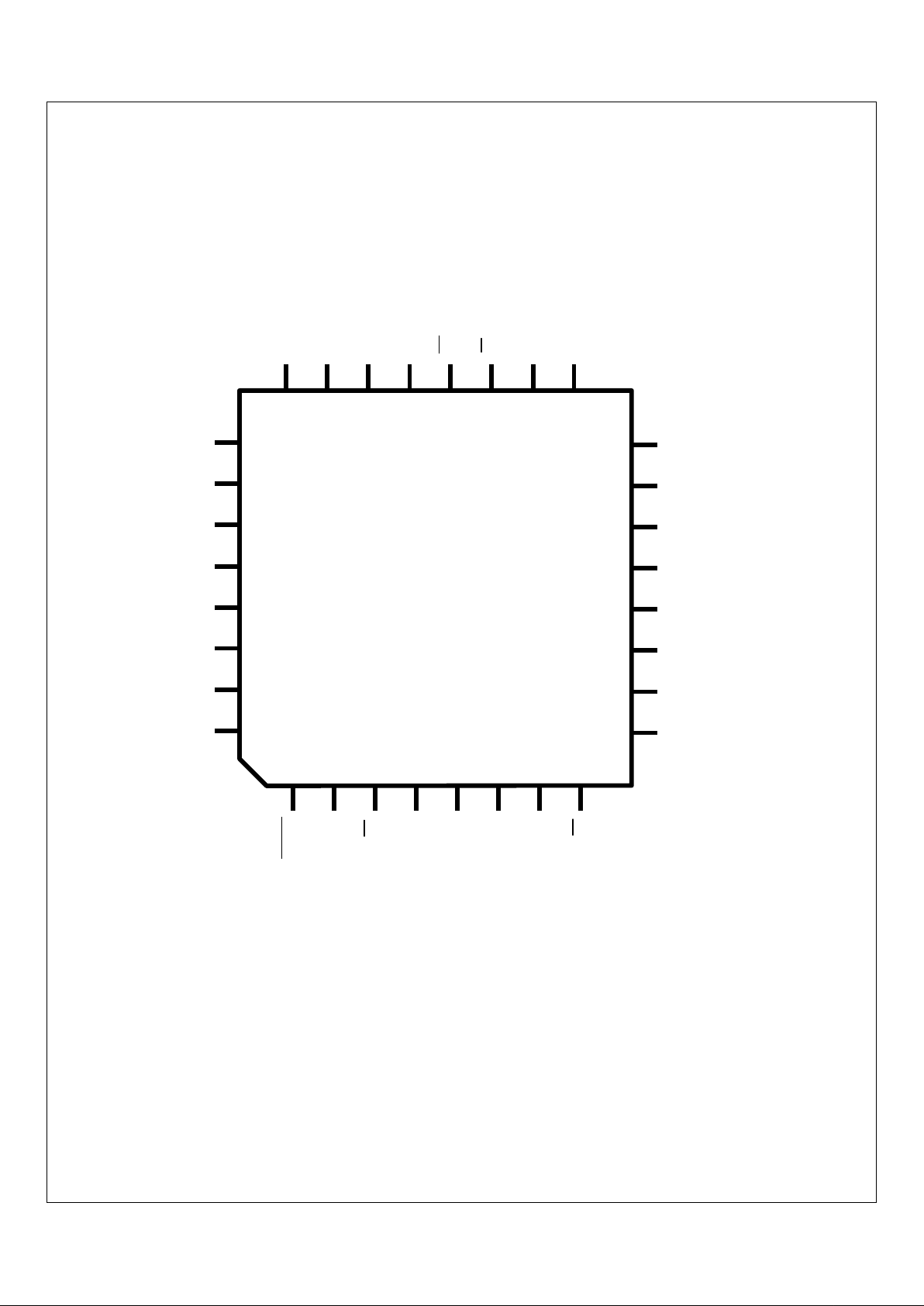

1.1 Connection Diagram 7

1.2 Pin Description 8

2. Functional Description 10

2.1 Device Overview 10

2.2 UART Mode 10

2.3 Sharp-IR Mode 10

2.4 IrDA 1.0 SIR Mode 11

2.5 IrDA 1.1 MIR and FIR Modes 11

2.5.1 High Speed Infrared Transmit 11

2.5.2 High Speed Infrared Receive 12

2.6 Consumer Electronics IR (CEIR) Mode 12

2.6.1 Consumer Electronics IR Transmit 12

2.6.2 Consumer Electronics IR Receive 13

2.7 FIFO Time-outs 13

2.8 Transmit Deferral 14

2.9 Automatic Fallback to 16550 Compatibility Mode 14

2.10 Optical Transceiver Interface 15

3. Architectural Description 16

3.1 Bank 0 17

3.1.1 TXD/RXD - Transmit/Receive Data Ports 17

3.1.2 IER - Interrupt Enable Register 17

3.1.3 EIR/FCR - Event Identification/FIFO Control Registers 18

3.1.4 LCR/BSR - Link Control/Bank Select Register 21

3.1.5 MCR - Mode Control Register 22

3.1.6 LSR - Link Status Register 23

3.1.7 SPR/ASCR - Scratchpad/Auxiliary Status and Control Register 25

3.2 Bank 1 27

3.2.1 LBGD - Legacy Baud Generator Divisor Port 27

3.2.2 LCR/BSR - Link Control/Bank Select Registers 27

3.3 Bank 2 27

3.3.1 BGD - Baud Generator Divisor Port 28

3.3.2 EXCR1 - Extended Control Register 1 28

3.3.3 LCR/BSR - Link Control/Bank Select Registers 30

3.3.4 EXCR2 - Extended Control Register 2 30

3.3.5 TXFLV - TX_FIFO Level, Read Only 31

3.3.6 RXFLV - RX_FIFO Level, Read Only 31

3.4 Bank 3 31

3.4.1 MRID - Module Revision Identification Register, Read Only 31

www.national.com

3

3.4.2 SH_LCR - Link Control Register Shadow, Read Only 31

3.4.3 SH_FCR - FIFO Control Register Shadow, Read Only 32

3.4.4 LCR/BSR - Link Control/Bank Select Registers 32

3.5 Bank 4 32

3.5.1 TMR - Timer Register 32

3.5.2 IRCR1- Infrared Control Register 1 32

3.5.3 LCR/BSR - Link Control/Bank Select Registers 33

3.5.4 TFRL/TFRCC - Transmitter Frame Length/Current-Count 33

3.5.5 RFRML/RFRCC - Receiver Frame Maximum Length/Current-Count 33

3.6 Bank 5 33

3.6.1 LCR/BSR - Link Control/Bank Select Registers 34

3.6.2 IRCR2 - Infrared Control Register 2 34

3.6.3 ST_FIFO - Status FIFO 34

3.7 Bank 6 36

3.7.1 IRCR3 - Infrared Control Register 3 36

3.7.2 MIR_PW - MIR Pulse Width Register 36

3.7.3 SIR_PW - SIR Pulse Width Register 37

3.7.4 LCR/BSR - Link Control/Bank Select Registers 37

3.7.5 BFPL - Beginning Flags/Preamble Length Register 37

3.8 Bank 7 38

3.8.1 IRRXDC - Infrared Receiver Demodulator Control Register 38

3.8.2 IRTXMC - Infrared Transmitter Modulator Control Register 39

3.8.3 RCCFG - CEIR Configuration Register 40

3.8.4 LCR/BSR - Link Control/Bank Select Registers 41

3.8.5 IRCFG1, 4 - Infrared Interface Configuration Registers 41

4. Device Configuration 44

4.1 Overview 44

4.2 Configuration Registers 44

4.2.1 CSCFG – Control Signals Configuration Register (offset = 08h) 44

4.2.2 CSEN - Control Signals Enable Register (offset = 09h) 45

4.2.3 MCTL - Mode Control Register (offset = 0Ah) 45

4.2.4 DID - Device Identification Register (offset = 0Dh) 46

5. Device Specifications 47

5.1 Absolute Maximum Ratings 47

5.2 Capacitance 47

5.3 Electrical Characteristics 47

5.4 Switching Characteristics 48

5.4.1 Timing Table 48

5.4.2 Timing Diagrams 51

6. Physical Dimensions 55

6.1 32-Pin Thin Quad Flat Pack 55

www.national.com

4

List Of Figures

Figure 1-1. 32-Pin TQFP Package 7

Figure 1-2. Basic Configuration 9

Figure 2-1. Serial Data Stream Fromat 9

Figure 3-1. Register Bank Architecture 16

Figure 3-2. Interrupt Enable Register 17

Figure 3-3. Event Identification Register, Non-Extended Mode 18

Figure 3-4. Event Identification Register, Extended Mode 19

Figure 3-5. FIFO Control Register 20

Figure 3-6. Link Control Register 21

Figure 3-7. Mode Control Register, Non-Extended Model 22

Figure 3-8. Mode Control Register, Extended Mode 23

Figure 3-9. Link Status Register 24

Figure 3-10. Auxiliary Status and Control Register 26

Figure 3-11. Extended Control Register 1 28

Figure 3-12. DMA Control Signals Routing 30

Figure 3-13. Extended Control Register 2 30

Figure 3-14. Transmit FIFO Level 31

Figure 3-15. Receive FIFO Level 31

Figure 3-16. Infrared Control Register 1 32

Figure 3-17. Infrared Control Register 2 34

Figure 3-18. Frame Status Byte 35

Figure 3-19. Infrared Control Register 3 36

Figure 3-20. MIR Pulse Width Register 36

Figure 3-21. SIR Pulse Width Register 37

Figure 3-22. Beginning Flags/Preamble Length Register 37

Figure 3-23. Infrared Receiver Demodulator Control Register 38

Figure 3-24. Infrared Transmitter Modulator Control Register 39

Figure 3-25. CEIR Configuration Register 40

Figure 3-26. Infrared Configuration Register 1 41

Figure 3-27. Infrared Configuration Register 4 42

Figure 4-1. Control Signals Configuration Register 44

Figure 4-2. Control Signals Enable Register 45

Figure 4-3. Mode Control Register 45

Figure 5-1. Testing Specification Standard 48

Figure 5-2. Clock Timing 51

Figure 5-3. CPU Read Timing 51

Figure 5-4. CPU Write Timing 52

Figure 5-5. DMA Access Timing 52

Figure 5-6. UART, Sharp-IR and CEIR Timing 53

Figure 5-7. SIR, MIR and FIR Timing 53

Figure 5-8. IRSLn Write Timing 53

Figure 5-9. Reset Timing 54

Figure 6-1. Thin Plastic Quad Flat Pack 53

www.national.com

5

www.national.com

6

List Of Tables

Table 3-1. Register Banks Summary 16

Table 3-2. Bank 0 Register Set 17

Table 3-3. Non-Extended Mode Interrupt Priorities 19

Table 3-4. Bank Selection Encoding 22

Table 3-5. UIR Module Operational Modes 23

Table 3-6. Bank 1 Register Set 27

Table 3-7. Bank 2 Register Set 27

Table 3-8. Baud Generator Divisor Settings 28

Table 3-9. Bank 3 Register Set 31

Table 3-10. Bank 4 Register Set 32

Table 3-11. Bank 5 Register Set 33

Table 3-12. Bank 6 Register Set 36

Table 3-13. Bank 7 Register Set 38

Table 3-14. CEIR Low-Speed Demodulator Frequency Ranges in kHz (RXHSC = 0) 39

Table 3-15. CEIR High-Speed Demodulator Frequency Ranges in kHz (RXHSC=1) 39

Table 3-16. Sharp-IR Demodulator Frequency Ranges in kHz 39

Table 3-17. Infrared Receiver Input Selection 43

Table 4-1. Configuration Registers 42

www.national.com

7

1.0 Pin Descriptions

1.1 Connection Diagram

1

8

32

16

PC87109VBE

A3

A2

A1

A0

CS

MR

DACK

TC

9

25

24

17

IRQ

D4

D5

D7

V

DD

DRQ

V

SS

D6

IRTX

IRRX1

ID0/IRSL0/IRRX2

ID1/IRSL1

V

SS

SOUT

SIN

V

DD

D3

D2

D1

D0

WR

RD

RESERVED

CLKIN

Top View

Figure 1-1. 32-Pin TQFP Package

Order number PC87109VBE

See NS package VBE32A

www.national.com

8

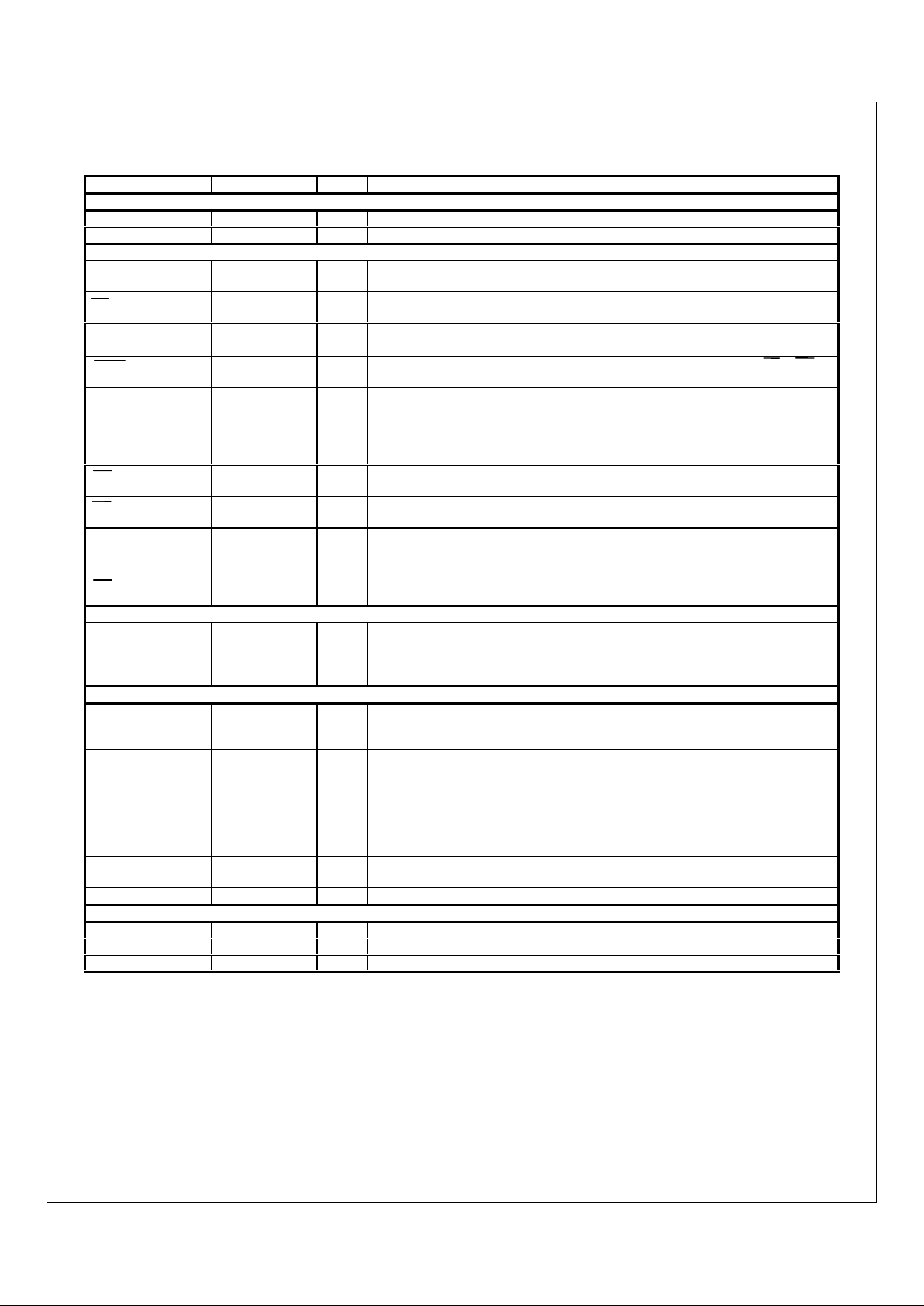

1.2 Pin Descriptions

Symbol Pin(s) Type Description

SUPPLIES

V

DD

13, 28

5V or 3.3V Power Supply

V

SS

12, 29

Ground.

BUS INTERFACE SIGNALS

A0-A3 7-4 I Address. Input signals used to determine which internal register is accessed

(Section 4.2). A0-A3 are ignored during a DMA access.

CS

3IChip Select. Active low input used in conjunction with A0-A3 to select the internal

registers.

D0-D7 21-27, 30 I/O Data Bus. 8-bit bi-directional data lines used to transfer data between the PC87109

and the CPU or DMA controller. D0 is the LSB and D7 is the MSB

.

DACK

1 I DMA Acknowledge. Used to acknowledge a DMA request and enable the RD or

WR signals during a DMA access cycle. The polarity of this signal is programmable.

DRQ 32 O DMA Request. Used to signal the DMA controller that a data transfer from the

PC87109 is required. The polarity of this signal is programmable.

IRQ 31 O Interrupt Request. This output is used to signal an interrupt condition to the CPU

(Section 4.2.2). The IRQ signal can be configured to be either open-drain or totem

pole. Its polarity is also programmable.

MR

8IMaster Reset. A low level on this input resets the PC87109. This signal

asynchronously terminates any activity and places the device in the Disable state.

RD

19 I Read. Active low input asserted by the CPU or DMA controller to read data or status

information from the PC87109.

TC 2 I Terminal Count. This signal is asserted by the DMA controller to indicate the end of

a DMA transfer. The signal is only effective during a DMA access cycle. Its polarity is

programmable.

WR

20 I Write. Active low input asserted by the CPU or DMA controller to write data or

control information to the PC87109.

UART INTERFACE SIGNALS

SIN 9 I Serial Data In. This input receives serial data from the communications link.

SOUT 10 O Serial Data Out. This output sends serial data to the communications link. This

signal is set to a Marking state (logic 1) after a Master Reset operation or when the

device is in one of the Infrared communications modes.

INFRARED INTERFACE SIGNALS

IRRX1 16 I Infrared Receive. Primary input to receive serial data from the infrared transceiver

module. If the infrared transceiver provides two receive data outputs, the low-speed

output should be connected to this pin.

ID0/IRSL0/IRRX2 14 I/O Transceiver Identification, Control or Secondary Infrared Receive.

Multi function pin implementing the following functions:

- ID0, to read identification data to support infrared adapters.

- IRSL0, to select the transceiver operational mode.

- IRRX2, used either as a high-speed receiver input (for MIR and FIR) to support

transceiver modules with two receive data outputs, or as an auxiliary input

to support two transceiver modules.

ID1/IRSL1 11 I/O Transceiver Identification or Control. Used to read identification data to support

infrared adapters, as well as to select the transceiver operational mode.

IRTX 15 O Infrared Transmit. This output sends serial data to the transceiver module(s).

MISCELLANEOUS SIGNALS

CLKIN 17 I Clock. 48 MHz clock input.

RESERVED 18 NC Reserved. No connection should be made on this pin.

www.national.com

9

Figure 1-2. Basic Configuration

PC87109

A0-A3

D0-7

RD

WR

CS

TC

DRQ

DACK

IRQ

EIA

Interface

CLKIN

SIN

SOUT

IRRX1

ID0/IRSL0/IRRX2

IRTX

48MHz

Clock

IR Interface

XCVR

SYSTEM BUS

www.national.com

10

2.0 Functional Description

2.1 Device Overview

The PC87109 is a serial communications element that

implements the most common infrared communications

protocols.

In addition to the infrared modes, the device provides a

UART mode of operation that is backward compatible to

the 16550 to support existing communications software.

The device includes two basic modules: the UIR (universal

infrared) module and the configuration module. The UIR

module implements all the communications functions while

the configuration module controls the enabling of the device

as well as the enabling the interrupt and DMA control

signals. The UIR module uses a register-banking scheme

similar to the one used by the 16550.

This minimizes the number of I/O addresses needed to

access the internal registers. Most of the communications

features are programmed via configuration registers placed

in banks 0 through 7. The main control and status

information has been consolidated into bank 0 to eliminate

unnecessary bank switching. A description of the device

operation is provided in the following sections.

2.2 UART Mode

This mode is designed to support serial data

communications with a remote peripheral device or modem

using a wired interface. The PC87109 provides transmit

and receive channels that can operate concurrently to

handle full-duplex operation. They perform parallel-toserial conversion on data characters received from the

CPU or a DMA controller, and serial-to-parallel conversion

on data characters received from the serial interface. The

format of the serial data stream is shown in figure 1-3. A

data character contains from 5 to 8 data bits. It is preceded

by a start bit and is followed by an optional parity bit and a

stop bit. Data is transferred in Little Indian order (least

significant bit first).

The UART mode is the default mode of operation after

power up or reset. In fact, after reset, the 16450compatibility mode is selected. In addition to the 16450

and 16550 compatibility modes, an extended mode of

operation is also available. When the extended mode is

selected, the architecture changes slightly and a variety of

additional features will be made available. The interrupt

sources are no longer prioritized, and an auxiliary status

and control register replaces the scratch pad register. The

additional features include transmitter FIFO thresholding,

DMA capability, and interrupts on transmitter empty and

DMA event.

The clock for both transmit and receive channels is

provided by an internal baud generator that divides its input

clock by any divisor value from 1 to 2

16

- 1. The output

clock frequency of the baud generator must be

programmed to be sixteen times the baud rate value. The

baud generator input clock is derived from a 24 MHz clock

through a programmable prescaler. The PRESL bits in the

EXCR2 register determine the prescaler value. Its default

value is 13. This allows all the standard baud rates, up to

115.2 Kbaud to be obtained. Smaller prescaler values will

allow baud rates up to 921.6 Kbaud (standard) and 1.5

Mbaud (non-Standard).

Before operation can begin, both the communications

format and the software must program baud rate. The

communications format is programmed by loading a control

byte into the LCR register, while the baud rate is selected

by loading an appropriate value into the baud generator

divisor register. The software can read the status of the

device at any time during operation. The status information

includes FULL/EMPTY state for both transmit and receive

channels, and any other condition detected on the received

data stream, like a parity error, framing error, data overrun,

or break event.

START 5 to 8 DATA BITS PARITY STOP

Figure 2-1. Serial Data Stream Format

2.3 Sharp-IR Mode

This mode supports bi-directional data communication with

a remote device using infrared radiation as the transmission

medium. Sharp-IR uses Digital Amplitude Shift Keying

(DASK) and allows serial communication at baud rates up

to 38.4 Kbaud. The format of the serial data is similar to

the UART data format. Each data word is sent serially

beginning with a zero value start bit, an optional parity bit,

and ending with at least one stop bit with a binary value of

one. Sending a 500 kHz continuous pulse train of infrared

radiation signals a zero. A one is signaled by the absence

of any infrared signal. The PC87109 can perform the

modulation and demodulation operations internally, or it can

rely on the external optical module to perform them.

The device operation, in Sharp-IR, is similar to the

operation in UART mode. The main difference being that

data transfer operation is normally performed in half-duplex

fashion. The MDSL bits in the MCR register control

selection of the Sharp-IR mode when the device is in

extended mode or by the IR_SL bits in the IRCR1 register

when the device is in non-extended mode. This prevents

legacy software, running in non-extended mode, from

spuriously switching the device to UART mode, when the

software writes to the MCR register.

www.national.com

11

2.4 IrDA 1.0 SIR Mode

This is the first operational mode that has been defined by

the IrDA committee and, similarly to Sharp-IR, it also

supports bi-directional data communication with a remote

device using infrared radiation as the transmission medium.

IrDA 1.0 SIR allows serial communication at baud rates up

to 115.2 Kbaud. The format of the serial data is similar to

the UART data format. Each data word is sent serially

beginning with a zero value start bit, followed by 8 data bits,

and ending with at least one stop bit with a binary value of

one. Sending a single infrared pulse signals a zero. A one

is signaled by not sending any pulse. The width of each

pulse can be either 1.6 µs or 3/16ths of a single bit time.

(1.6 µs equals 3/16ths of a bit time at 115.2 Kbaud). This

way, each word begins with a pulse for the start bit.

The device operation, in IrDA 1.0 SIR, is similar to the

operation in UART mode. The main differences being

those data transfer operations are normally performed in

half-duplex fashion. Selection of the IrDA 1.0 SIR mode is

controlled by the MDSL bits in the MCR register when the

device is in extended mode or by the IR_SL bits in the

IRCR1 register when the device is in non-extended mode.

This prevents legacy software, running in non-extended

mode, from spuriously switching the device to UART mode,

when the software writes to the MCR register.

2.5 IrDA 1.1 MIR and FIR Modes

The PC87109 supports both IrDA 1.1 MIR and FIR modes,

with data rates of 576 Kbps, 1.152 Mbps and 4.0 Mbps.

Details on the frame format, encoding schemes, CRC

sequences, etc. are provided in the appropriate IrDA

documents. The MIR transmitter front-end section

performs bit stuffing on the outbound data stream and

places the Start and Stop flags at the beginning and end of

MIR frames. The MIR receiver front-end section removes

flags and “de-stuffs” the inbound bit stream, and checks for

abort conditions.

The FIR transmitter front-end section adds the Preamble as

well as Start and Stop flags to each frame and encodes the

transmit data into a 4PPM (Four Pulse Position Modulation)

data stream. The FIR receiver front-end section strips the

Preamble and flags from the inbound data stream and

decodes the 4PPM data while also checking for coding

violations.

Both MIR and FIR front-ends also automatically append

CRC sequences to transmitted frames and check for CRC

errors on received frames.

2.5.1 High Speed Infrared Transmit

When the transmitter is empty, if either the CPU or the

DMA controller writes data into the TX_FIFO, transmission

of a frame will begin. Frame transmission can be normally

completed by using one of the following methods:

1. S_EOT bit (Set End of Transmission)

This method is used when data transfers are performed

in PIO mode. When the CPU sets the S_EOT bit before

writing the last byte into the TX_FIFO, the byte will be

tagged with an EOF indication. When this byte reaches

the TX_FIFO bottom, and is read by the transmitter front-

end, a CRC is appended to the transmitted DATA and

the frame is normally terminated.

2. DMA TC Signal (DMA Terminal Count)

This method is used when data transfers are performed

in DMA mode. It works similarly to the previous method

except that the tagging of the last byte of a frame occurs

when the DMA controller asserts the TC signal during the

write of the last byte to the TX_FIFO.

3. Frame Length Counter

This method can be used when data transfers are

performed in either PIO or DMA mode. The value of the

FEND_MD bit in the IRCR2 register determines whether

the Frame Length Counter is effective in the PIO or DMA

mode. The counter is loaded from the Frame Length

Register (TFRL) at the beginning of each frame, and it is

decrements as each byte is transmitted. An EOF is

generated when the counter reaches zero. This method

allows a large data block to be automatically split into

equal-size back-to-back frames, plus a shorter frame that

is terminated by the DMA TC signal when an 8237 type

DMA controller is used.

An option is also provided to stop transmission at the end

of each frame. This happens when the transmitter frameend stop mode is selected (TX_MS bit in IRCR2 register

set to 1).

By using this option, the software can send frames of

different sizes without re-initializing the DMA controller

for each frame. After transmission of each frame, the

transmitter stops and generates an interrupt. The

software loads the length of the next frame into the TFRL

register and restarts the transmitter by clearing the

TXHFE bit in the ASCR register.

While a frame is being transmitted, data must be written to

the TX_FIFO at a rate dictated by the transmission speed.

If the CPU or DMA controller fails to meet this requirement,

a transmitter under-run will occur, an inverted CRC is

appended to the frame being transmitted, and the frame is

terminated with a Stop flag. Data transmission will then

stop. Transmission of the inverted CRC will guarantee that

the remote receiving device will receive the frame with a

CRC error and will discard it.

Following an under-run condition, data transmission always

stops at the next frame boundary. The frame bytes from

the point where the under-run occurred to the end of the

frame will not be sent out to the external infrared interface.

Nonetheless, they will be removed from the TX_FIFO by

the transmitter and discarded. The under-run indication will

be reported only when the transmitter detects the end of

frame via one of the methods described above. The

software can do various things to recover form an underrun condition. For example, it can simply clear the underrun condition by writing a 1 into bit 6 of ASCR and retransmit the under-run frame later, or it can re-transmit it

immediately, before transmitting other frames.

If it chooses to re-transmit the frame immediately, it needs

to perform the following steps:

1. Disable DMA controller, if DMA mode was selected.

2. Read the TXFLV register to determine the number of

bytes in the TX_FIFO. (This is needed to determine

www.national.com

12

the exact point where the under-run occurred, and

whether or not the first byte of a new frame is in the

TX_FIFO).

3. Reset TX_FIFO.

4. Backup DMA controller registers.

5. Clear Transmitter under-run bit.

6. Re-enable DMA controller.

Note: the setting of the DMA_EN bit in the extended-mode MCR register only controls PIO or DMA mode.

The device treats CPU and DMA access cycles the same except that DMA cycles always access the TX_ FIFO or

RX_FIFO, regardless of the selected bank. When DMA_EN is set to 1, the CPU can still access the TX_FIFO and

RX_FIFO. The CPU accesses will, however, be treated as DMA accesses as far as the function of the FEND_MD bit

is concerned.

2.5.2 High Speed Infrared Receive

When the receiver front-end detects an incoming frame, it

will start de-serializing the infrared bit stream and load the

resulting data bytes into the RX_FIFO. When the EOF is

detected, two or four CRC bytes are appended to the

received data, and an EOF flag is written into the tag

section of the RX_FIFO along with the last byte. In the

present implementation, the CRC bytes are always

transferred to the RX_FIFO following the data. Additional

status information, related to the received frame, is also

written into the RX_FIFO tag section at this time. The

status information will be loaded into the LSR register when

the last frame byte reaches the RX_FIFO bottom.

The receiver keeps track of the number of received bytes

from the beginning of the current frame. It will only transfer

to the RX_FIFO a number of bytes not exceeding the

maximum frame length value, which is programmed via the

RFRML register in bank 4. Any additional frame bytes will

be discarded. When the maximum frame length value is

exceeded, the MAX_LEN error flag will be set.

Although data transfers from the RX_FIFO to memory can

be performed either in PIO or DMA mode, DMA mode

should be used due to the high data rates.

In order to handle back-to-back incoming frames, when

DMA mode is selected and an 8237 type DMA controller is

used, an 8-level ST_FIFO (Status FIFO) is provided. When

an EOF is detected, in 8237 DMA mode, the status and

byte count information for the frame is written into the

ST_FIFO. An interrupt is generated when the ST_FIFO

level reaches a programmed threshold or an ST_FIFO

time-out occurs.

The CPU uses this information to locate the frame

boundaries in the memory buffer where the 8237 type DMA

controller has transferred the data.

During reception of multiple frames, if the RX_FIFO and/or

the ST_FIFO fills up, due to the DMA controller or CPU not

serving them in time, one or more frames can be crushed

and lost. This means that no bytes belonging to these

frames were written to the RX_FIFO. In fact, a frame will

be lost in 8237 mode when the ST_FIFO is full for the

entire time during which the frame is being received, even

though there were empty locations in the RX_FIFO. This is

because no data bytes can be loaded into the RX_FIFO

and then transferred to memory by the DMA controller,

unless there is at least one available entry in the ST_FIFO

to store the number of received bytes. This information, as

mentioned before, is needed by the software to locate the

frame boundaries in the DMA memory buffer.

In the event that a number of frames are lost, for any of the

reasons mentioned above, one or more lost-frame

indications including the number of lost frames, are loaded

into the ST_FIFO.

Frames can also be lost in PIO mode, but only when the

RX_FIFO is full. The reason being that, in these cases, the

ST_FIFO is only used to store lost-frame indications. It will

not store frame status and byte count.

2.6 Consumer Electronics IR (CEIR) Mode

The Consumer Electronics IR circuitry is designed to

optimally support all the major protocols presently used in

remote-controlled home entertainment equipment. The

main protocols currently in use are RC-5, RC-6, RECS 80,

NEC and RCA. The PC87109, in conjunction with an

external optical module, provides the physical layer

functions necessary to support these protocols. These

functions include modulation, demodulation, serialization,

de-serialization, data buffering, status reporting, interrupt

generation, etc. The software is responsible for the

generation of the infrared code to be transmitted, and for

the interpretation of the received code.

2.6.1 Consumer Electronics IR Transmit

The code to be transmitted consists of a sequence of bytes

that represent either a bit string or a set of run-length

codes. The number of bits or run-length codes usually

needed to represent each infrared code bit depends on the

infrared protocol used. The RC-5 protocol, for example,

needs two bits or between one and two run-length codes to

represent each infrared code bit.

CEIR transmission starts when the transmitter is empty and

either the CPU or the DMA controller writes code bytes into

the TX_FIFO. The transmission is normally completed

when the CPU sets the S_EOT bit in the ASCR register

before writing the last byte, or when the DMA controller

activates the TC signal. Transmission is also completed if

the CPU simply stops transferring data and the transmitter

becomes empty. In this case however, a transmitter underrun condition will be generated. The under-run must be

cleared before the next transmission can occur. The code

bytes written into the TX_FIFO are either de-serialized or

run-length decoded, and the resulting bit string is

modulated by a sub-carrier signal and sent to the

transmitter LED. The bit rate of this bit string, like in the

UART mode, is determined by the value programmed in the

baud generator divisor register. Unlike a UART

www.national.com

13

transmission, start, stop and parity bits are not included in

the transmitted data stream. Logic 1 in the bit string will

keep the LED off, so no infrared signal is transmitted. A

logic 0 will generate a sequence of modulating pulses

which will turn on the transmitter LED. Frequency and pulse

width of the modulating pulses are programmed by the

MCFR and MCPW bits in the IRTXMC register as well as

the TXHSC bit in the RCCFG register.

The RC_MMD bits select the transmitter modulation mode.

If C_PLS mode is selected, modulation pulses are

generated continuously for the entire time in which one or

more logic 0 bits are being transmitted. If 6_PLS or 8_PLS

modes are selected, 6 or 8 pulses are generated each time

one or more logic 0 bits are transmitted following logic 1 bit.

C_PLS modulation mode is used for RC-5, RC-6, NEC and

RCA protocols. 8_PLS or 6_PLS modulation mode is used

for the RECS 80 protocol. The 8_PLS or 6_PLS mode

allows minimization of the number of bits needed to

represent the RECS 80 infrared code sequence. The

current transmitter implementation supports only the

modulated modes of the RECS 80 protocol. The flash

mode is not supported since it is not popular and is

becoming less frequently used.

Note: The total transmission time for the logic 0 bits must

be equal or greater than 6 or 8 times the period of the

modulation sub-carrier, otherwise fewer pulses will be

transmitted.

2.6.2 Consumer Electronics IR Receive

The CEIR receiver is significantly different from a UART

receiver for two basic reasons. First, the incoming infrared

signals are DASK modulated. Therefore, a demodulation

operation may be necessary. Second, there are no start

bits in the incoming data stream.

Whenever an infrared signal is detected, the operations

performed by the receiver are slightly different depending

on whether or not receiver demodulation is enabled. If the

demodulator is not enabled, the receiver will immediately

switch to the active state. If the demodulator is enabled, the

receiver checks the sub-carrier frequency of the incoming

signal, and it switches to the active state only if the

frequency falls within the programmed range. If this is not

the case, the signal is ignored and no other action is taken.

When the receiver active state is entered, the RXACT bit in

the ASCR register is set to 1. Once in the active state, the

receiver keeps sampling the infrared input signal and

generates a bit streams where logic 1 indicates an idle

condition and logic 0 indicates the presence of infrared

energy. The infrared input is sampled regardless of the

presence of infrared pulses at a rate determined by the

value loaded into the baud generator divisor register. The

received bit string is both de-serialized and assembled into

8-bit characters, or it is converted to run-length encoding

values. The resulting data bytes are then transferred to the

RX_FIFO.

The receiver also sets the RXWDG bit in the ASCR register

each time an infrared pulse signal is detected. This bit is

automatically cleared when the ASCR register is read, and

it is intended to assist the software in determining when the

infrared link has been idle for a certain time. The software

can then stop the data reception by writing a 1 into the

RXACT bit to clear it and return the receiver to the inactive

state.

The frequency bandwidth for the incoming modulated

infrared signal is selected by DFR and DBW bits in the

IRRXDC register. There are two CEIR receiver data

modes: "Over-sampled" and "Programmed-T-Period"

mode. For either mode the sampling rate is determined by

the setting of the baud generator divisor register.

The "Over-sampled" mode can be used with the receiver

demodulator either enabled or disabled. It should be used

with the demodulator disabled when a detailed snapshot of

the incoming signal is needed, for example to determine the

period of the sub-carrier signal. If the demodulator is

enabled, the stream of samples can be used to reconstruct

the incoming bit string. To obtain a good resolution, a fairly

high sampling rate should be selected.

The "Programmed-T-Period" mode should be used with the

receiver demodulator enabled. The T Period represents

one half bit time, for protocols using bi-phase encoding, or

the basic unit of pulse distance, for protocols using pulse

distance encoding. The baud rate is usually programmed to

match the T Period. For long periods of logic low or high,

the receiver samples the demodulated signal at the

programmed sampling rate.

Whenever a new infrared energy pulse is detected, the

receiver will re-synchronize the sampling process to the

incoming signal timing. This reduces timing related errors

and eliminates the possibility of missing short infrared pulse

sequences, especially when dealing with the RECS 80

protocol. In addition, the "Programmed-T-Period" sampling

minimizes the amount of data used to represent the

incoming infrared signal, therefore reducing the processing

overhead in the host CPU.

2.7 FIFO Time-outs

In order to prevent received data from sitting in the RX

_FIFO and/or the ST_FIFO indefinitely, if the programmed

interrupt or DMA thresholds are not reached, time-out

mechanisms are provided.

An RX_FIFO time-out generates a receiver High-DataLevel interrupt and/or a Receiver DMA request if bit 0 of

IER and/or bit 2 of MCR (in extended mode) are set to 1

respectively. An RX_FIFO time-out also sets bit 0 of ASCR

to 1 if the RX_FIFO is below the threshold. This bit is

tested by the software, when a receiver High-Data-Level

interrupt occurs, to decide whether a number of bytes, as

indicated by the RX_FIFO threshold, can be read without

checking bit 0 of the LSR register. An ST_FIFO time-out is

enabled only in MIR and FIR modes, and generates an

interrupt if bit 6 of IER is set to 1.

The conditions that must exist for a time-out to occur in the

various modes of operation are described below. When a

time-out has occurred, it can only be reset when the CPU

or DMA controller reads the FIFO that caused the time-out.

MIR or FIR Modes

RX_FIFO Time-out Conditions:

1. At least one byte is in the RX_FIFO, and

2. More than 64 µs have elapsed since the last byte

was loaded into the RX_FIFO from the receiver logic,

and

www.national.com

14

3. More than 64 µs have elapsed since the last byte

was read from the RX_FIFO by the CPU or DMA

controller.

ST_FIFO Time-out Conditions:

1. At least one entry is in the ST_FIFO, and

2. More than 1 ms has elapsed since the last byte was

loaded into the RX_FIFO from the receiver logic, and

3. More than 1 ms has elapsed since the CPU read the

last entry from the ST_FIFO.

UART, Sharp-IR, SIR Modes

RX_FIFO Time-out Conditions:

1. At least one byte is in the RX_FIFO, and

2. More than four character times have elapsed since

the last byte was loaded into the RX_FIFO from the

receiver logic, and

3. More than four character times have elapsed since

the last byte was read from the RX_FIFO by the CPU

or DMA controller.

CEIR Mode

RX_FIFO Time-out Conditions:

The RX_FIFO Time-out, in CEIR mode, is disabled while

the receiver is active. The conditions for this time-out to

occur are as follows:

1. At least one byte has been in the RX_FIFO for 64 µs

or more, and

2. The receiver has been inactive (RXACT=0) for 64 µs

or more, and

3. More than 64 µs have elapsed since the last byte

was read from the RX_FIFO by the CPU or DMA

controller.

2.8 Transmit Deferral

This feature allows the software to send short high-speed

data frames in PIO mode without the risk of a transmitter

under-run being generated. Even though this feature is

available and works the same way in all modes, it will most

likely be used in MIR and FIR modes to support high-speed

negotiations. This is because in other modes, either the

transmit data rate is relatively low and thus the CPU can

keep up with it without letting an under-run occur, as in the

case CEIR Mode, or transmit under-runs are allowed and

are not considered to be error conditions.

Transmit deferral is available only in extended mode and

when the TX_FIFO is enabled. When transmit deferral is

enabled (TX_DFR bit of MCR set to 1) and the transmitter

becomes empty, an internal flag will be set that locks the

transmitter. If the CPU now writes data into the TX_FIFO,

the transmitter will not start sending the data until the

TX_FIFO level reaches either 14 for a 16-level TX_FIFO, or

30 for a 32-level TX_FIFO, at which time the internal flag is

cleared. The internal flag is also cleared and the

transmitter starts transmitting when a time-out condition is

reached. This prevents some bytes from being in the

TX_FIFO indefinitely if the threshold is not reached.

A timer that is enabled when the internal flag is set and

there is at least one byte in the TX_FIFO implements the

time-out mechanism. Whenever a byte is loaded into the

TX_FIFO the timer gets reloaded with the initial value. If no

bytes are loaded for a 64 µs time, the timer times out and

the internal flag gets cleared, thus enabling the transmitter.

2.9 Automatic Fallback to 16550

Compatibility Mode

This feature is designed to support existing legacy software

packages using the 16550 UART.

For proper operation, many of these software packages

require that the device look identical to a plain 16550 since

they access the UART registers directly.

Due to the fact that several extended features as well as

new operational modes are provided, the user must make

sure that the device is in the proper state before a legacy

program can be executed.

The fallback mechanism is designed for this purpose. It

eliminates the need for user intervention to change the

state of the device, when a legacy program must be

executed following completion of a program that used any

of the device’s extended features.

This mechanism automatically switches the device to

16550 compatibility mode and turns off any extended

features whenever the baud generator divisor register is

accessed through the LBGDL or LBGDH ports in register

bank 1.

In order to avoid spurious fallbacks, baud generator divisor

ports are provided in bank 2. Accesses of the baud

generator divisor through these ports will change the baud

rate setting but will not cause a fall back.

New programs, designed to take advantage of the device

extended features, should not use LBGDL and LBGDH to

change the baud rate. They should use the BGDL or

BGDH instead.

A fallback can occur from either extended or non-extended

modes. If extended mode is selected, fallback is always

enabled. In this case, when a fallback occurs, the following

happens:

1. Transmitter and receiver FIFOs will switch to 16 levels.

2. A value of 13 will be selected for the baud generator

prescaler.

3. The ETDLBK and BTEST bits in the EXCR1 Register

will be cleared.

4. UART mode will be selected.

5. A switch to non-extended mode will occur.

When a fallback occurs from non-extended mode, only the

first three of the above actions will take place. No switching

to UART mode occurs if either Sharp-IR or SIR infrared

modes were selected. This prevents spurious switching to

UART mode when a legacy program, running in infrared

mode, accesses the baud generator divisor register from

bank 1.

Setting the LOCK bit in the EXCR2 register can disable

fallback from non-extended mode. When Lock is set to 1

and the device is in non-extended mode, two scratch-pad

registers overlaid with LBGDL and LBGDH are enabled.

Any attempted CPU access of the baud generator divisor

register through LBGDL and LBGDH will access the

scratch-pad registers, and the baud rate setting will not be

affected. This feature allows existing legacy programs to

run faster than 115.2 Kbaud without their being aware of it.

www.national.com

15

2.10 Optical Transceiver Interface

The PC87109 implements a very flexible interface for the

external infrared transceiver. Several signals are provided

for this purpose. A transceiver module with one or two

receive signals can be directly interfaced without any

additional logic.

Since various operational modes are supported, the

transmitter power as well as the receiver filter in the

transceiver module must be configured according to the

selected mode.

Two special interface pins (ID/IRSL[1-0]) are used to

control the operational mode of the infrared transceiver.

The logic levels of the ID/IRSL[1-0] pins are directly

controlled by the software (through the setting of bits 1-0 in

the IRCFG1 register).

The ID/IRSL[1-0] pins will power up as inputs and can be

driven by an external source. When in input mode, they

can be used to read the identification data of Plug-n-Play

infrared adapters.

The ID0/IRSL0/IRRX2 pin can also function as an input to

support an additional infrared receive signal. In this case,

however, only one configuration pin will be available. The

IRSL0_DS and IRSL1_DS bits in the IRCFG4 register

determine the direction of the ID/IRSL[1-0] pins.

www.national.com

16

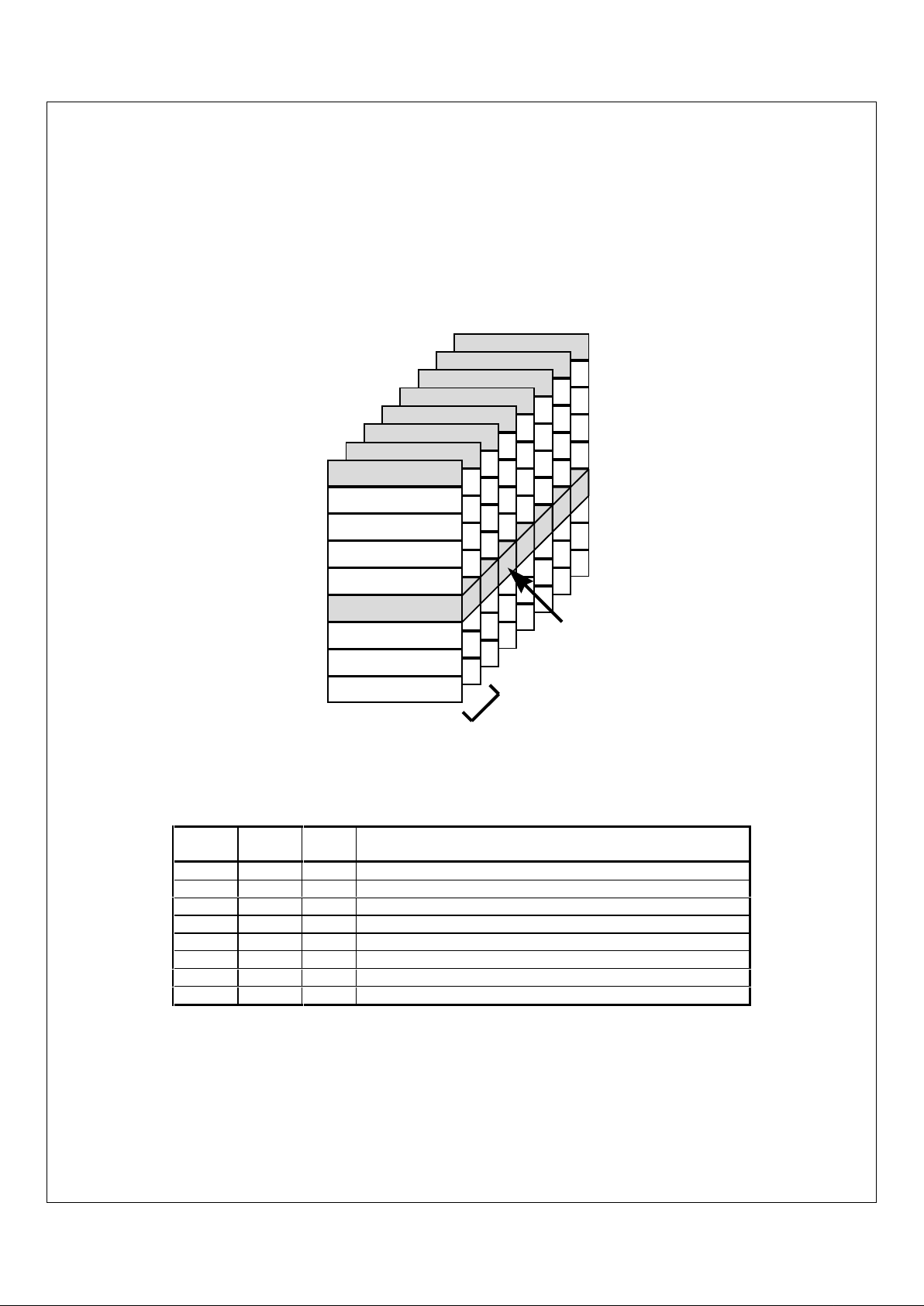

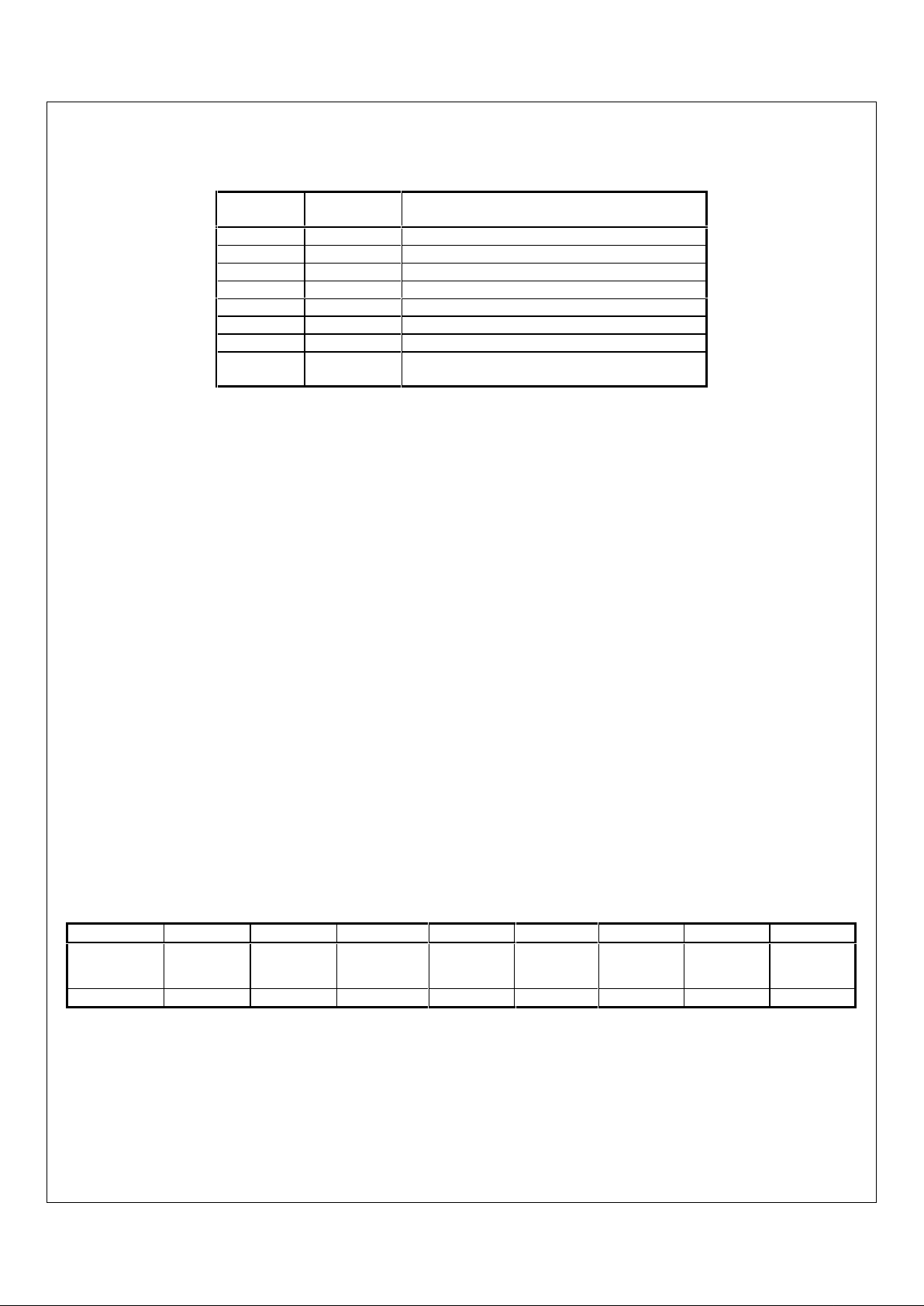

3.0 Architectural Description

Eight register banks are provided to control the operation of the UIR module. These banks are mapped into the same address

range, and only the selected bank is directly accessible by the software. The address range spans 8 byte locations. The BSR

register is used to select the bank and is common to all banks. Therefore, each bank defines seven new registers. The register

banks can be divided into two sets. Banks 0-3 are used to control both UART and infrared modes of operation; banks 4-7 are

used to control and configure the infrared modes only. The register bank main functions are listed in Table 3-1. Descriptions of

the various registers are given in the following sections.

Bank 7

Bank 6

Bank 5

Bank 4

Bank 3

Bank 2

Common

Register

Throughout

All Banks

16550 Banks

Bank 1

Reg 0

Reg 1

Reg 2

LCR/BSR

Reg 4

Reg 5

Reg 6

Reg 7

Bank 0

Figure 3-1. Register Bank Architecture

Bank UART

ModeIRMode

Description

0

✓✓

Global Control and Status Registers

1

✓✓

Legacy Bank

2

✓✓

Baud Generator Divisor and Extended Control

3

✓✓

Identification and Shadow Registers

4

✓

Timer and Counters

5

✓

Infrared Control and Status FIFO

6

✓

Infrared Physical Layer Configuration

7

✓

CEIR and Optical Transceiver Configuration

Table 3-1. Register Banks Summary

www.national.com

17

3.1 Bank 0

Address

Offset

Register

Name

Description

0

TXD/RXD

Transmit/Receive Data Ports

1

IER

Interrupt Enable Register

2

EIR/FCR

Event Identification/FIFO Control Registers

3

LCR/BSR

Link Control/Bank Select Registers.

4

MCR

Mode Control Register

5

LSR

Link Status Register

6

Reserved

Reserved (return 0x30 upon read).

7

SPR/ASCR

Scratch-pad /Auxiliary Status and control

Register

Table 3-2. Bank 0 Register Set

3.1.1 TXD/RXD - Transmit/Receive Data Ports

These ports share the same address.

TXD is accessed during CPU write cycles. It provides the write data path to the transmitter holding register when the FIFOs are

disabled, or to the TX_FIFO top location when the FIFOs are enabled.

RXD is accessed during CPU read cycles. It provides the read data path from the receiver holding register when the FIFOs are

disabled, or from the RX_FIFO bottom location when the FIFOs are enabled.

DMA cycles always access the transmitter and receiver holding registers or FIFOs, regardless of the selected bank.

3.1.2 IER - Interrupt Enable Register

This register controls the enabling of the various interrupts. Some interrupts are common to all operating modes, while others

are only available with specific modes. Bits 4 to 7 can be set in extended mode only. They are cleared in non-extended mode.

When a bit is set to 1, an interrupt is generated when the corresponding event occurs. In the non-extended mode most events

can be identified by reading the LSR and MSR registers. Reading the EIR register after the corresponding interrupt has been

generated can only identify the receiver high-data-level event. In the extended mode event flags in the EIR register identify

events. Upon reset, all bits are set to 0.

Note1: If the interrupt signal drives an edge-sensitive interrupt controller input, it is advisable to disable all interrupts by clearing all the IER

bits upon entering the interrupt routine, and re-enable them just before exiting it. This will guarantee proper interrupt triggering in the

interrupt controller in case one or more interrupt events occur during execution of the interrupt routine.

Note 2: If an interrupt source must be disabled, the CPU can do so by clearing the corresponding bit in the IER register. However, if an

interrupt event occurs just before the corresponding enable bit in the IER register is cleared, a spurious interrupt may be

generated. To avoid this problem, the clearing of any IER bit should be done during execution of the interrupt service routine. If

the interrupt controller is programmed for level-sensitive interrupts, the clearing of IER bits can also be performed outside the

interrupt service routine, but with the CPU interrupt disabled.

Note 3: If the LSR, MSR or EIR registers are to be polled, the interrupt sources which are identified via self-clearing bits should have their

corresponding IER bits set to 0. This will prevent spurious pulses on the interrupt output pin.

Bits B7 B6 B5 B4 B3 B2 B1 B0

Function

TMR_IE SFIF_IE TXEMP_IE DMA_IE res LS_IE/

TXHLT_IE

TXLDL_IE RXHDL_IE

Reset State

00 0 00000

Figure 3-2. Interrupt Enable Register

B0

RXHDL_IE - Receiver High-Data-Level Interrupt Enable.

B1

TXLDL_IE - Transmitter Low-Data-Level Interrupt Enable.

Loading...

Loading...