NSC LM2453TA Datasheet

April 2000

LM2453

Monolithic Triple 6 nS CRT Driver With Integrated Clamp

and G1 Blanking

LM2453 Monolithic Triple 6 nS CRT Driver With Integrated Clamp and G1 Blanking

General Description

The AC2DC driver is an integrated high voltage triple CRT

driver circuit designed for use in color monitor applications.

The input signal interface to the IC is a multiplexed signal

containing both clamp and video signal information, relative

to a 1.7 V

The IC contains three high gain, high input impedance, wide

band amplifiers which directly drive the RGB cathodes of a

CRT. Each channel has its gain internally set to −52 and can

drive CRT capacitive loads as well as resistive loads present

in other applications, limited only by the package’s power

dissipation.

Integrated with the driver is triple clamp circuit for DC recovery of each of the AC coupled outputs. The DC clamp circuit

amplifies the clamp signal that is multiplexed on the video

signal input. The DC clamp amplifiers are high gain, high input impedance amplifiers, setting a low impedance DC level

at the clamp output which can be used to restore the DC

level of the cathode drive. Each channel has a gain that is internally set to +73.

Also integrated within the package is a 40 V

blanking driver that is designed to provide vertical retrace

blanking on G1 of the CRT. This is a current limited, low impedance output capable of driving normal G1 decoupling ca-

reference.

DC

P-P

vertical

pacitances via an external resistor. The output of the G1

driver can also be used to drive a voltage boost capacitor (22

µF). When connected between the G1 drive output and the

120V supply input pin, a 120V boost supply is achieved

which can be used to drive the internal DC clamp circuit,

thereby eliminating the requirement for a 120V clamp supply.

The IC is packaged in an industry standard 15-lead TO-220

molded plastic power package.

Features

n Low power dissipation

n Well matched with LM1253A video pre-amp

n Three wideband video amplifiers

n Three integrated active clamp circuits

n Convenient TO-220 staggered lead package

n Built in horizontal blanking

n Integrated 120V supply and G1 vertical blank drive

circuit

Applications

n 1280 x 1024 Resolution displays up to 85 Hz refresh

n Pixel clock frequencies up to 135 MHz

n Monitors requiring horizontal video blanking

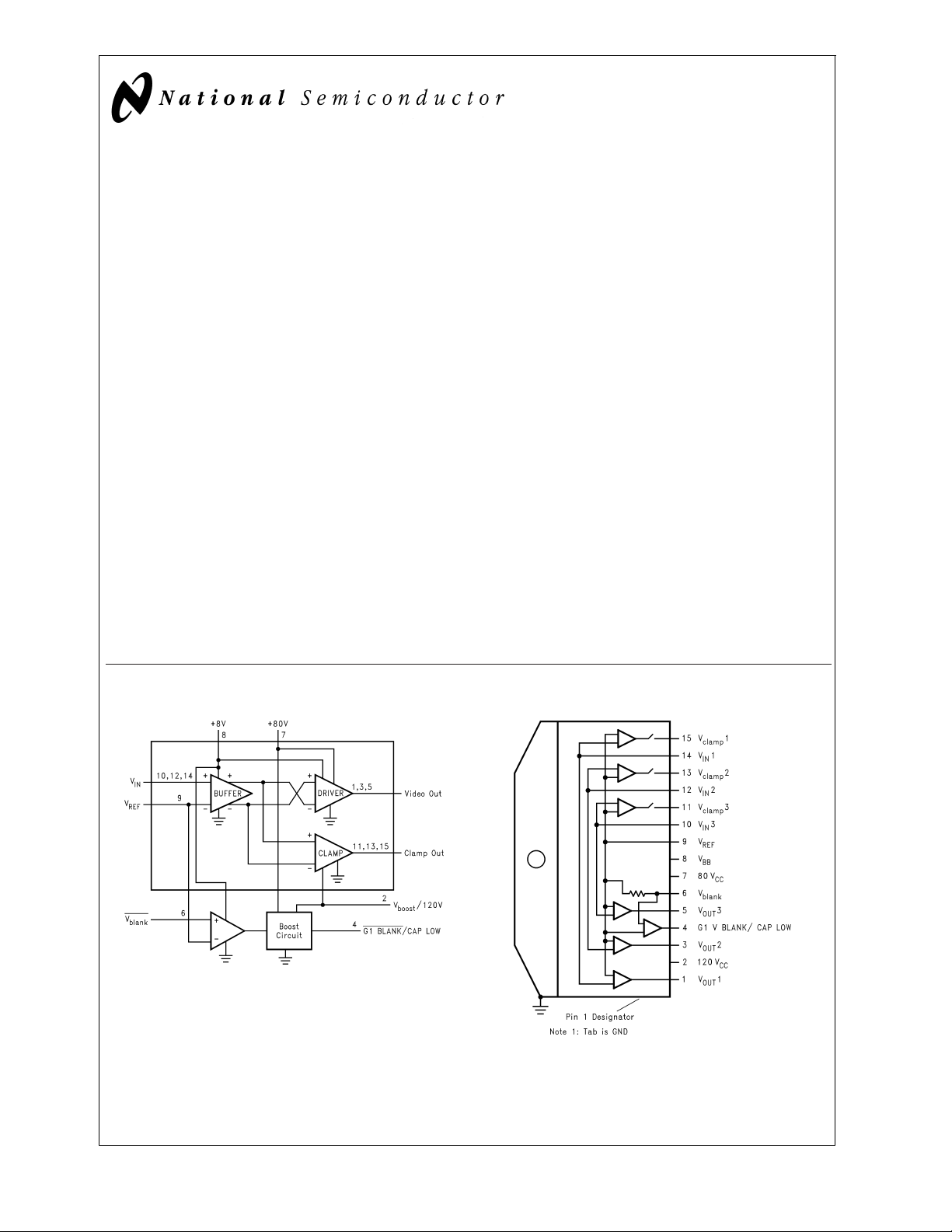

Block Diagram Package Pinout

DS101302-1

FIGURE 1. LM2453 Block Diagram

DS101302-2

FIGURE 2. LM2453 Package Pinout

Order Number LM2453TA

© 2000 National Semiconductor Corporation DS101302 www.national.com

Special Features

LM2453

MULTIPLEXED VIDEO SIGNAL INPUT

The LM2453 accepts the multiplexed video signal from the

LM1253 which contains the video signal and DC clamp level.

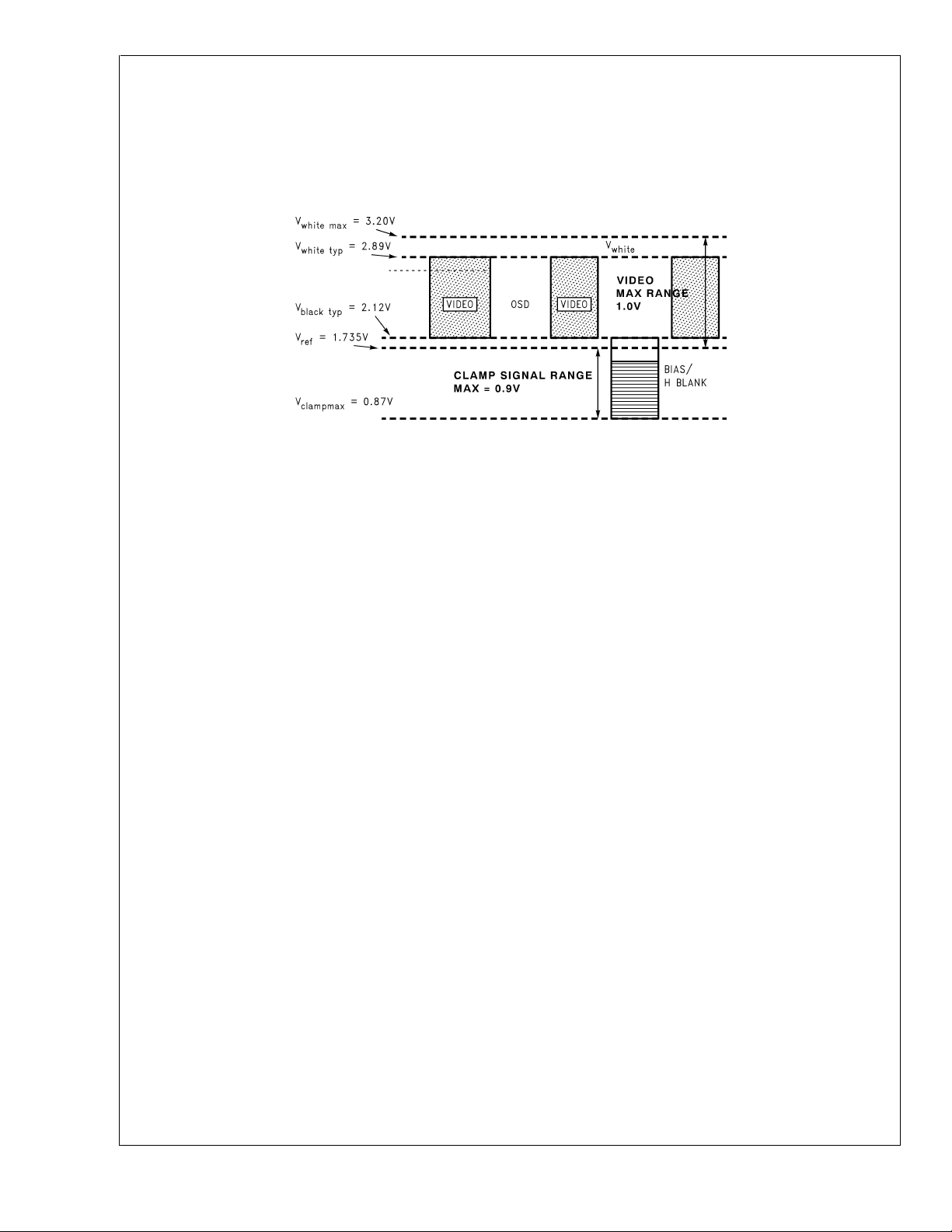

This multiplexed signal is shown in

to simplify the interface between the pre-amp and CRT

Figure 3

. It was designed

FIGURE 3. National LM1253 Multiplexed Video Signal

Driver. Slightly over 1V of dynamic range is provided for the

video and OSD portions of the waveform. The clamp signal

control voltage range is approximately 0.9V. The typical

numbers for the black and white levels shown correspond to

a nominal swing of 40 V

(from 25 to 65) at the video out-

P-P

puts of the LM2453. The clamp pulse lower level is used to

set the voltage at the clamp outputs of the LM2453.

DS101302-3

www.national.com 2

LM2453

Absolute Maximum Ratings (Notes 1, 3)

ESD Tolerance, Machine Model 200V

If Military/Aerospace specified devices are required,

please contact the National Semiconductor Sales Office/

Distributors for availability and specifications.

80V Voltage, V

120V Supply V

Bias Voltage, V

Input Voltage, V

V

BLANK

CC1

CC2

BB

IN

Input Voltage, V

BLANK

Storage Temperature Range, T

STG

−65˚C to +150˚C

+90V

+130V

+15V

0V to 4V

0V to VBBV

Lead Temperature

<

(Soldering,

10 sec.) 300˚C

ESD Tolerance, Human Body

Model 2 kV

Operating Ranges (Note 2)

V

CC1

V

BOOST

V

BB

V

IN

V

REF

V

Input Voltage, V

V

V

BLANK

OUT

CLAMP

BLANK

Case Temperature −20˚C to 100˚C

+60V to +85V

V

to +125V

CC1

7.0V to +9V

0.8V to +3.5V

+1.6V to +1.9V

0V to 5.5V

+15V to +78V

+55V to +118V

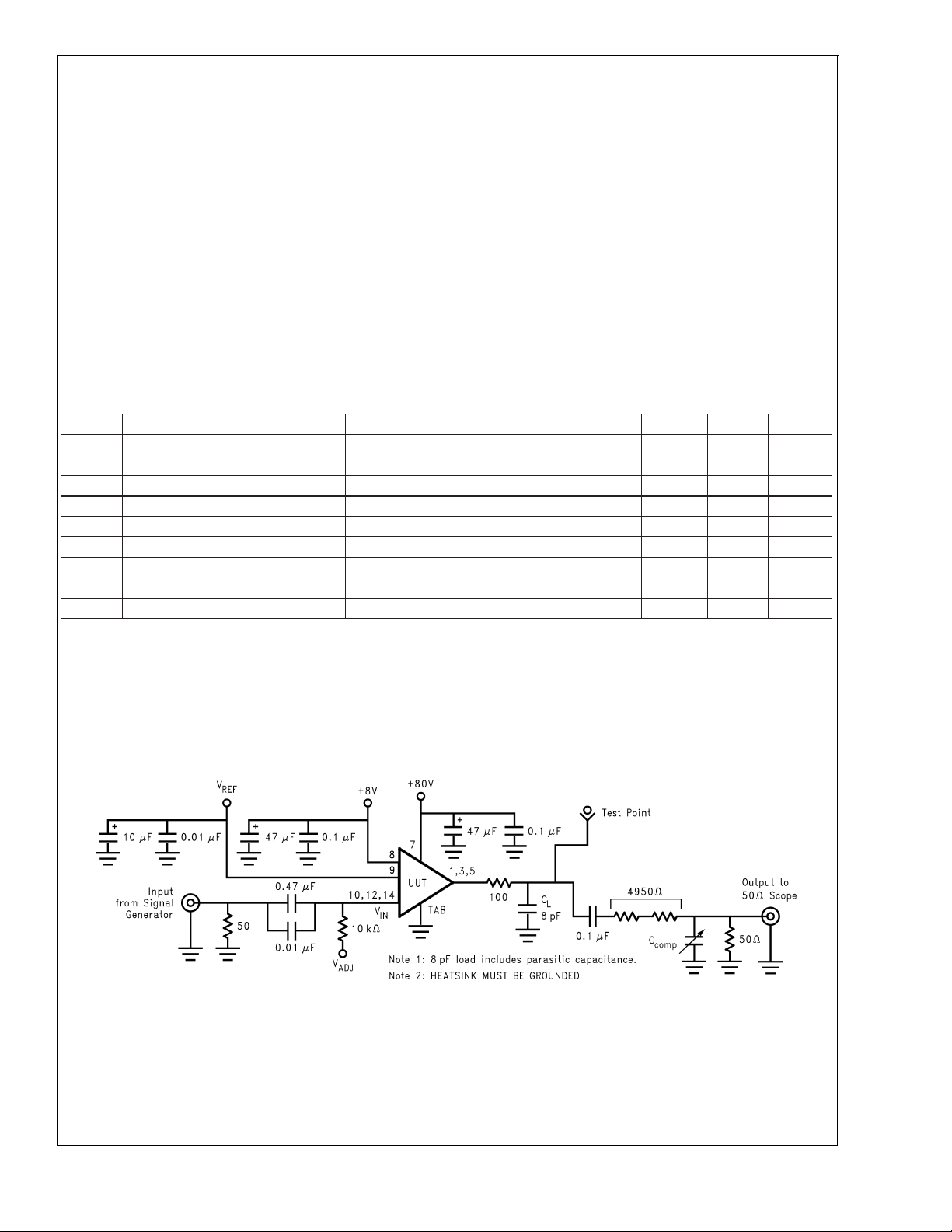

AC Driver Electrical Characteristics

(See

Figure 4

Unless otherwise noted: VCC= +80V, VBB= +8V, VIN= 2.500 VDC,CL= 8 pF, Output = 40 VPPat 1 MHz, TC= 50˚C,

V

= 1.735V, HEATSINK MUST BE GROUNDED.

REF

Symbol Parameter Conditions Min Typ Max Units

I

CC

I

BB

I

OUTTYP

A

VTYP

I

RTYP

+OS Overshoot on Rising Edge 5 %

t

FTYP

−OS Overshoot on Falling Edge 6 %

LE Linearity Error V

Note 1: Limits of “Absolute Maximum Ratings” indicate limits below which damage to the device will not occur.

Note 2: Limits of“Operating Ratings” indicate required boundaries of conditions for which the device is functional, but is not guaranteed to meet specific performance

limits.

Note 3: All voltages are measured with respect to GND, unless otherwise specified.

Note 4: Linearity error is the variation in DC gain from V

Note 5: Input from signal generator: t

for Test Circuit)

VCCSupply Current All 3 Channels, No Output Load 35 45 mA

VBBSupply Current All 3 Channels, No Output Load 22 35 mA

Typical DC Output Voltage No AC Input Signal, VIN= 2.100 V

DC

62 66 70 V

DC

Typical DC Voltage Gain No AC Input Signal −52 V/V

Typical Rise Time 10% to 90%, (Note 5) 6.0 ns

Typical Fall Time 90% to 10%, (Note 5) 6.0 ns

2.0 VDCto 3.0 VDC, (Note 4) 6 %

IN

= 2.0 to 3.0.

IN

r,tf

<

1 ns.

DRIVER Test Circuit

FIGURE 4. Test Circuit (One Channel)

Figure 4

FET probe. The 4950Ω resistor at the output forms a 200:1 voltage divider when connected to a 50Ω load. C

justed for equivalent performance to the FET probe. Performance will be affected slightly by the 5k load.

shows the test circuit for the LM2453. This circuit allows testing of the LM2453 in a 50Ω environment as well as with a

COMP

DS101302-4

must be ad-

www.national.com3

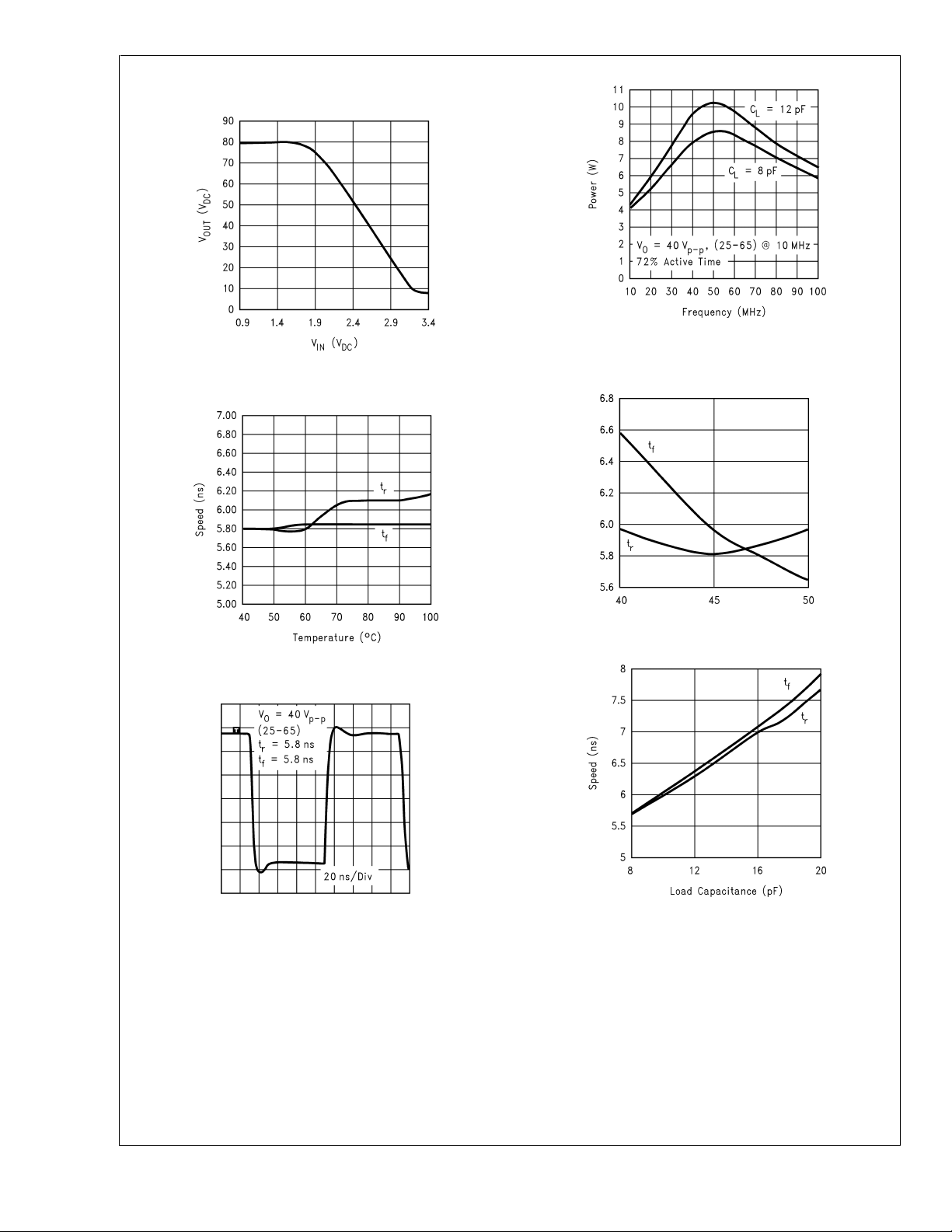

DRIVER Test Circuit (Continued)

LM2453

FIGURE 5. CRT Driver VOvs V

DS101302-5

IN

DS101302-8

FIGURE 8. CRT Driver Power

Dissipation vs. Frequency

DS101302-6

FIGURE 6. CRT Driver Speed vs. Temperature

DS101302-7

FIGURE 7. CRT Driver Transient Response

DS101302-9

FIGURE 9. CRT Driver Speed vs. Offset

DS101302-10

FIGURE 10. Speed vs. Load

www.national.com 4

LM2453

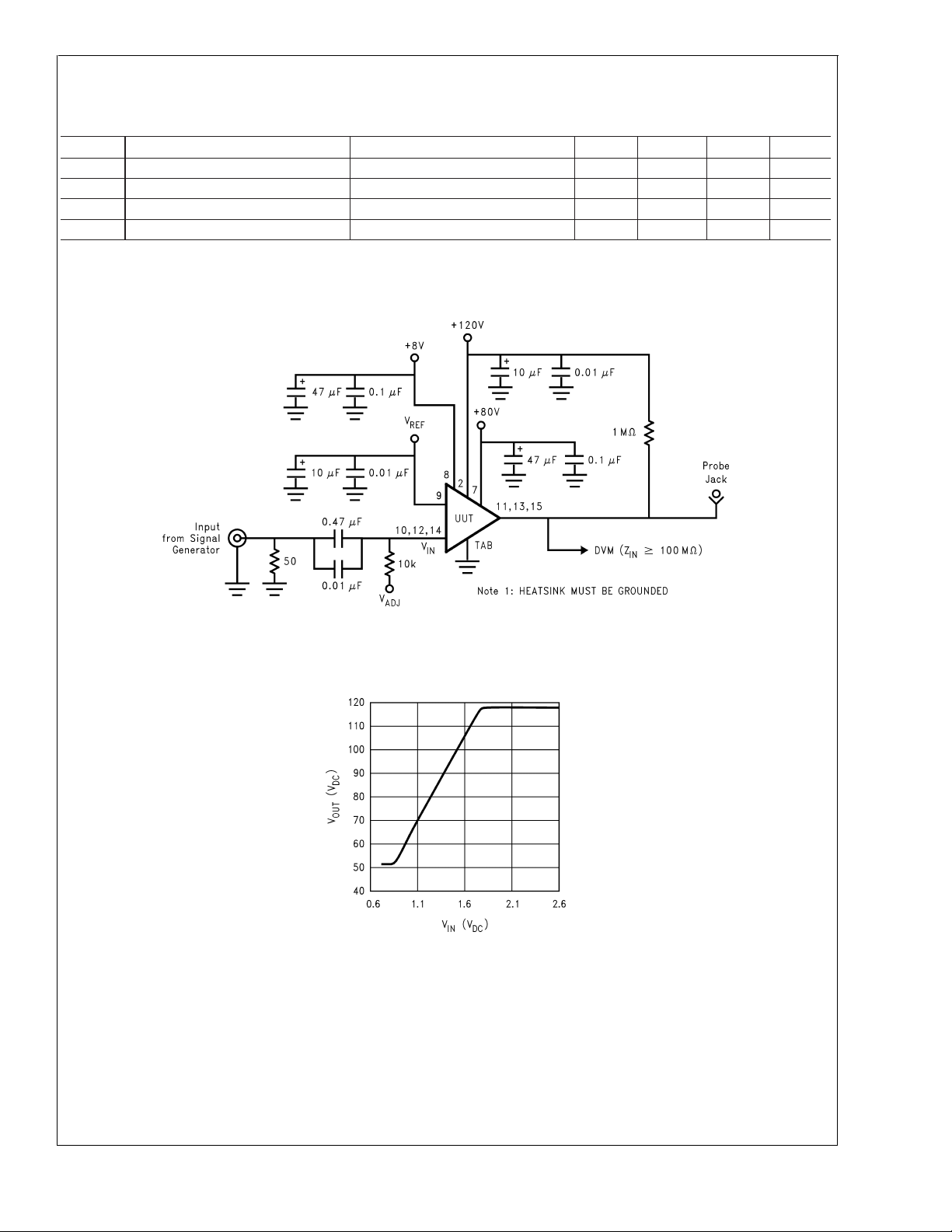

DC CLAMP Electrical Characteristic Targets and Limits (See

Unless otherwise noted: V

CC1

= +80V, V

= 120V, VBB= +8V, TC= 50˚C, V

CC2

= 1.735V, SW1 open.

REF

Figure 11

for Test Circuit)

HEATSINK MUST BE GROUNDED.

Symbol Parameter Conditions Min Typ Max Units

I

CC2

V

OUT

A

VTYP

LE

TYP

Note 6: Linearity Error is the variation in DC gain from VIN= 1.0V to VIN= 1.6V.

V

Supply Current All 3 Channels VIN= 1.20 V

CC2

DC

47mA

DC Output Voltage No AC Input Signal, VIN= 1.400V 87 92 97 V

Typical DC Voltage Gain No AC Input Signal 73

Typical Linearity Error No AC Input Signal (Note 6) 2 %

DC

Clamp Amplifier Test Circuit

Figure 7

shows the test circuit for evaluation of the LM2453 clamp amplifier. A high impedance VM (>100 MΩ) is used for DC

measurements at the outputs.

FIGURE 11. Test Circuit (One Channel)

DS101302-12

FIGURE 12. Clamp Circuit VOvs. V

IN

DS101302-11

www.national.com5

Loading...

Loading...