NSC LM2405T Datasheet

LM2405

Monolithic Triple 7 ns CRT Driver

General Description

The LM2405 is an integrated high voltage CRT driver circuit

designed for use in color monitor applications. The IC contains three high input impedance, wide band amplifiers

which directly drivethe RGB cathodes of a CRT. Each channel has its gain internally set at −14 and can drive CRT capacitive loads as well as resistive loads presented by other

applications, limited only by the package’s power dissipation.

The IC is packaged in an industry standard 11 lead TO-220

molded plastic power package. See thermal considerations

on page 5.

Features

n Rise/fall times typically 7 ns with 8 pF load

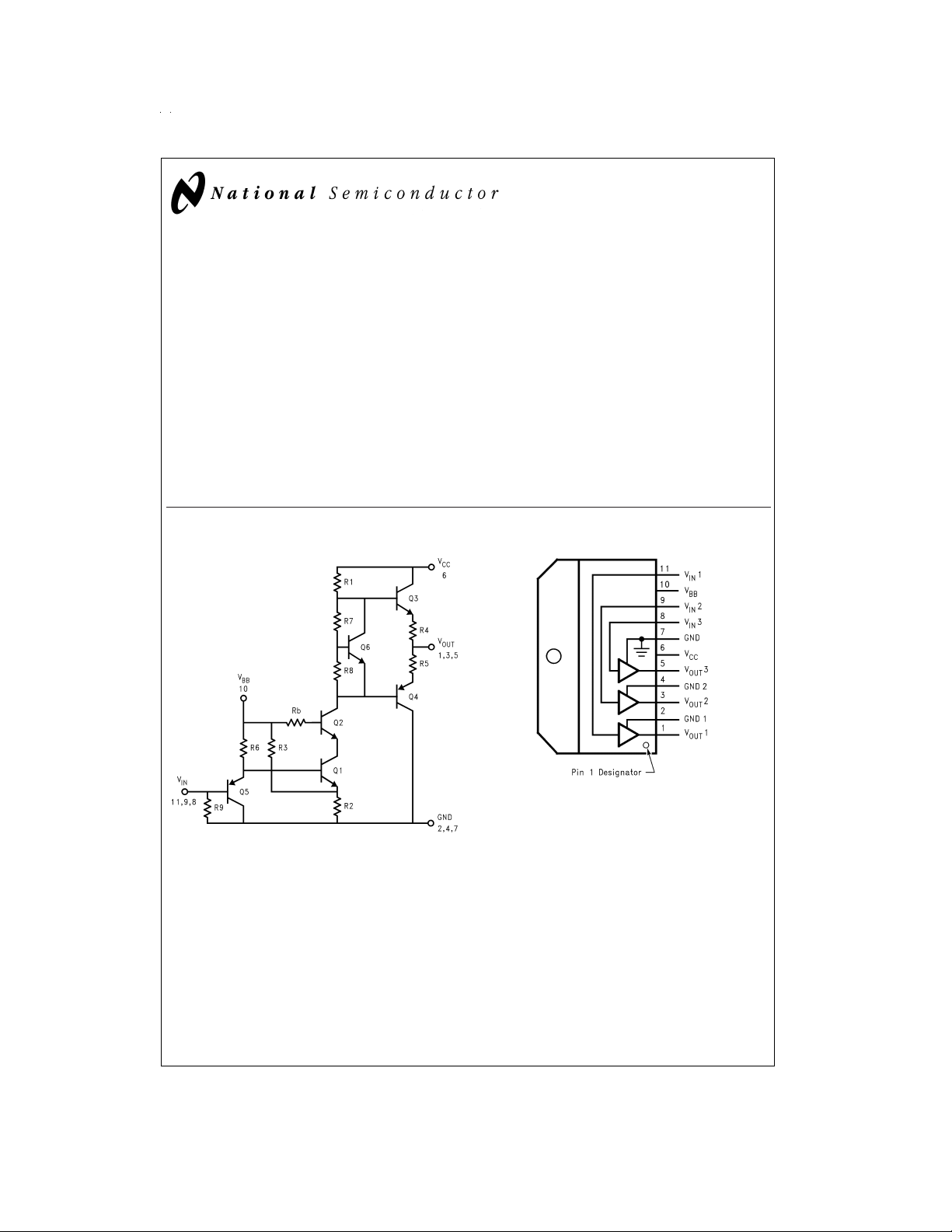

Schematic and Connection Diagram

n Output swing capability:

50 V

40 V

30 V

n Pinout designed for easy PCB layout

n 0V to 6V input range

n Stable with 0 pF–20 pF capactive loads

n Convenient TO-220 staggered lead package style

Applications

n CRT driver for 1280 x 1024 (Non-interlaced) and XGA

display resolution color monitors

n Pixel clock frequency up to 130 MHz

n Monitors using video blanking

LM2405 Monolithic Triple 7 ns CRT Driver

August 1999

=

for V

PP

for V

PP

for V

PP

80

CC

=

70

CC

=

60

CC

TabisatGND

Top View

DS012682-1

FIGURE 1. Simplified Schematic Diagram (One

Channel)

© 1999 National Semiconductor Corporation DS012682 www.national.com

Order Number LM2405T

DS012682-2

Absolute Maximum Ratings (Notes 1, 3)

Supply Voltage (V

Bias Voltage (V

Input Voltage (V

Storage Temperature Range

) −65˚C to +150˚C

(T

STG

Lead Temperature

(Soldering,

) +90V

CC

) +16V

BB

) −0.5V to V

IN

<

10 sec.) 300˚C

BIAS

+ 0.5V

Operating Ranges (Note 2)

V

CC

V

BB

V

IN

Case Temperature (T

Do not operate the part without a heat sink.

) −20˚C to +100˚C

CASE

+60V to +85V

+8V to +15V

0V to +6V

ESD Tolerance 2 kV

Electrical Characteristics

Unless otherwise noted: V

=

T

25˚C.

A

CC

=

+80V, V

Symbol Parameter Conditions

I

I

V

A

∆A

CC

BB

OUT

V

V

Supply Current Per Channel, No Output Load 18 30 mA

Bias Current 38 mA

DC Output Voltage No Input Signal 47 50 53 V

DC Voltage Gain No Input Signal −12 −14 −16

Gain Matching No Input Signal (Note 4) 1.0 dB

LE Linearity Error No Input Signal (Notes 4, 5) 8

t

R

t

F

Note 1: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur.

Note 2: Operating ratings indicate conditions for which the device is functional, but do not guarantee specific performance limits. For guaranteed specifications and

test conditions, see the Electrical Characteristics. The guaranteed specifications apply only for the test conditions listed. Some performance characteristics may

change when the device is not operated under the listed test conditions.

Note 3: All voltages are measured with respect to GND, unless otherwise specified.

Note 4: Calculated value from Voltage Gain test on each channel.

Note 5: Linearity Error is the variation in DC gain from V

Note 6: Input from signal generator: t

Rise Time 10%to 90

Fall Time 90%to 10

R,tF

=

+12V, V

BB

1 ns.

IN

<

%

%

=

+ 1.3V to V

=

+2.6V (at LM2405 input pins), C

IN

Min Typical Max

=

+3.9V.

IN

=

8 pF, Output=40 V

L

LM2405

at 1 MHz,

PP

Units

7ns

5.5 ns

DC

%

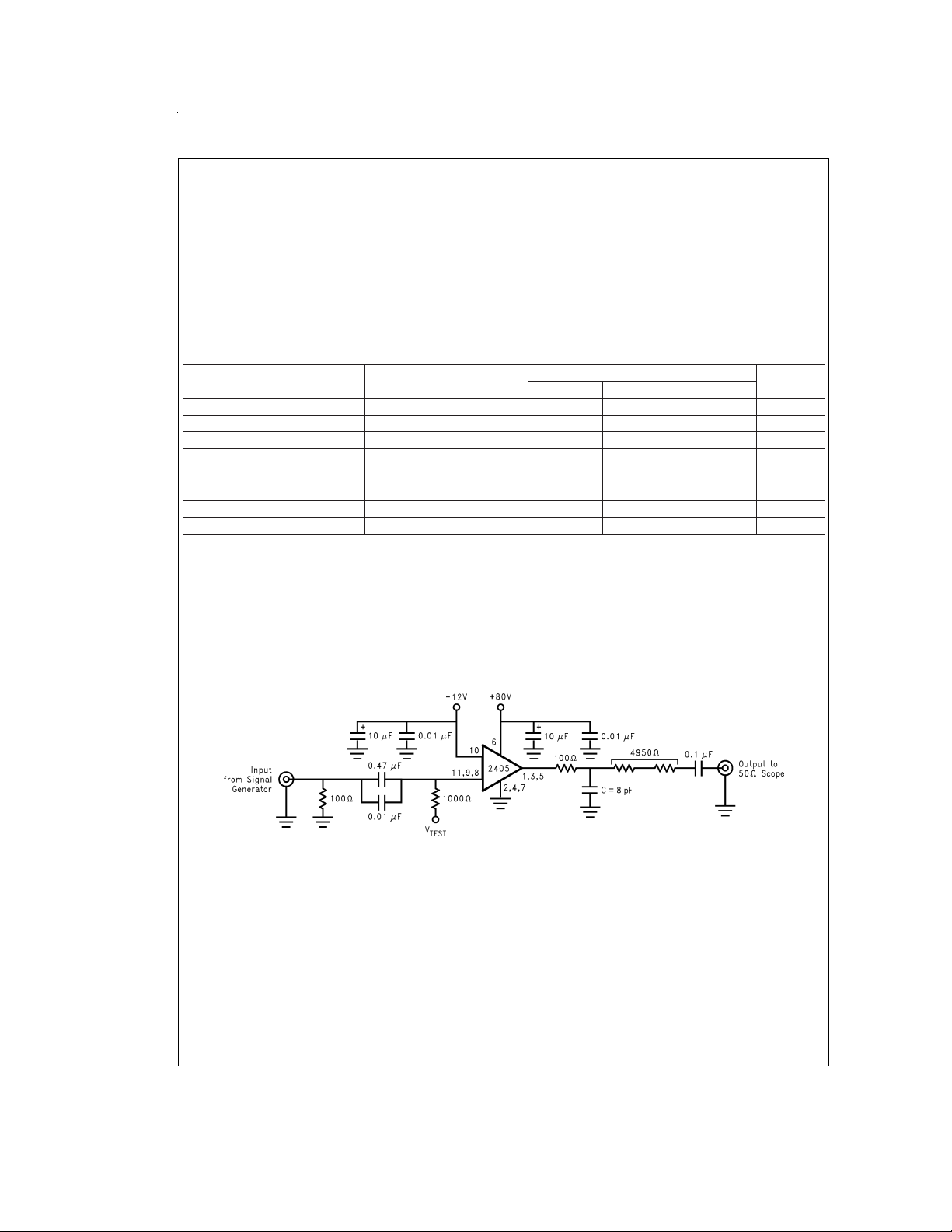

AC Test Circuit

Note: 8 pF is total load plus parasitic capacitance.

Note: Adjust Vtest for +2.6V DC at LM2405 input pins. See “Input Resistance” section of Application Hints.

FIGURE 2. Test Circuit (One Channel)

Figure 2

LM2405. This circuit is designed to allow testing of the

LM2405 in a 50Ω environment, such as a pulse generator,

oscilloscope or network analyzer. The 4950Ω resistor at the

output forms a 100:1 voltage divider when connected to a

50Ω load.

www.national.com 2

shows a typical test circuit for evaluation of the

DS012682-3

AC Test Circuit (Continued)

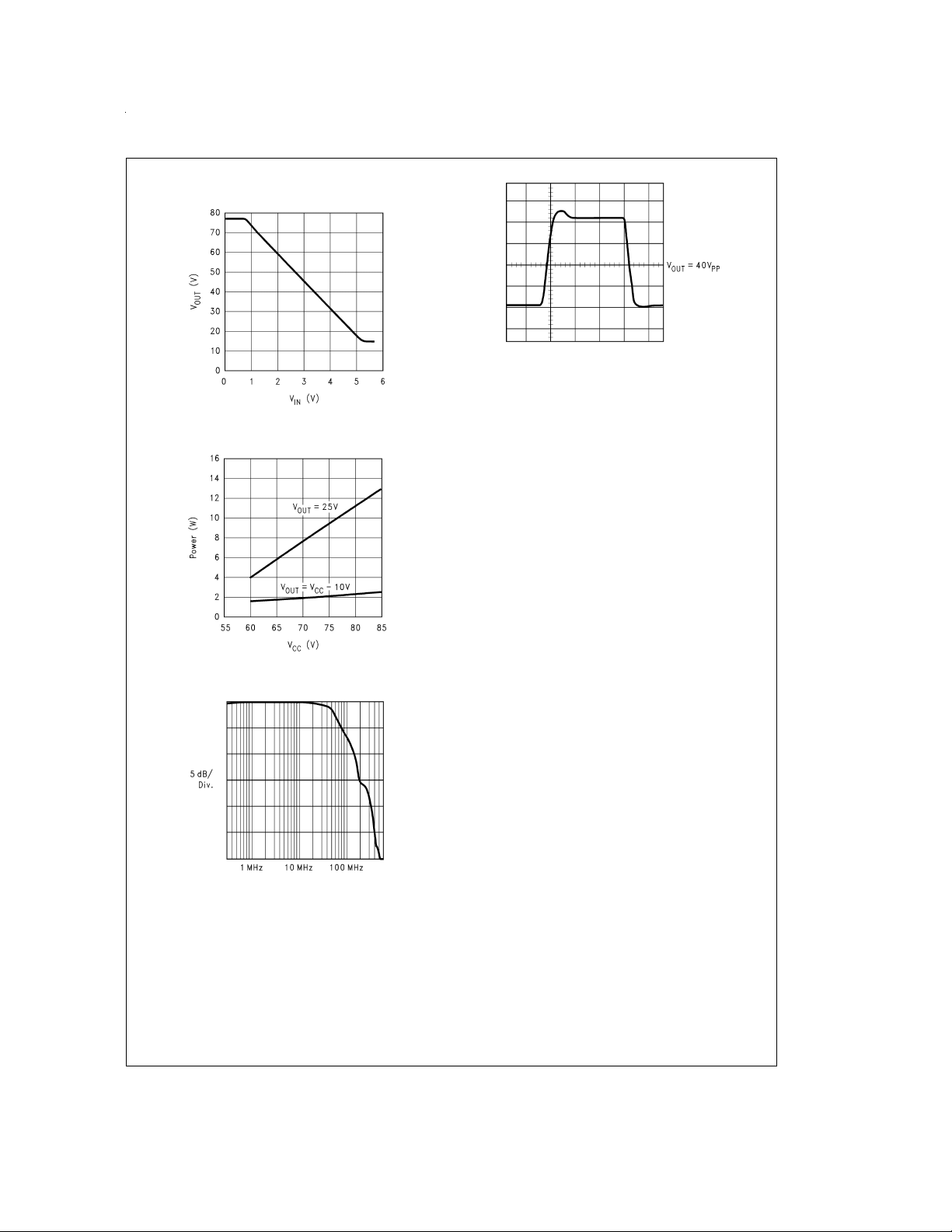

DS012682-7

FIGURE 6. Pulse Response

DS012682-4

FIGURE 3. V

FIGURE 4. Power Dissipation vs V

OUT

vs V

IN

DS012682-5

CC

DS012682-6

FIGURE 5. Large Signal Frequency Response

Theory of Operation

The LM2405 is a high voltage monolithic triple CRT driver

suitable for SVGA and XGA display applications. The

LM2405 features +80V operation and low power dissipation.

The part is housed in the industry standard 11-lead TO-220

molded plastic power package.

The circuit diagram of the LM2405 is shown in

Figure 1

.A

PNP emitter follower, Q5, provides input buffering. Q1 and

Q2 form a fixed gain cascode amplifier, with a gain of −14.

Emitter followers Q3 and Q4 isolate the high output impedance of the amplifier from the capacitance of the CRT cathode, and make the circuit relative insensitive to load capacitance. Q6 provides biasing to the output emitter follower

stage to reduce crossover distortion at low signal levels.

Figure 2

shows a typical test circuit for evaluation of the

LM2405. This circuit is designed to allow testing of the

LM2405 in a 50Ω environment, such as a pulse generator

and a scope, or a network analyzer. In this test circuit, two

low inductance resistors in series totaling 4.95 kΩ form a

100:1 wideband low capacitance probe when connected to a

50Ω cable and load. The input signal from the generator is

AC coupled to the base of Q5.

Application Hints

INTRODUCTION

National Semiconductor is committed to providing application information that assists our customers in obtaining the

best performance possible from our products. The following

information is provided in order to support this commitment.

The reader should be aware that the optimization of performance was done using a specific printed circuit board designed at National. Variations in performance can be realized

due to physical changes in the printed circuit board and the

application. Therefore, the designer should be aware that

component value changes may be required in order to optimize performance in a given application. The values shown

in this document can be used as a starting point for evaluation purposes. When working with high bandwidth circuits,

good layout practices are also critical to achieving maximum

performance.

POWER SUPPLY BYPASS

Since the LM2405 is a wide bandwidth amplifier, proper

power supply bypassing is critical for optimum performance.

Improper power supply bypassing can result in large overshoot, ringing and oscillation. A 0.01 µF capacitor should be

connected from the supply pin, V

, to ground, as close to

CC

www.national.com3

Loading...

Loading...