NSC LM1292N Datasheet

LM1292

Video PLL System for Continuous-Sync Monitors

LM1292 Video PLL System for Continuous-Sync Monitors

April 1999

General Description

The LM1292 is a very low jitter, integrated horizontal time

base solution specifically designed to operate in high performance, continuous-sync video monitors. It automatically

synchronizes to any H frequency from 22 kHz to 125 kHz

and provides the drive pulse tothehighpower deflection circuit.

Available sync processing includes a vertical sync separator

and a composite video sync stripper. An internal sync selection scheme gives highest priority to separate H and V sync,

then composite sync, and finally sync on video; no external

switching between sync sources is necessary. The LM1292

provides polarity-normalized H/HV and V sync outputs.

The LM1292 design uses an on-chip FVC

(Frequency-to-Voltage Converter) to set the center frequency of the VCO (Voltage-Controlled Oscillator). This

technique allows autosync operation over the entire frequency range using just one optimized set of external components.

The system includes a second phase detector which compensates for storage time variation in the horizontal output

transistor; the picture’s horizontal position is thus independent of temperature and component variance.

The LM1292 provides DC control pins for H Drive duty cycle

and flyback phase.

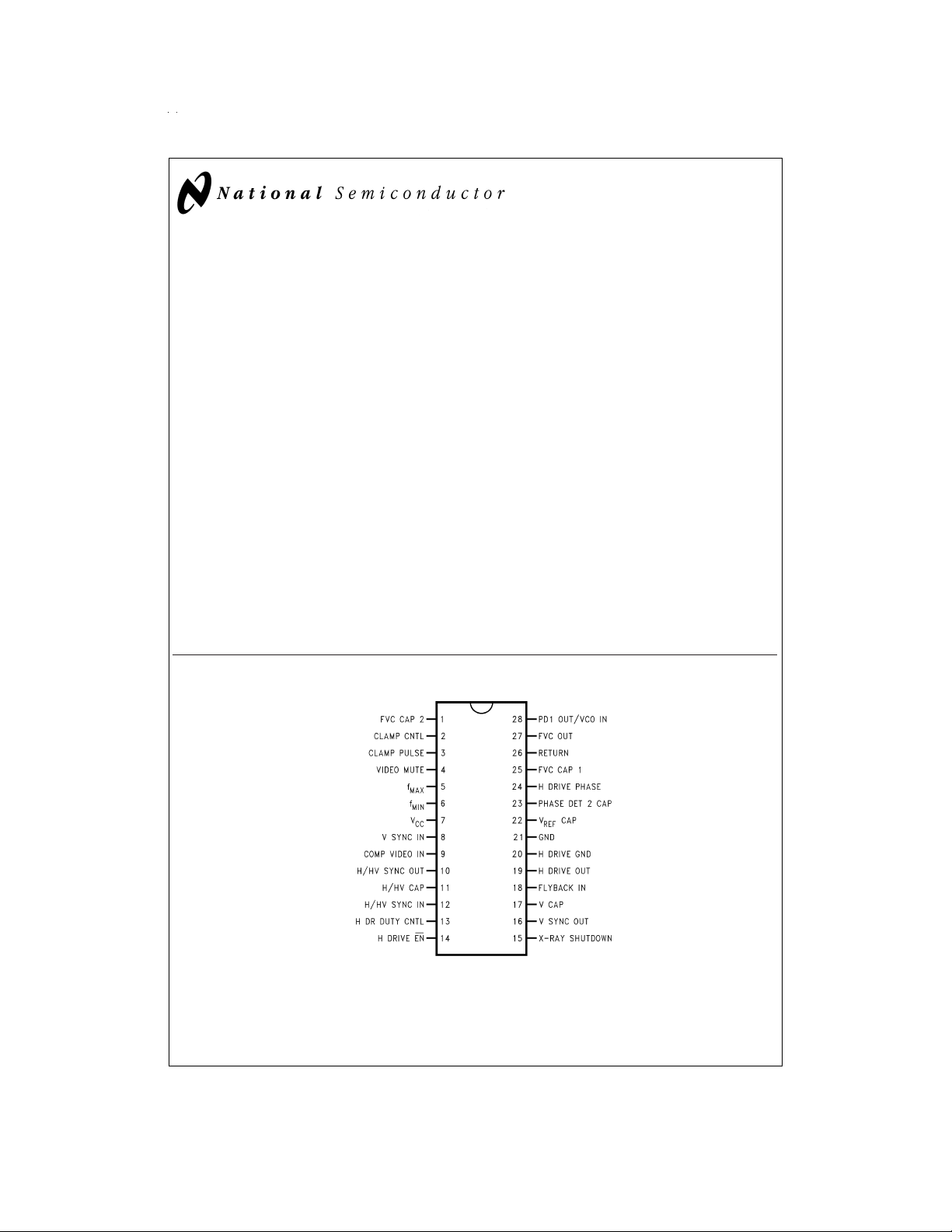

Connection Diagram

Features

n Wide continuous autosync range— 22 kHz–125 kHz

(1:5.7) with no component switching or external

adjustments

n No manufacturing trims required— internal VCO

capacitor trimmed on chip

n No costly high-precision components needed

n Very low phase jitter (below 800 ps at 125 kHz)

n DC controlled H phase and duty cycle

n Video mute pulse for blanking during H frequency

transitions

n Input sync prioritization

n Clamp pulse position and width control

n Continuous clamp pulse output, even with no sync input

n Resistor-programmable minimum and maximum VCO

frequency

n X-ray input disables H drive and mutes video until V

powered down

n H drive disabled for V

n Horizontal output transistor protected against accidental

turn-on during flyback

n Capacitor-programmable frequency ramping, d

protects H output transistor during scanning mode

changes

<

9.5V

CC

CC

f

/dt,

vco

DS012844-1

FIGURE 1. Order Number LM1292N

See NS Package Number N28B

© 1999 National Semiconductor Corporation DS012844 www.national.com

Absolute Maximum Ratings (Notes 1, 3)

If Military/Aerospace specified devices are required,

please contact the National Semiconductor Sales Office/

Distributors for availability and specifications.

Supply Voltage 14V

Input Voltage, V

Pin 14

Pin 24

Pins 5, 6

Pins 8, 28

Pins 2, 9, 12, 13, 15, 18

Power Dissipation (PD) 2.5W

(Above 25˚C, derate based on θ

DC

<

1.3V

and TJ)

JA

5V

<

V

7.2V

IN

8V

10V

V

CC

Thermal Resistance (θ

Junction Temperature (T

) 50˚C/W

JA

) 150˚C

J

ESD Susceptibility (Note 5) 2 kV

Storage Temperature −65˚C to +80˚C

Lead Temperature

(Soldering 10 sec.) 265˚C

Operating Ratings (Note 2)

Operating Temperature Range −20˚C to +80˚C

Supply Voltage 10.8V ≤ V

CC

≤ 13.2V

Electrical Characteristics See Test Circuit (

otherwise stated

Parameter Conditions

Supply Current

Minimum Composite Video

Input Amplitude (Pin 9)

Cap Coupled (0.01 µF), Sync Tip to

Black Level

Figure 2

); T

A

=

25˚C; V

=

12V; V

CC

=

0V; V

14

Typical

(Note 6)

30 41

0.14 V

=

15

Limit

(Note 7)

0V unless

Units

(max)

DC Clamp Level, Composite Video Input 2.0 V

Clamp Charging Current, Composite

Video Input

Minimum H/HV Sync Input Amplitude

(Pin 12)

Cap Coupled, 10%Duty Cycle (Note 8)

6mA

1.0 V

Minimum V Sync Input Amplitude (Pin 8) Cap Coupled, 1%Duty Cycle 1.0 V

High Level Output Voltage VOH(Pins 10,

16)

Low Level Output Voltage V

16)

(Pins 10,

OL

Video Mute Low Level Output Voltage

(Pin 4)

Mute Detection Voltage Threshold ∆V, | FVC Cap 1 - FVC Cap 2 | for Mute

=

I

−100 µA

OH

=

I

1.6 mA

OL

=

2mA

I

OL

Output Low

4.3 3.8 V (Min)

0.25 0.4 V (Max)

0.4 V (Max)

100 mV

Flyback Input Threshold (Pin 18) Positive Going Flyback Pulse 1.4 V

Under-Voltage Lockout (Pin 7) V

Frequency to Voltage Gain 22 kHz ≤ f

VCO Gain Constant f

PD1 Phase Detector Gain Constant f

Frequency to Voltage Linearity 22 kHz ≤ f

VCO Linearity 22 kHz ≤ f

Jitter f

H Drive Duty Cycle Control Gain V

H Drive Phase Control Gain V

PD1 Phase Detector Leakage Current

+ VCO Input Bias Current (Pin 28)

Below Threshold: H Drive Output

CC

Open (Unlatched)

≤ 125 kHz 0.047 V/kHz

H

=

100 kHz 1.34 x 10

VCO

=

100 kHz 130

VCO

=

60 kHz 78.1

VCO

=

f

22 kHz 28.6

f

f

f

VCO

H

H

H

H

=

=

=

=

13

24

≤ 125 kHz 1.0

H

≤ 125 kHz 1.0

VCO

30 kHz (Note 9)

60 kHz

100 kHz

125 kHz

=

0V–4V; 30%–70%Allowed 0.11 T

=

1.5V–7V (Note 10) 32 ˚/V

10.8 V

5

3.25

1.45

895

763

1µA

Rad/s/V

µA/Radf

ns p-p

ps p-p

mA

%

%

H

PP

PP

PP

/V

www.national.com 2

Electrical Characteristics See Test Circuit (

otherwise stated (Continued)

Figure 2

); T

A

=

25˚C; V

=

12V; V

CC

=

14

0V; V

15

=

0V unless

Parameter Conditions

H Drive Low Level Output Voltage (Pin

19)

H Drive EN Low Level Input Voltage (Pin

=

100 mA

I

OL

H Drive Output Active

Typical

(Note 6)

0.7 V

14)

H Drive EN High Level Input Voltage (Pin

H Drive Output Open (Unlatched)

14)

X-Ray Shutdown Threshold Voltage (Pin

15)

H/HV Sync Out Propagation Delay

Change

Clamp Pulse Width (Back Porch)R

Clamp Pulse Delay (Back Porch) Trailing Edge H/HV Sync

Note 1: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur.

Note 2: Operating Ratings indicate conditions for which the device is functional, but do not guarantee specific performance limits. For guaranteed specifications and

test conditions, see the Electrical Characteristics. The guaranteed specifications apply only for the test conditions listed. Some performance characteristics may degrade when the device is not operated under the listed test conditions.

Note 3: All voltages are measured with respect to GND, unless otherwise specified.

Note 4: The maximum power dissipation must be derated at elevated temperatures and is dictated by T

allowable power dissipation at any elevated temperature is P

this device, T

Note 5: Human Body model, 100 pF capacitor discharged through a 1.5 kΩ resistor.

Note 6: Typical specifications are at T

Note 7: Tested limits are guaranteed to National’s AOQL (Average Outgoing Quality Level).

Note 8: The typical duty cycle range allowed for the H sync tip is from 5%–26%.

Note 9: The standard deviation, σ, of the flyback pulse period is measured with HP 53310A Modulation Domain Analyzer. Peak-to-peak jitter of the flyback pulse is

defined by 6σ.

Note 10: Phase Limits:

=

150˚C. The typical thermal resistance (θ

JMAX

=

A

25˚C and represent most likely parametric norm.

V

Above Threshold, H Drive

15

Output Open (Latched)

H/HV In vs Comp Video In

(Back Porch)R

(Sync Tip)R

SET

SET

SET

=

=

15 kΩ;V

=

15 kΩ;V

15 kΩ;V

=

0V 0.4 µs

SET

=

1.5V 1.4 µs

SET

=

4V 0.6 µs

SET

In to Leading Edge Clamp Pulse

(Sync Tip) Leading Edge H/HV Sync In

to Leading Edge Clamp Pulse

, θJAand the ambient temperature, TA. The maximum

=

(T

D

) of these parts when board mounted follow: LM1292N 50˚C/W.

JA

,

)/θJAor the number given in the Absolute Maximum Ratings, whichever is lower. For

JMAX−TA

JMAX

1.8

32 ns

0.1 µs

0.025 T

Limit

(Note 7)

Units

0.8 V (Max)

2.0 V (Min)

1.7

1.9

H

V (Min)

V (Max)

s

expressed as a fraction of the horizontal period T

positive phase value represents a phase lead of the FBP peak with reference to the leading edge of H sync.

, where T

H

is the horizontal output transistor turn-off delay from the rising edge of H Drive to the FBP peak. A

DFB

www.national.com3

Loading...

Loading...