© 2000 National Semiconductor Corporation www.national.com

Geode™ CS5530 I/O Companion Multi-Function South Bridge

April 2000

Geode™ CS5530 I/O Companion

Multi-Function South Bridge

General Description

The CS5530 I/O companion is designed to work in conjunction with the GXLV and GXm series processors; all

members of the National Semiconductor

®

Geode™ family

of products. Together the Geode processor and CS5530

provide a system-level solution well suited for the high

performance needs of a host of devices such as digital

set-top boxes and thin c lient devices. Due to the low

power consumption of a GXLV processor, this solution

satisfies the needs of battery powered devices such as

National’s WebPAD™ system, a Geode GXLV processor/CS5530 based design. Also, thermal design is eased

allowing forfanless system design.

The CS5530 I/O companion is a PCI-to-ISA bridge (South

Bridge), ACPI-compliant chipset that provides AT/ISA

style functionality. To those familiar with PC architecture

this enables a quicker understanding of the CS5530’s

architecture. The device contains state-of-the-art power

management that enables systems, especially battery

powered systems, to significantly reduce power consumption.

Audiois supported throughPCIbusmaster engines which

connect to an AC97 compatible codec such as the

National Semiconductor LM4548. If industry standard

audio is required, a combination of hardwareandsoftware

called Virtual System Architecture

®

(VSA™) technology is

provided.

The GXLV processor’sgraphics/video output is connected

to the CS5530. The CS5530 graphics/video support

includes a PLL that generates the DOTclockfor the GXLV

processor (where the graphics controlleris located), video

acceleration hardware, gamma RAM plus three DACs for

RGB output to CRT, and digital RGB that can be directly

connected to TFT panels or NTSC/PAL encoders. The

digital RGB output can also be connected to the National

Semiconductor CS9210 Graphics Companion (a DSTN

Controller) for DSTN panel support. The CS9210 is also a

member of the Geode product family.

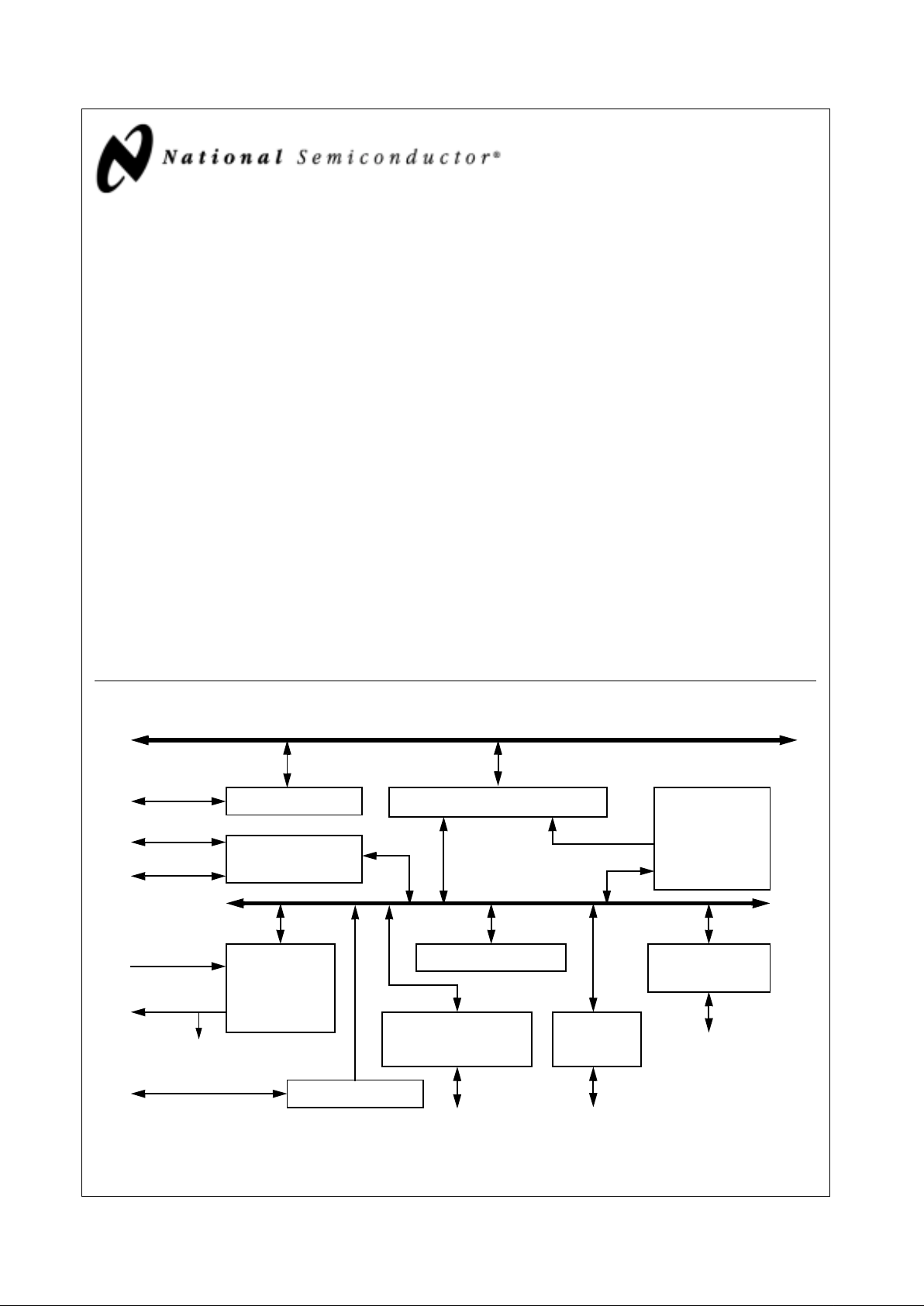

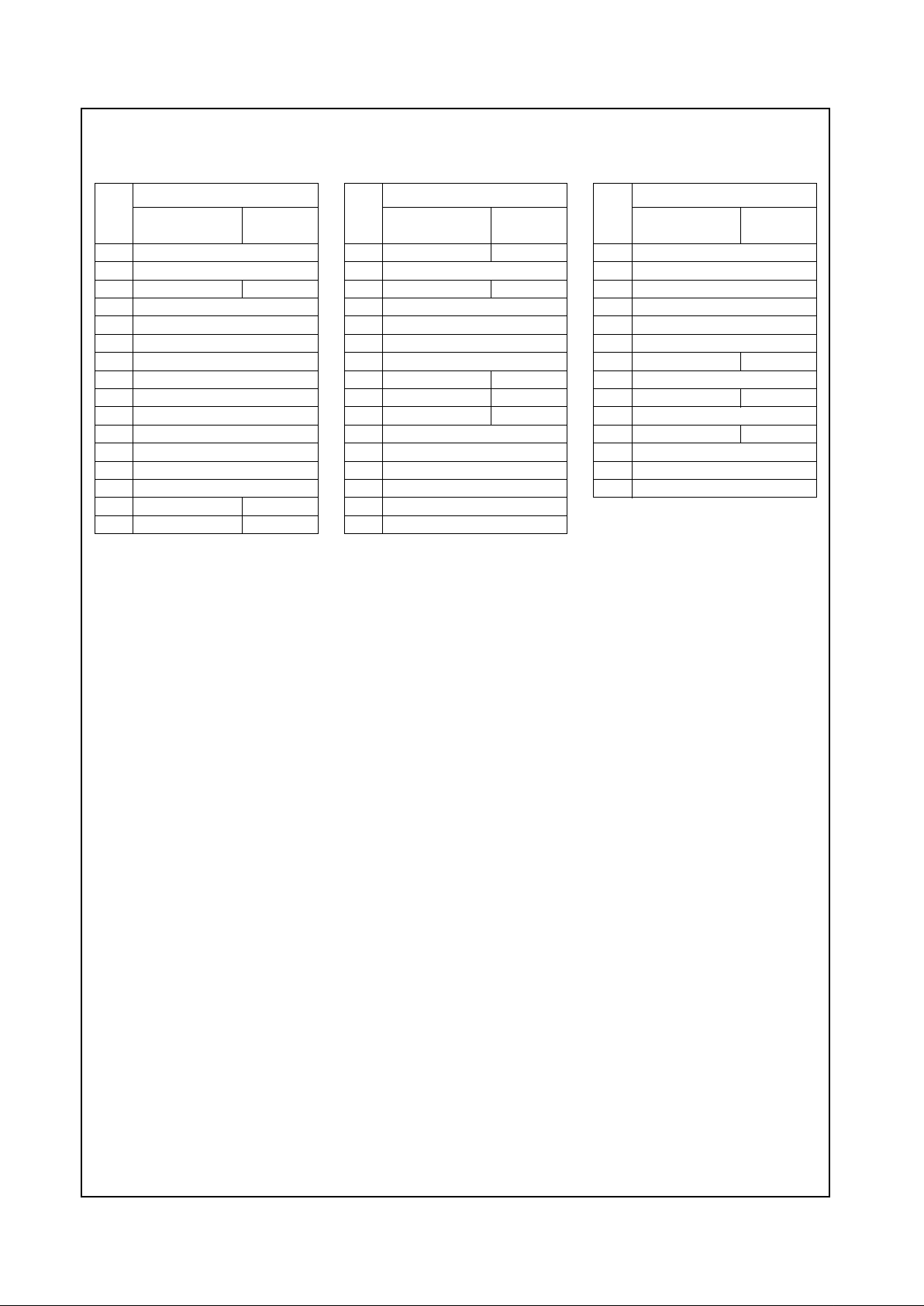

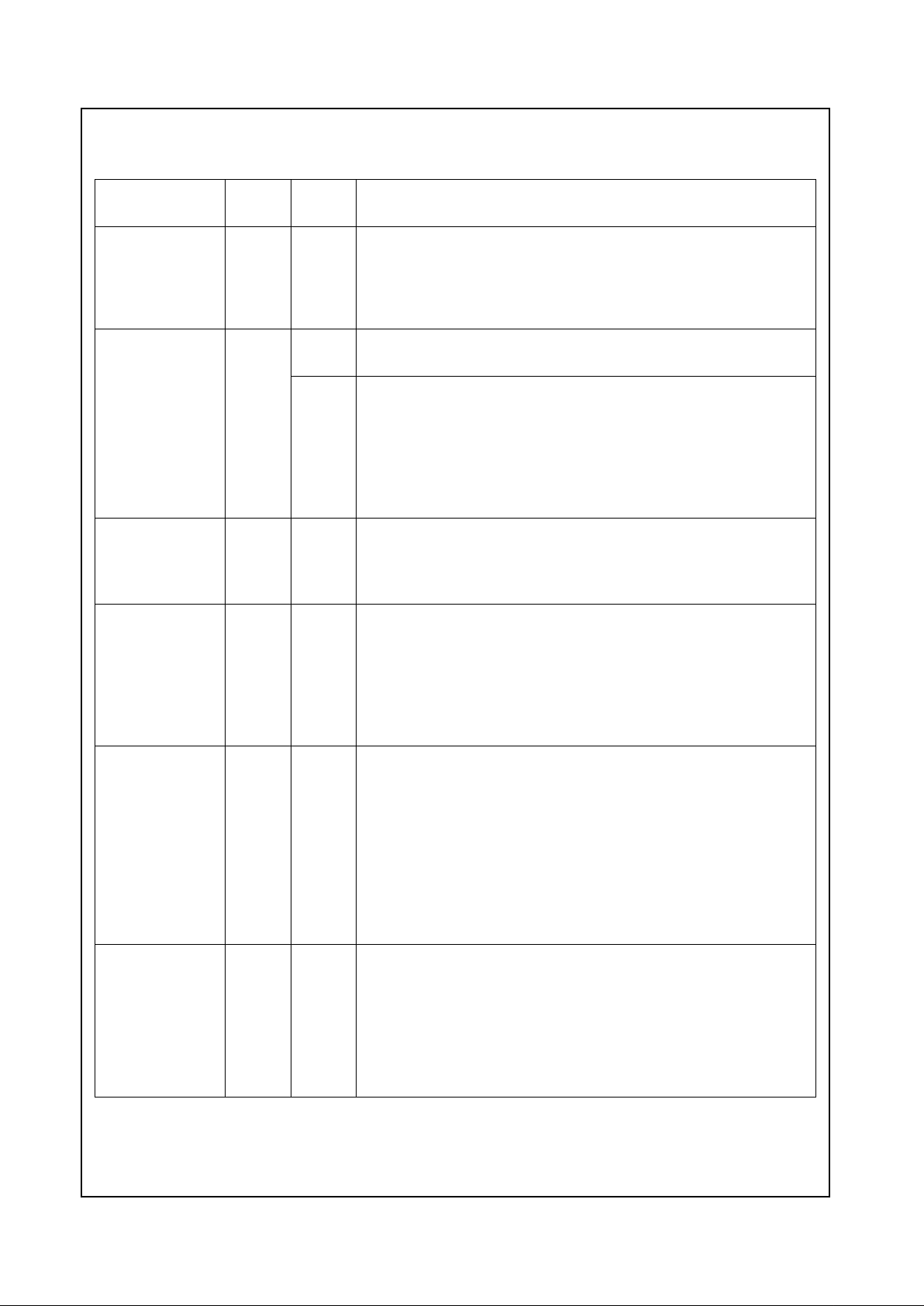

Geode™ CS5530 Internal Block Diagram

X-Bus

ISA Bus

PCI Bus

USB

PCI to X-Bus / X-Bus to PCI Bridge

PCI to USB Macro

Active Decode

Address Mapper

Audio/Codec/MPU

Interface

Pwr Mgmt, Traps,

Events, and Timers

IDE

Interface

Display Interface

MPEG, DOT Clock

CSC and SCL

RGB/FP Interface

AT Compatibility Logic

ISA Bus Interface

AT Ports, ISA Megacells

Display

PCI Configuration

Registers

Graphics

and Video

from CPU

X-Bus Arbiter

CS5530 Support

GPIOs

IDE

AC97 Codec

Ultra DMA/33

(e.g., LM4548)

Joystick / Game Port

Joystick

PC97317 SIO

GPCS

Geode™ CS9210

Graphics Companion

National Semiconductor and Virtual System Architecture are registered trademarks of National Semiconductor Cor poration.

Geode, VSA, and WebPAD are trademarks of National Semiconductor Corporation.

For a complete listing of National Semiconductor trademarks, please visit www.national.com/trademarks.

www.national.com 2 Revision 4.1

Geode™ CS5530

Two bus mastering IDE controllers are included for support of up to four ATA-compliant devices. A two-port Universal Serial Bus (USB) provides high speed, Plug & Play

expansion for a variety of consumer peripheral devices

such as a keyboard, mouse, printer, and digital cameras.

If additional functions are required, such as real-time

clock, floppy disk, PS2 keyboard, and PS2 mouse, a

SuperI/O (e.g., National PC97317) can be easily connected to the CS5530.

Features

General Features

Designed for use with the GXLV and GXm Geode

series processors

352-Terminal TapeBall Gr id Array(TBGA) package

3.3V or 5.0V PCI bus compatible

5.0V tolerant I/O interfaces

3.3V core

PCI-to-ISA Bridge

PCI 2.1 compliant

Supports PCI initiator-to-ISA and ISA master-to-PCI

cycle translations

PCI master for audio I/O and IDE controllers

Subtractive agent for unclaimed transactions

PCI-to-ISA interrupt mapper/translator

AT Compatibility

Two 8259A-equivalent interrupt controllers

8254-equivalent timer

Two 8237-equivalent DMA controllers

Boot ROM and keyboard chip select

ExtendedROMto16MB

Bus Mastering IDE Controllers

Two controllers with support for up to four IDE devices

Independent timing for master and slave devices for

both channels

PCI bus master burst reads and writes

Ultra DMA/33 (ATA-4)support

Multiword DMA support

Programmed I/O (PIO) Modes 0-4 support

Power Management

Intelligent system controller supports multiple power

management standards:

— Full ACPI and Legacy (APM) support

— Directly manages all GXLV and GXmprocessor

power states (including automatic Suspend modulation for optimal performance/thermal balancing)

I/O traps and idle timersfor peripheral power

management

Up to eight GPIOs for system control:

— All eight are configurable as external wakeupevents

Dedicated inputs for keyboard and mousewakeup

events

XpressAUDIO

Provides "back-end" hardware support via six buffered

PCI bus masters

AC97 codec interface:

— Specification Revision 1.3, 2.0, and 2.1 compliant

interface.Note that the codec (e.g., LM4548) must

have SRC (sample rate conversion) suppor t

Display Subsystem Extensions

Complements the GXLV and GXm processor’s

graphics and video capabilities:

— Three independent line buffers for accelerating

video data streams

— Handles asynchronous video and graphics data

streams concurrently from the processor

— YUV to RGB conversion hardware

— Arbitrary X & Y interpolative scaling

— Color keying for graphics/video overlay

VDACs/Displayinterface:

— Three integrated D ACs

— Gamma RAM:

– Provides gamma correction for graphics data

streams

– Provides brightness/contrast correction for video

data streams

— Integrated DOT clock generator

— Digital RGB interface drivesTFT panels or standard

NTSC/PAL encoders

Universal Serial Bus

Two independent USB interfaces:

— Open Host Controller Interface (OpenHCI)

specificationcompliant

— Second generation proven core design

Revision 4.1 3 www.national.com

Table of Contents

Geode™ CS5530

1.0 ArchitectureOverview..............................................6

1.1 PCIBUSINTERFACE ......................................................6

1.2 ISABUSINTERFACE ......................................................7

1.3 ATCOMPATIBILITYLOGIC..................................................7

1.3.1 DMAController.....................................................7

1.3.2 ProgrammableIntervalTimer..........................................7

1.3.3 ProgrammableInterruptController......................................7

1.4 IDECONTROLLERS .......................................................7

1.5 POWERMANAGEMENT ....................................................8

1.5.1 GPIOInterface .....................................................8

1.6 XPRESSAUDIO ...........................................................8

1.6.1 AC97CodecInterface ...............................................8

1.6.2 VSATechnologySupportHardware.....................................8

1.7 DISPLAYSUBSYSTEMEXTENSIONS.........................................9

1.8 CLOCKGENERATION ....................................................10

1.9 UNIVERSALSERIALBUS..................................................10

1.10 PROCESSORSUPPORT ..................................................11

2.0 SignalDefinitions.................................................12

2.1 PINASSIGNMENTS ......................................................13

2.2 SIGNALDESCRIPTIONS ..................................................22

2.2.1 ResetInterface....................................................22

2.2.2 ClockInterface ....................................................22

2.2.3 CPUInterface.....................................................23

2.2.4 PCIInterface .....................................................24

2.2.5 ISABusInterface ..................................................27

2.2.6 ROMInterface ....................................................30

2.2.7 IDEInterface .....................................................31

2.2.8 USBInterface.....................................................32

2.2.9 GamePortandGeneralPurposeI/OInterface ...........................32

2.2.10 AudioInterface ....................................................33

2.2.11 DisplayInterface...................................................34

2.2.12 DCLKPLL .......................................................38

2.2.13 Power,Ground,andReserved........................................39

2.2.14 InternalTestandMeasurement .......................................39

3.0 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

3.1 PROCESSORINTERFACE .................................................41

3.1.1 DisplaySubsystemConnections ......................................42

3.1.2 PSERIALPinInterface..............................................44

3.1.2.1 VideoRetraceInterrupt .............................................44

3.2 PCIBUSINTERFACE .....................................................45

3.2.1 PCIInitiator ......................................................45

3.2.2 PCITarget .......................................................46

3.2.3 SpecialBusCycles–Shutdown/Halt ....................................47

3.2.4 PCIBusParity ....................................................47

3.2.5 PCIInterruptRoutingSupport ........................................48

3.2.6 DelayedTransactions ...............................................48

www.national.com 4 Revision 4.1

Table of Contents (Continued)

Geode™ CS5530

3.3 RESETSANDCLOCKS....................................................49

3.3.1 Resets ..........................................................49

3.3.2 ISAClock ........................................................49

3.3.3 DOTClock .......................................................50

3.3.3.1 DCLKProgramming................................................51

3.4 POWERMANAGEMENT ...................................................54

3.4.1 APMSupport .....................................................54

3.4.2 CPUPowerManagement............................................55

3.4.2.1 SuspendModulation ...............................................55

3.4.2.2 3VoltSuspend....................................................58

3.4.2.3 Save-To-Disk .....................................................59

3.4.3 PeripheralPowerManagement .......................................60

3.4.3.1 DeviceIdleTimersandTraps ........................................60

3.4.3.2 GeneralPurposeTimers ............................................70

3.4.3.3 ACPITimerRegister ...............................................72

3.4.3.4 GeneralPurposeI/OPins ...........................................73

3.4.3.5 PowerManagementSMIStatusReportingRegisters......................75

3.4.3.6 Device Power Management Register Programming Summary . . . . . . . . . . . . . . . 82

3.5 PC/ATCOMPATIBILITYLOGIC..............................................84

3.5.1 ISASubtractiveDecode .............................................84

3.5.2 ISABusInterface ..................................................85

3.5.2.1 DelayedPCITransactions ...........................................86

3.5.2.2 LimitedISAandISAMasterModes....................................87

3.5.2.3 ISABusDataSteering..............................................89

3.5.2.4 I/ORecoveryDelays ...............................................89

3.5.2.5 ISADMA ........................................................90

3.5.3 ROMInterface ....................................................91

3.5.4 Megacells ........................................................91

3.5.4.1 DirectMemoryAccess(DMA)........................................92

3.5.4.2 ProgrammableIntervalTimer ........................................94

3.5.4.3 ProgrammableInterruptController ....................................95

3.5.4.4 PCICompatibleInterrupts ...........................................98

3.5.5 I/OPorts092hand061hSystemControl...............................100

3.5.5.1 I/OPort092hSystemControl .......................................101

3.5.5.2 I/OPort061hSystemControl .......................................101

3.5.5.3 SMIGenerationforNMI............................................101

3.5.6 KeyboardInterfaceFunction ........................................102

3.5.6.1 FastKeyboardGateAddress20andCPUReset ........................103

3.5.7 ExternalReal-TimeClockInterface ...................................104

3.6 IDECONTROLLER ......................................................105

3.6.1 IDEInterfaceSignals ..............................................105

3.6.2 IDEConfigurationRegisters.........................................106

3.6.2.1 PIOMode ......................................................106

3.6.2.2 BusMasterMode ................................................108

3.6.2.3 UltraDMA/33Mode ...............................................111

3.7 XPRESSAUDIO .........................................................113

3.7.1 SubsystemDataTransportHardware .................................113

3.7.1.1 AudioBusMasters................................................113

3.7.1.2 PhysicalRegionDescriptorTableAddress .............................116

3.7.1.3 PhysicalRegionDescriptorFormat ...................................116

3.7.1.4 ProgrammingModel ..............................................117

3.7.1.5 AC97CodecInterface .............................................118

3.7.2 VSATechnologySupportHardware...................................120

3.7.2.1 VSATechnology .................................................120

3.7.2.2 AudioSMIRelatedRegisters........................................120

3.7.2.3 IRQConfigurationRegisters ........................................126

Revision 4.1 5 www.national.com

Table of Contents (Continued)

Geode™ CS5530

3.8 DISPLAYSUBSYSTEMEXTENSIONS.......................................128

3.8.1 VideoInterfaceConfigurationRegisters................................128

3.8.2 VideoAccelerator.................................................129

3.8.2.1 LineBuffers .....................................................129

3.8.2.2 VideoPortProtocol ...............................................129

3.8.2.3 VideoFormat....................................................130

3.8.2.4 XandYScaler/Filter .............................................131

3.8.2.5 Color-Space-Converter ............................................131

3.8.3 VideoOverlay....................................................132

3.8.4 GammaRAM ....................................................133

3.8.5 DisplayInterface..................................................134

3.8.5.1 VideoDACs .....................................................134

3.8.5.2 VESA DDC2B / DPMS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 134

3.8.5.3 FlatPanelSupport................................................134

3.9 UNIVERSALSERIALBUSSUPPORT .......................................135

3.9.1 USBPCIController ...............................................135

3.9.2 USBHostController...............................................136

3.9.3 USB Power Management ...........................................136

4.0 RegisterDescriptions ............................................137

4.1 PCICONFIGURATIONSPACEANDACCESSMETHODS .......................138

4.2 REGISTERSUMMARY ...................................................139

4.3 CHIPSETREGISTERSPACE ..............................................149

4.3.1 BridgeConfigurationRegisters-Function0 ............................149

4.3.2 SMIStatusandACPITimerRegisters-Function1.......................179

4.3.3 IDEControllerRegisters-Function2 .................................184

4.3.4 XpressAUDIORegisters-Function3..................................188

4.3.5 VideoControllerRegisters-Function4 ................................199

4.4 USBCONTROLLERREGISTERS-PCIUSB ..................................206

4.5 ISALEGACYI/OREGISTERSPACE ........................................208

4.6 V-ACPII/OREGISTERSPACE .............................................217

5.0 ElectricalSpecifications ..........................................224

5.1 TESTMODES...........................................................224

5.1.1 NandTreeMode..................................................225

5.2 ELECTRICALCONNECTIONS .............................................227

5.2.1 Pull-UpResistors .................................................227

5.2.2 UnusedInputPins ................................................227

5.2.3 NC-DesignatedPins...............................................227

5.2.4 Power/GroundConnectionsandDecoupling ............................227

5.3 ABSOLUTEMAXIMUMRATINGS...........................................227

5.4 RECOMMENDEDOPERATINGCONDITIONS.................................227

5.5 DCCHARACTERISTICS .................................................228

5.6 ACCHARACTERISTICS ..................................................230

5.7 VIDEOCHARACTERISTICS ...............................................234

6.0 MechanicalSpecifications ........................................238

Appendix A Support Documentation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 240

A.1 REVISIONHISTORY .....................................................240

www.national.com 6 Revision 4.1

Geode™ CS5530

1.0 Architecture Overview

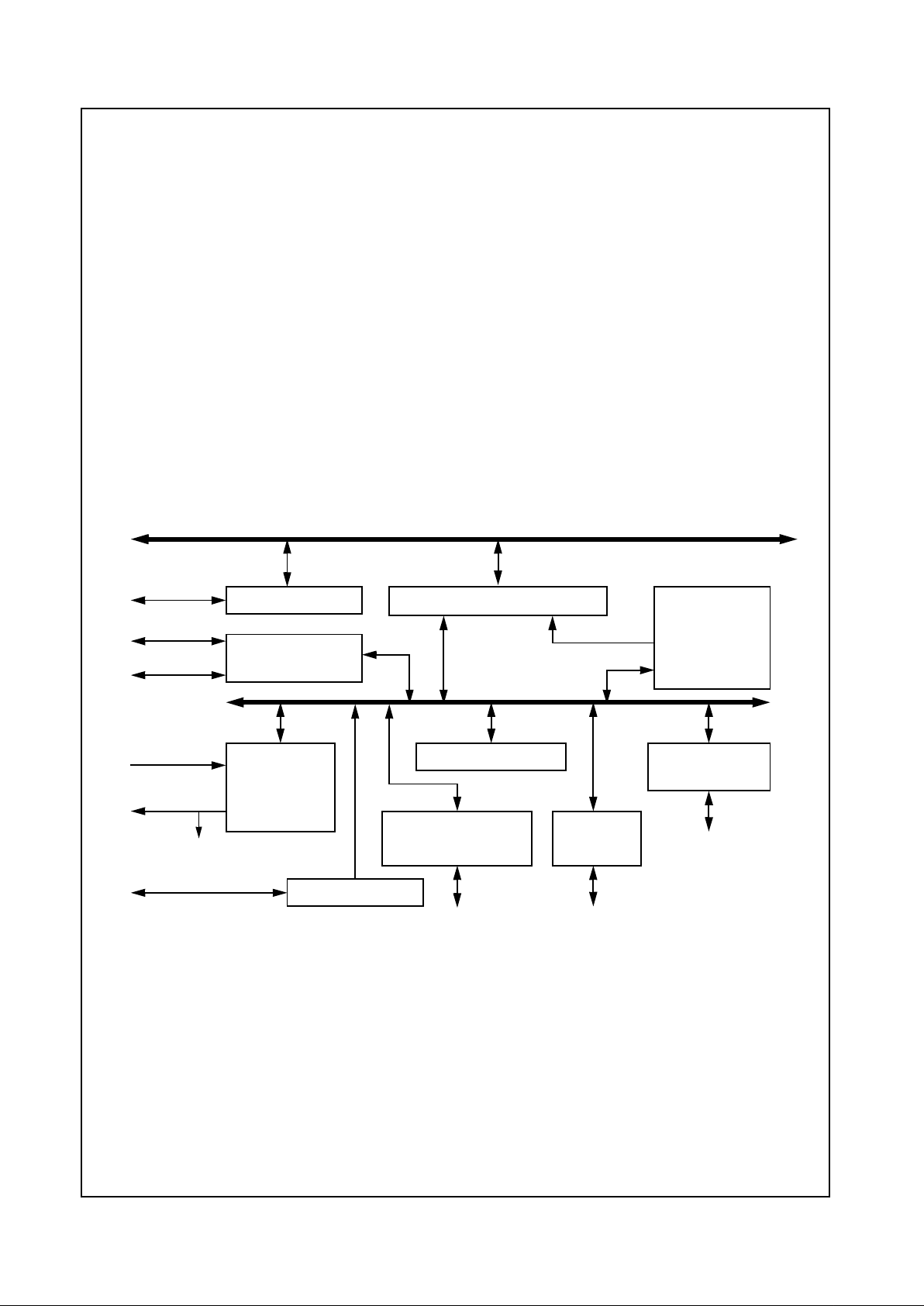

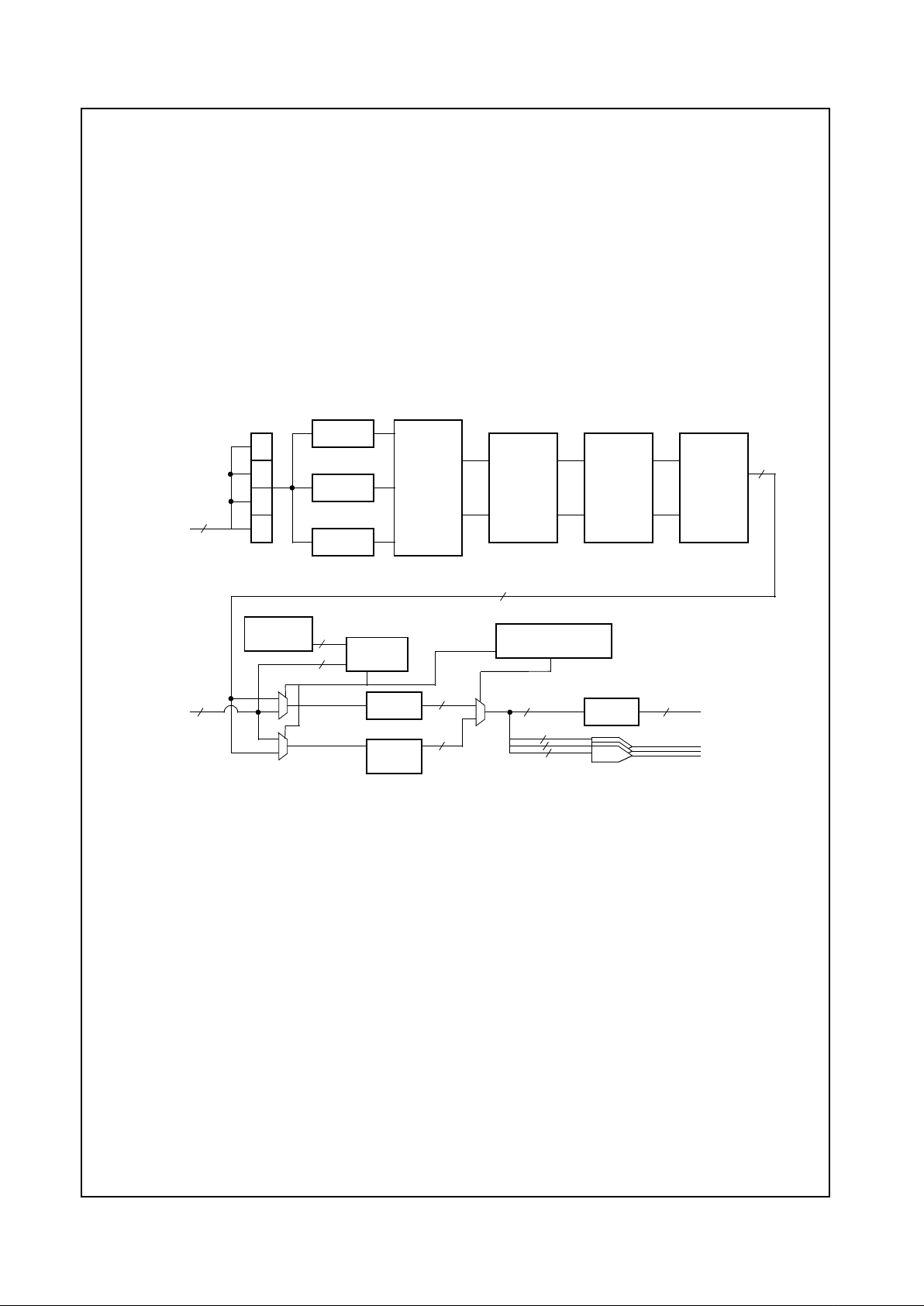

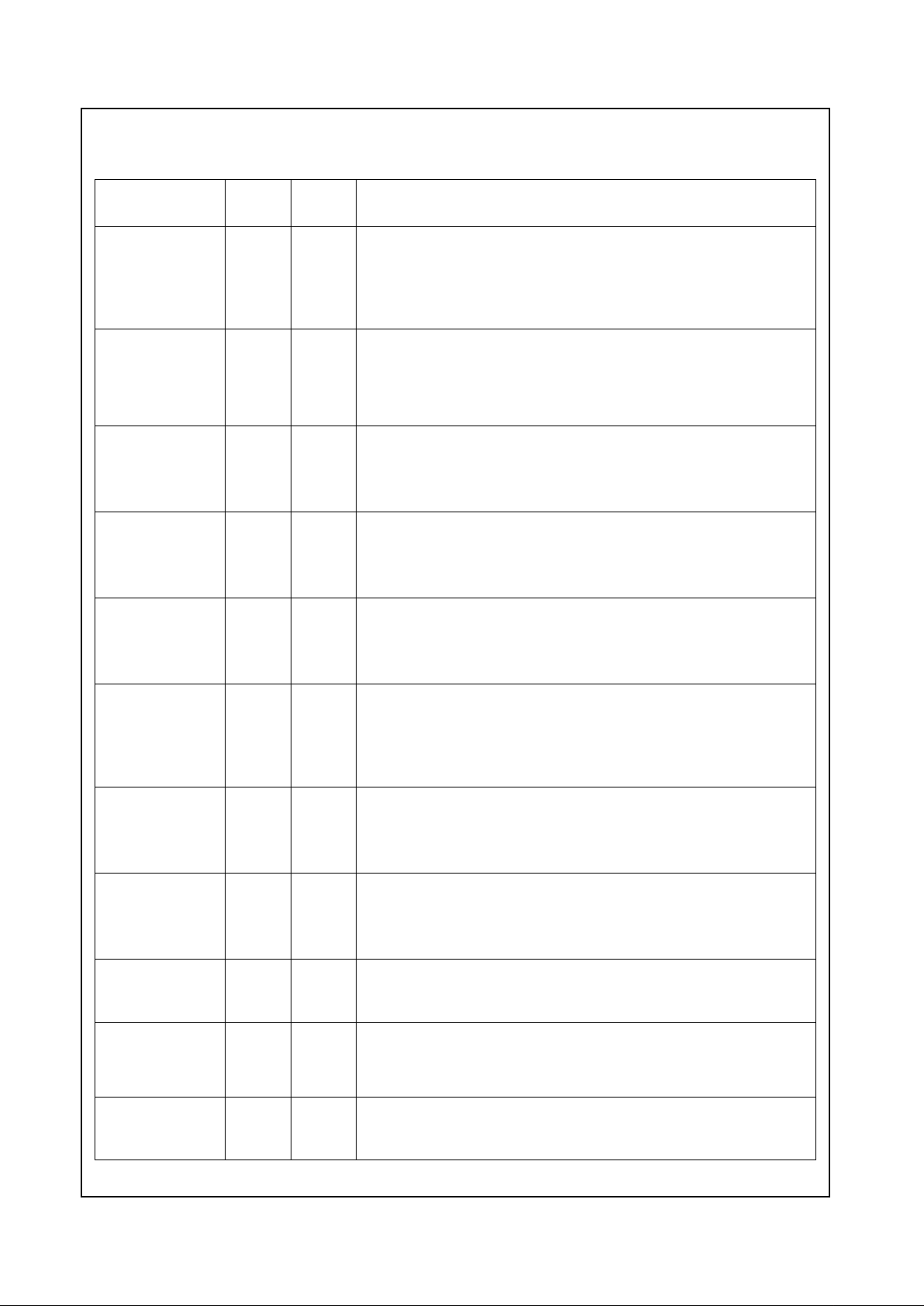

The Geode CS5530 can be described as providing the

functional blocks shown in Figure 1-1.

• PCI bus master/slave interface

• ISA bus interface

• AT compatibility logic

• IDE controllers

• Power management

-GPIOinterfaces

- Traps, Events, Timers

• Joystick/Game Port interface

• Virtual audio support hardware

• Videodisplay, whichincludes MPEG accelerator,

RAMDAC, and videoports

•USBcontrollers

For CPU interface connection refer to Figure 1-5 on page

11.

1.1 PCI BUS INTERFACE

The CS5530 provides a PCI bus interface that is both a

slave for PCI cycles initiated by the CPU or other PCI

master devices, and a non-preemptable master for DMA

transfercycles. The chip also isa standard PCI master for

the IDE controllers and audio I/O logic. The CS5530 supports positive decode for configurable memory and I/O

regions and implements a subtractive decode option for

unclaimed PCI accesses. The CS5530 also generates

address and data parity and performs parity checking.

The CS5530 does not include the PCI bus arbiter, it is

locatedintheprocessor.

Configuration registers are accessed through the PCI

interface using the PCI Bus Type 1 configuration mechanism as described in the PCI 2.1Specification.

Figure 1-1. Internal Block Diagram

X-Bus

ISA B us

PCI Bus

USB

PCI to X-Bus / X-Bus to PCI Bridge

PCI to USB Macro

Active Decode

Address Mapper

Audio/Codec/MPU

Interface

Pwr Mgmt, Traps,

Events, and Timers

IDE

Interface

Display Interface

MPEG, DOT Clock

CSC and SCL

RGB/FP Interface

AT Compatibility Logic

ISA Bus Interface

AT Ports, ISA Megacells

Display

PCI Configuration

Registers

Graphics

and Video

from CPU

X-Bus Arbiter

CS5530 Support

GPIOs

IDE

AC97 Codec

Ultra DMA/33

(e.g., LM4548)

Joystick / Game Port

Joystick

PC97317 SIO

GPCS

Geode™ CS9210

Graphics Companion

Revision 4.1 7 www.national.com

Architecture Overview (Continued)

Geode™ CS5530

1.2 ISA BUS INTERFACE

The CS5530 provides an ISA bus interface for unclaimed

memory and I/O cycles on PCI. The CS5530 is the default

subtractive decoding agent and forwards all unclaimed

memory and I/O cycles to the ISA interface; however, the

CS5530 may be configured to ignore either I/O, memory

or all unclaimed cycles (subtractive decode disabled).

The CS5530 supports two modes on the ISA interface.

The default mode, Limited ISA Mode, supports the full

memory and I/O address range without ISA mastering.

The address and data buses are multiplexed together,

requiring an external latch to latch the lower 16 bits of

address of the ISA cycle. The signal SA_LATCH is generated when the data on the SA/SD bus is a valid address.

Additionally, the upper four address bits, SA[23:20] are

multiplexed on GPIO[7:4].

The second mode, ISA Master Mode, supports ISA bus

masters and requires no external circuitry. When the

CS5530 is placed in ISA Master Mode, a large number of

pins are redefined. In this mode of operation the CS5530

cannot support TFT flat panels or TV controllers, since

most of the signals used to support these functions have

been redefined. This mode is required if ISA slots or ISA

masters are used. ISA master cycles are only passed to

the PCI bus i f they access memory. I/O accesses are left

to complete on the ISAbus.

For further information regarding mode selection and

operational details refer to Section 3.5.2.2 “Limited ISA

and ISA Master Modes” on page 87.

1.3 AT COMPATIBILITY LOGIC

The CS5530 integrates:

• Two 8237-equivalent DMA c ontrollers withfull 32-bit

addressing

• Two 8259-equivalent interrupt controllers providing 13

individually programmable external interrupts

• An 8254-equivalent timer for refresh, timer, and

speaker logic

• NMI control and generation for PCI system errors and

all parity errors

• Support for standard AT keyboard controllers

• Positive decode for the AT I/O register space

• Reset control

1.3.1 DMA Controller

The CS5530 supports the industry standard DMA architecture using two 8237-compatible DMA controllers in

cascaded configuration. CS5530-supported DMA functions include:

• Standard seven-channel DMA support

• 32-bit address range support via high page registers

• IOCHRDY extended cycles for compatible timing

transfers

• ISA bus master device support using cascade mode

1.3.2 Programmable Interval Timer

The CS5530 contains an 8254-equivalent programmable

interval timer. This device has three timers, each with an

input frequency of 1.193 MHz.

1.3.3 Programmable Interrupt Controller

The CS5530 contains two 8259-equivalent programmable

interrupt controllers, with eight interrupt request lines

each, for a total of 16 interrupts. The two controllers are

cascaded internally, and two of the interrupt request

inputs are connected to the internal circuitry. This allows a

total of 13 externally available interrupt requests.

Each CS5530 IRQ signal can be individually selected as

edge- or level-sensitive. The PCI interrupt signals are

routed internally to the PIC IRQs.

1.4 IDE CONTROLLERS

The CS5530 integrates two PCI bus mastering, ATA-4

compatible IDE controllers. These controllers support

UltraDMA/33(enabledinMicrosoftWindows95andWindows NT by using a driver provided by National Semiconductor), Multiword DMA and Programmed I/O (PIO)

modes. Two devices are supported on each controller.

The data-transfer speed for each device on each controller can be independently programmed. This allows highspeed IDE peripherals to coexist on the same channel as

lower speed devices. Faster devices must be ATA-4 compatible.

www.national.com 8 Revision 4.1

Architecture Overview (Continued)

Geode™ CS5530

1.5 POWER MANAGEMENT

The CS5530 integrates advanced power management

featuresincluding:

• Idle timers for common system peripherals

• Addresstrap registers for programmable address

ranges for I/O or memory accesses

• Up to eight programmable GPIOs

• Clock throttling with automatic speedup for the CPU

clock

• SoftwareCPU stop clock

• Zero Volt Suspend/Resume with peripheral shadow

registers

• Dedicated serial bus to/from the GXLV processor

providing CPU power management status

TheCS5530isanACPI(AdvancedControlandPower

Interface)compliant chipset. An ACPI compliant system is

one whose underlying BIOS, device drivers, chipset and

peripherals conform to revision 1.0 or newer of the ACPI

specification. The “Fixed Feature” and “General Purpose”

registers are virtual. They are emulated by the SMI handling code rather than existing in physical hardware. To

the ACPI compliant operating system, the SMI-base virtualization is transparent; however, to eliminate unnecessary latencies, the ACPI timer exists in physical hardware.

The CS5530 V-ACPI (Virtual ACPI) solution provides the

following support:

• CPU States — C1, C2

• Sleep States — S1, S2, S4, S4BIOS, S5

• EmbeddedController (Optional) — SCI and SWI event

inputs.

• GeneralPurpose Events

— Fully programmable GPE0

Event Block registers.

1.5.1 GPIO Interface

Eight GPIO pins are provided for general usage in the

system. GPIO[3:0] are dedicated pins and can be configured as inputs or outputs. GPIO[7:4] can be configured as

the upper addresses of the ISA bus, SA[23:20]. All GPIOs

can also be configured to generate an SMI on input edge

transitions.

1.6 XPRESSAUDIO

XpressAUDIO i n the CS5530 offers a combined hardware/software support solution to meet industry standard

audio requirements. XpressAUDIO uses VSA technology

along with additional hardware features to provide the

necessary support for industry standard 16-bit stereo synthesis and OPL3 emulation.

The hardware portion of the XpressAUDIO subsystem

can broadly be divided into two categories. Hardware for:

• Transporting streaming audio data to/fromthe system

memoryandanAC97codec.

• VSA technology suppor t.

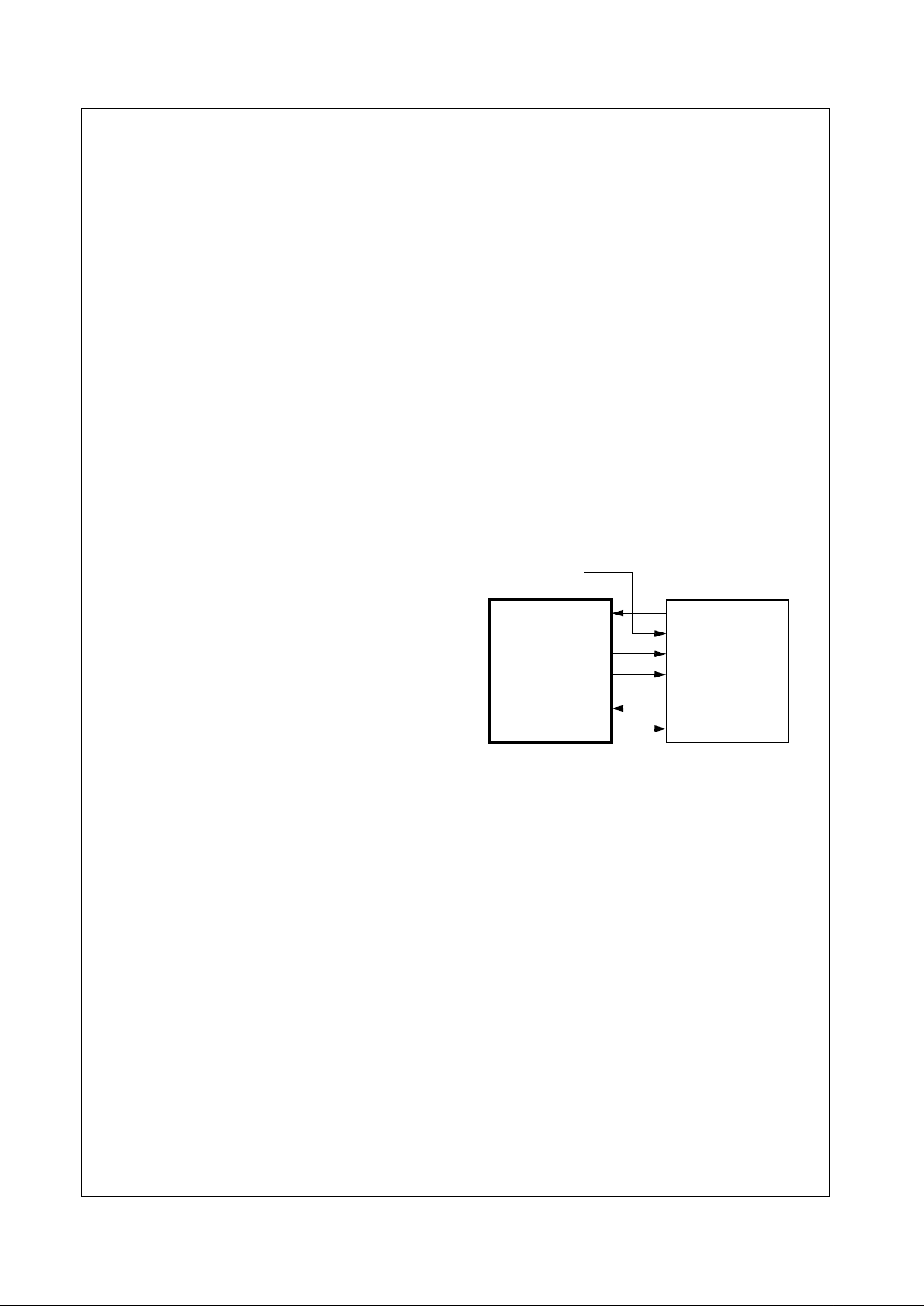

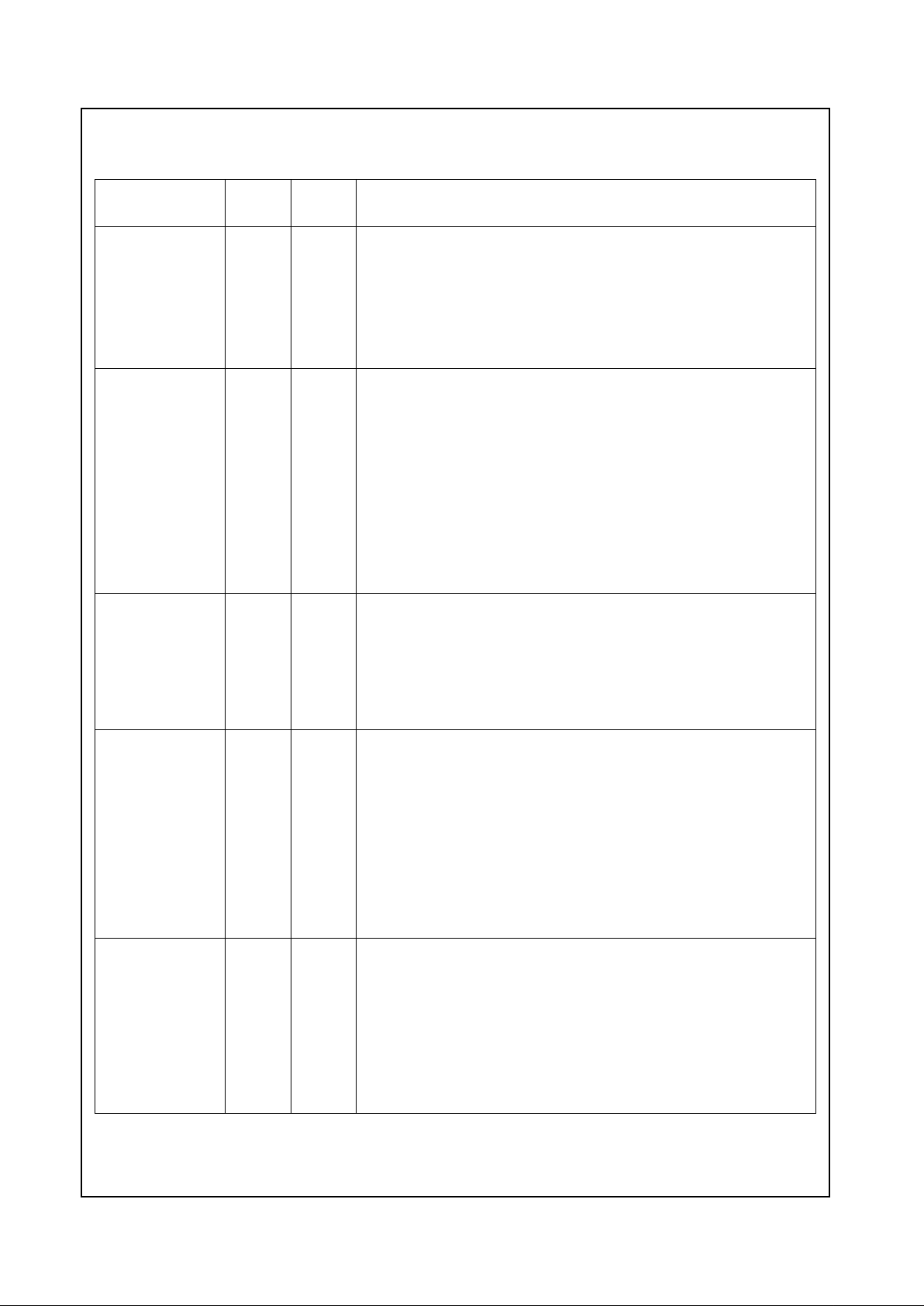

1.6.1 AC97 Codec Interface

The CS5530 provides an AC97 Specification Revision

1.3, 2.0, and 2.1 compatible interface. Any AC97 codec

which supports an independent input and output sample

rate conversion interface (e.g., National Semiconductor

LM4548) can be used with the CS5530. This type of

codec will allow for a design which meets the requirements for PC97 and PC98-compliant audio as defined by

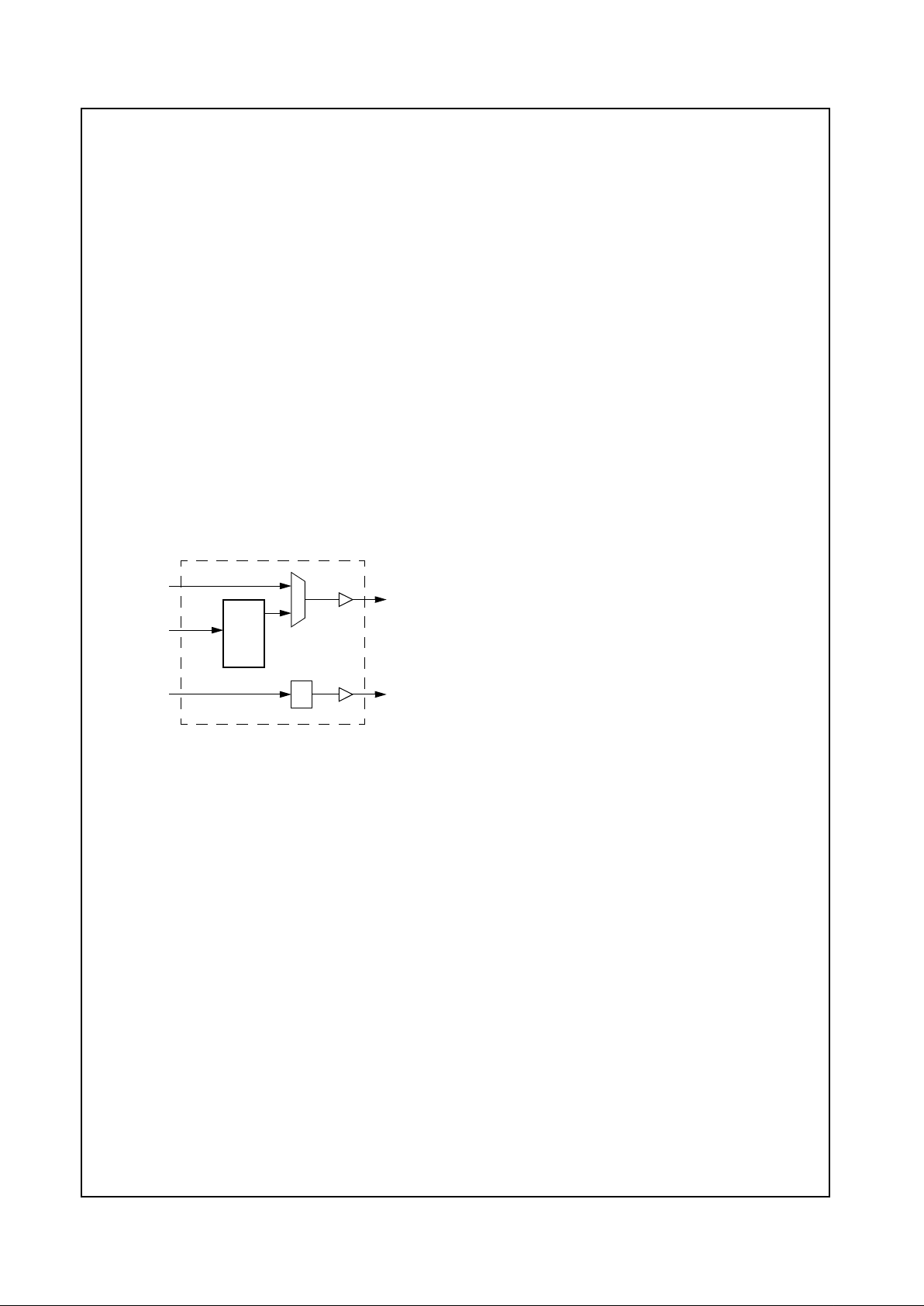

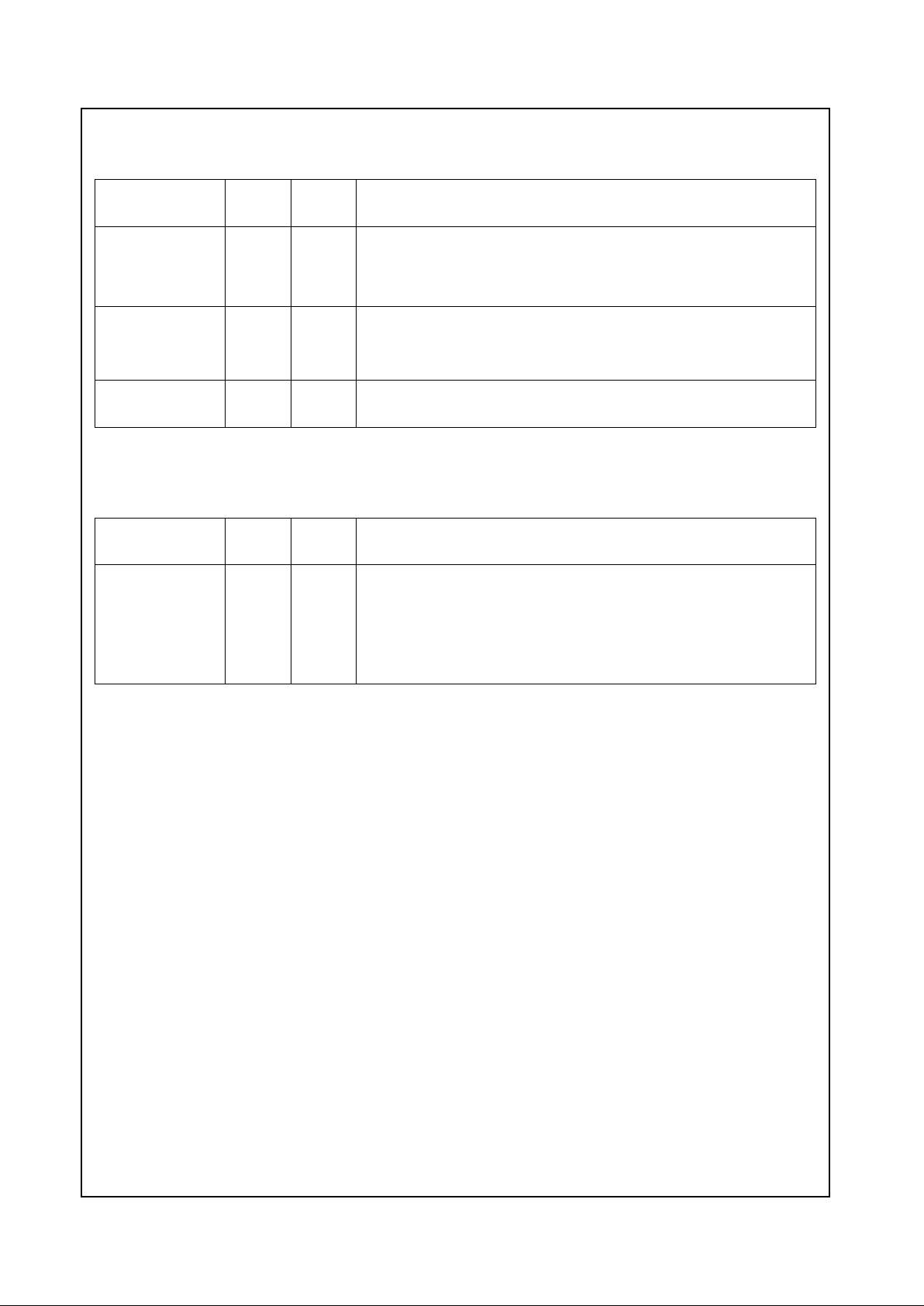

Microsoft Corporation. Figure 1-2 shows the codec and

CS5530 signal connections. For specifics on the serial

interface, refer to the appropriate codec manufacturer’s

data sheet.

Low latency audio I/O is accomplished by a buffered PCI

bus mastering controller.

Figure 1-2. AC97 Codec Signal Connections

1.6.2 VSA Technology Support Hardware

The CS5530 I/O companion incorporates the required

hardware in order to support VSA technology for the capture and playback of audio using an external codec. This

eliminates much of the hardware traditionally associated

with industry standard audio functions.

XpressAUDIO software provides 16-bit compatible sound.

This software is available to OEMs for incorporation into

the system BIOS ROM.

BITCLK

PC_BEEP

SDAT_I

SDAT_O

PC_BEEP

SDATA_IN

SDATA_OUT

AC97

Geode™

BIT_CLK

24.576 MHz

SYNC SYNC

Codec

External Source

CS5530

Revision 4.1 9 www.national.com

Architecture Overview (Continued)

Geode™ CS5530

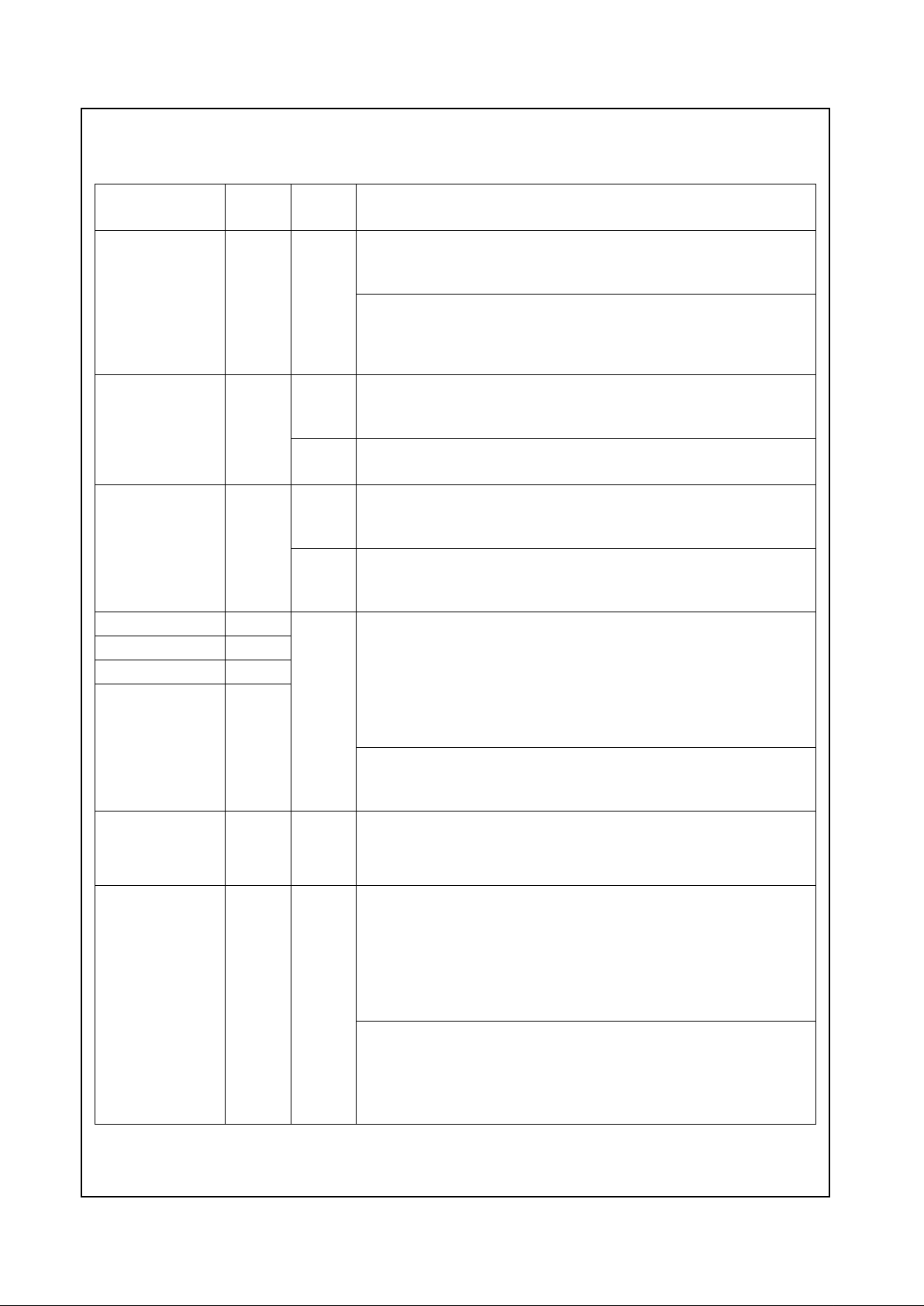

1.7 DISPLAY SUBSYSTEM EXTENSIONS

The CS5530 incorporates extensions to theGXLV processor’s display subsystem. These include:

• Video Accelerator

- Buffers and formats input YUV video data from

processor

- 8-bit interface to the GXLV processor

- X & Y scaler withbilinear filter

- Color space converter (YUV to RGB)

• VideoOverlay Logic

-Colorkey

- Data switch for graphics and video data

•GammaRAM

- Brightness and contrastcontrol

• Display Interface

- Integrated RGB Video DACs

- VESA DDC2B/DPMS support

- Flat panel interface

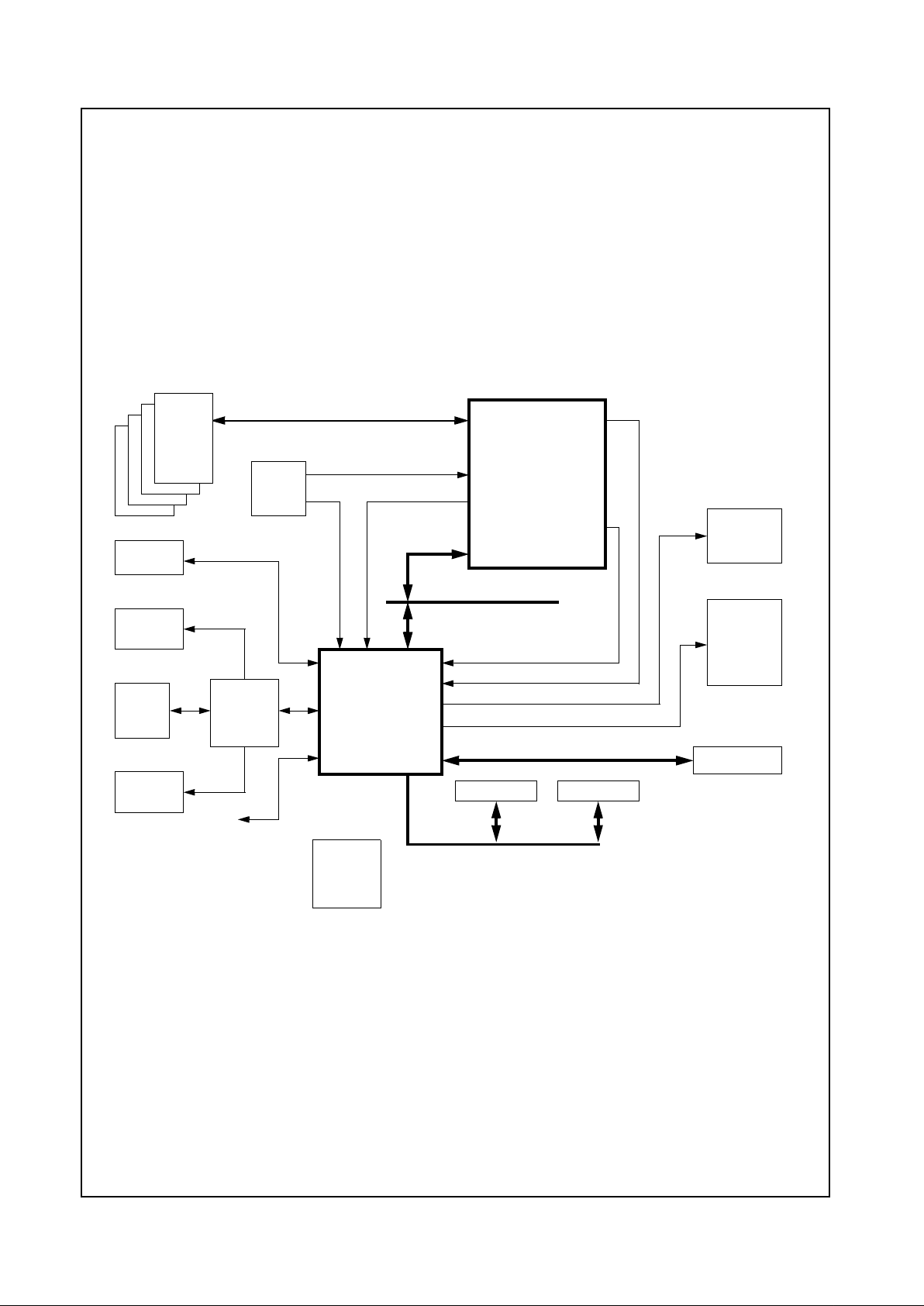

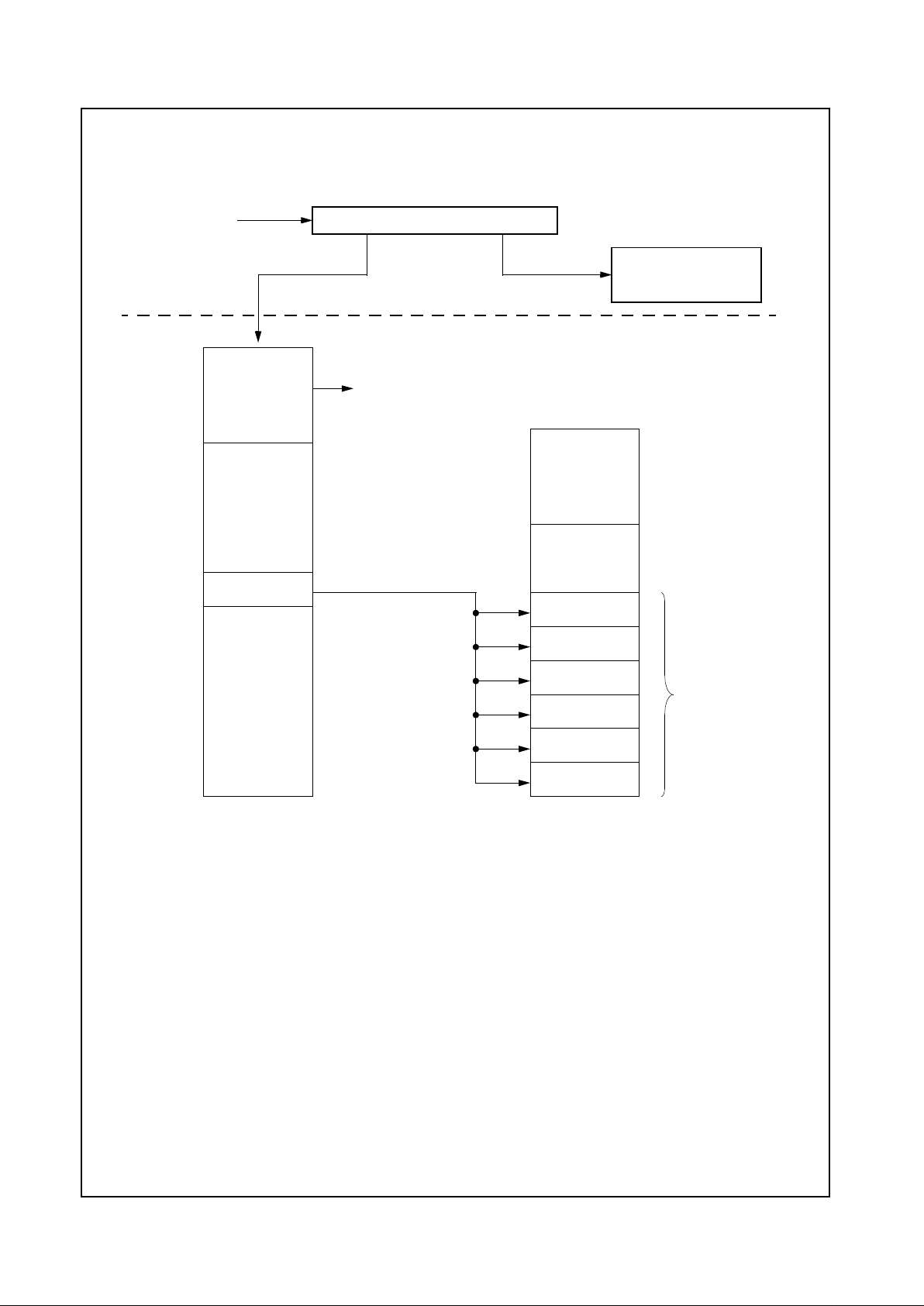

Figure 1-3 shows the data path of the display subsystem

extensions.

Figure 1-3. Display Subsystem Extensions, 8-Bit Interface

VID_DATA[7:0]

8

Input

Buffer 0

(3x360x32 bit)

Buffer 1

Buffer 2

Formatter

/

Scaler

Vertical

Filter

Horizontal

Filter

Color

Space

Converter

Formatter

24

Color Key

Color

Compare

24

PIXEL[23:0]

Bypass

Gamma

RAM

24

Video

Dither

24

8each

DAC

RGB to CRT

FP_DATA

18

24

24

Enable Gamma

Correction Register

24

24

Register

www.national.com 10 Revision 4.1

Architecture Overview (Continued)

Geode™ CS5530

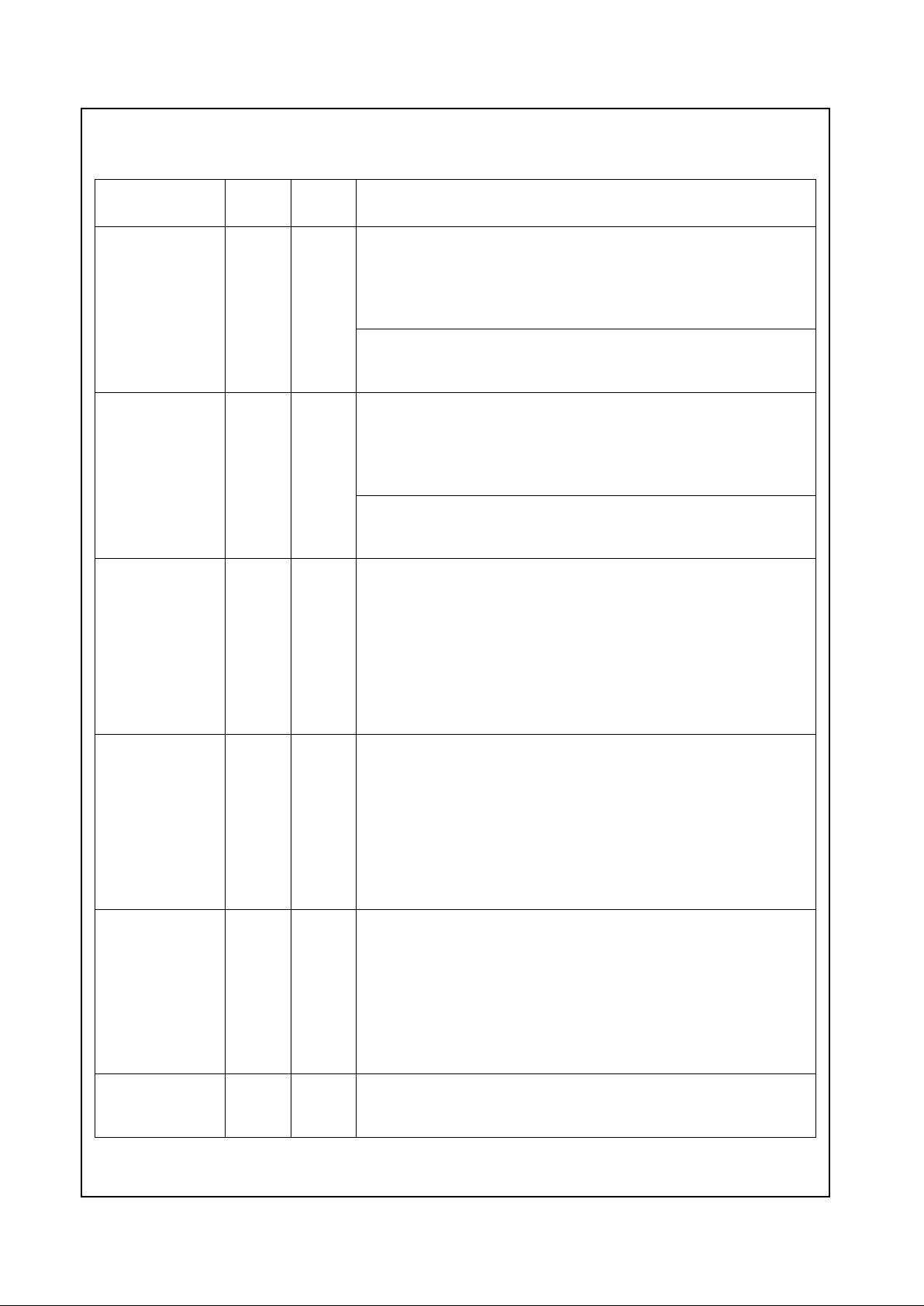

1.8 CLOCK GENERATION

In a CS5530/GXLV processor-based system, the CS5530

generates only the video DOT clock (DCLK) for the CPU

and the ISA clock. All other clocks are generated by an

external clock chip.

The ISACLK is created by dividing the PCICLK. For ISA

compatibility, the ISACLK nominally runs at 8.33 MHz or

less. The ISACLK dividers are programmed via F0 Index

50h[2:0].

DCLK is generated from the 14.31818 MHz input

(CLK_14MHZ). A combination of a phase locked loop

(PLL), linear feedback shift register (LFSR) and divisors

are used to generate the desired frequencies for the

DCLK. The divisors and LFSR are configurable through

the F4BAR+Memory Offset 24h. For applications that do

not use the GXLV processor’s video, this is an available

clock for general purpose use.

Figure 1-4 shows a block diagram for clock generation

within the CS5530.

Figure 1-4. CS5530 Clock Generation

1.9 UNIVERSAL SERIAL BUS

The CS5530 provides two complete, independent USB

ports. Each port has a Data "–" and a Data "+" pin.

The USB controller is a compliant Open Host Controller

Interface (OpenHCI). The OpenHCI specification provides

a register-level description for a host controller, as well as

a common industry hardware/software interface and drivers (see OpenHCI Specification, Revision 1.0, for description).

DCLK

DCLK

PLL

÷N

TVCLK

CLK_14MHZ

ISACLK

PCICLK

M

U

X

Revision 4.1 11 www.national.com

Architecture Overview (Continued)

Geode™ CS5530

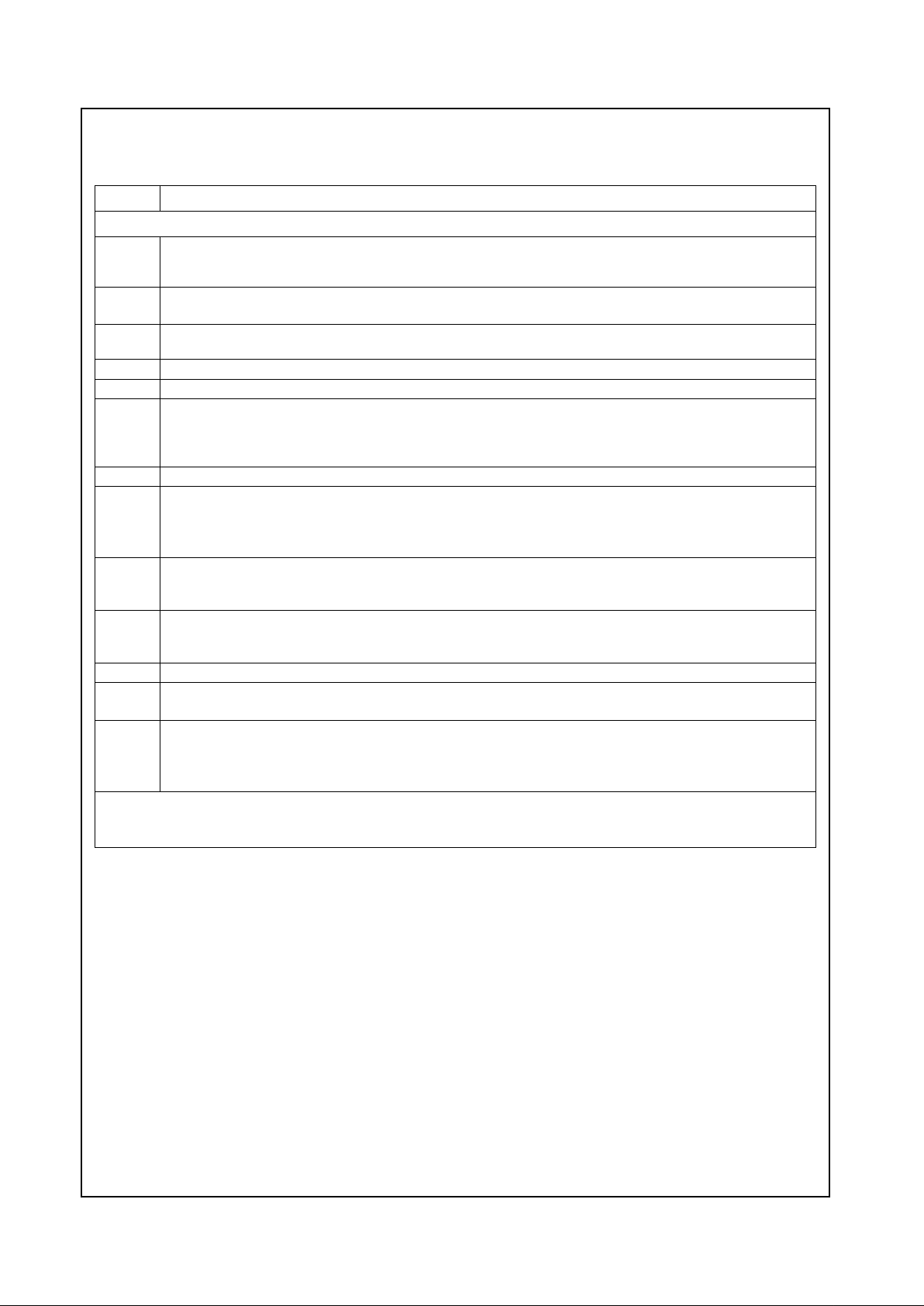

1.10 PROCESSOR SUPPORT

The traditional south bridge functionality included in the

CS5530 I/O companion chip has been designed to support the GXLV processor. When combined with the GXLV

processor, the CS5530 provides a bridge which supports

a standard ISA bus and system ROM. As part of the video

subsystem, the CS5530 provides MPEG video acceleration and a digital RGB interface, to allowdirect connection

to TFT LCD panels. This chip also integrates a gamma

RAM and three DACs, allowing for direct connection of a

CRT monitor. Figure 1-5 shows a typical system block diagram.

For detailed information regarding processor signal connections refer to Section 3.1 “Processor Interface” on

page 41.

Figure 1-5. System Block Diagram

YUV Port

(Video)

RGB Port

PCI Interface

Memory

Memory Data Bus

PCI Bus

Geode™ CS5530

I/O Companion

Graphics Data

Video Data

Analog RGB

Digital RGB

CRT

TFT

Flat Panel

USB

(2 Ports)

AC97

Codec

Speakers

CD

ROM

Audio

Microphone

GPIOs

Port

(Graphics)

Geode™ GXLV

IDE Devices

SuperI/O BIOS

ISA Bus

Ultra DMA/33 IDE Bus

Memory

Serial

Packet

DC-DC

&

Battery

Clocks

or TV

NTSC/PAL

Encoder

Processor

www.national.com 12 Revision 4.1

Geode™ CS5530

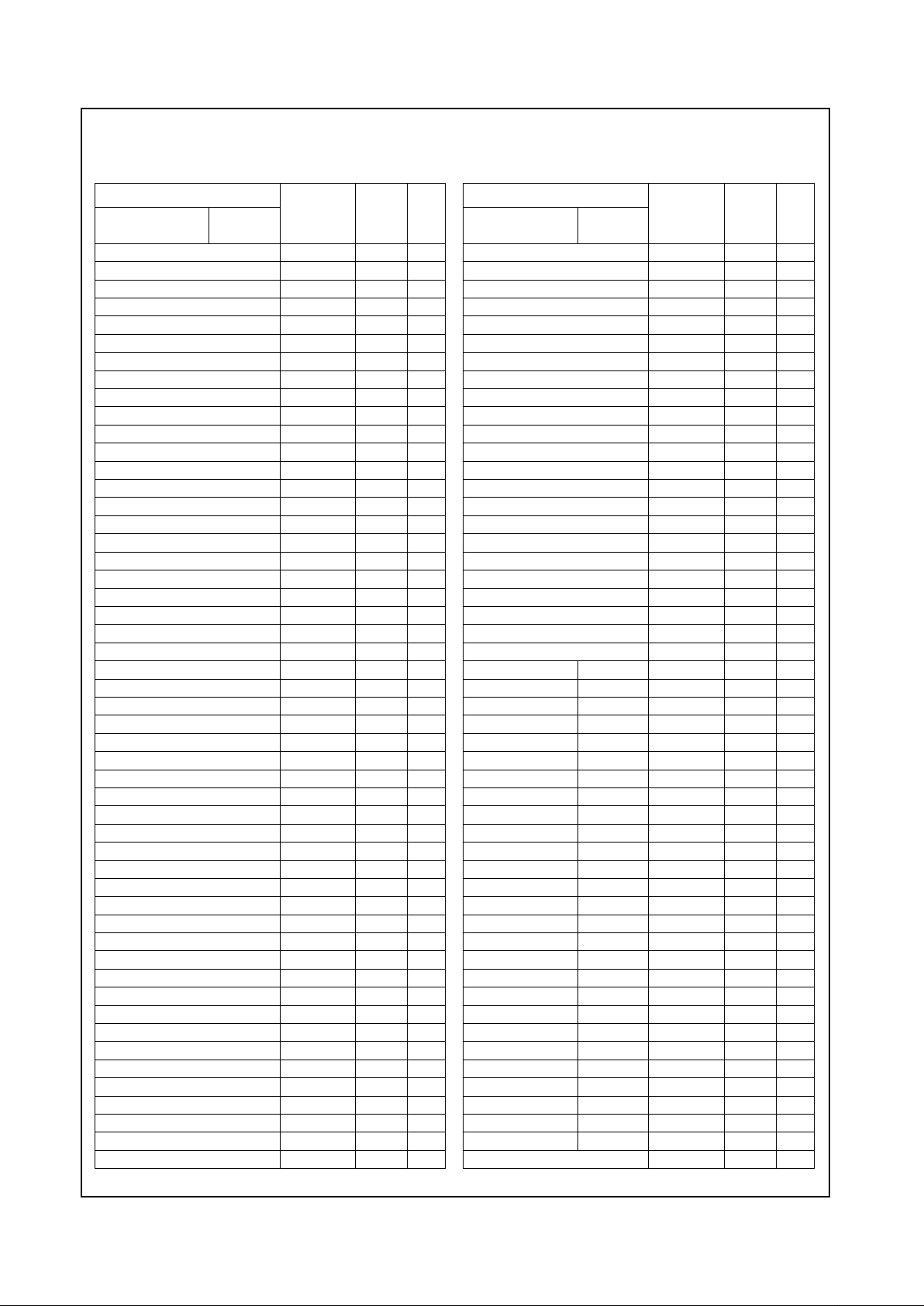

2.0 Signal Definitions

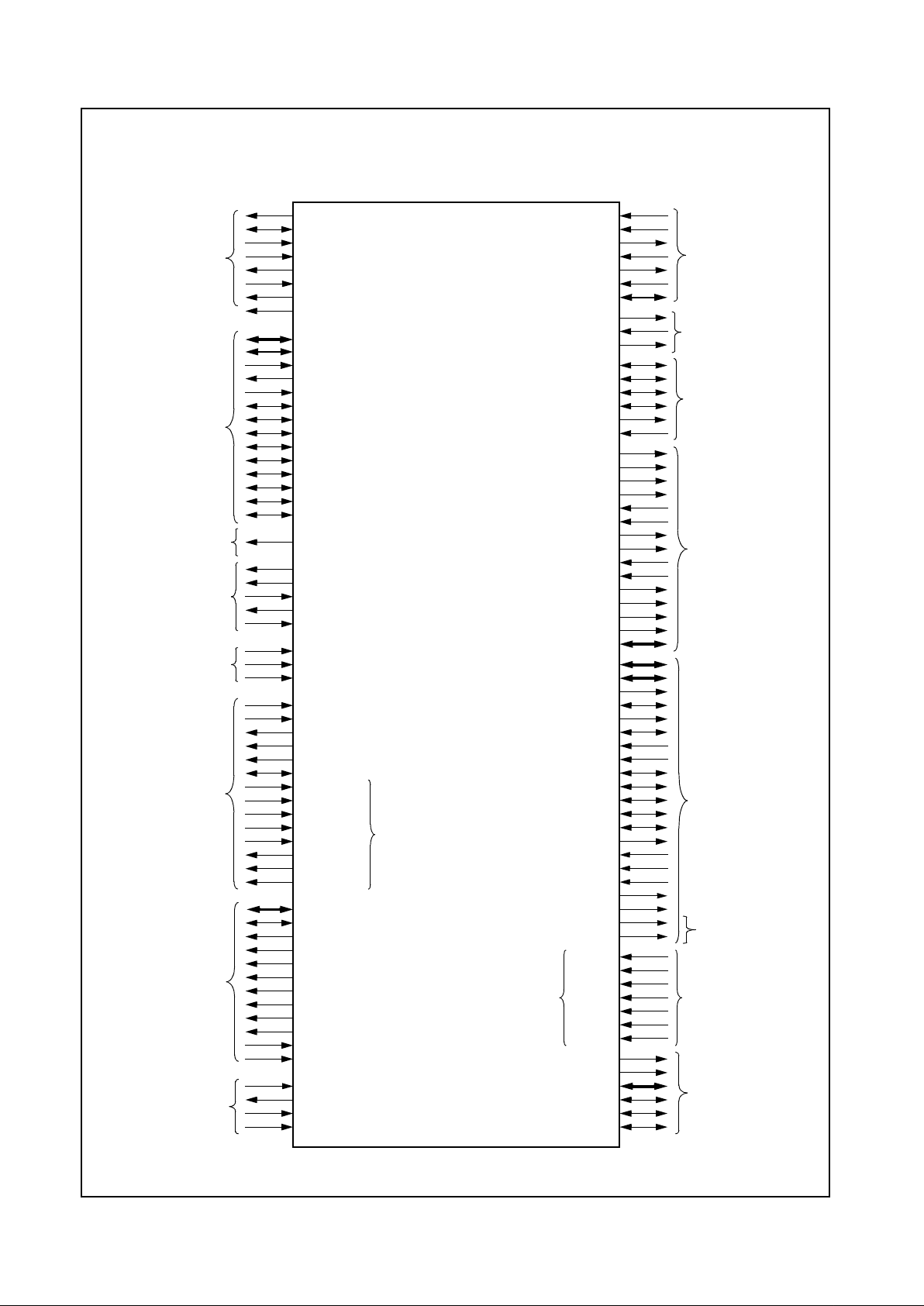

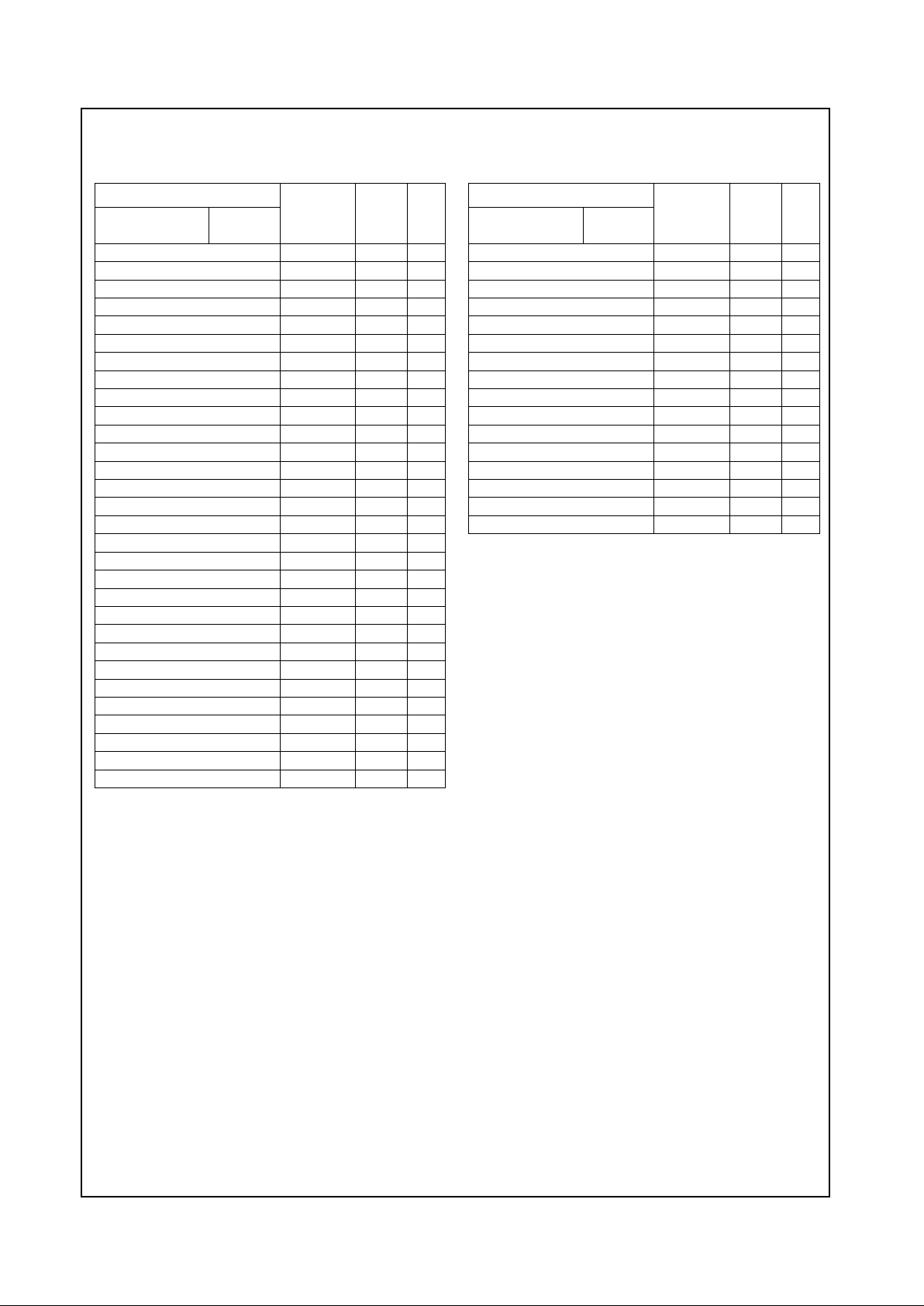

This section defines the signals and describes the external interface of the Geode CS5530. Figure 2-1 shows the

pins organized by their functional groupings (internal test

and electrical pins are not shown).

Figure 2-1. CS5530 Signal Groups

AD[31:0]

C/BE[3:0]#

PAR

HOLD_REQ#

FRAME#

TRDY#

STOP#

LOCK#

DEVSEL#

REQ#

GNT#

SERR#

INTA#-INTD#

IRQ13

INTR

SMI#

IDE_DACK1#

IDE_IORDY0

ROM Interface

PCI Bus

CPU Interface

IDE Controller

PSERIAL

SUSP#

SUSPA#

KBROMCS#

IRDY#

PERR#

SUSP_3V

IDE_IOW1#

IDE_IOW0#

IDE_IOR0#

IDE_IOR1#

Geode™ CS5530

IDE_DATA[15:0]

IDE_ADDR[2:0]

IDE_RST#

IDE_CS0#

IDE_CS1#

IDE_DREQ1

IDE_DACK0#

IDE_DREQ0

IDE_IORDY1

TVCLK

DCLK

PCICLK

ISACLK

Clocks

CLK_32K

CLK14_MHZ

Reset

PCI_RST#

POR#

CPU_RST

USBCLK

D+_PORT1

D–_PORT1

D+_PORT2

D–_PORT2

USB

POWER_EN

OVER_CUR#

SDATA_OUT

SDATA_IN

SYNC

BIT_CLK

PC_BEEP

Audio Interface

I/O Companion

VREF

EXTVREFIN

PCLK

IOUTG

IOUTB

AVSS1-5

IOUTR

AVDD1-3

HSYNC_OUT

HSYNC

VSYNC

PIXEL[23:0]

FP_DATA17 (MASTER#)

FP_CLK (No Function)

Display: Pixel

Display: CRT

ENA_DISP

VSYNC_OUT

DDC_SCL

DDC_SDA

FP_HSYNC_OUT (SMEMW#)

FP_CLK_EVEN (No Function)

FP_VSYNC_OUT (SMEMR#)

IREF

FP_DISP_ENA_OUT (No Function)

FP_ENA_VDD(No Function)

FP_ENA_BKL (No Function)

FP_HSYNC(No Function)

FP_VSYNC(No Function)

Analog

Display: MPEG

PLLDVD

PLLVAA

PLLRO

PLLLP

PLLAGS

DCLKPLL

Analog

Port

PLLAGD

PLLDGN

VID_RDY

VID_VAL

VID_CLK

VID_DATA[7:0]

SA[19:16]

(SA_DIR) SA_LATCH

SBHE#

BALE

IOCHRDY

ZEROWS#

IOR#

IOW#

MEMCS16#

MEMR#

MEMW#

AEN

DRQ[7:5], [3:0]

DACK#[7:5], [3:0]

TC

IRQ[15:14], [12:9], [7:3], 1

ISA Bus

IRQ8#

IOCS16#

(SD[15:0]) SA[15:0]/SD[15:0]

GPCS#

GPORT_CS#

(SA[23:20]) GPIO[7:4]/SA[23:20]

GPIO[3:2]

GPIO1/SDATA_IN2

GPIO0

Game Port/

GPIO

SMEMW#/RTCCS#

SMEMR#/RTCALE

FP_DATA16(SA_OE#)

FP_DATA[15:0] (SA[15:0])

External RTC

Display: TFT/TV

Note: Pins that change

function when ISA Master

mode is invoked are represented with the ISA Master Mode function signal

name in parenthesis.

Revision 4.1 13 www.national.com

Signal Definitions (Continued)

Geode™ CS5530

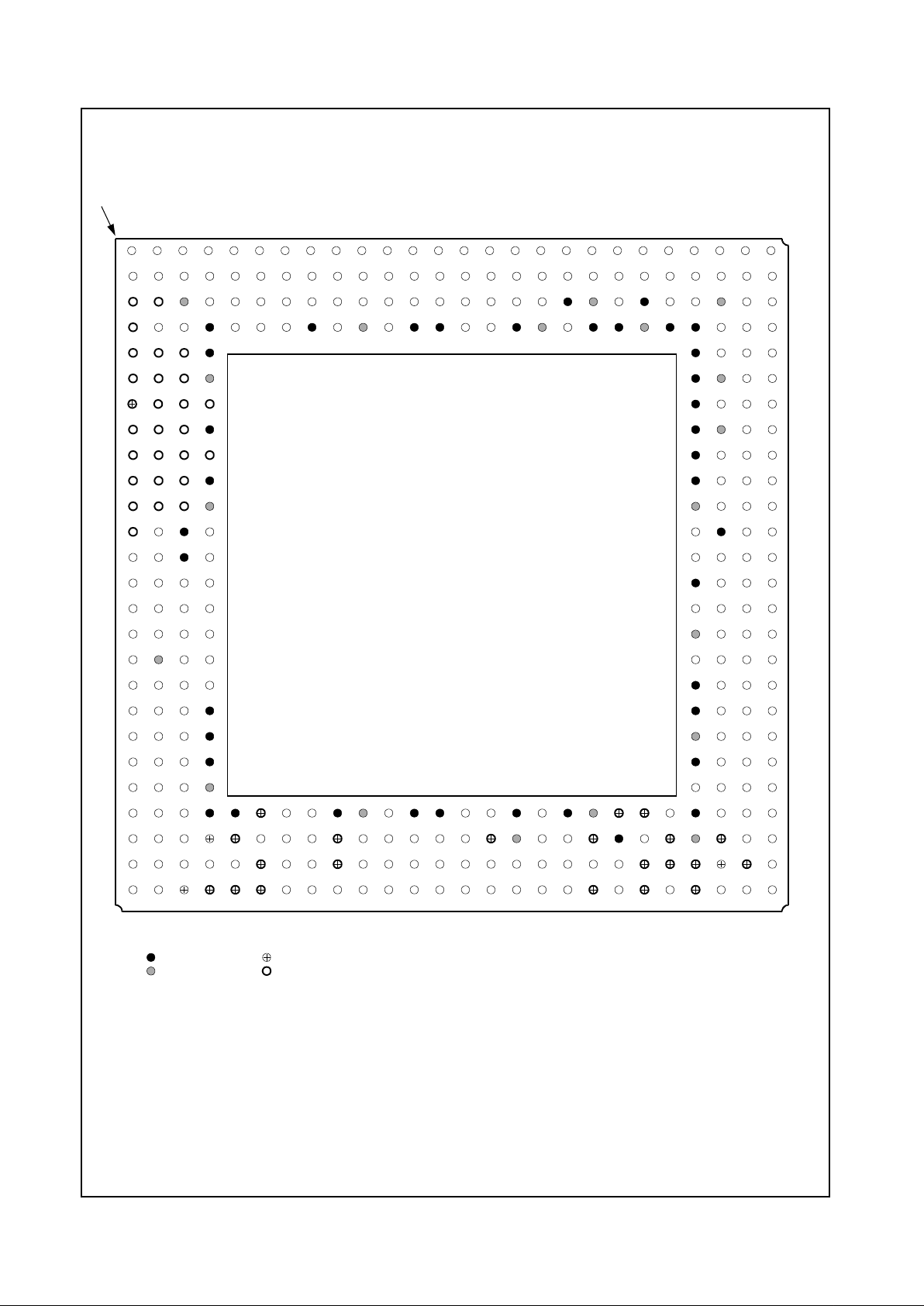

2.1 PIN ASSIGNMENTS

The tables in this section use several common abbreviations. Table 2-1 lists the mnemonics and their meanings.

Figure 2-2 shows the pin assignment for the CS5530 with

Tables 2-2 and 2-3 listing the pin assignments sorted by

terminal number and alphabetically by signal name,

respectively.

In Section 2.2 “Signal Descriptions” a description of each

signal within its associated functional group is provided.

In the signal definitions, references to F0-F4, F1BAR,

F2BAR, F3BAR, F4BAR, and PCIUSB are made. These

terms relate to designated register spaces. Refer to Table

4-1 "PCI Configuration Address Register (0CF8h)" on

page 138 for details regarding these register spaces and

their access mechanisms.

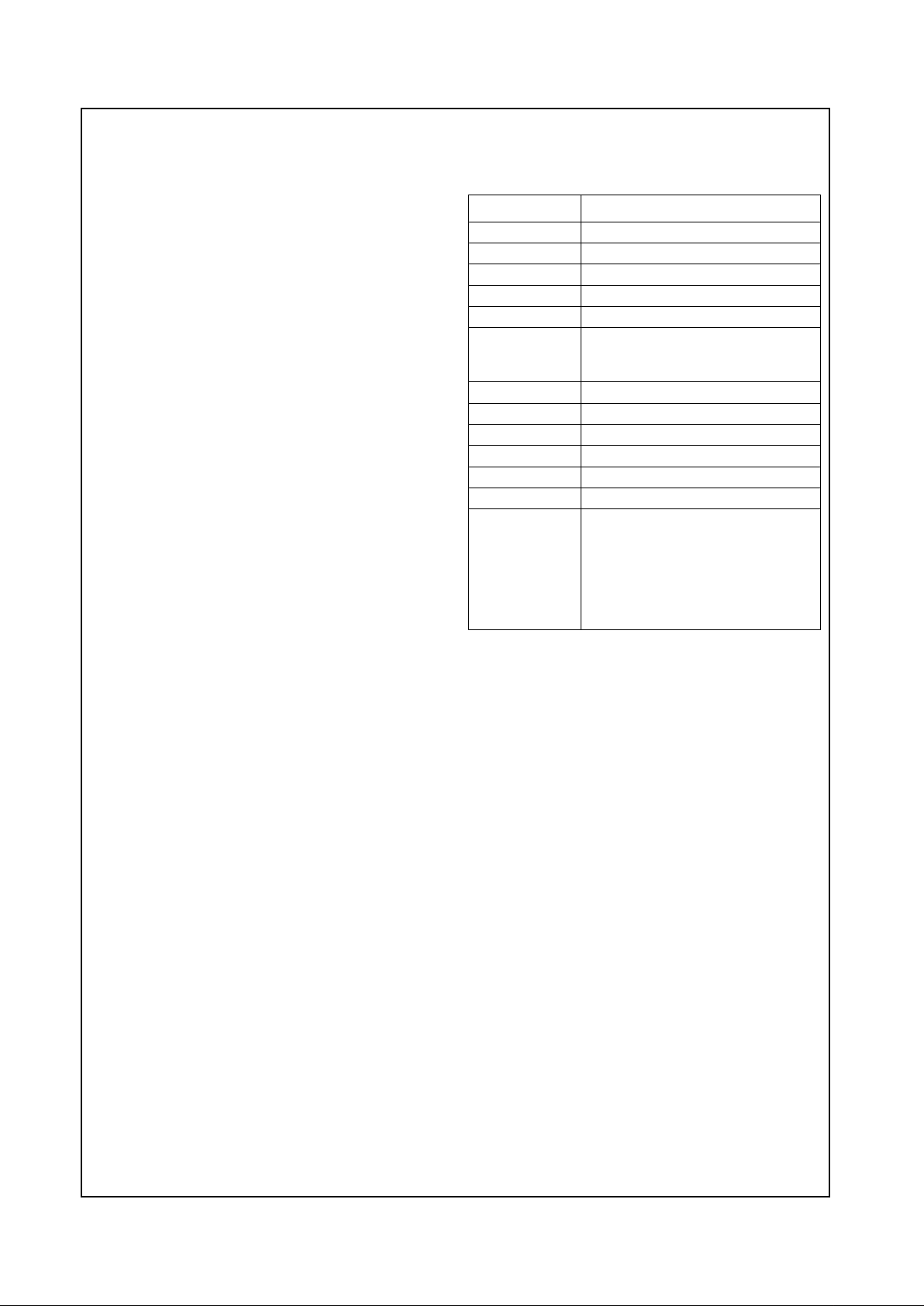

Table 2-1. Pin Type Definitions

Mnemonic Definition

5VT Buffer is 5V tolerant

I Input pin

I/O Bidirectional pin

IBUF Input buffer

OOutput

OD Open-drain output structure that

allows multiple devices to share the

pin in a wired-ORconfiguration

PU Pull-upresistor

PD Pull-down resistor

smt Schmitt Trigger

t/s Tri-state signal

VDD (PWR) Power pin

VSS (GND) Ground pin

# The "#" symbol at theend of a signal

name indicates that the active, or

asserted state occurs when the signal

is at a lowvoltage level. When "#"is

not present after the signal name, the

signal is asserted when at a high volt-

age level.

www.national.com 14 Revision 4.1

Signal Definitions (Continued)

Geode™ CS5530

Figure 2-2. TBGA Pin Assignment Diagram

Order Number: 25420-03

1234567891011121314151617181920

21 22 23 24 25 26

A

B

C

D

E

F

G

H

J

K

L

M

N

P

R

T

U

V

W

Y

AA

AB

AC

AD

AE

AF

Index Corner

PIX0 PIX1 PIX2 PIX7 PIX10 VCLK PIX12 PIX16 PIX19 DCLK VDAT0 VDAT5 PCLK INTA# AD0 AD7 AD9 AD12 AD10 AD15 PAR SERR# DVSL# C/BE2# AD17 AD16

ENADISP TVCLK PIX4 PIX5 VSYNC PIX8 VDVAL PIX15 PIX18 VDRDY PIX22 VDAT6 VDAT2 INTD# AD3 AD5 AD6 C/BE0# AD11 AD14 C/BE1# PERR# TRDY# IRDY# AD18 AD19

FPVSY FPHSY VDD PIX3 PIX11 HSYN PIX14 PIX17 PIX21 PIX23 VDAT3 VDAT7 VDAT1 PRST# INTC# AD2 AD4 VSS VDD AD13 VSS LOCK# FRAM# VDD AD21 AD22

FPD11 NC TEST VSS PIX6 PIX9 PIX13 VSS PIX20 VDD VDAT4 VSS VSS AD1 INTB# VSS VDD AD8 VSS VSS VDD VSS VSS GNT# AD26 C/BE3#

FPHSYO FPD10 FPVSYO VSS VSS AD20 AD23 STOP#

FPD9 DISENO FPD17 VDD VSS VDD AD24 AD27

FPD8 FPD5 FPD7 FPD6 VSS AD25 AD28 AD29

FPD4 FPD15 FPD16 VSS VSS VDD AD31 HDRQ#

FPD3 FPD1 FPD2 ENBKL VSS AD30 REQ# PCICLK

FPD14 FPD13 FPD0 VSS VSS POR# CPURST SUSP#

FPD12 ENVDD CKEVEN VDD VDD SUSP3V SUSPA# PSERL

FPCLK DDCSCL VSS DDCSDA PLDVD VSS PLVAA PLRO

HSYNO VSYNO VSS AVDD3 PLP PLAGS PLAGD PLDGN

AVSS4 AVSS5 IOUTR IOUTG VSS 14MHZ SMI# INTR

IOUTB AVSS1 IREF AVSS2 IRQ13 DIOW0# DIOR1# DIOR0#

VREF XVREFI AVDD2 AVSS3 VDD DDCK1# DIOW1# DDCK0#

AVDD1 VDD SYNC SDATI IDED7 IDED6 IDEA0 IDEA1

SDATO BITCLK PCBEEP PWREN VSS IDED8 IDED10 DCS0#

USBCLK NC OVRCUR# VSS VSS IDEA2 DRST# IDED5

D–PT1 D+PT1 NC VSS VDD IDED11 IDED9 DCS1#

D–PT2 D+PT2 NC VSS VSS IDED1 IDED12 IDED4

NC NC NC VDD IDED15 IDED2 IDED13 IDED3

NC NC NC VSS VSS SA3 DCK7# DCK1# VSS VDD IOW# VSS VSS IRQ3 MCS16# VSS IRQ14 VSS VDD SA10 GPIO5 GPIO0 VSS DREQ1 IDED14 IDED0

NC NC NC SMEMR# SA5 ISACLK DCK6# DCK0# SA2 SA19 SA16 DRQ1 DRQ3 IRQ7 SLTCH VDD IRQ15 DRQ5 SA9 VSS GPTCS# GPIO4 VDD SA14 IORDY0 DREQ0

NC NC 32K KRMCS# IRQ9 SA1 DCK5# AEN SA0 DRQ2 SA18 IOR# IRQ5 IRQ8# IRQ4 IRQ10 SBHE# DRQ0 MEMR# DRQ6 SA12 SA13 GPIO6 GPIO1 SA15 IORDY1

NC NC SMEMW# SA7 SA6 SA4 DCK3# DCK2# BALE 0WS# CHRDY SA17 IRQ1 IRQ6 TC CS16# IRQ12 IRQ11 SA8 MEMW# SA11 DRQ7 GPIO7 GPIO3 GPIO2 GPCS#

1234567891011121314151617181920

21 22 23 24 25 26

A

B

C

D

E

F

G

H

J

K

L

M

N

P

R

T

U

V

W

Y

AA

AB

AC

AD

AE

AF

Geode™ CS5530

I/O Companion

Top View

Note: Signal names have been abbreviated in this f ig ure due to space constraints.

= GND terminal

= PWR terminal

= Multiplexed signal

= Changes function in ISA Master Mode

Revision 4.1 15 www.national.com

Signal Definitions (Continued)

Geode™ CS5530

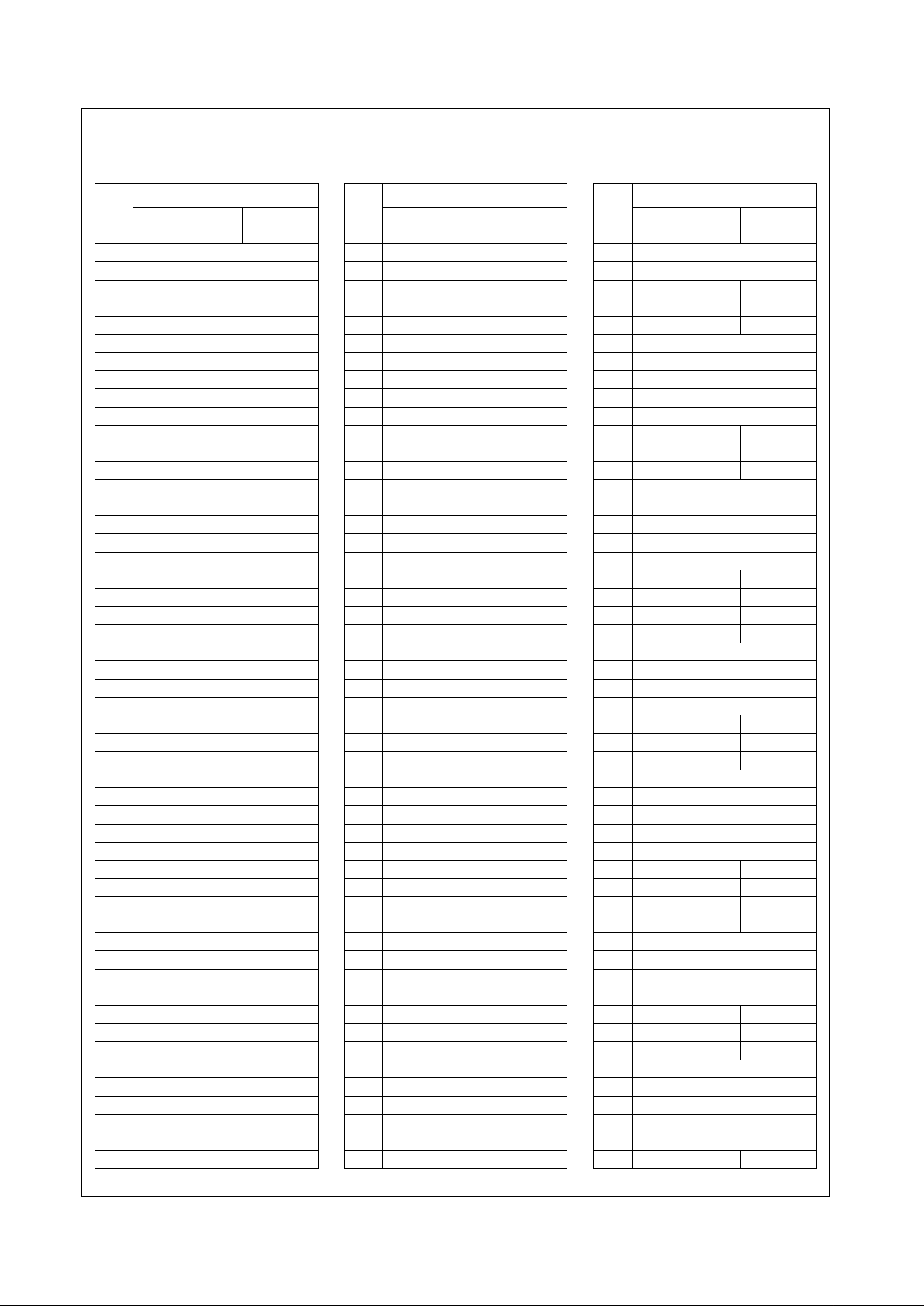

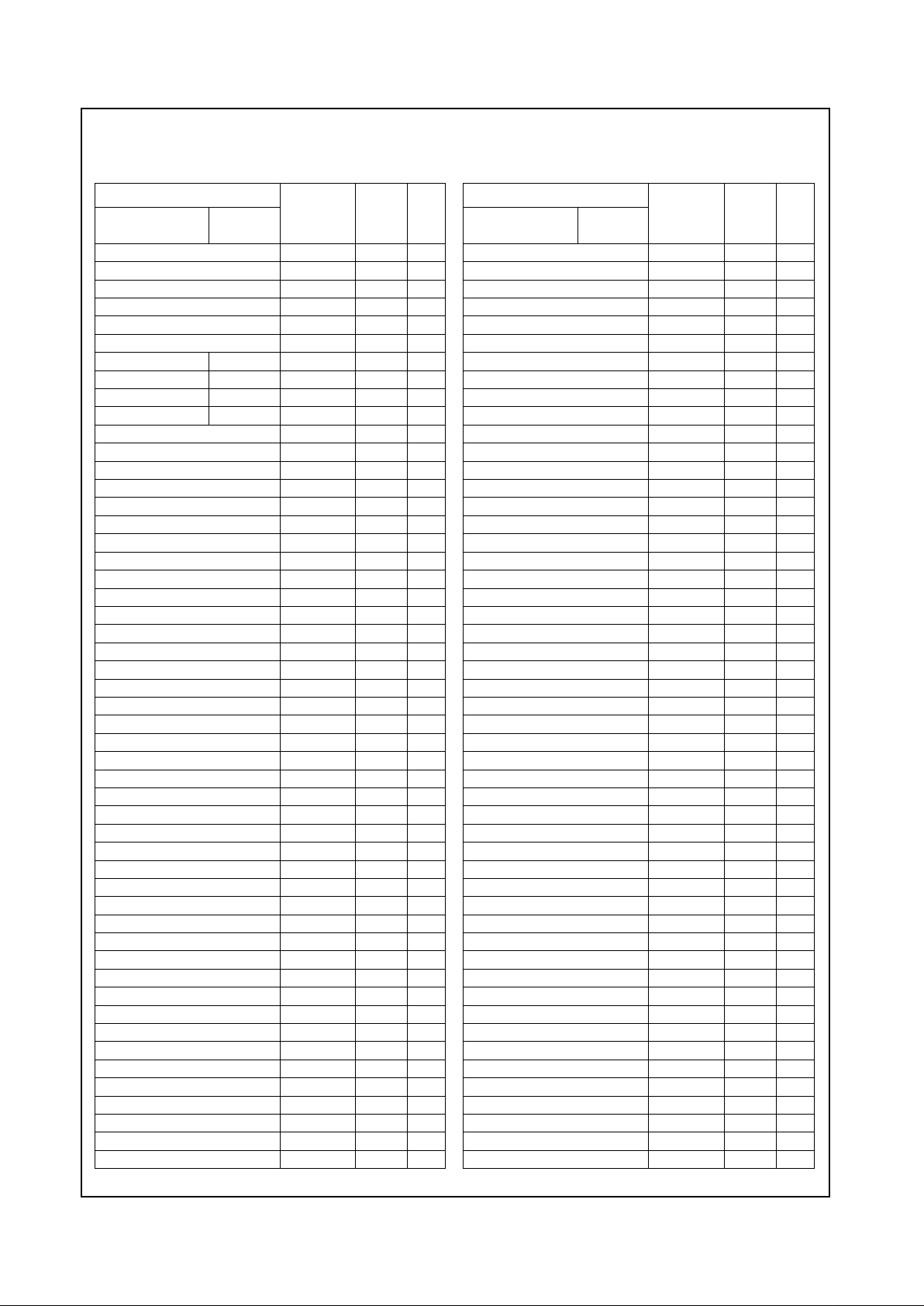

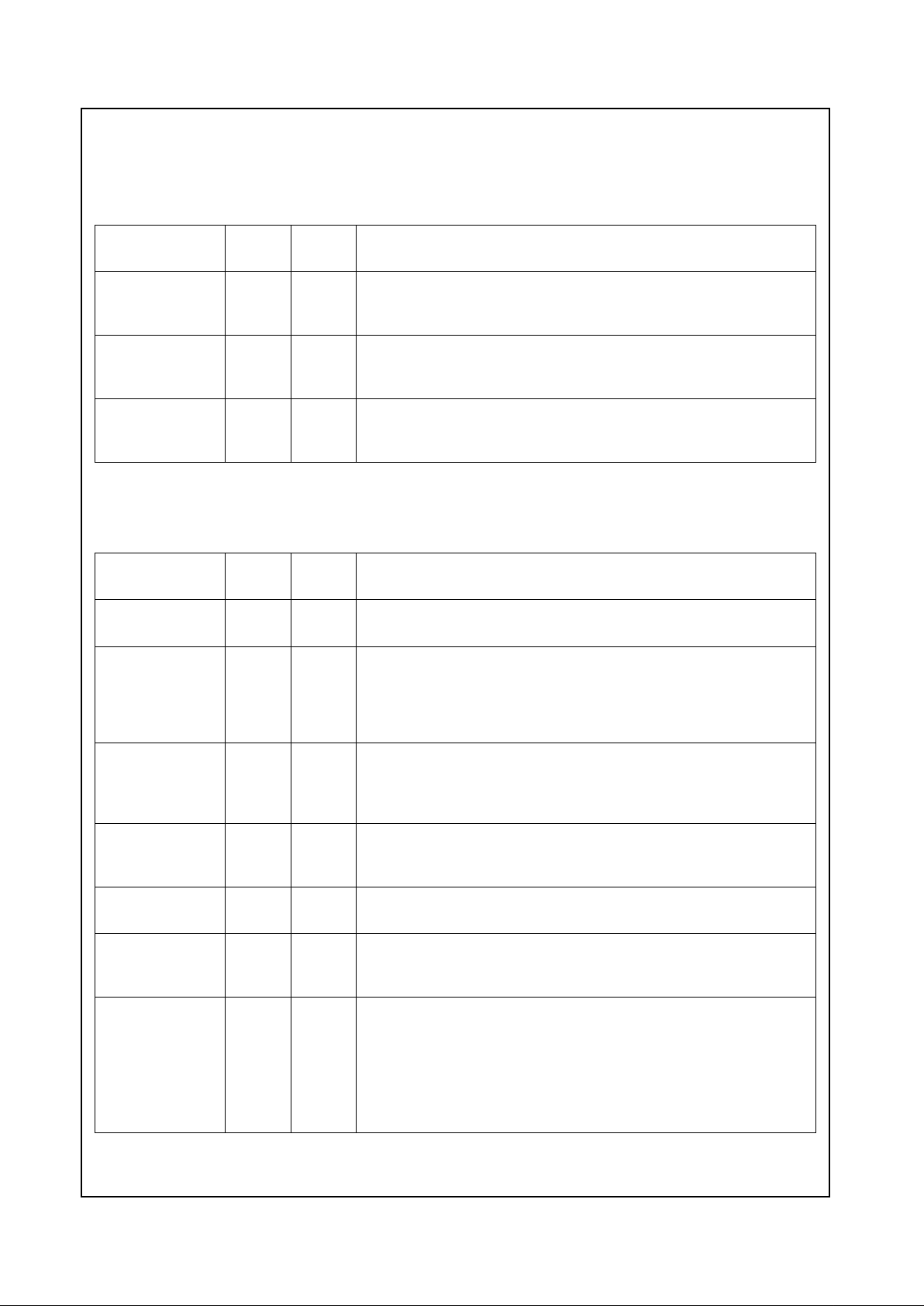

Table 2-2. 352 TBGA Pin Assignments - Sorted by Pin Number

Pin

No.

Signal Name

Limited

ISA Mode

ISA Master

Mode

A1 PIXEL0

A2 PIXEL1

A3 PIXEL2

A4 PIXEL7

A5 PIXEL10

A6 VID_CLK

A7 PIXEL12

A8 PIXEL16

A9 PIXEL19

A10 DCLK

A11 VID_DATA0

A12 VID_DATA5

A13 PCLK

A14 INTA#

A15 AD0

A16 AD7

A17 AD9

A18 AD12

A19 AD10

A20 AD15

A21 PAR

A22 SERR#

A23 DEVSEL#

A24 C/BE2#

A25 AD17

A26 AD16

B1 ENA_DISP

B2 TVCLK

B3 PIXEL4

B4 PIXEL5

B5 VSYNC

B6 PIXEL8

B7 VID_VAL

B8 PIXEL15

B9 PIXEL18

B10 VID_RDY

B11 PIXEL22

B12 VID_DATA6

B13 VID_DATA2

B14 INTD#

B15 AD3

B16 AD5

B17 AD6

B18 C/BE0#

B19 AD11

B20 AD14

B21 C/BE1#

B22 PERR#

B23 TRDY#

B24 IRDY#

B25 AD18

B26 AD19

C1 FP_VSYNC No Function

C2 FP_HSYNC No Function

C3 VDD

C4 PIXEL3

C5 PIXEL11

C6 HSYNC

C7 PIXEL14

C8 PIXEL17

C9 PIXEL21

C10 PIXEL23

C11 VID_DATA3

C12 VID_DATA7

C13 VID_DATA1

C14 PCI_RST#

C15 INTC#

C16 AD2

C17 AD4

C18 VSS

C19 VDD

C20 AD13

C21 VSS

C22 LOCK#

C23 FRAME#

C24 VDD

C25 AD21

C26 AD22

D1 FP_DATA11 SA11

D2 NC

D3 TEST

D4 VSS

D5 PIXEL6

D6 PIXEL9

D7 PIXEL13

D8 VSS

D9 PIXEL20

D10 VDD

D11 VID_DATA4

D12 VSS

D13 VSS

D14 AD1

D15 INTB#

D16 VSS

D17 VDD

D18 AD8

D19 VSS

D20 VSS

D21 VDD

D22 VSS

D23 VSS

D24 GNT#

Pin

No.

Signal Name

Limited

ISA Mode

ISA Master

Mode

D25 AD26

D26 C/BE3#

E1 FP_HSYNC_OUT SMEMW#

E2 FP_DATA10 SA10

E3 FP_VSYNC_OUT SMEMR#

E4 VSS

E23 VSS

E24 AD20

E25 AD23

E26 STOP#

F1 FP_DATA9 SA9

F2 FP_DISP_ENA_OUT No Function

F3 FP_DATA17 MASTER#

F4 VDD

F23 VSS

F24 VDD

F25 AD24

F26 AD27

G1 FP_DATA8 SA8

G2 FP_DATA5 SA5

G3 FP_DATA7 SA7

G4 FP_DATA6 SA6

G23 VSS

G24 AD25

G25 AD28

G26 AD29

H1 FP_DATA4 SA4

H2 FP_DATA15 SA15

H3 FP_DATA16 SA_OE#

H4 VSS

H23 VSS

H24 VDD

H25 AD31

H26 HOLD_REQ#

J1 FP_DATA3 SA3

J2 FP_DATA1 SA1

J3 FP_DATA2 SA2

J4 FP_ENA_BKL No Function

J23 VSS

J24 AD30

J25 REQ#

J26 PCICLK

K1 FP_DATA14 SA14

K2 FP_DATA13 SA13

K3 FP_DATA0 SA0

K4 VSS

K23 VSS

K24 POR#

K25 CPU_RST

K26 SUSP#

L1 FP_DATA12 SA12

Pin

No.

Signal Name

Limited

ISA Mode

ISA Master

Mode

www.national.com 16 Revision 4.1

Signal Definitions (Continued)

Geode™ CS5530

L2 FP_ENA_VDD No Function

L3 FP_CLK_EVEN No Function

L4 VDD

L23 VDD

L24 SUSP_3V

L25 SUSPA#

L26 PSERIAL

M1 FP_CLK NoFunction

M2 DDC_SCL

M3 VSS

M4 DDC_SDA

M23 PLLDVD

M24 VSS

M25 PLLVAA

M26 PLLRO

N1 HSYNC_OUT

N2 VSYNC_OUT

N3 VSS

N4 AVDD3(DAC)

N23 PLLLP

N24 PLLAGS

N25 PLLAGD

N26 PLLDGN

P1 AVSS4(ICAP)

P2 AVSS5(DAC)

P3 IOUTR

P4 IOUTG

P23 VSS

P24 CLK_14MHZ

P25 SMI#

P26 INTR

R1 IOUTB

R2 AVSS1(DAC)

R3 IREF

R4 AVSS2(ICAP)

R23 IRQ13

R24 IDE_IOW0#

R25 IDE_IOR1#

R26 IDE_IOR0#

T1 VREF

T2 EXTVREFIN

T3 AVDD2(VREF)

T4 AVSS3(VREF)

T23 VDD

T24 IDE_DACK1#

T25 IDE_IOW1#

T26 IDE_DACK0#

U1 AVDD1(DAC)

U2 VDD

U3 SYNC

U4 SDATA_IN

Pin

No.

Signal Name

Limited

ISA Mode

ISA Master

Mode

U23 IDE_DATA7

U24 IDE_DATA6

U25 IDE_ADDR0

U26 IDE_ADDR1

V1 SDATA_OUT

V2 BIT_CLK

V3 PC_BEEP

V4 POWER_EN

V23 VSS

V24 IDE_DATA8

V25 IDE_DATA10

V26 IDE_CS0#

W1 USBCLK

W2 NC

W3 OVER_CUR#

W4 VSS

W23 VSS

W24 IDE_ADDR2

W25 IDE_RST#

W26 IDE_DATA5

Y1 D–_PORT1

Y2 D+_PORT1

Y3 NC

Y4 VSS

Y23 VDD

Y24 IDE_DATA11

Y25 IDE_DATA9

Y26 IDE_CS1#

AA1 D–_PORT2

AA2 D+_PORT2

AA3 NC

AA4 VSS

AA23 VSS

AA24 IDE_DATA1

AA25 IDE_DATA12

AA26 IDE_DATA4

AB1 NC

AB2 NC

AB3 NC

AB4 VDD

AB23 IDE_DATA15

AB24 IDE_DATA2

AB25 IDE_DATA13

AB26 IDE_DATA3

AC1 NC

AC2 NC

AC3 NC

AC4 VSS

AC5 VSS

AC6 SA3/SD3 SD3

AC7 DACK7#

Pin

No.

Signal Name

Limited

ISA Mode

ISA Master

Mode

AC8 DACK1#

AC9 VSS

AC10 VDD

AC11 IOW#

AC12 VSS

AC13 VSS

AC14 IRQ3

AC15 MEMCS16#

AC16 VSS

AC17 IRQ14

AC18 VSS

AC19 VDD

AC20 SA10/SD10 SD10

AC21 GPIO5/SA21 SA21

AC22 GPIO0

AC23 VSS

AC24 IDE_DREQ1

AC25 IDE_DATA14

AC26 IDE_DATA0

AD1 NC

AD2 NC

AD3 NC

AD4 SMEMR#/RTCALE

AD5 SA5/SD5 SD5

AD6 ISACLK

AD7 DACK6#

AD8 DACK0#

AD9 SA2/SD2 SD2

AD10 SA19

AD11 SA16

AD12 DRQ1

AD13 DRQ3

AD14 IRQ7

AD15 SA_LATCH SA_DIR

AD16 VDD

AD17 IRQ15

AD18 DRQ5

AD19 SA9/SD9 SD9

AD20 VSS

AD21 GPORT_CS#

AD22 GPIO4/SA20 SA20

AD23 VDD

AD24 SA14/SD14 SD14

AD25 IDE_IORDY0

AD26 IDE_DREQ0

AE1 NC

AE2 NC

AE3 CLK_32K

AE4 KBROMCS#

AE5 IRQ9

AE6 SA1/SD1 SD1

Pin

No.

Signal Name

Limited

ISA Mode

ISA Master

Mode

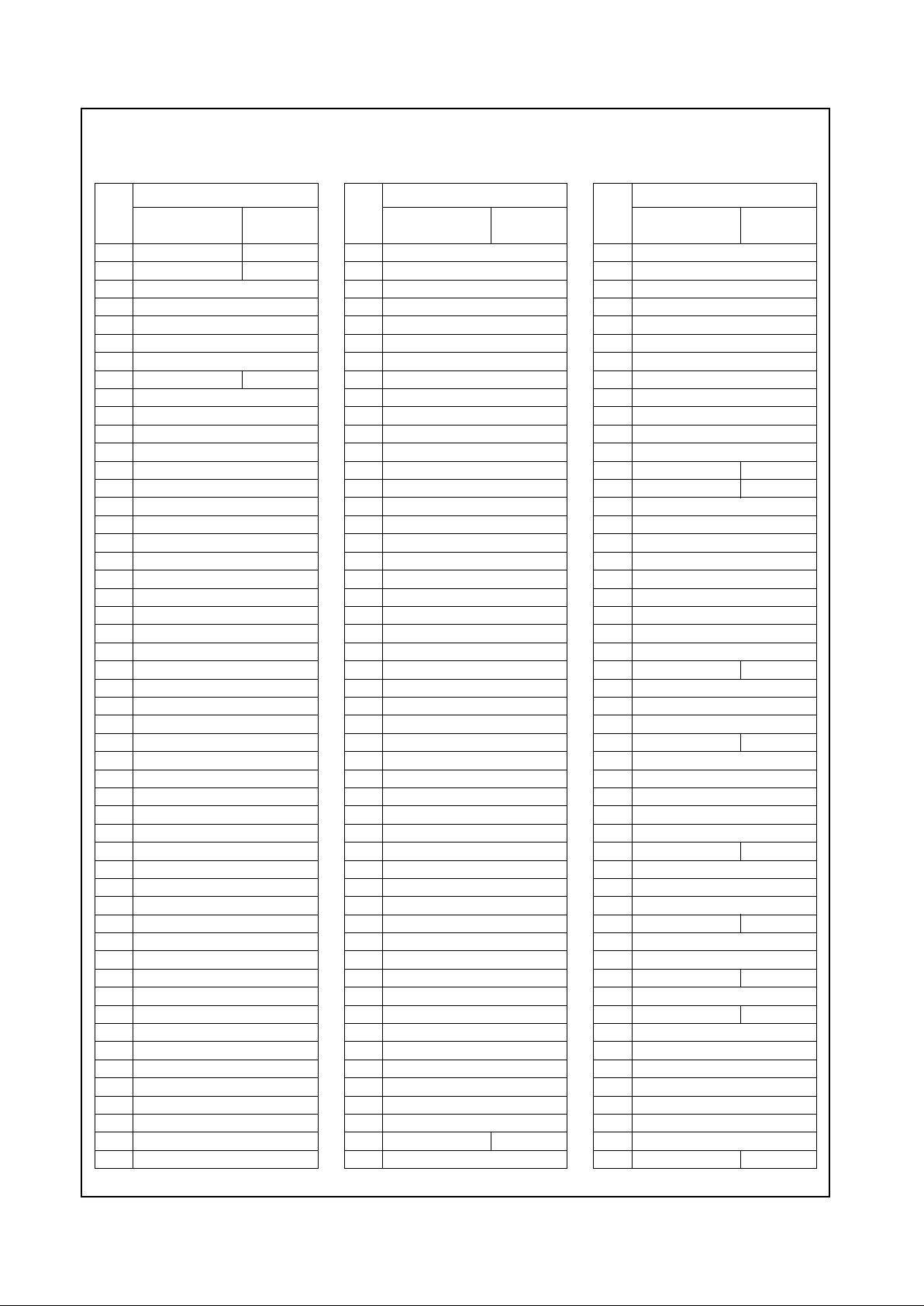

Table 2-2. 352 TBGA Pin Assignments - Sorted by Pin Number (Continued)

Revision 4.1 17 www.national.com

Signal Definitions (Continued)

Geode™ CS5530

AE7 DACK5#

AE8 AEN

AE9 SA0/SD0 SD0

AE10 DRQ2

AE11 SA18

AE12 IOR#

AE13 IRQ5

AE14 IRQ8#

AE15 IRQ4

AE16 IRQ10

AE17 SBHE#

AE18 DRQ0

AE19 MEMR#

AE20 DRQ6

AE21 SA12/SD12 SD12

AE22 SA13/SD13 SD13

Pin

No.

Signal Name

Limited

ISA Mode

ISA Master

Mode

AE23 GPIO6/SA22 SD22

AE24 GPIO1/SDATA_IN2

AE25 SA15/SD15 SD15

AE26 IDE_IORDY1

AF1 NC

AF2 NC

AF3 SMEMW#/RTCCS#

AF4 SA7/SD7 SD7

AF5 SA6/SD6 SD6

AF6 SA4/SD4 SD4

AF7 DACK3#

AF8 DACK2#

AF9 BALE

AF10 ZEROWS#

AF11 IOCHRDY

AF12 SA17

Pin

No.

Signal Name

Limited

ISA Mode

ISA Master

Mode

AF13 IRQ1

AF14 IRQ6

AF15 TC

AF16 IOCS16#

AF17 IRQ12

AF18 IRQ11

AF19 SA8/SD8 SD8

AF20 MEMW#

AF21 SA11/SD11 SD11

AF22 DRQ7

AF23 GPIO7/SA23 SA23

AF24 GPIO3

AF25 GPIO2

AF26 GPCS#

Pin

No.

Signal Name

Limited

ISA Mode

ISA Master

Mode

Table 2-2. 352 TBGA Pin Assignments - Sorted by Pin Number (Continued)

www.national.com 18 Revision 4.1

Signal Definitions (Continued)

Geode™ CS5530

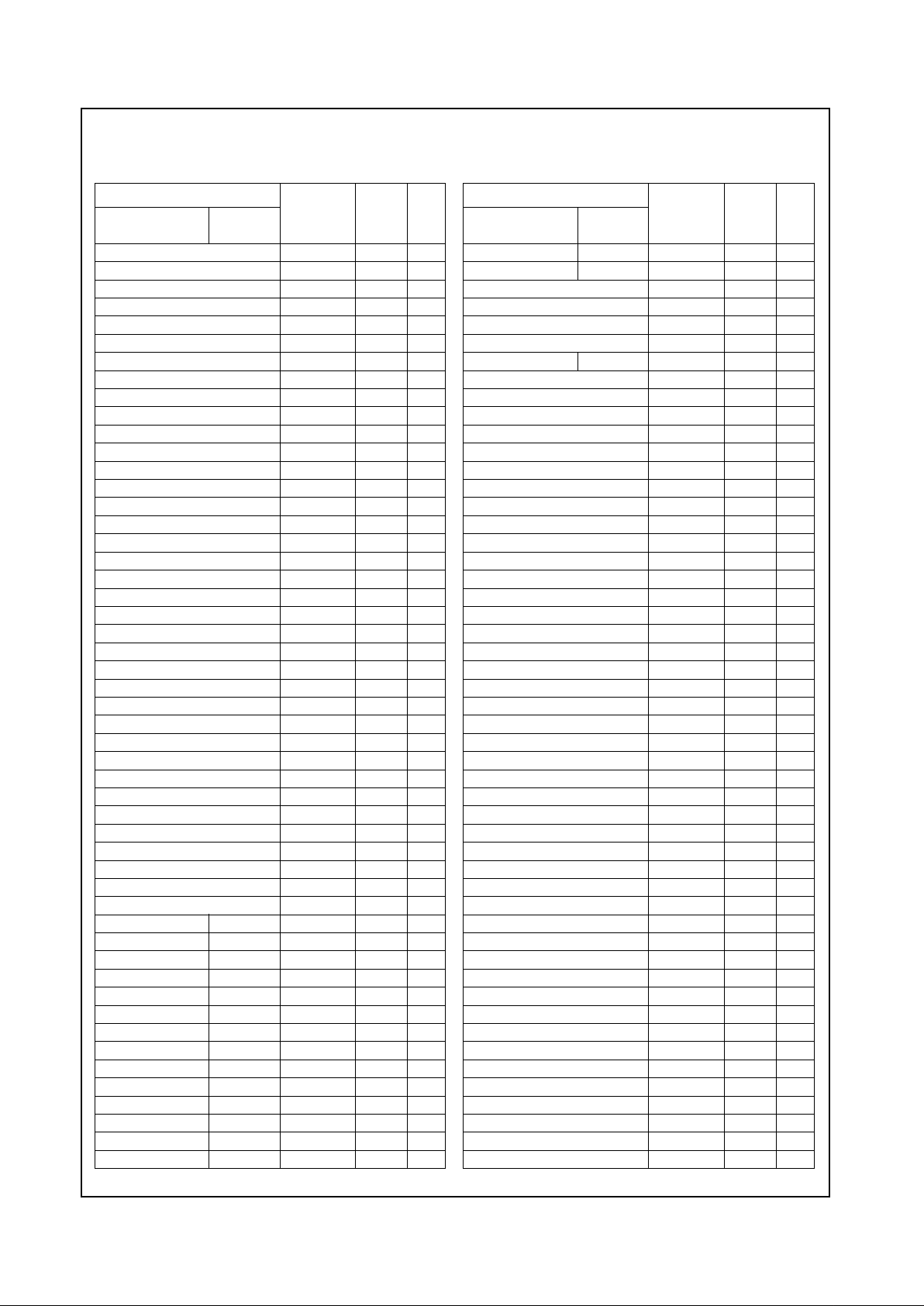

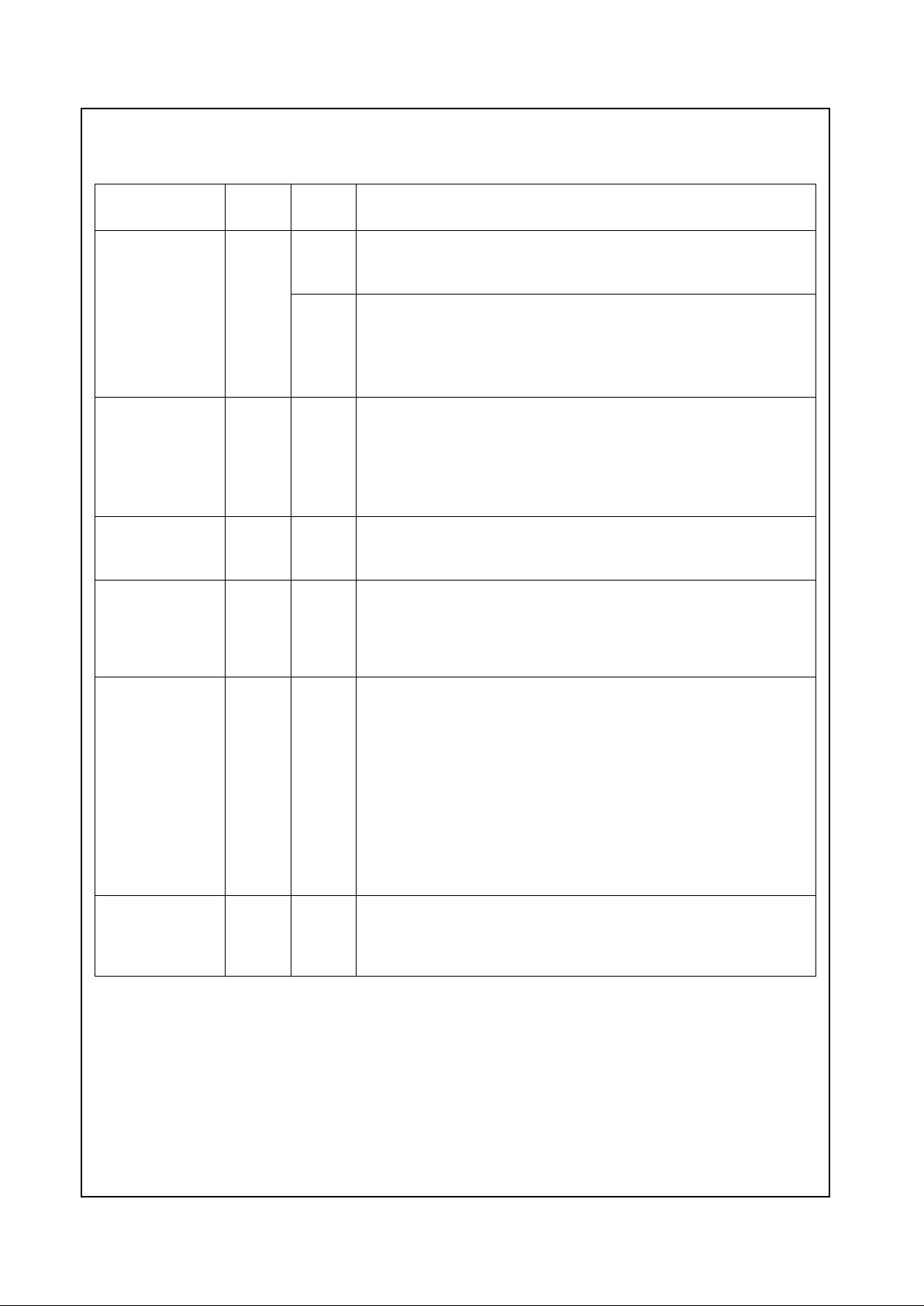

Table 2-3. 352 TBGA Pin Assignments - Sorted Alphabetically by S ignal Name

Signal Name

Pin Type

(Note 1)

Buffer

Type

(Note 2)

Pin

No.

Limited ISA

Mode

ISA Master

Mode

AD0

I/O, t/s, 5VT PCI A15

AD1 I/O, t/s, 5VT PCI D14

AD2 I/O, t/s, 5VT PCI C16

AD3 I/O, t/s, 5VT PCI B15

AD4 I/O, t/s, 5VT PCI C17

AD5 I/O, t/s, 5VT PCI B16

AD6 I/O, t/s, 5VT PCI B17

AD7 I/O, t/s, 5VT PCI A16

AD8 I/O, t/s, 5VT PCI D18

AD9 I/O, t/s, 5VT PCI A17

AD10 I/O, t/s, 5VT PCI A19

AD11 I/O, t/s, 5VT PCI B19

AD12 I/O, t/s, 5VT PCI A18

AD13 I/O, t/s, 5VT PCI C20

AD14 I/O, t/s, 5VT PCI B20

AD15 I/O, t/s, 5VT PCI A20

AD16 I/O, t/s, 5VT PCI A26

AD17 I/O, t/s, 5VT PCI A25

AD18 I/O, t/s, 5VT PCI B25

AD19 I/O, t/s, 5VT PCI B26

AD20 I/O, t/s, 5VT PCI E24

AD21 I/O, t/s, 5VT PCI C25

AD22 I/O, t/s, 5VT PCI C26

AD23 I/O, t/s, 5VT PCI E25

AD24 I/O, t/s, 5VT PCI F25

AD25 I/O, t/s, 5VT PCI G24

AD26 I/O, t/s, 5VT PCI D25

AD27 I/O, t/s, 5VT PCI F26

AD28 I/O, t/s, 5VT PCI G25

AD29 I/O, t/s, 5VT PCI G26

AD30 I/O, t/s, 5VT PCI J24

AD31 I/O, t/s, 5VT PCI H25

AEN O 8mA AE8

AVDD1(DAC) I, Analog -- U1

AVDD2(VREF) I, Analog -- T3

AVDD3(DAC) I, Analog -- N4

AVSS1 (DAC) I, Analog -- R2

AVSS2 (ICAP) I,Analog -- R4

AVSS3(VREF) I, Analog -- T4

AVSS4 (ICAP) I,Analog -- P1

AVSS5 (DAC) I, Analog -- P2

BALE O8mAAF9

BIT_CLK I, 5VT IBUF V2

C/BE0# I/O, t/s, 5VT PCI B18

C/BE1# I/O, t/s, 5VT PCI B21

C/BE2# I/O, t/s, 5VT PCI A24

C/BE3# I/O, t/s, 5VT PCI D26

CLK_14MHZ IsmtP24

CLK_32K I/O, 5VT 4 mA AE3

CPU_RST O8mAK25

DACK0# O8mAAD8

DACK1# O8mAAC8

DACK2# O8mAAF8

DACK3# O8mAAF7

DACK5# O 8 mA AE7

DACK6# O8mAAD7

DACK7# O8mAAC7

DCLK O8mAA10

DDC_SCL O 8 mA M2

DDC_SDA I/O, 5VT 8mA M4

DEVSEL# I/O, t/s, 5VT PCI A23

D–_PORT1 I/O USB Y1

D+_PORT1 I/O USB Y2

D–_PORT2 I/O USB AA1

D+_PORT2 I/O USB AA2

DRQ0 I, 5VT IBUF AE18

DRQ1 I, 5VT IBUF AD12

DRQ2 I, 5VT IBUF AE10

DRQ3 I, 5VT IBUF AD13

DRQ5 I, 5VT IBUF AD18

DRQ6 I, 5VT IBUF AE20

DRQ7 I, 5VT IBUF AF22

ENA_DISP IIBUFB1

EXTVREFIN I, Analog -- T2

FP_CLK No Function O 8 mA M1

FP_CLK_EVEN No Function O8mAL3

FP_DA TA0 SA0 I/O 8 mA K3

FP_DA TA1 SA1 I/O 8 mA J2

FP_DA TA2 SA2 I/O 8 mA J3

FP_DA TA3 SA3 I/O 8 mA J1

FP_DA TA4 SA4 I/O 8 mA H1

FP_DA TA5 SA5 I/O 8 mA G2

FP_DA TA6 SA6 I/O 8 mA G4

FP_DA TA7 SA7 I/O 8 mA G3

FP_DA TA8 SA8 I/O 8 mA G1

FP_DA TA9 SA9 I/O 8 mA F1

FP_DATA10 SA10 I/O 8 mA E2

FP_DATA11 SA11 I/O 8 mA D1

FP_DATA12 SA12 I/O 8 mA L1

FP_DATA13 SA13 I/O 8 mA K2

FP_DATA14 SA14 I/O 8 mA K1

FP_DATA15 SA15 I/O 8 mA H2

FP_DATA16 SA_OE# O8mAH3

FP_DATA17 MASTER# I/O 8 mA F3

FP_DISP_ENA_OUT No Function O8mAF2

FP_ENA_BKL No Function O8mAJ4

FP_ENA_VDD No Function O8mAL2

FP_HSYNC No Function IIBUFC2

FP_HSYNC_OUT SMEMW# O8mAE1

FP_VSYNC No Function IIBUFC1

FP_VSYNC_OUT SMEMR# O8mAE3

FRAME# I/O, t/s, 5VT PCI C23

Signal Name

Pin Type

(Note 1)

Buffer

Type

(Note 2)

Pin

No.

Limited ISA

Mode

ISA Master

Mode

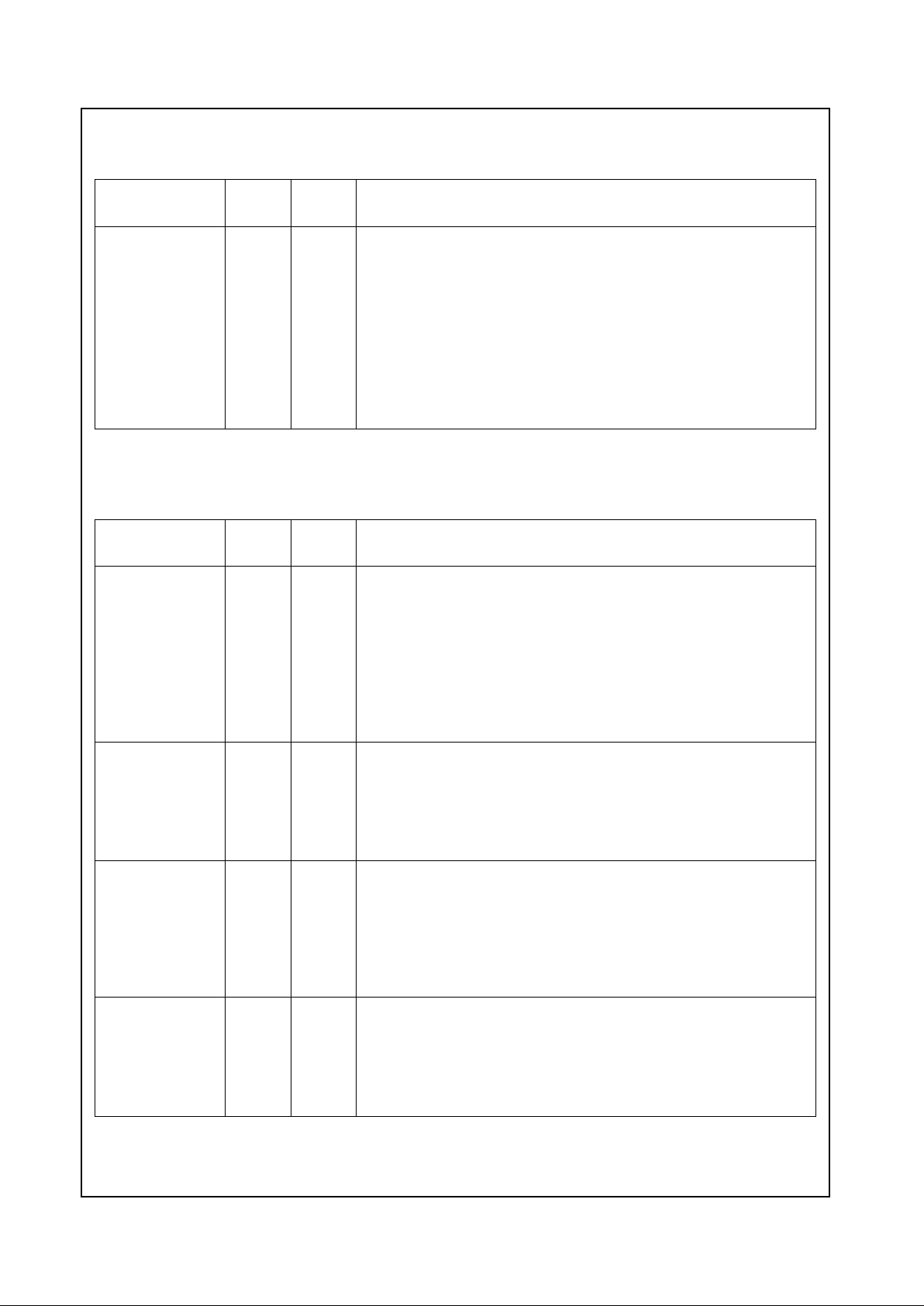

Revision 4.1 19 www.national.com

Signal Definitions (Continued)

Geode™ CS5530

GNT# I, 5VT PCI D24

GPCS# O4mAAF26

GPIO0 I/O, 5VT 8 mA AC22

GPIO1/SDATA_IN2 I/O, 5VT 8 mA AE24

GPIO2 I/O, 5VT 8 mA AF25

GPIO3 I/O, 5VT 8 mA AF24

GPIO4/SA20 SA20 I/O, 5VT 8 mA AD22

GPIO5/SA21 SA21 I/O, 5VT 8 mA AC21

GPIO6/SA22 SA22 I/O, 5VT 8 mA AE23

GPIO7/SA23 SA23 I/O, 5VT 8 mA AF23

GPORT_CS# O8mAAD21

HOLD_REQ# (strap pin) I/O, 5VT PCI H26

HSYNC IIBUFC6

HSYNC_OUT O16mAN1

IDE_ADDR0 O8mAU25

IDE_ADDR1 O8mAU26

IDE_ADDR2 O8mAW24

IDE_CS0# O8mAV26

IDE_CS1# O8mAY26

IDE_DACK0# O8mAT26

IDE_DACK1# O8mAT24

IDE_DATA0 I/O, 5VT 8 mA AC26

IDE_DATA1 I/O, 5VT 8 mA AA24

IDE_DATA2 I/O, 5VT 8 mA AB24

IDE_DATA3 I/O, 5VT 8 mA AB26

IDE_DATA4 I/O, 5VT 8 mA AA26

IDE_DATA5 I/O, 5VT 8 mA W26

IDE_DATA6 I/O, 5VT 8 mA U24

IDE_DATA7 I/O, 5VT 8 mA U23

IDE_DATA8 I/O, 5VT 8 mA V24

IDE_DATA9 I/O, 5VT 8 mA Y25

IDE_DATA10 I/O, 5VT 8 mA V25

IDE_DATA11 I/O, 5VT 8 mA Y24

IDE_DATA12 I/O, 5VT 8 mA AA25

IDE_DATA13 I/O, 5VT 8 mA AB25

IDE_DATA14 I/O, 5VT 8 mA AC25

IDE_DATA15 I/O, 5VT 8 mA AB23

IDE_DREQ0 I, 5VT IBUF AD26

IDE_DREQ1 I, 5VT IBUF AC24

IDE_IOR0# O8mAR26

IDE_IOR1# O8mAR25

IDE_IORDY0 I, 5VT IBUF AD25

IDE_IORDY1 I, 5VT IBUF AE26

IDE_IOW0# O8mAR24

IDE_IOW1# O8mAT25

IDE_RST# O8mAW25

INTA# I, 5VT IBUF A14

INTB# I,5VT IBUF D15

INTC# I, 5VT IBUF C15

INTD# I, 5VT IBUF B14

INTR (strap pin) I/O 4 mA P26

Signal Name

Pin Type

(Note 1)

Buffer

Type

(Note 2)

Pin

No.

Limited ISA

Mode

ISA Master

Mode

IOCHRDY I/O, OD, 5VT 8 mA AF11

IOCS16# I, 5VT IBUF AF16

IOR# I/O (PU), 5VT 8 mA AE12

IOUTB O,Analog R1

IOUTR O , Analog P3

IOUTG O, Analog P4

IOW# I/O (PU), 5VT 8 mA AC11

IRDY# I/O, t/s, 5VT PCI B24

IREF I, Analog R3

IRQ1 I, 5VT IBUF AF13

IRQ3 I, 5VT IBUF AC14

IRQ4 I, 5VT IBUF AE15

IRQ5 I, 5VT IBUF AE13

IRQ6 I, 5VT IBUF AF14

IRQ7 I, 5VT IBUF AD14

IRQ8# I, 5VT IBUF AE14

IRQ9 I, 5VT IBUF AE5

IRQ10 I, 5VT IBUF AE16

IRQ11 I, 5VT IBUF AF18

IRQ12 I, 5VT IBUF AF17

IRQ13 I, 5VT IBUF R23

IRQ14 I, 5VT IBUF AC17

IRQ15 I, 5VT IBUF AD17

ISACLK O16mAAD6

KBROMCS# O 4 mA AE4

LOCK# I/O, t/s, 5VT PCI C22

MEMCS16# I/O, OD, 5VT 8 mA AC15

MEMR# I/O (PU), 5VT 8 mA AE19

MEMW# I/O (PU), 5VT 8 mA AF20

NC -- -- AA3

NC -- -- AB1

NC -- -- AB2

NC -- -- AB3

NC -- -- AC1

NC -- -- AC2

NC -- -- AC3

NC -- -- AD1

NC -- -- AD2

NC -- -- AD3

NC -- -- AE1

NC -- -- AE2

NC -- -- AF1

NC -- -- AF2

NC -- -- D2

NC -- -- W2

NC -- -- Y3

OVER_CUR# I, 5VT IBUF W3

PAR I/O, t/s, 5VT PCI A21

PC_BEEP O4mAV3

PCICLK IsmtJ26

PCI_RST# O16mAC14

Signal Name

Pin Type

(Note 1)

Buffer

Type

(Note 2)

Pin

No.

Limited ISA

Mode

ISA Master

Mode

Table 2-3. 352 TBGA Pin Assignments - Sorted Alphabetically by Signal Name (Continued)

www.national.com 20 Revision 4.1

Signal Definitions (Continued)

Geode™ CS5530

PCLK IsmtA13

PERR# I/O, t/s, 5VT PCI B22

PIXEL0 IIBUFA1

PIXEL1 IIBUFA2

PIXEL2 IIBUFA3

PIXEL3 IIBUFC4

PIXEL4 IIBUFB3

PIXEL5 IIBUFB4

PIXEL6 IIBUFD5

PIXEL7 IIBUFA4

PIXEL8 IIBUFB6

PIXEL9 IIBUFD6

PIXEL10 IIBUFA5

PIXEL11 IIBUFC5

PIXEL12 IIBUFA7

PIXEL13 IIBUFD7

PIXEL14 IIBUFC7

PIXEL15 IIBUFB8

PIXEL16 IIBUFA8

PIXEL17 IIBUFC8

PIXEL18 IIBUFB9

PIXEL19 IIBUFA9

PIXEL20 IIBUFD9

PIXEL21 IIBUFC9

PIXEL22 IIBUFB11

PIXEL23 IIBUFC10

PLLAGD I, Analog -- N25

PLLAGS I, Analog -- N24

PLLDGN I,Analog -- N26

PLLDVD I, Analog -- M23

PLLLP I, Analog -- N23

PLLRO I,Analog -- M26

PLLVAA I,Analog -- M25

POR# IIBUFK24

POWER_EN O4mAV4

PSERIAL IIBUFL26

REQ# O,5VT PCI J25

SA0/SD0 SD0 I/O (PU), 5VT 8 mA AE9

SA1/SD1 SD1 I/O (PU), 5VT 8 mA AE6

SA2/SD2 SD2 I/O (PU), 5VT 8 mA AD9

SA3/SD3 SD3 I/O (PU), 5VT 8 mA AC6

SA4/SD4 SD4 I/O (PU), 5VT 8 mA AF6

SA5/SD5 SD5 I/O (PU), 5VT 8 mA AD5

SA6/SD6 SD6 I/O (PU), 5VT 8 mA AF5

SA7/SD7 SD7 I/O (PU), 5VT 8 mA AF4

SA8/SD8 SD8 I/O (PU), 5VT 8 mA AF19

SA9/SD9 SD9 I/O (PU), 5VT 8 mA AD19

SA10/SD10 SD10 I/O (PU), 5VT 8 mA AC20

SA11/SD11 SD11 I/O (PU), 5VT 8 mA AF21

SA12/SD12 SD12 I/O (PU), 5VT 8 mA AE21

SA13/SD13 SD13 I/O (PU), 5VT 8 mA AE22

Signal Name

Pin Type

(Note 1)

Buffer

Type

(Note 2)

Pin

No.

Limited ISA

Mode

ISA Master

Mode

SA14/SD14 SD14 I/O (PU), 5VT 8 mA AD24

SA15/SD15 SD15 I/O (PU), 5VT 8 mA AE25

SA16 I/O (PU), 5VT 8 mA AD11

SA17 I/O (PU), 5VT 8 mA AF12

SA18 I/O (PU), 5 VT 8 mA AE11

SA19 I/O (PU), 5VT 8 mA AD10

SA_LATCH SA_DIR O4mAAD15

SBHE# I/O (PU), 5VT 8 mA AE17

SDAT A_IN I, 5VT IBUF U4

SDAT A_OUT O4mAV1

SERR# I/O, OD, 5VT PCI A22

SMEMR#/RTCALE O4mAAD4

SMEMW#/RTCCS# O4mAAF3

SMI# I/O 4 mA P25

STOP# I/O, t/s, 5VT PCI E26

SUSP# O4mAK26

SUSPA# IIBUFL25

SUSP_3V I/O 4 mA L24

SYNC O4mAU3

TC O8mAAF15

TEST IIBUFD3

TRDY# I/O, t/s, 5VT PCI B23

TVCLK I,5VT 4 mA B2

USBCLK IsmtW1

VDD PWR -- D10

VDD PWR -- D17

VDD PWR -- AB4

VDD PWR -- AC10

VDD PWR -- AC19

VDD PWR -- AD16

VDD PWR -- AD23

VDD PWR -- C19

VDD PWR -- C24

VDD PWR -- C3

VDD PWR -- D21

VDD PWR -- F24

VDD PWR -- F4

VDD PWR -- H24

VDD PWR -- L23

VDD PWR -- L4

VDD PWR -- T23

VDD PWR -- U2

VDD PWR -- Y23

VID_CLK IsmtA6

VID_DATA0 IIBUFA11

VID_DATA1 IIBUFC13

VID_DATA2 IIBUFB13

VID_DATA3 IIBUFC11

VID_DATA4 IIBUFD11

VID_DATA5 IIBUFA12

VID_DATA6 IIBUFB12

Signal Name

Pin Type

(Note 1)

Buffer

Type

(Note 2)

Pin

No.

Limited ISA

Mode

ISA Master

Mode

Table 2-3. 352 TBGA Pin Assignments - Sorted Alphabetically by Signal Name (Continued)

Revision 4.1 21 www.national.com

Signal Definitions (Continued)

Geode™ CS5530

Notes: 1) S ee Table 2-1 on page13 for pin type definitions.

2) See Table5-6 "DC Character istics (at Recommended

Operating Conditions)" on page 228 for more information. IBUF refers to input buffer.

VID_DATA7 IIBUFC12

VID_RDY O8mAB10

VID_VAL IIBUFB7

VREF I, Analog -- T1

VSS GND -- D12

VSS GND -- D13

VSS GND -- D16

VSS GND -- AA23

VSS GND -- AA4

VSS GND -- AC12

VSS GND -- AC13

VSS GND -- AC16

VSS GND -- AC18

VSS GND -- AC23

VSS GND -- AC4

VSS GND -- AC5

VSS GND -- AC9

VSS GND -- AD20

VSS GND -- C18

VSS GND -- C21

VSS GND -- D19

VSS GND -- D20

VSS GND -- D22

VSS GND -- D23

VSS GND -- D4

VSS GND -- D8

VSS GND -- E23

VSS GND -- E4

VSS GND -- F23

VSS GND -- G23

Signal Name

Pin Type

(Note 1)

Buffer

Type

(Note 2)

Pin

No.

Limited ISA

Mode

ISA Master

Mode

VSS GND -- H23

VSS GND -- H4

VSS GND -- J23

VSS GND -- K23

VSS GND -- K4

VSS GND -- M24

VSS GND -- M3

VSS GND -- N3

VSS GND -- P23

VSS GND -- V23

VSS GND -- W23

VSS GND -- W4

VSS GND -- Y4

VSYNC IIBUFB5

VSYNC_OUT O16mAN2

ZEROWS# I, 5VT IBUF AF10

Signal Name

Pin Type

(Note 1)

Buffer

Type

(Note 2)

Pin

No.

Limited ISA

Mode

ISA Master

Mode

Table 2-3. 352 TBGA Pin Assignments - Sorted Alphabetically by Signal Name (Continued)

www.national.com 22 Revision 4.1

Signal Definitions (Continued)

Geode™ CS5530

2.2 SIGNAL DESCRIPTIONS

2.2.1 Reset Interface

Signal Name

Pin

No. Type Description

PCI_RST# C14 O PCI Reset

PCI_RST# resets the PCI bus and is asserted while POR# is asserted,

and for approximately 9 ms following the deassertion of POR#.

POR# K24 I

smt

Power On Reset

POR# is the system reset signal generated from the power supply to indicate that the system should be reset.

CPU_RST K25 O CPU Reset

CPU_RST resets the CPU and is asserted while POR# is asserted, and

for approximately 9 ms following the deassertion of POR#.

2.2.2 Clock Interface

Signal Name

Pin

No. Type Description

PCICLK J26 I PCI Clock

The PCI clock is used to drivemost circuitry of the C S5530.

TVCLK B2 I

5VT

Television Clock

The TVCLK is an input from a digital NTSC/PAL converter which is optionally re-driven back out onto the DCLK signal under software program control. This is only used if interfacing to a compatible digital NTSC/PAL

encoder device.

DCLK A10 O DOT Clock

DOT clock is generated by the CS5530 and typically connects to the processor to create the video pixel clock. The minimum frequency of DCLK is

10 MHz and the maximumis 200 MHz.

ISACLK AD6 O ISA Bus Clock

ISACLK is derivedfrom PCICLK and is typically programmed for approximately 8 MHz. F0 Index 50h[2:0] is used to program the ISA clock divisor.

CLK_14MHZ P24 I 14.31818 MHz Clock

DOT clock (DCLK) is derivedfrom this clock.

USBCLK W1 I USBCLK

This input is used as the clocksource for the USB. In this mode,a 48 MHz

clock source input is required.

CLK_32K AE3 I/O

5VT

32KHz Clock

CLK_32K is a 32.768 KHz clock used to generatereset signals,as well as

to maintain power management functionality. It shouldbe active when

power is applied to the CS5530.

CLK_32K can be an inputor an output. As an output CLK_32Kis internally derived from CLK_14MHZ. F0 Index 44h[5:4] are usedto program

this pin.

Revision 4.1 23 www.national.com

Signal Definitions (Continued)

Geode™ CS5530

2.2.3 CPU Interface

Signal Name

Pin

No. Type Description

INTR P26

Strap

Option

Pin

O CPU Interrupt Request

INTR is the level output from the integrated 8259 PICs and is asserted if

an unmasked interrupt request (IRQ

n

) is sampled active.

I StrapOptionSelectPin

Pin P26 is a strap option select pin.It is used to select whether the

CS5530 operates in Limited ISA or ISA Master mode.

ISA Limited Mode—Strap pin P26 low through a 10-kohm resistor.

ISA Master Mode—Strap pin P26 high through a 10-kohm resistor.

SMI# P25 I/O System Management Interrupt

SMI# is a level-sensitive interrupt to the CPU thatcan be configured to

assert on a number of different system events. After an SMI# assertion,

System Management Mode (SMM) is entered, and program execution

begins at the base of SMM address space.

Once asserted, SMI# remains active until all SMI sourcesare cleared.

IRQ13 R23 I

5VT

IRQ13

IRQ13 is an input from the processor indicating that a floating point error

was detected and that INTR should be asser ted.

PSERIAL L26 I Power Management Serial Interface

PSERIAL is the unidirectional serial data link between the GXLV processor and the CS5530. An 8-bit serialdata packet carries status on power

management events within the CPU. Data is clocked synchronous to the

PCICLK input clock.

SUSP# K26 O CPU Suspend

SUSP# asserted requests that the processor enter Suspend mode and

assert SUSPA#after completion. The SUSP# pin is deasserted after

detecting any Speedup or Resume event. If the SUSP#/SUSPA#handshake is configured as a system 3 Volt Suspend, the deassertion of

SUSP# is delayedto allow the system clock chip and the processor to stabilize.

The SUSP#/SUSPA# handshake occurs as a resultof a write to the Suspend Notebook CommandRegister (F0 Index AFh), or an expirationof the

Suspend Modulation OFF Count Register (F0 Index 94h) when Suspend

Modulation is enabled. Suspend Modulation is enabled via F0 Index

96h[0].

SUSPA# L25 I CPU Suspend Acknowledge

SUSPA# is a levelinput from the processor. When asserted it indicates

the CPU is in Suspend mode as aresult of SUSP# assertion or execution

of a HALT instruction.

www.national.com 24 Revision 4.1

Signal Definitions (Continued)

Geode™ CS5530

SUSP_3V L24 I/O Suspend 3 Volt Active

SUSP_3V can be connected to the output enable (OE) of a clock synthesis or buffer chip to stop the clocks to the system. SUSP_3V is asserted

on any write to SuspendNotebook Command Register (F0 Index AFh)

with bit 0 set in the Clock Stop Control Register (F0 Index BCh).

SUSP_3V is only asserted after the SUSP#/SUSPA# handshake.

As an input, SUSP_3V is sampled during power-on-resetto determine the

inactivestate. This allows the system designer to match the active state of

SUSP_3V to the inactive state for a clock driver output enabled with a pullup/down 10-kohm resistor. If pulled down, SUSP_3V is active high. If

pulled up, SUSP_3V is active low.

2.2.3 CPU Interface (Continued)

Signal Name

Pin

No. Type Description

2.2.4 PCI Interface

Signal Name

Pin

No. Type Description

AD[31:0] Refer

toTable

2-3

I/O

t/s

5VT

PCI Address/Data

AD[31:0] is a physical address during the first clock of a PCI transaction; it

is the data during subsequent clocks.

When the CS5530 is a PCI master, AD[31:0] are outputs during the

addressand write data phases, and are inputs during the read data phase

of a transaction.

When the CS5530 is a PCI slave, AD[31:0] are inputs during the address

and write data phases, and are outputs during the read data phase of a

transaction.

C/BE[3:0]# D26,

A24,

B21,

B18

I/O

t/s

5VT

PCI Bus Command and Byte Enables

During the address phase of a PCI transaction, C/BE[3:0]# defines the

bus command. During the data phase of a transaction, C/BE[3:0]# are the

data byte enables.

C/BE[3:0]# are outputs when the CS5530 is a PCI master and are inputs

when it is a PCI slave.

INTA#,

INTB#,

INTC#,

INTD#

A14,

D15,

C15,

B14

I

5VT

PCI Interrupt Pins

The CS5530 provides inputs for the optional “level-sensitive” PCI interrupts (also known in industry terms as PIRQx#). These interrupts may be

mapped to IRQs of the internal 8259s usingPCI Interrupt Steering Registers 1 and 2 (F0 Index 5Ch and 5Dh).

The USB controller uses INTA#as its output signal. Refer to PCIUSB

Index 3Dh.

REQ# J25 O

5VT

PCI Bus Request

The CS5530 asserts REQ# in response to a DMA request or ISA master

request to gain ownership of the PCI bus. The REQ#and GNT# signals

areusedtoarbitrateforthePCIbus.

REQ# should connect to the REQ0# of the GXLVprocessor and function

as the highest-priority PCI master.

Revision 4.1 25 www.national.com

Signal Definitions (Continued)

Geode™ CS5530

GNT# D24 I

5VT

PCI Bus Grant

GNT# is asserted by an arbiter that indicates to the CS5530 thataccess

to the PCI bus has been granted.

GNT# should connect to GNT0# of the GXLV processor and function as

the highest-priority PCI master.

HOLD_REQ# H26

Strap

Option

Pin

O PCI Bus Hold Request

This pin’s function as HOLD_REQ# is no longer applicable.

I

5VT

StrapOptionSelectPin

Pin H26 is a strap option select pin. It allows selection of whichaddress

bitsareusedastheIDSEL.

Strap pin H26 low: IDSEL = AD28 (Chipset Register Space) and AD29

(USB Register Space)

Strap pin H26 high: IDSEL= AD26 (Chipset Register Space) and AD27

(USB Register Space)

FRAME# C23 I/O

t/s

5VT

PCI Cycle Frame

FRAME# is asserted to indicate the start and duration of a transaction. It

is deasserted on the final data phase.

FRAME# is an input when the CS5530is a PCI slave.

IRDY# B24 I/O

t/s

5VT

PCI Initiator Ready

IRDY# is driven by the master to indicate valid data on a write transaction,

or that it is ready to receive data on a read transaction.

When the CS5530 is a PCI slave, IRDY# is an input thatcan delay the

beginning of a write transaction or the completion of a read transaction.

Waitcycles are inserted until both IRDY#and TRDY# are asserted

together.

TRDY# B23 I/O

t/s

5VT

PCI Target Ready

TRDY# is asserted by a PCI slave to indicate it is ready to complete the

current data transfer.

TRDY# is an input that indicates a PCI slave has driven valid data on a

read or a PCI slave is ready to accept data fromthe CS5530 on a write.

TRDY# is an output that indicates theCS5530 has placed valid data on

AD[31:0] during a read or is ready to acceptthe data from a PCI master

on a write.

Waitcycles are inserted until both IRDY#and TRDY# are asserted

together.

STOP# E26 I/O

t/s

5VT

PCI Stop

As an input, STOP# indicates that a PCI slavewants to terminate the current transfer. The transfer will either be aborted or retried. STOP# is also

used to end a burst.

As an output, STOP# is asser ted with TRDY# to indicate a target disconnect, or without TRDY#to indicate a target retry. The CS5530 will assert

STOP#during any cache linecrossings if in singletransfer DMA mode or

if busy.

2.2.4 PCI Interface (Continued)

Signal Name

Pin

No. Type Description

www.national.com 26 Revision 4.1

Signal Definitions (Continued)

Geode™ CS5530

LOCK# C22 I/O

t/s

5VT

PCI Lock

LOCK# indicates an atomic operation that may require multiple transactions to complete.

If the CS5530 is currently the target of a LOCKed transaction, any other

PCI master request with the CS5530as the target is forced to retry the

transfer.

The CS5530 does not generate LOCKed transactions.

DEVSEL# A23 I/O

t/s

5VT

PCI Device Select

DEVSEL# is asserted by a PCI slave, to indicate to a PCI master and subtractivedecoder that it is the target of the current transaction.

As an input, DEVSEL# indicates a PCI slavehas responded to the current

address.

As an output, DEVSEL# is asserted one cycle after the assertion of

FRAME# and remains asserted to the end of atransaction as the result of

a positive decode. DEVSEL# is asserted four cycles after the assertion of

FRAME# if DEVSEL#has not been asserted by another PCI device when

the CS5530 is programmed to be the subtractive decode agent. The subtractivedecode sample point is configured in F0Index 41h[2:1]. Subtractive decode cycles are passedto the ISA bus.

PAR A21 I/O

t/s

5VT

PCI Parity

PAR is the parity signal driven to maintain even parity across AD[31:0]

and C/BE[3:0]#.

The CS5530 drives PARone clock after the address phase and one clock

after each completed data phase of write transactions as a PCI master. It

also drives PAR one clock after each completed data phaseof read transactions as a PCI slave.

PERR# B22 I/O

t/s

5VT

PCI Parity Error

PERR# is pulsed by a PCI device to indicate that a parity error was

detected.If a parity error was detected, PERR# is a sserted by a PCI slave

during a write data phase and by a PCI master during a read data phase.

When the CS5530 is a PCI master, PERR# is anoutput during read transfers and aninput during w rite transfers.When the CS5530 is aPCI slave,

PERR# is an input during read transfers and an output during write transfers.

Parity detection is enabled through F0 Index 04h[6]. An NMI is generated

if I/O Port 061h[2] is set. PERR# can assert SERR# if F0 Index 41h[5] is

set.

SERR# A22 I/O

OD

5VT

PCI System Error

SERR# is pulsed by a PCI device to indicatean address parity error, data

parity error on a specialcycle command, or other fatal system errors.

SERR# is an open-drain output reporting an error condition, and an input

indicating that the CS5530 should generate an NMI. As an input, SERR#

is asserted for a single clock by the slave reporting the error.

System error detection is enabled with F0 Index 04h[8]. An NMI is generated if I/O Port 061h[2]is set. PERR# can assert SERR# if F0 Index

41h[5] is set.

2.2.4 PCI Interface (Continued)

Signal Name

Pin

No. Type Description

Revision 4.1 27 www.national.com

Signal Definitions (Continued)

Geode™ CS5530

2.2.5 ISA B us Interface

Signal Name

Pin

No. Type Description

SA_LATCH/

SA_DIR

AD15 O Limited ISA Mode: System AddressLatch

This signal is used to latchthe destination address, which is multiplexed

on bits [15:0] of the SA/SD bus.

ISA Master Mode: System Address Direction

Controls the direction of the external 5.0V tolerant transceiver on bits

[15:0] of the SA bus. When low, the SA bus is drivenout. When high, the

SA bus is driven into the CS5530 by the external transceiver.

SA_OE#/

FP_DATA16

H3 O Limited ISA Mode: Flat Panel Data Port Line 16

Refer to Section 2.2.11 “Display Interface” on page 34 for this signal’s definition.

O ISA Master Mode: System Address Transceiver Output Enable

Enables the external transceiver on bits [15:0] of the SA bus.

MASTER#/

FP_DATA17

F3 O Limited ISA Mode: Flat Panel Data Port Line 17

Refer to Section 2.2.11 “Display Interface” on page 34 for this signal’s definition.

I ISA Master Mode: Master

The MASTER# input asserted indicates an ISA bus master is driving the

ISA bus.

SA23/GPIO7 AF23 I/O

5VT

Limited ISA Mode: System Address Bus Lines 23 through 20 or

General Purpose I/Os 7 through4

These pins can function either as the upper four bits of the SA busor as

general purpose I/Os. Programming is done through F0 Index43h, bits 6

and 2.

Refer to Section 2.2.9 “GamePort and General Purpose I/O Interface” on

page 32 for further detailswhen used as GPIOs.

SA22/GPIO6 AE23

SA21/GPIO5 AC21

SA20/GPIO4 AD22

ISA Master Mode: System AddressBus Lines 23 through 20

The pins function only as the four MSB (most significant bits) of the SA

bus.

SA[19:16] AD10,

AE11,

AF12,

AD11

I/O

PU

5VT

System Address Bus Lines 19 through 16

Refer to SA[15:0] signal description.

SA[15:0]/SD[15:0] Refer

to

Table

2-3

I/O

PU

5VT

Limited ISA Mode: System Address Bus / System Data Bus

This bus carries both the addresses and data for all ISA cycles. Initially,

the address is placed on the bus and then SA_LATCHis asserted for

externallatches to latch the address. At some time later,the data is put on

the bus, for a read,or the bus direction is changed to an input,for a write.

Pins designated as SA/SD[15:0] are internallyconnected to a 20-kohm

pull-up resistor.

ISA Master Mode: System Data Bus

These pins perform only as SD[15:0] and pins FP_DATA[15:0] take on the

functions of SA[15:0].

Pins designated as SA/SD[15:0] are internallyconnected to a 20-kohm

pull-up resistor.

www.national.com 28 Revision 4.1

Signal Definitions (Continued)

Geode™ CS5530

SMEMW#/

FP_HSYNC_OUT

E1 O Limited ISA Mode: Flat Panel Horizontal Sync Output

Refer to Section 2.2.11 “Display Interface” on page 34 for this signal’s definition.

Note that if Limited ISA Mode of operation is selected, SMEMW# is available on pin AF3 (multiplexed with RTCCS#).

ISA Master Mode: System Memory Write

SMEMW# is asserted for any memory write accesses below 1 MB. It

enables 8-bit memory slaves to decode the memory address on SA[19:0].

SMEMR#/

FP_VSYNC_OUT

E3 O Limited ISA Mode: Flat PanelVertical Sync Output

Refer to Section 2.2.11 “Display Interface” on page 34 for this signal’s definition.

Note that if Limited ISA Mode of operation is selected, SMEMR# is available on pin AD4 (multiplexedwith RTCALE).

ISA Master Mode: System M emory Read