NSC DS8911V Datasheet

DS8911/DS8913 AM/FM/TV Sound

Up-Conversion Frequency Synthesizer

General Description

The DS8911 is a digital Phase-Locked Loop (PLL) frequency synthesizer intended for use as a Local Oscillator (LO) in

electronically tuned radios. The device is used in conjunction with a serial data controller, a loop filter, some varactor

diodes and several passive elements to provide the local

oscillator function for both AM and FM tuning.

The conventional superheterodyne AM receiver utilizes a

low IF or down conversion tuning approach whereby the IF

is chosen to be below the frequencies to be received. The

DS8911 PLL on the other hand, utilizes an up-conversion

technique in the AM mode whereby the first IF frequency is

chosen to be well above the RF frequency range to be

tuned. This approach eliminates the need for tuned circuits

in the AM frontend since the image, half IF, and other spurious responses occur far beyond the range of frequencies to

be tuned. Sufficient selectivity and second IF image protection is provided by a crystal filter at the output of the first

mixer.

A significant cost savings can be realized utilizing this upconversion approach to tuning. Removal of the AM tuned

circuits eliminates the cost of expensive matched varactor

diodes and reduces the amount of labor required for alignment down from 6 adjustments to 2. Additional cost savings

are realized because up-conversion enables both the AM

and FM bands to be tuned using a single Voltage Controlled

Oscillator (VCO) operating between 98 and 120 MHz. (The

2 to 1 LO tuning range found in conventional AM down conversion radios is reduced to a 10% tuning range; 9.94 MHz

to 11.02 MHz).

Up-conversion AM tuning is accomplished by first dividing

the VCO signal down by a modulus 10 to obtain the LO

signal. This LO in turn is mixed on chip with the RF signal to

obtain a first IF at the MIXER output pins. This first IF after

crystal filtering is mixed (externally) with a reference frequency provided by the PLL to obtain a 450 kHz second IF

frequency. The DS8911 derives the 450 kHz second IF by

mixing an 11.55 MHz first IF with a 12.00 MHz reference

frequency.

FM and WB (weather band) tuning is done using the conventional down conversion approach. Here the VCO signal

is buffered to produce the LO signal and then mixed on chip

with the RF signal to obtain an IF frequency at the MIXER

output pins. This IF frequency is typically chosen to be 10.7

MHz although placement at 11.50 MHz can further enhance

AM mode performance and minimize IF circuitry.

The PLL provides phase comparator reference frequencies

of 10, 12.5, 25, and 100 kHz. The tuning resolutions resulting from these reference frequencies are determined by dividing the reference by the premix modulus. Table II shows

the tuning resolutions possible.

The DS8911 contains the following logic elements: a voltage controlled oscillator, a reference oscillator, a 14-bit programmable dual-modulus counter, a reference frequency divider chain, a premix divider, a mixer, a phase comparator, a

charge pump, an operational amplifier, and control circuitry

for latched serial data entry.

The DS8913 includes all the above logic elements except

that it requires a 10 MHz reference frequency instead of

12 MHz.

Features

Y

Direct synthesis of LW, MW, SW, FM, and WB

frequencies

Y

Serial data entry for simplified processor control

Y

10, 12.5, 25, and 100 kHz reference frequencies

Y

8 possible tuning resolutions (see Table II)

Y

An op amp with high impedance inputs for loop filtering

Y

Programmable mixer with high dynamic range

DS8911/DS8913 AM/FM/TV Sound Up-Conversion Frequency Synthesizer

April 1990

TRI-STATEÉis a registered trademark of National Semiconductor Corporation.

TM

MICROWIRE

C

1995 National Semiconductor Corporation RRD-B30M105/Printed in U. S. A.

is a trademark of National Semiconductor Corporation.

TL/F/7398

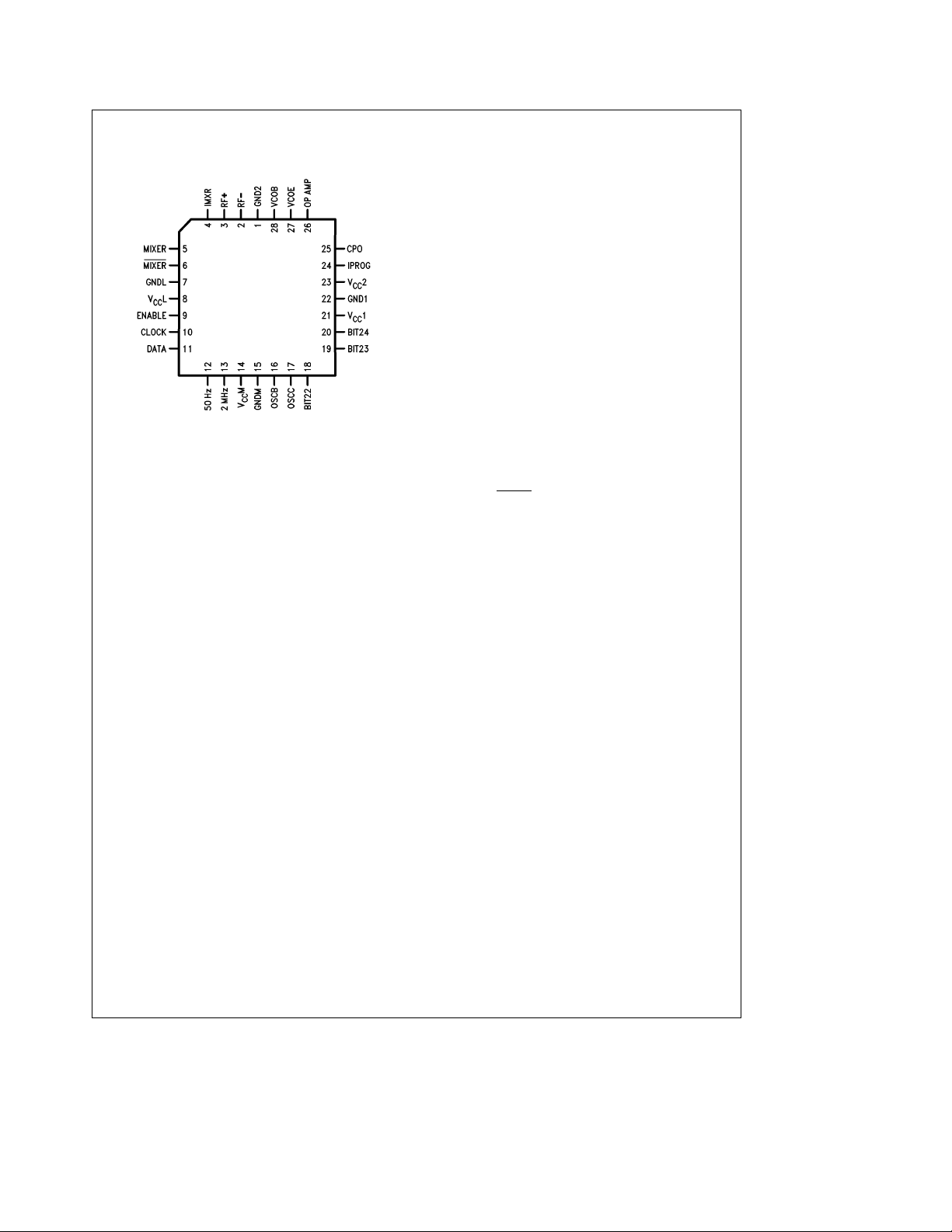

Connection Diagram

Plastic Chip Carrier

Top View

TL/F/7398– 8

Order Number DS8911V/DS8913V

See NS Package Number V28A

Pin Descriptions

V

: The V

CC1

circuitry except the reference divider chain, op amp and mixer sections of the die.

V

: The V

CC2

Op amp.

V

: The V

CCL

for the premix divider and mixer functions.

V

: The V

CCM

reference oscillator and divider chain down through the 50

Hz output, thus enabling low standby current for time-of-day

clock applications.

GND1, GND2, GNDL and GNDM: Provide isolated circuit

ground for the various sections of the device.

DATA and CLOCK: The DATA and CLOCK inputs are for

serial data entry from a controller. They are CMOS inputs

with TTL logic thresholds. The 24-bit data stream is loaded

into the PLL on the positive transition of the CLOCK. The

first 14 bits of the data stream select PLL divide code in

binary form MSB first. The 15th through 24th bits select the

premix modulus, the reference frequency, the bit output

status, and the test/operate modes as shown in Tables I

through V.

ENABLE: The ENABLE input is a CMOS input with a TTL

logic threshold. The ENABLE input enables data when at a

logic ‘‘one’’ and latches data on the transition to a logic

‘‘zero’’.

pin provides a 5V supply source for all

CC1

pin provides a 12V supply source for the

CC2

pin provides an isolated 5V supply source

CCL

pin provides a 5V supply source for the

CCM

BIT Outputs: The open-collector BIT outputs provide either

the status of shift register bits 22, 23, and 24 or enable

access to key internal circuit test nodes. The mode for the

bit outputs is controlled by shift register bits 20 and 21. In

operation, the bit outputs are intended to drive radio functions such as gain, mute, and AM/FM status. These outputs

can also be used to program the loop gain by connection of

an external resistor to IPROG. Bit 24 output can also be

used as a 300 millisecond timer under control of shift register bit 19. During service testing, these pins can be used for

the purpose of either monitoring or driving internal logic

points as indicated in the TEST MODES description under

Table V.

VCOb and VCOe: The Voltage Controlled Oscillator inputs

drive the 14-bit programmable counter and the premix divider. These inputs are the base and emitter leads of a transistor which require connection of a coil, varactor, and several

capacitors to function as a Colpitts oscillator. The VCO is

designed to operate up to 225 MHz. The VCO’s minimum

operating frequency may be limited by the choice of reference frequency and the 961 minimum modulus constraint of

the 31/32 dual modulus counter.

a

RF

and RFb: The Radio Frequency inputs are fed differ-

entially into the mixer.

IMXR: The bias current for the mixer is programmed by connection of an external resistor to this pin. The total mixer

output current equals 4 times the current entering this pin.

MIXER and MIXER

: The MIXER outputs are the collectors

of the double balanced pair mixer transistors. They are intended to operate at voltages greater than V

CC1

.

OSCb and OSCc: The Reference Oscillator inputs are part

of an on-chip Pierce oscillator designed to work in conjunction with 2 capacitors and a crystal resonator. The DS8911

requires a 12 MHz crystal to derive the reference frequencies shown in Table II. The DS8913 requires 10 MHz crystal.

The 12 MHz OSC signal is also used externally as the 2nd

AM LO to obtain a 450 kHz 2nd IF frequency in the AM

mode.

2 MHz: The 2 MHz output is provided to drive a controller’s

clock input.

50 Hz: The 50 Hz output is provided as a time reference for

radios with time-of-day clocks.

IPROG: The IPROG pin enables the charge pump to be

programmed from 0.25 mA to 1.0 mA by connection of an

external resistor to ground.

CPO: The Charge Pump Output circuit sources current if the

VCO frequency is high and sinks current if the VCO frequency is low. The CPO is wired directly to the negative input of

the loop filter op amp.

OP AMP: The OP AMP output is provided for loop filtering.

The op amp has high impedance PMOS gate inputs and is

wired as a transconductance amplifier/filter. The op amp’s

positive input is internally referenced while its negative input

is common with the CPO output.

2

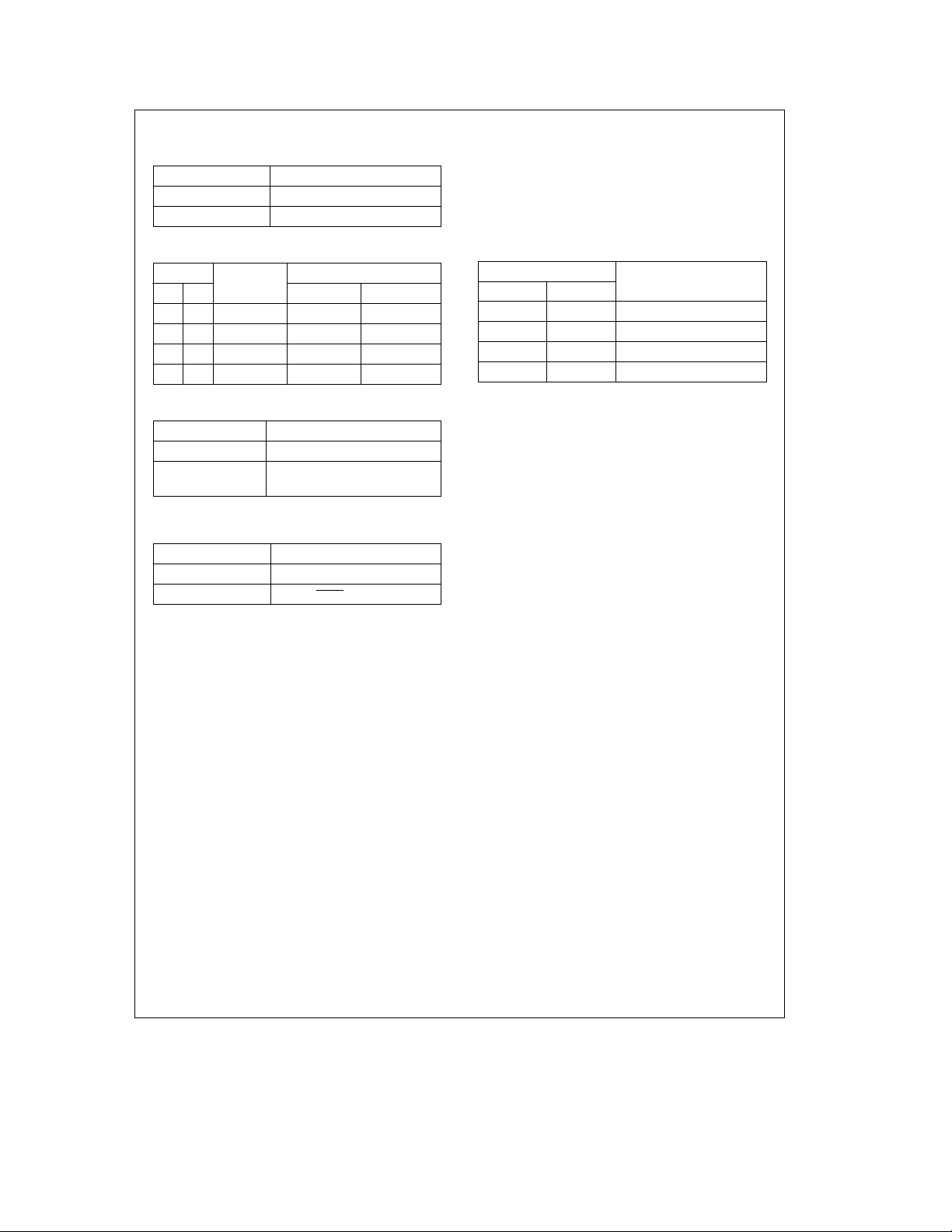

Reference Tables

TABLE I

Bit 15 Premix Modulus

0

1

TABLE II

Bit Reference Tuning Resolution

16 17

Frequency

d

0 0 10 kHz 10 kHz 1 kHz

0 1 12.5 kHz 12.5 kHz 1.25 kHz

1 0 25 kHz 25 kHz 2.5 kHz

1 1 100 kHz 100 kHz 10 kHz

TABLE III

Bit 18 Mode

0 Normal Operation*

1

*The user should always load Bit 18 low.

TABLE IV

Bit 19 Timer

0 Bit 24 Status

1 Bit 24 for 300 ms

TIMER OPERATION

The timer function is provided for use as a retriggerable

‘‘one shot’’ to enable muting for approximately 300 milliseconds after station changes. The timer is enabled at bit 24’s

output if the normal operating mode is selected (shift register bits 20 and 21

e

‘‘LOW’’) and shift register bit 19 data is

latched as a ‘‘HI’’. The timer’s output state will invert immediately upon latching bit 19 ‘‘HI’’ and remain inverted for

approximately 300 milliseconds. If the user readdresses the

device with bit 19 data ‘‘LOW’’ before the timer finishes its

d

1

d

10

1 Premixd10 Premix

Production Test

Mode Only

cycle the timer’s BIT 24 output will finish out the 300 ms

pulse. Readdressing the device with bit 19 ‘‘HI’’ before the

timer finishes its cycle will extend the BIT 24 output pulse

width by 300 ms. Addressing should be performed immediately after the 50 Hz output transitions ‘‘HI’’. BIT 24’s output

state is not guaranteed during the first 300 ms after V

power up as a result of a timer reset in progress.

CC

TABLE V

Bit FUNCTION OF

20 21

PINS 3, 4, & 5

0 0 Status of Bits 22-24

0 1 Test mode 1

1 0 Test mode 2

1 1 Test mode 3

TEST MODE OPERATION

Test Mode 1: Enables the BIT output pins to edge trigger

the phase comparator inputs and monitor an internal lock

detector. BIT 22 negative edge triggers the reference divider input of the phase comparator if the reference divider

state is low. BIT 23 provides the open collector ORing of the

phase comparator’s pump up and down outputs. BIT 24

negative edge triggers the N counter input of the phase

comparator if the N counter state is preconditioned low.

Test Mode 2: Enables the BIT outputs to clock the programmable N counter, monitor its output, and force either its

load or count condition. BIT 22 provides the N counter output which negative edge triggers the phase comparator and

which appears low one N counter clock pulse before it reloads. BIT 23 positive edge triggers the N counter’s clock

input if the prescaler’s output is preconditioned HI. BIT 24

clears the N counter output so that loading will occur on the

next N counter clock edge.

Test Mode 3: Enables the BIT outputs to clock the 50 Hz

and 10 kHz reference dividers and monitor the reference

divider input to the phase comparator. BIT 22 positive edge

clocks the 10 kHz reference divider chain if the 10 kHz output is preconditioned HI. BIT 23 positive edge clocks the 50

Hz divider chain. BIT 24 is the reference divider negative

edge trigger input to the phase comparator.

1

3

Loading...

Loading...