NSC DS8838N, DS8838MX, DS8838M Datasheet

DS8838

Quad Unified Bus Transceiver

General Description

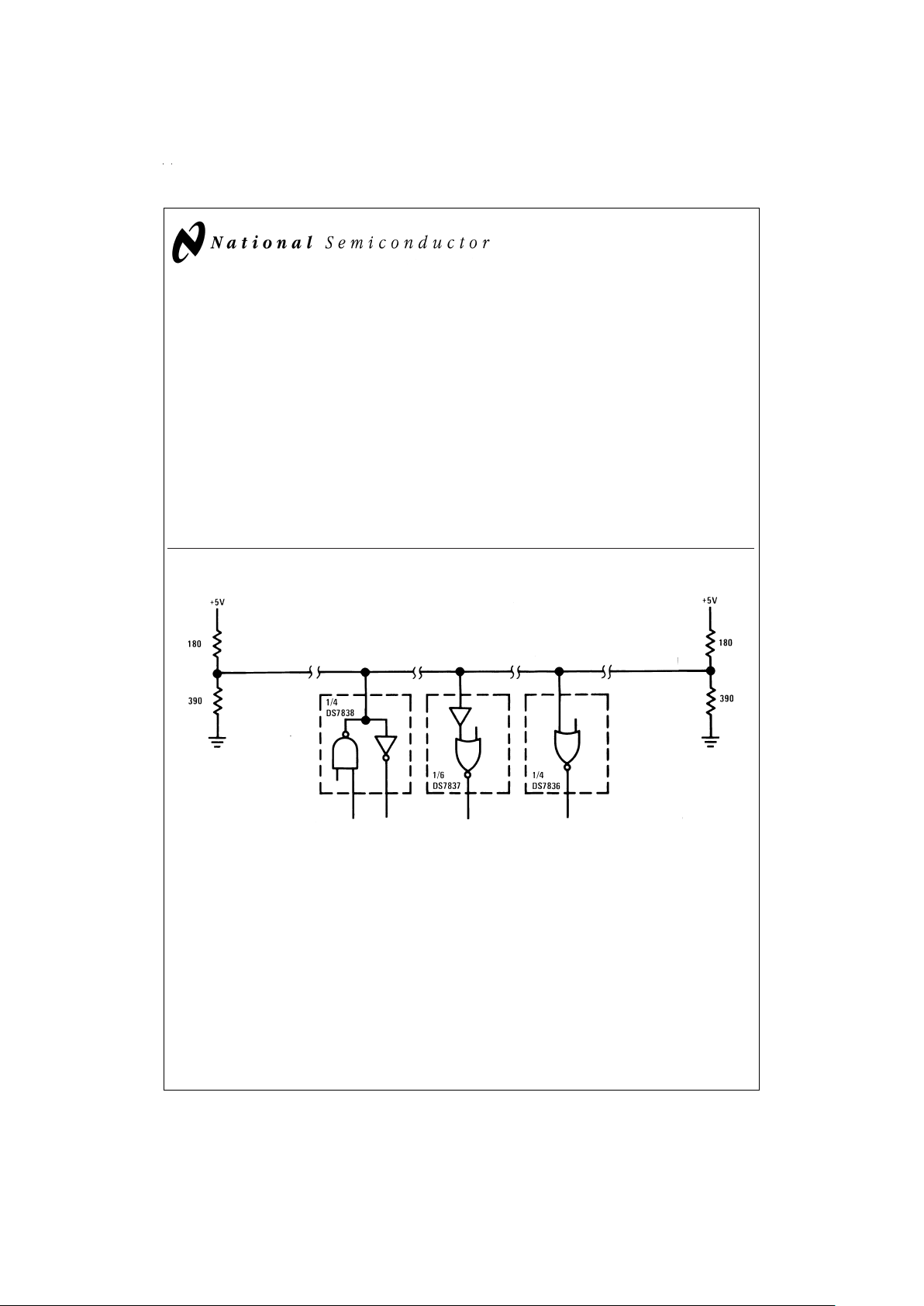

The DS8838 is a quad high speed driver/receiver designed

for use in bus organized data transmission systems interconnected by terminated 120Ω impedance lines. The external

termination is intended to be 180Ω resistor from the bus to

the +5V logic supply together with a 390Ω resistor from the

bus to ground. The bus can be terminated at one or both

ends. Low bus pin current allows up to 27 driver/receiver

pairs to utilize a common bus. The bus loading is unchanged

when V

CC

=

0V. The receivers incorporate hysteresis to

greatly enhance bus noise immunity. One two-input NOR

gate is included to disable all drivers in a package simultaneously.Receiverperformanceis optimized for systems with

bus rise and fall times ≤ 1.0 µs/V.

Features

n 4 totally separate driver/receiver pairs per package

n 1V typical receiver input hysteresis

n Receiver hysteresis independent of receiver output load

n Guaranteed minimum bus noise immunity of 1.3V, 2V

typ.

n Temperature-insensitive receiver thresholds track bus

logic levels

n 20 µA typical bus terminal current with normal V

CC

or

with V

CC

=

0V

n Open collector driver output allows wire-OR connection

n High speed

n Series 74 TTL compatible driver and disable inputs and

receiver outputs

Typical Application

DS005812-1

May 1999

DS8838 Quad Unified Bus Receiver

© 1999 National Semiconductor Corporation DS005812 www.national.com

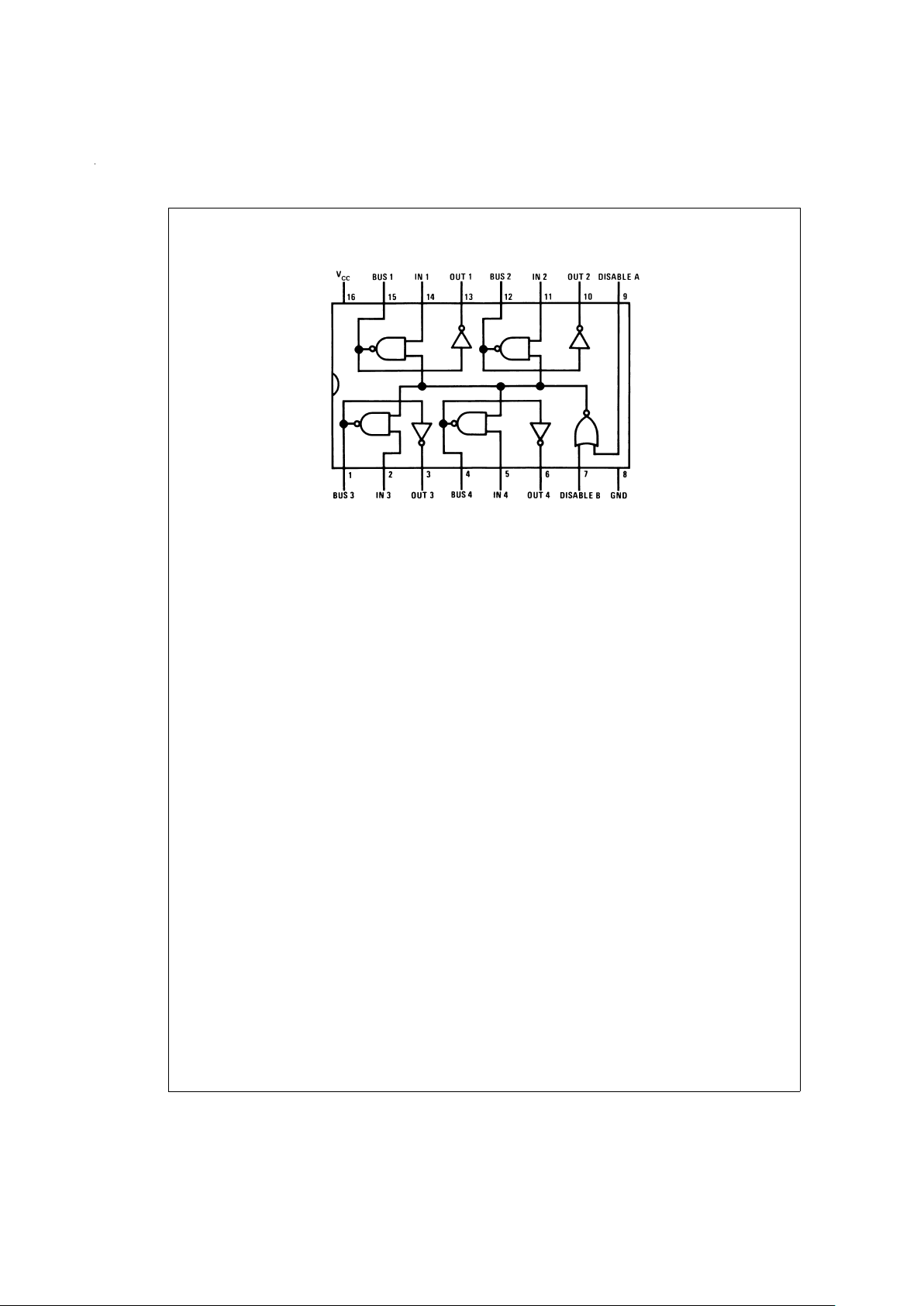

Connection Diagram

Dual-In-Line Package

DS005812-2

Top View

Order Number DS7838J, DS8838M or DS8838N

See NS Package Number J16A, M16A or N16A

www.national.com 2

Loading...

Loading...