DS7831/DS8832

Dual TRI-STATE

®

Line Driver

General Description

Through simple logic control, the DS7831/DS8832 can be

used as either a quad single-ended line driver or a dual differential line driver. They are specifically designed for party

line (bus-organized) systems. The DS8832 does not have

the V

CC

clamp diodes found on the DS7831.

The DS7831 is specified for operation over the −55˚C to

+125˚C military temperature range. The DS8832 is specified

for operation over the 0˚C to +70˚C temperature range.

Features

n Series 54/74 compatible

n 17 ns propagation delay

n Very low output impedance —high drive capability

n 40 mA sink and source currents

n Gating control to allow either single-ended or differential

operation

n High impedance output state which allows many outputs

to be connected to a common bus line

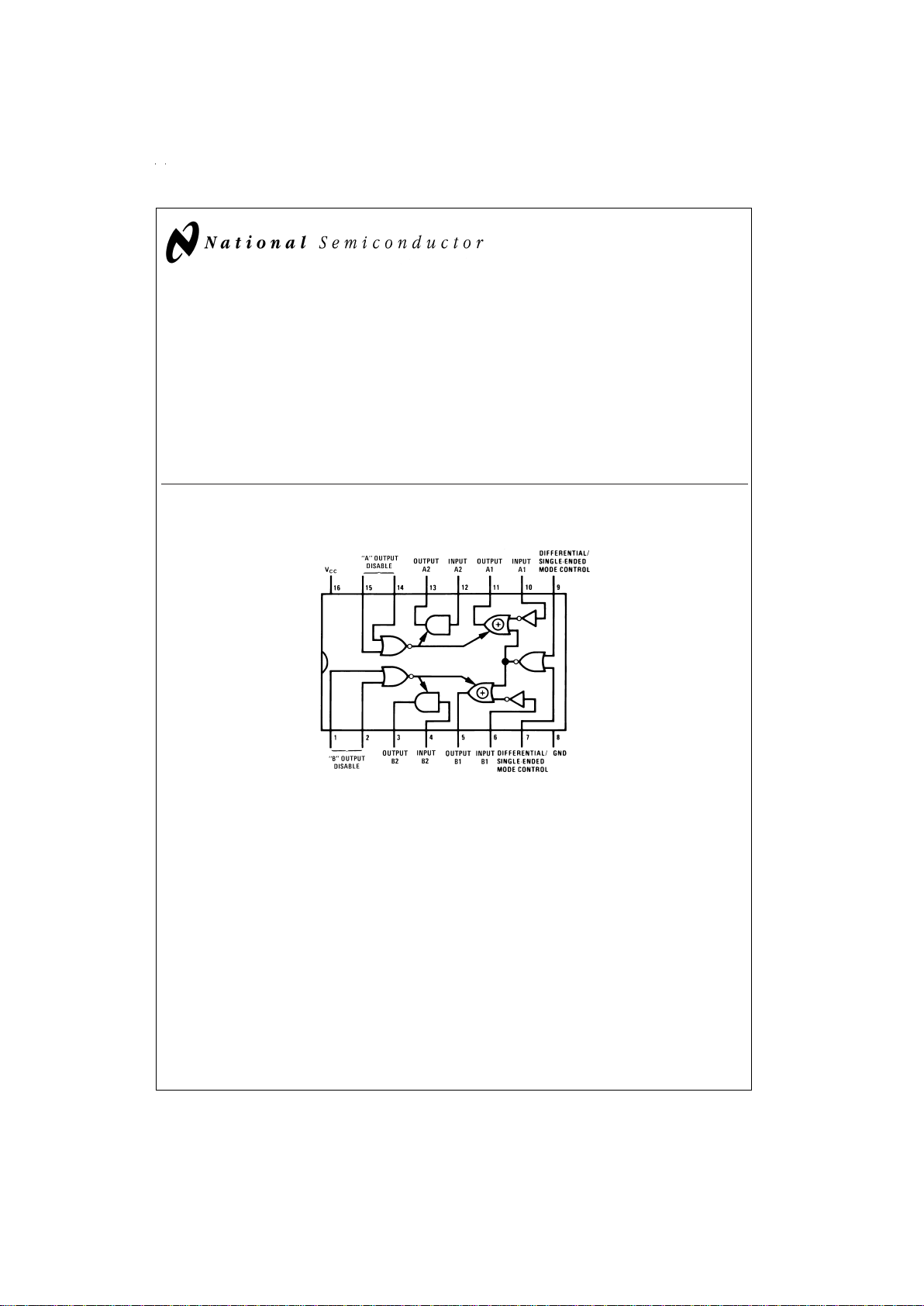

Connection and Logic Diagram

TRI-STATE®is a registered trademark of National SemiconductorCorp.

Dual-In-Line Package

DS005800-1

Top View

Order Number DS8832J or DS8832N

See NS Package Number J16A or N16A

For Complete Military 883 Specificatons,

See RETS Data Sheet.

Order Number DS7831J/883, DS7831W/883,

See NS Package Number J16A or W16A

May 1999

DS7831DS8832 Dual TRI-STATE Line Driver

© 1999 National Semiconductor Corporation DS005800 www.national.com

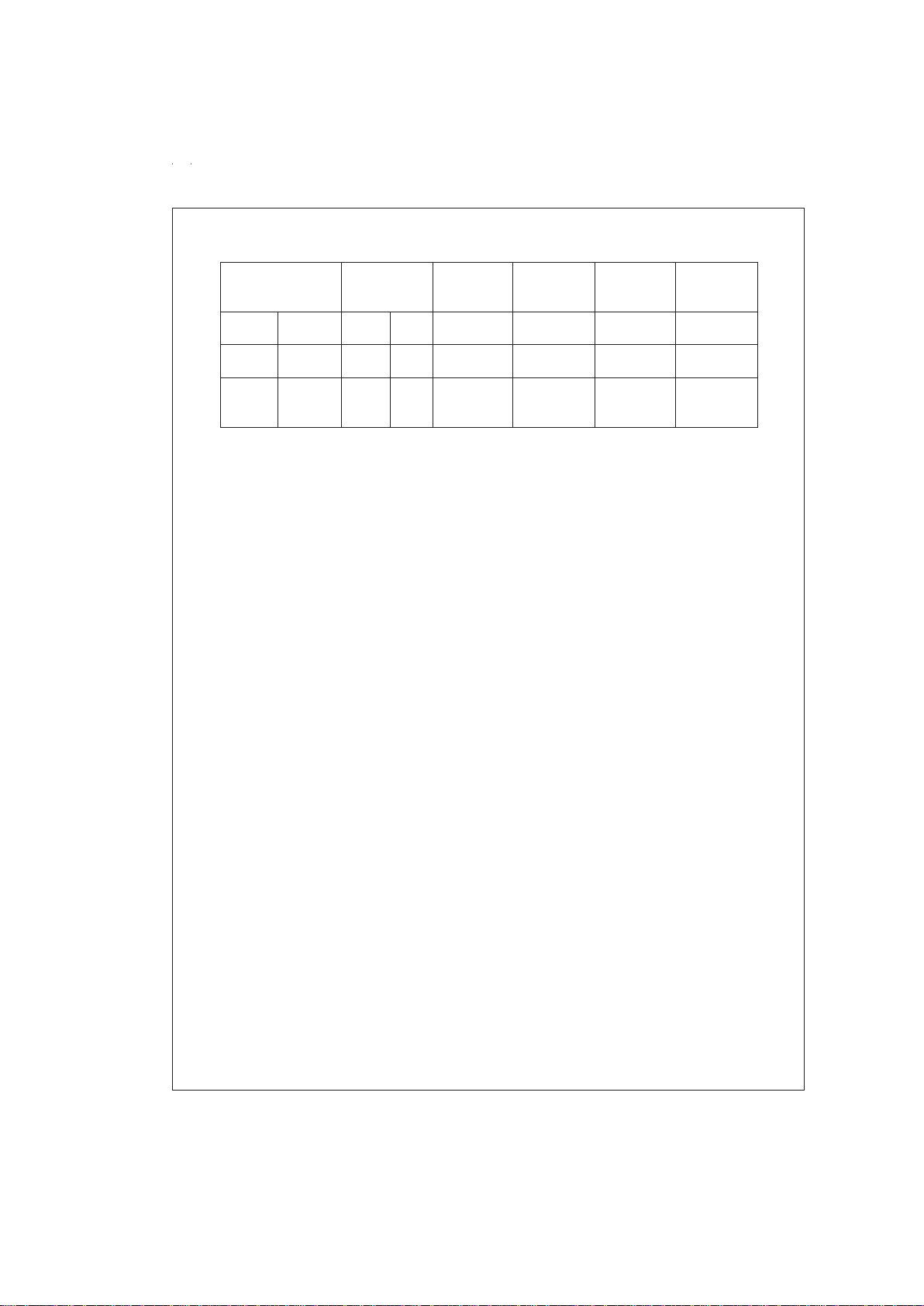

Truth Table

(Shown for A Channels Only)

Differential/

“A” Output Disable Single-Ended Input A1 Output A1 Input A2 Output A2

Mode Control

0 0 0 0 Logical “1” or Same as Logical “1” or Same as

Logical “0” Input A1 Logical “0” Input A2

0

0 X 1 Logical “1” or Opposite of Logical “1” or Same as

1 X Logical “0” Input A1 Logical “0” Input A2

1 X High High

X 1 X X X Impedance X Impedance

State State

X=Don’t Care

www.national.com 2

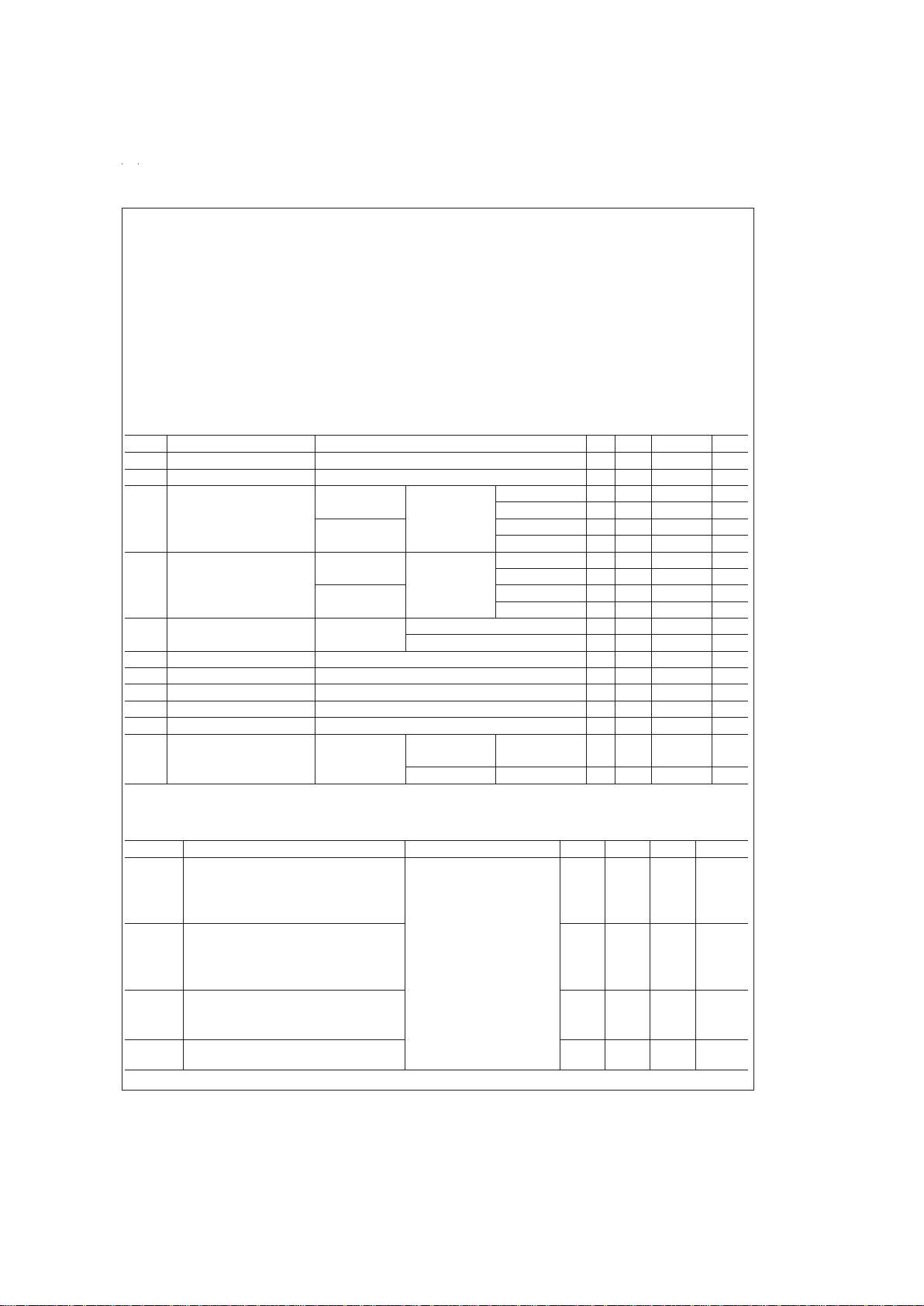

Absolute Maximum Ratings (Note 2)

If Military/Aerospace specified devices are required,

please contact the National Semiconductor Sales Office/

Distributors for availability and specifications.

Supply Voltage 7V

Input Voltage 5.5V

Output Voltage 5.5V

Storage Temperature Range −65˚C to +150˚C

Lead Temperature (Soldering, 4 sec.) 260˚C

Maximum Power Dissipation (Note 1) at 25˚C

Cavity Package 1433 mW

Molded Package 1362 mW

Operating Conditions

Min Max Units

Supply Voltage (V

CC

)

DS7831 4.5 5.5 V

DS8831/DS8832 4.75 5.25 V

Temperature (T

A

)

DS7831 −55 +125 ˚C

DS8832 0 +70 ˚C

Note 1: Derate cavity package 9.6 mW/˚C above 25˚C; derate molded package 10.9 mW/˚C above 25˚C.

Electrical Characteristics (Notes 3, 4)

Symbol Parameter Conditions Min Typ Max Units

V

IH

Logical “1” Input Voltage V

CC

=

Min 2.0 V

V

IL

Logical “0” Input Voltage V

CC

=

Min 0.8 V

V

OH

Logical “1” Output Voltage DS7831 I

O

=

−40 mA 1.8 2.3 V

V

CC

=

Min I

O

=

−2 mA 2.4 2.7 V

DS8832 I

O

=

−40 mA 1.8 2.5 V

I

O

=

−5.2 mA 2.4 2.9 V

V

OL

Logical “0” Output Voltage DS7831 I

O

=

40 mA 0.29 0.50 V

V

CC

=

Min I

O

=

32 mA 0.40 V

DS8832 I

O

=

40 mA 0.29 0.50 V

I

O

=

32 mA 0.40 V

I

IH

Logical “1” Input Current V

CC

=

Max DS7831, V

IN

=

5.5V 1 mA

DS8832, V

IN

=

2.4V 40 µA

I

IL

Logical “0” Input Current V

CC

=

Max, V

IN

=

0.4V −1.0 −1.6 mA

I

OD

Output Disable Current V

CC

=

Max, V

O

=

2.4V or 0.4V −40 40 µA

I

SC

Output Short Circuit Current V

CC

=

Max, (Note 5) −40 −100 −120 mA

I

CC

Supply Current V

CC

=

Max in TRI-STATE 65 90 mA

V

CLI

Input Diode Clamp Voltage V

CC

=

5.0V, T

A

=

25˚C, I

IN

=

−12 mA −1.5 V

V

CLO

Output Diode Clamp

Voltage

V

CC

=

5.0V, I

OUT

=

−12 mA DS7831 −1.5 V

T

A

=

25˚C DS8832

I

OUT

=

12 mA DS7831 V

CC

+ 1.5 V

Switching Characteristics

T

A

=

25˚C, V

CC

=

5V, unless otherwise noted

Symbol Parameter Conditions Min Typ Max Units

t

pd0

Propagation Delay to a Logical “0”

from Inputs A1, A2, B1, B2 13 25 ns

Differential Single-ended Mode

Control to Outputs

t

pd1

Propagation Delay to a Logical “1”

from Inputs A1, A2, B1, B2 13 25 ns

Differential Single-ended Mode

Control to Outputs

t

1H

Delay from Disable Inputs to High

Impedance State (from Logical “1” (See

Figure 4

and

Figure 5

) 6 12 ns

Level)

t

0H

Delay from Disable Inputs to High

Impedance State (from Logical “0” Level)

14 22 ns

www.national.com3

Switching Characteristics (Continued)

T

A

=

25˚C, V

CC

=

5V, unless otherwise noted

Symbol Parameter Conditions Min Typ Max Units

t

H1

Propagation Delay from Disable Inputs

to Logical “1” Level (from High 14 22 ns

Impedance State)

t

H0

Propagation Delay from Disable Inputs

to Logical “0” Level (from High 18 27 ns

Impedance State)

Note 2: “Absolute Maximum Ratings” are those values beyond which the safety of the device cannot be guaranteed. Except for “Operating Temperature Range” they

are not meant to imply that the devices should be operated at these limits. The table of “Electrical Characteristics” provides conditions for actual device operation.

Note 3: Unless otherwise specified min/max limits apply across the −55˚C to +125˚C temperature range for the DS7831 and across the 0˚C to +70˚C range for the

DS8832. All typical values are for T

A

=

25˚C and V

CC

=

5V.

Note 4: All currents into device pins shown as positive, out of device pins as negative, all voltage referenced to ground unless otherwise noted. All values shown

as max or min on absolute value basis.

Note 5: Applies for T

A

=

125˚C only. Only one output should be shorted at a time.

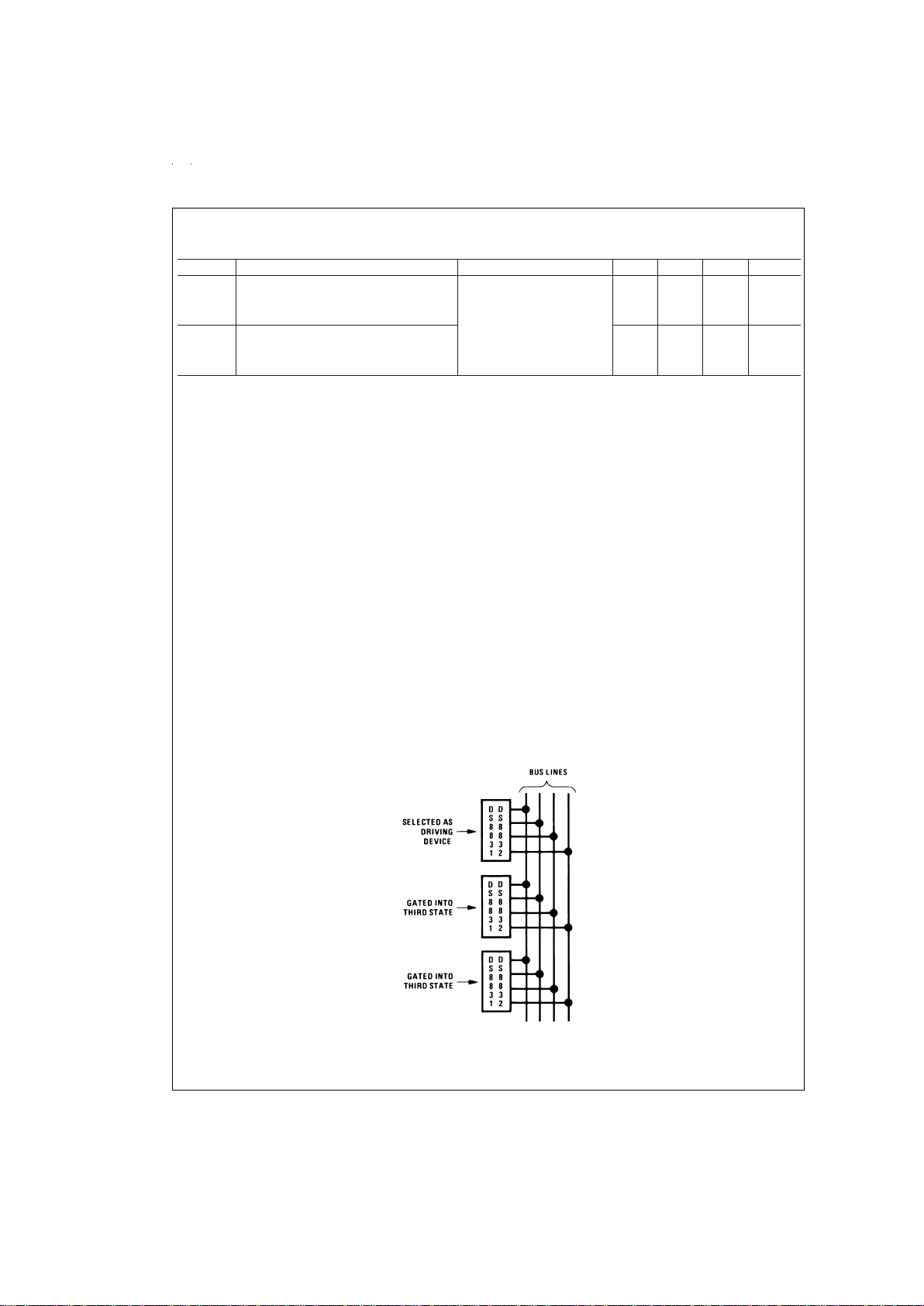

Mode of Operation

To operate as a quad single-ended line driver apply logical

“0”s to the output disable pins (to keep the outputs in the normal low impedance mode) and apply logical “0”s to both

Differential/Single-ended Mode Control inputs. All four channels will then operate independently and no signal inversion

will occur between inputs and outputs.

To operate as a dual differential line driver apply logical “0”s

to the Output Disable pins and apply at least one logical “1”

to the Differential/Single-ended Mode Control inputs.

The inputs to the A channels should be connected together

and the inputs to the B channels should be connected together.

In this mode the signals applied to the resulting inputs will

pass non-inverted on the A

2

and B2outputs and inverted on

the A

1

and B1outputs.

When operating in a bus-organized system with outputs tied

directly to outputs of other DS7831, DS8832’s (

Figure 1

), all

devices except one must be placed in the “high impedance”

state. This is accomplished by ensuring that a logical “1” is

applied to at least one of the Output Disable pins of each device which is to be in the “high impedance” state. A NOR gate

was purposely chosen for this function since it is possible

with only two DM5442/DM7442, BCD-to-decimal decoders,

to decode as many as 100 DS7831, DS8832’s (

Figure 2

).

The unique device whose Disable inputs receive two logical

“0” levels assumes the normal low impedance output state,

providing good capacitive drive capability and waveform integrity especially during the transition from the logical “0” to

logical ”1” state. The other outputs —in the high impedance

state— take only a small amount of leakage current from the

low impedance outputs. Since the logical “1” output current

from the selected device is 100 times that of a conventional

Series 54/74 device (40 mA vs. 400 µA), the output is easily

able to supply that leakage current for several hundred other

DS7831/DS8831’s, DS7832/DS8832’s and still have available drive for the bus line (

Figure 3

).

DS005800-2

FIGURE 1.

www.national.com 4

Mode of Operation (Continued)

DS005800-3

FIGURE 2.

DS005800-4

FIGURE 3.

www.national.com5

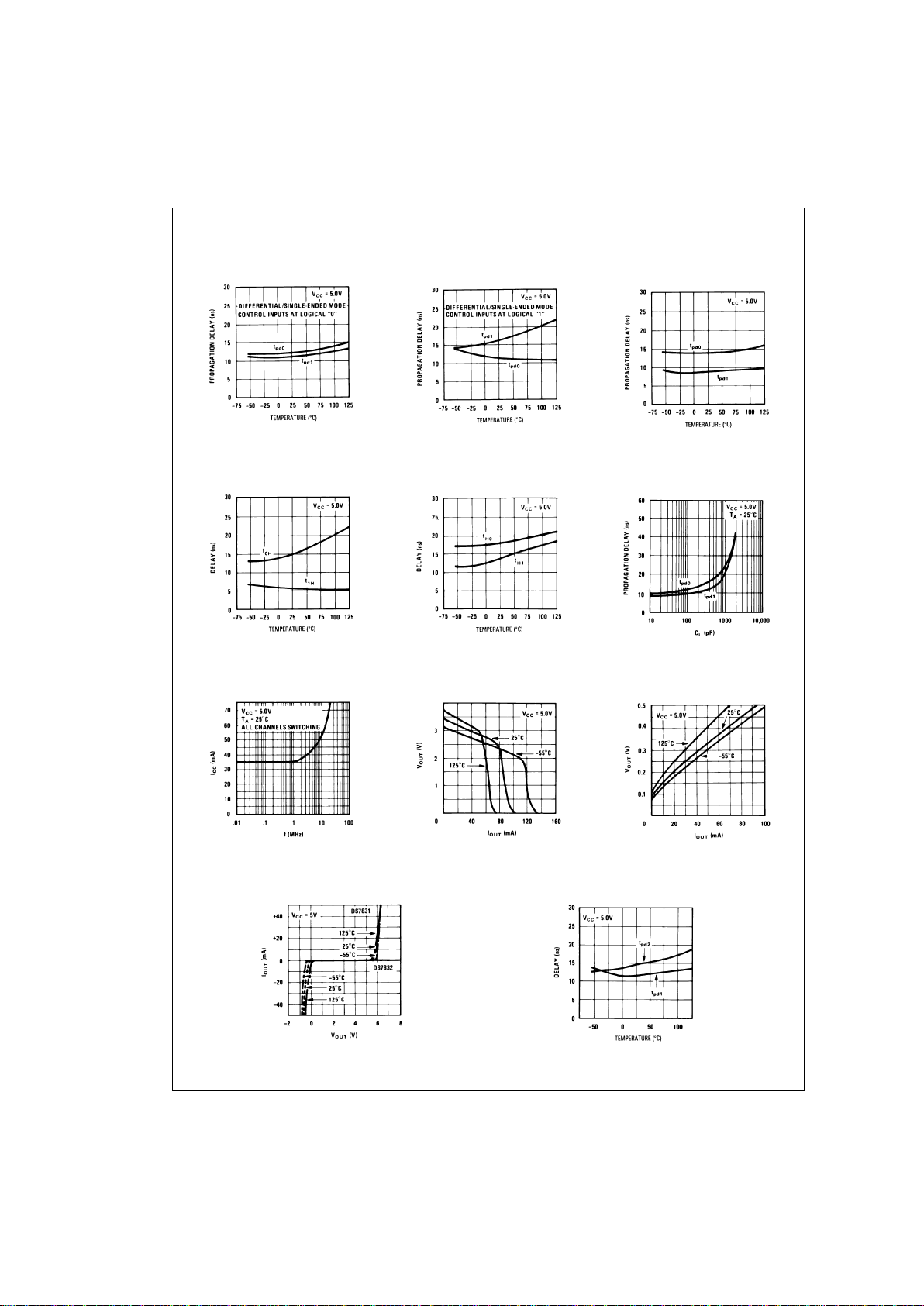

Typical Performance Characteristics

Propagation Delay from Input

to Output (Channel 1)

DS005800-5

Propagation Delay from Input

to Output (Channel 1)

DS005800-10

Propagation Delay from Input

to Output (Channel 2)

DS005800-11

Delay from Disable to High

Impedance State

DS005800-12

Delay from Disable to Low

Impedance State

DS005800-13

Propagation Delay vs Load

Capacitance

DS005800-14

Total Supply Current vs

Frequency

DS005800-15

Logical “1” Output Voltage

vs Source Current

DS005800-16

Logical “0” Output Voltage

vs Sink Current

DS005800-17

I

OUT

vs V

OUT

High

Impedance Output State

DS005800-18

Propagation Delay in

Differential Mode

DS005800-19

www.national.com 6

Typical Performance Characteristics (Continued)

Switching Time Waveforms

DS005800-6

DS005800-7

Input characteristic:

Amplitude=3.0V

Frequency=1.0 MHz, 50%duty cycle

t

r

=

t

f

≤ ns (10%to 90%)

www.national.com7

Switching Time Waveforms (Continued)

DS005800-8

FIGURE 4.

www.national.com 8

AC Load Circuit

DS005800-9

Symbol Switch S1 Switch S2 C

L

t

pd1

closed closed 50 pF

t

pd0

closed closed 50 pF

t

0H

closed closed

*

5pF

t

1H

closed closed

*

5pF

t

H0

closed open 50 pF

t

H1

open closed 50 pF

*

Jig capacitance

FIGURE 5.

www.national.com9

Physical Dimensions inches (millimeters) unless otherwise noted

Ceramic Dual-In-Line Package (J)

Order Number DS7831J or DS8832J

NS Package Number J16A

www.national.com 10

Physical Dimensions inches (millimeters) unless otherwise noted (Continued)

LIFE SUPPORT POLICY

NATIONAL’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT

DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL

COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

1. Life support devices or systems are devices or

systems which, (a) are intended for surgical implant

into the body, or (b) support or sustain life, and

whose failure to perform when properly used in

accordance with instructions for use provided in the

labeling, can be reasonably expected to result in a

significant injury to the user.

2. A critical component is any component of a life

support device or system whose failure to perform

can be reasonably expected to cause the failure of

the life support device or system, or to affect its

safety or effectiveness.

National Semiconductor

Corporation

Americas

Tel: 1-800-272-9959

Fax: 1-800-737-7018

Email: support@nsc.com

National Semiconductor

Europe

Fax: +49 (0) 1 80-530 85 86

Email: europe.support@nsc.com

Deutsch Tel: +49 (0) 1 80-530 85 85

English Tel: +49 (0) 1 80-532 78 32

Français Tel: +49 (0) 1 80-532 93 58

Italiano Tel: +49 (0) 1 80-534 16 80

National Semiconductor

Asia Pacific Customer

Response Group

Tel: 65-2544466

Fax: 65-2504466

Email: sea.support@nsc.com

National Semiconductor

Japan Ltd.

Tel: 81-3-5639-7560

Fax: 81-3-5639-7507

www.national.com

Molded Dual-In-Line Package (N)

Order Number DS8832N

NS Package Number N16A

DS7831DS8832 Dual TRI-STATE Line Driver

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.

Loading...

Loading...