TL/F/9579

DP8406 (54F/74F632) 32-Bit Parallel Error Detection and Correction Circuit

May 1991

DP8406 (54F/74F632)

32-Bit Parallel Error Detection and Correction Circuit

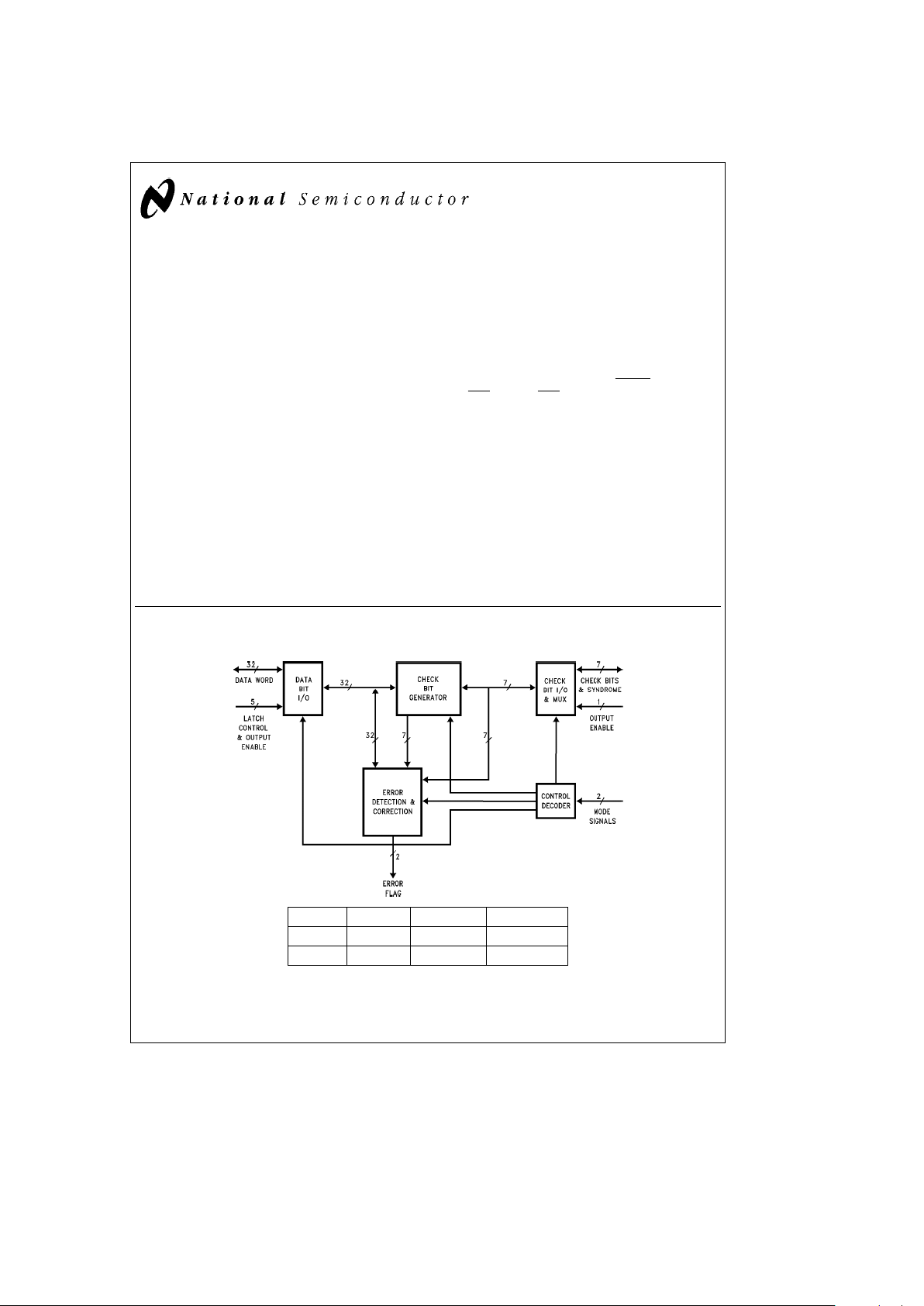

General Description

The DP8406 device is a 32-bit parallel error detection and

correction circuit (EDAC) in a 52-pin or 68-pin package. The

EDAC uses a modified Hamming code to generate a 7-bit

check word from a 32-bit data word. This check word is

stored along with the data word during the memory write

cycle. During the memory read cycle, the 39-bit words from

memory are processed by the EDAC to determine if errors

have occurred in memory.

Single-bit errors in the 32-bit data word are flagged and corrected.

Single-bit errors in the 7-bit check word are flagged, and the

CPU sends the EDAC through the correction cycle even

though the 32-bit data word is not in error. The correction

cycle will simply pass along the original 32-bit data word in

this case and produce error syndrome bits to pinpoint the

error-generating location.

Dual-bit errors are flagged but not corrected. These errors

may occur in any two bits of the 39-bit word from memory

(two errors in the 32-bit data word, two errors in the 7-bit

check word, or one error in each word). The gross-error

condition of all LOWs or all HIGHs from memory will be

detected. Otherwise, errors in three or more bits of the

39-bit word are beyond the capabilities of these devices to

detect.

Read-modify-write (byte-control) operations can be performed by using output latch enable, LEDBO

, and the indi-

vidual OEB

0

through OEB3byte control pins.

Diagnostics are performed on the EDACs by controls and

internal paths that allow the user to read the contents of the

Data Bit and Check Bit input latches. These will determine if

the failure occurred in memory or in the EDAC.

Features

Y

Detects and corrects single-bit errors

Y

Detects and flags dual-bit errors

Y

Built-in diagnostic capability

Y

Fast write and read cycle processing times

Y

Byte-write capability

Y

Guaranteed 4000V minimum ESD protection

Y

Fully pin and function compatible with TI’s

SN74ALS632A thru SN74ALS635 series

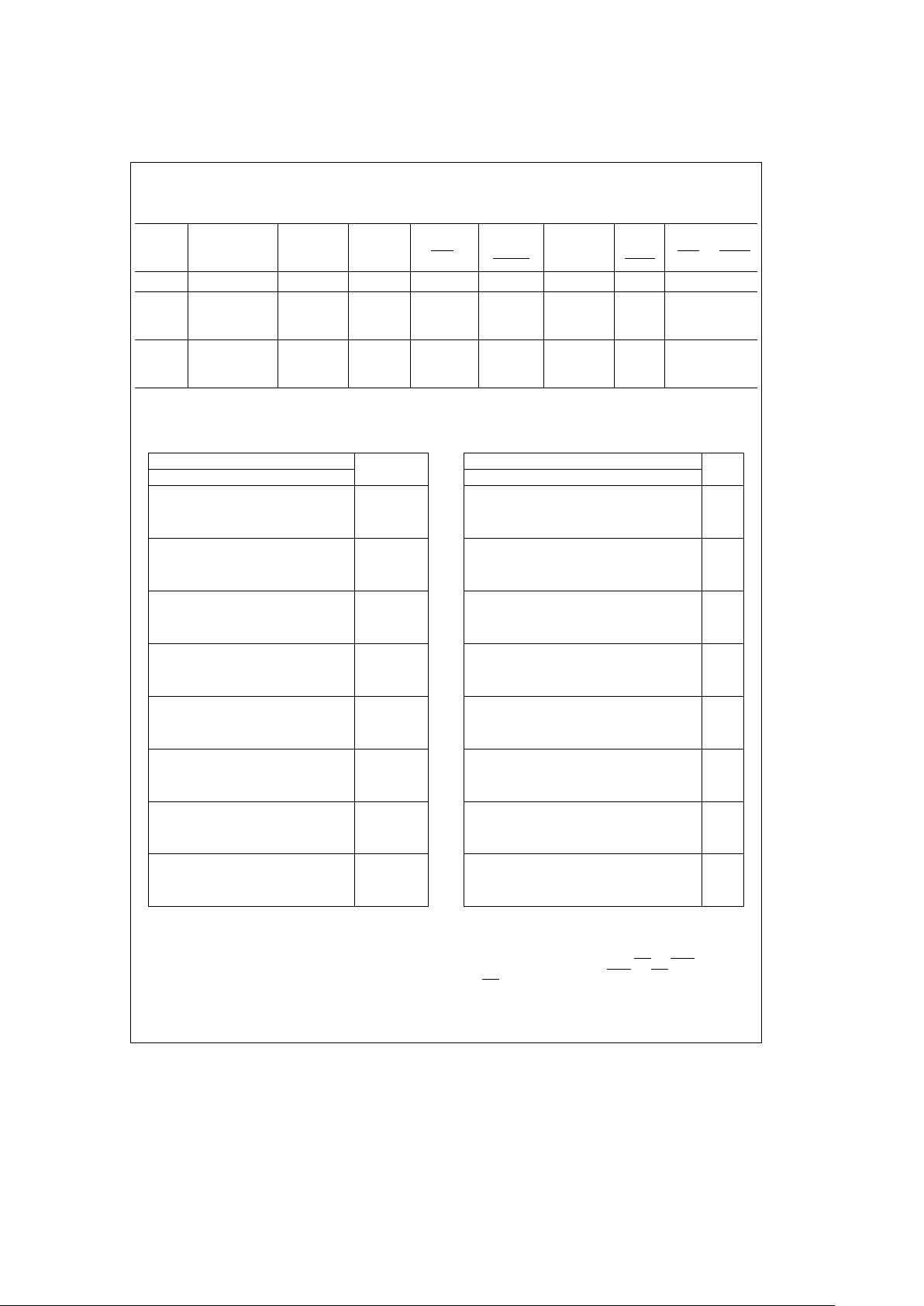

Simplified Functional Block

TL/F/9579– 9

Device Package Byte-Write Output

DP8406 52-Pin yes TRI-STATE

É

DP8406 68-Pin yes TRI-STATE

É

FASTÉand TRI-STATEÉare registered trademarks of National Semiconductor Corporation.

C

1995 National Semiconductor Corporation RRD-B30M105/Printed in U. S. A.

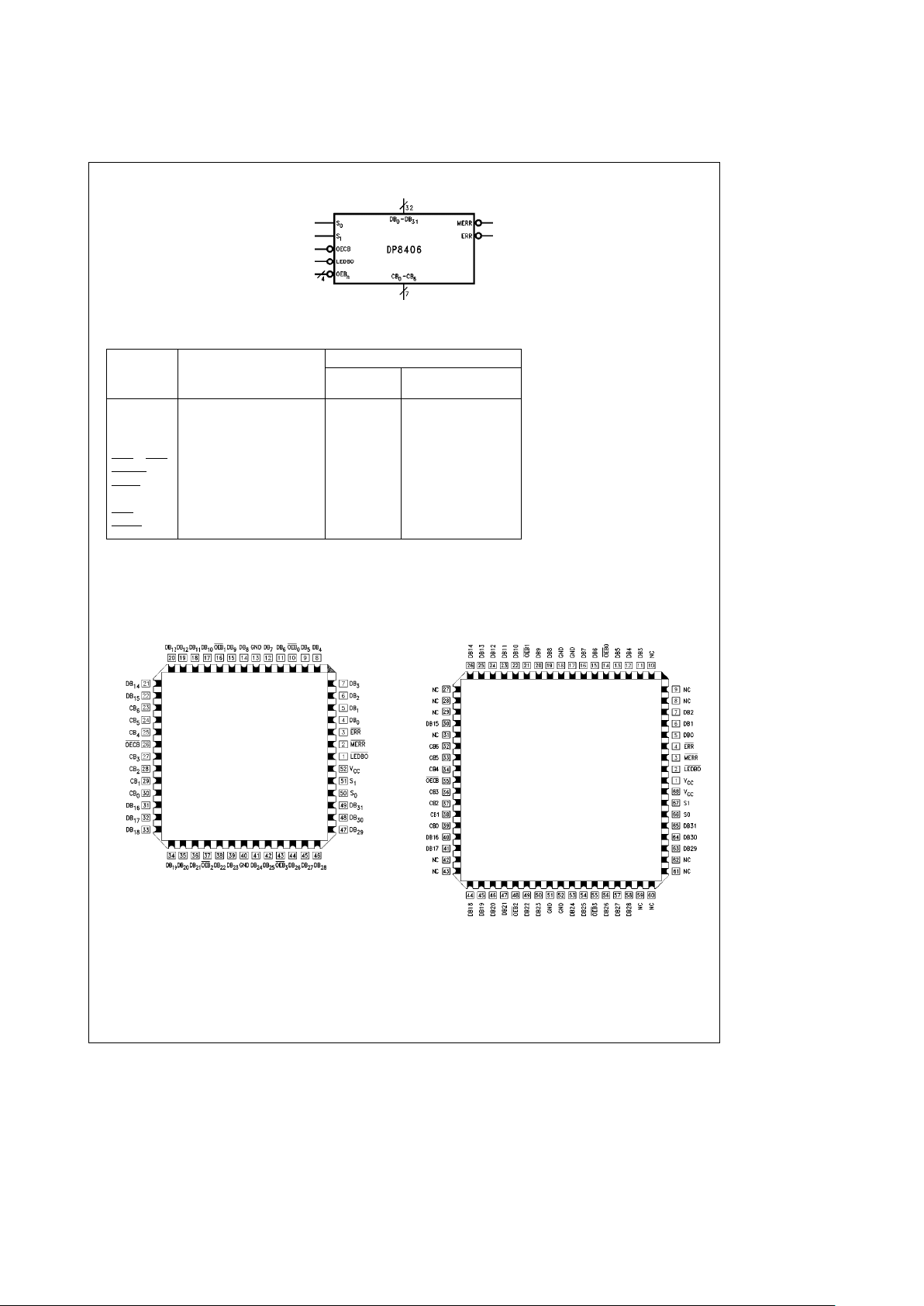

Logic Symbol

TL/F/9579– 1

Unit Loading/Fan Out

54F/74F

Pin Names Description

U.L. Input I

IH/IIL

HIGH/LOW Output IOH/I

OL

CB0–CB6Check Word Bit, Input 3.5/1.083 70 mA/b650 mA

or TRI-STATE

É

Output 150/40 (33.3)b3 mA/24 mA (20 mA)

DB

0

–DB31Data Word Bit, Input 3.5/1.083 70 mA/b650 mA

or TRI-STATE Output 150/40 (33.3)

b

3 mA/24 mA (20 mA)

OEB0–OEB3Output Enable Data Bits 1.0/1.0 20 mA/b0.6 mA

LEDBO Output Latch Enable Data Bit 1.0/1.0 20 mA/b0.6 mA

OECB

Output Enable Check Bit 1.0/1.0 20 m A/b0.6 mA

S

0,S1

Select Pins 1.0/1.0 20 mA/b0.6 mA

ERR

Single Error Flag 50/33.3

b

1 mA/20 mA

MERR

Multiple Error Flag 50/33.3

b

1 mA/20 mA

Connection Diagrams

Pin Assignment

for LCC and PCC

52-Pin

TL/F/9579– 3

Order Number DP8406QV (74F632QC)

See NS Package Number V52A

Pin Assignment

for LCC and PCC

68-Pin

TL/F/9579– 8

NCÐNo internal connection

Order Number DP8406V (74F632VC)

See NS Package Number V68A

2

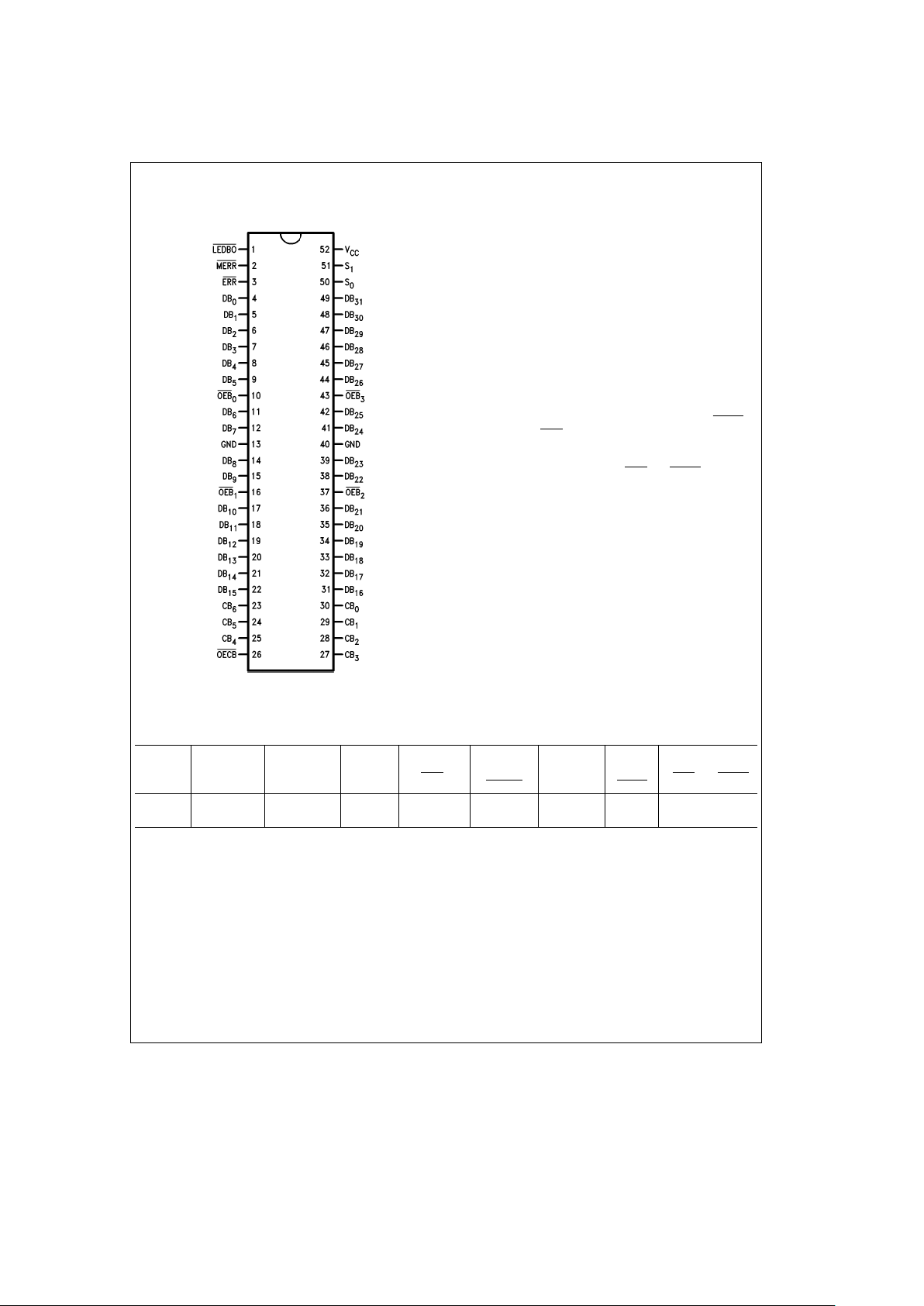

Connection Diagram (Continued)

Pin Assignment for

Side Brazed DIP

TL/F/9579– 2

Order Number DP8406D (74F632DC)

See NS Package Number D52A

Functional Description

MEMORY WRITE CYCLE DETAILS

During a memory write cycle, the check bits (CB0through

CB

6

) are generated internally in the EDAC by seven 16-input parity generators using the 32-bit data word as defined

in Table II. These seven check bits are stored in memory

along with the original 32-bit data word. This 32-bit word will

later be used in the memory read cycle for error detection

and correction.

ERROR DETECTION AND CORRECTION DETAILS

During a memory read cycle, the 7-bit check word is retrieved along with the actual data. In order to be able to

determine whether the data from memory is acceptable to

use as presented to the bus, the error flags must be tested

to determine if they are at the HIGH level.

The first case in Table III represents the normal, no-error

conditions. The EDAC presents HIGHs on both flags. The

next two cases of single-bit errors give a HIGH on MERR

and a LOW on ERR, which is the signal for a correctable

error, and the EDAC should be sent through the correction

cycle. The last three cases of double-bit errors will cause

the EDAC to signal LOWs on both ERR

and MERR, which is

the interrupt indication for the CPU.

Error detection is accomplished as the 7-bit check word and

the 32-bit data word from memory are applied to internal

parity generators/checkers. If the parity of all seven groupings of data and check bits is correct, it is assumed that no

error has occurred and both error flags will be HIGH.

TABLE I. Write Control Function

Memory EDAC Control DB Control

DB Output CB

Error Flags

Cycle Function S

1

S

0

Data I/O

OEB

n

Latch Check I/O Control

ERR

MERR

LEDBO OECB

Write

Generate

L L Input H X

Output

LHH

Check Word Check Bit*

*See Table II for details of check bit generation.

3

Functional Description (Continued)

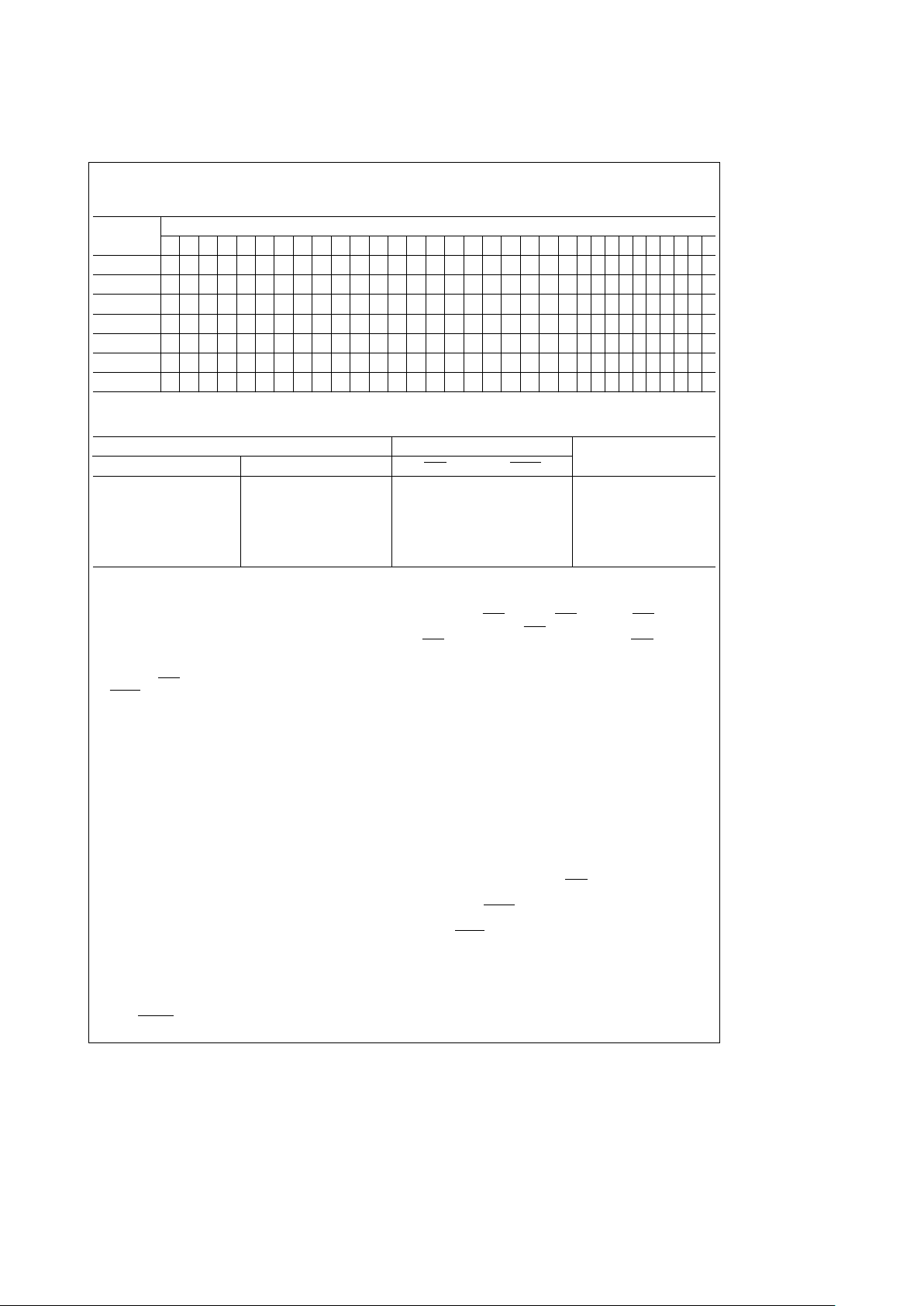

TABLE II. Parity Algorithm

Check Word

32-Bit Data Word

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

CB

0

XXXX XXXX X XXXXXX X

CB

1

XXXXXXXX XXXXXXXX

CB

2

XXXXXXXXXXXXXXXX

CB

3

XXX XXX XX XXX XXX XX

CB

4

XX XXXXXX XX XXXXXX

CB

5

XXXXXXXX XXXXXXXX

CB

6

XXXXXXXX XXXXXXXX

The seven check bits are parity bits derived from the matrix of data bits as indicated by X for each bit.

TABLE III. Error Function

Total Number of Errors Error Flags

Data Correction

32-Bit Data Word 7-Bit Check Word ERR MERR

0 0 H H Not Applicable

1 0 L H Correction

0 1 L H Correction

1 1 L L Interrupt

2 0 L L Interrupt

0 2 L L Interrupt

HeHIGH Voltage Level

L

e

LOW Voltage Level

If the parity of one or more of the check groups is incorrect,

an error has occurred and the proper error flag or flags will

be set LOW. Any single error in the 32-bit data word will

change the state of either three or five bits of the 7-bit

check word. Any single error in the 7-bit check word changes the state of only that one bit. In either case, the single

error flag (ERR

) will be set LOW while the dual error flag

(MERR

) will remain HIGH.

Any 2-bit error will change the state of an even number of

check bits. The 2-bit error is not correctable since the parity

tree can only identify single-bit errors. Both error flags are

set LOW when any 2-bit error is detected.

Three or more simultaneous bit errors can cause the EDAC

to believe that no error, a correctable error, or an uncorrectable error has occurred and will produce erroneous results

in all three cases. It should be noted that the gross-error

conditions of all LOWs and all HIGHs will be detected.

As the corrected word is made available on the data I/O

port (DB

0

through DB31), the check word I/O port (CB

0

through CB6) presents a 7-bit syndrome error code. This

syndrome error code can be used to locate the bad memory

chip. See Table V for syndrome decoding.

READ-MODIFY-WRITE (BYTE CONTROL) OPERATIONS

The ’F632 device is capable of byte-write operations. The

39-bit word from memory must first be latched into the Data

Bit and Check Bit input latches. This is easily accomplished

by switching from the read and flag mode (S

1

e

H, S

0

e

L)

to the latch input mode (S

1

e

H, S

0

e

H). The EDAC will

then make any corrections, if necessary, to the data word

and place it at the input of the output data latch. This data

word must then be latched into the output data latch by

taking LEDBO

from a LOW to a HIGH.

Byte control can now be employed on the data word

through the OEB

0

through OEB3controls. OEB0controls

DB

0

–DB7(byte 0), OEB1controls DB8–DB15(byte 1),

OEB

2

controls DB16–DB23(byte 2), and OEB3controls

DB

24

–DB31(byte 3). Placing a HIGH on the byte control will

disable the output and the user can modify the byte. If a

LOW is placed on the byte control, then the original byte is

allowed to pass onto the data bus unchanged. If the original

data word is altered through byte control, a new check word

must be generated before it is written back into memory.

This is easily accomplished by taking controls S

1

and S

0

LOW. Table VI lists the read-modify-write functions.

DIAGNOSTIC OPERATIONS

The ’F632 is capable of diagnostics that allow the user to

determine whether the EDAC or the memory is failing. The

diagnostic function tables will help the user to see the possibilities for diagnostic control. In the diagnostic mode

(S

1

e

L, S

0

e

H), the check word is latched into the input

latch while the data input latch remains transparent. This

lets the user apply various data words against a fixed known

check word. If the user applies a diagnostic data word with

an error in any bit location, the ERR

flag should be LOW. If a

diagnostic data word with two errors in any bit location is

applied, the MERR

flag should be LOW. After the check

word is latched into the input latch, it can be verified by

taking OECB

LOW. This outputs the latched check word.

The diagnostic data word can be latched into the output

data latch and verified. By changing from the diagnostic

mode (S

1

e

L, S

0

e

H) to the correction mode (S

1

e

H, S

0

e

H), the user can verify that the EDAC will correct the

diagnostic data word. Also, the syndrome bits can be produced to verify that the EDAC pinpoints the error location.

Table VII lists the diagnostic functions.

4

Functional Description (Continued)

TABLE IV. Read, Flag and Correct Function

Memory EDAC Control DB Control

DB Output CB

Error Flags

Cycle Function S

1S0

Data I/O

OEB

n

Latch Check I/O Control

ERR

MERR

LEDBO OECB

Read Read & Flag H L Input H X Input H Enabled (Note 1)

Read Latch Input Latched Latched

Data & Check H H Input H L Input H Enabled (Note 1)

Bits Data Check Word

Read Output Output Output

Corrected Data H H Corrected L X Syndrome L Enabled (Note 1)

& Syndrome Bits Data Word Bits (Note 2)

Note 1: See Table III for error description.

Note 2: See Table V for error location.

TABLE V. Syndrome Decoding

Syndrome Bits

Error

6543210

LLLLLLL unc

L L L L L L H 2-Bit

L L L L L H L 2-Bit

LLLLLHH unc

L L L L H L L 2-Bit

LLLLHLH unc

LLLLHHL unc

L L L L H H H 2-Bit (Note 2)

L L L H L L L 2-Bit

LLLHLLH unc

LLLHLHL DB

31

L L L H L H H 2-Bit

LLLHHLL unc

L L L H H L H 2-Bit

L L L H H H L 2-Bit

LLLHHHH DB

30

L L H L L L L 2-Bit

LLHLLLH unc

LLHLLHL DB

29

L L H L L H H 2-Bit

LLHLHLL DB

28

L L H L H L H 2-Bit

L L H L H H L 2-Bit

L LH L HHH DB

27

LLHHLLL DB

26

L L H H L L H 2-Bit

L L H H L H L 2-Bit

LLHHLHH DB

25

L L H H H L L 2-Bit

LLHHHLH DB

24

L L H H H H L unc

L L H H H H H 2-Bit

Syndrome Bits

Error

6543210

L H L L L L L 2-Bit

LHLLL LHunc

LHLLLHLDB

7

L H L L L H H 2-Bit

LHLLHLLDB

6

L H L L H L H 2-Bit

L H L L H H L 2-Bit

LHLLHHHDB

5

LHLHLLLDB

4

L H L H L L H 2-Bit

L H L H L H L 2-Bit

LHLHLHHDB

3

L H L H H L L 2-Bit

LHLHHLHDB

2

L H L H H H L unc

L H L H H H H 2-Bit

LHHLL LLDB

0

L H H L L L H 2-Bit

L H H L L H L 2-Bit

L H H L L H H unc

L H H L H L L 2-Bit

LHHLHLHDB

1

LHHLHHLunc

L H H L H H H 2-Bit

L H H H L L L 2-Bit

L H H H L L H unc

L H H H L H L unc

L H H H L H H 2-Bit

LHHHHL Lunc

L H H H H L H 2-bit

L H H H H H L 2-bit

LHHHHHHCB

6

CB

X

e

Error in check bit X

DB

Y

e

Error in data bit Y

2-Bit

e

Double-bit error

unc

e

Uncorrectable multi-bit error

Note: 2-bit and unc condition will cause both ERR

and MERR to be LOW

Note 1: Syndrome bits for all LOWs. MERR

and ERR LOW for all LOWs,

only ERR

LOW for DB30error.

Note 2: Syndrome bits for all HIGHs.

5

Loading...

Loading...