DP83959

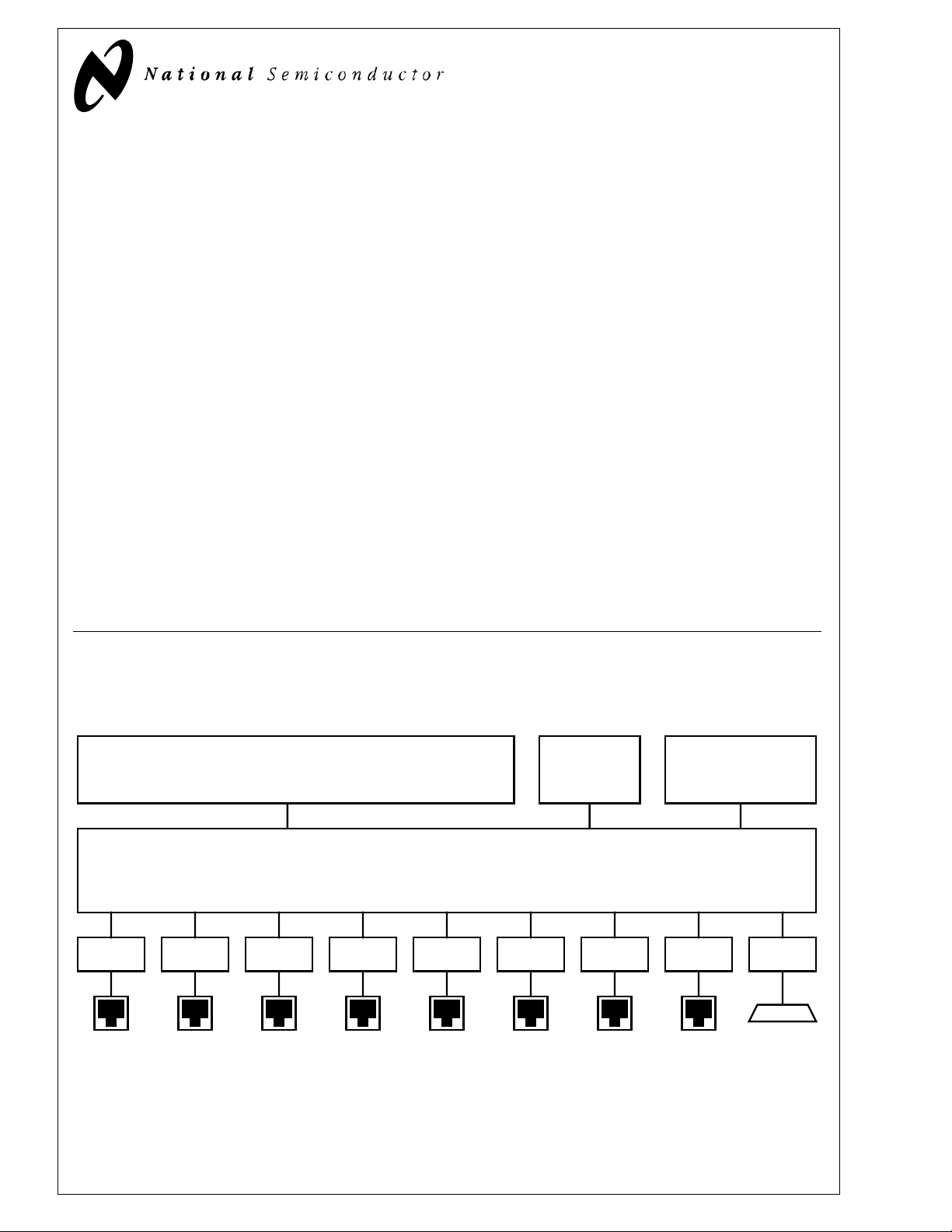

8-Port Lite Ethernet Repeater Interface Controller

DP83959 8-Port Lite Ethernet Repeater Interface Controller

October 1997

General Description

The DP83959 8-Port Lite Ethernet Repeater Interface

Controller (LERIC8) is a single chip solution for unmanaged 10BASE-T Ethernet repeater (hub) products. By integrating electronics needed to support eight 10BASE-T

ports, a full level/drive compatible AUI port for a backbone

connection, and an internal power on reset circuit, a

LERIC8 based design requires only the addition of a few

passive components: crystal, transformers, connectors

and a power source.

The LERIC8 provides on-chip LED drivers that connect directly to LEDs via series resistors. In addition to the Link

OK, Port Partition, Global Activity and Global Collision LED

outputs, the LERIC8 provides an on chip network traffic

level monitor circuit with 8 LED outputs to drive a barg raph

type display.

The LERIC8 also provides an LED and Inter Repeater Bus

interface that is compatible with the DP83955/6 LERIC™

products.

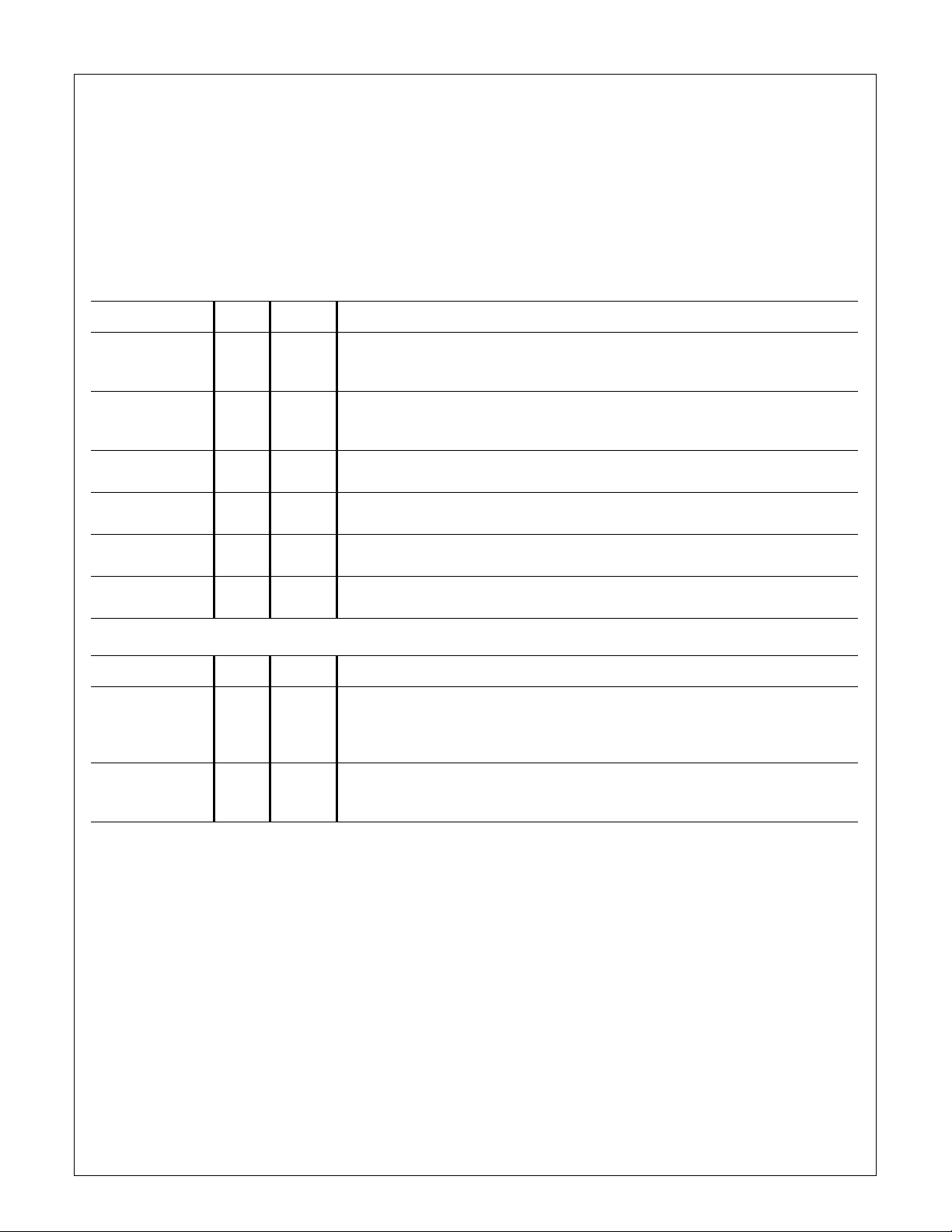

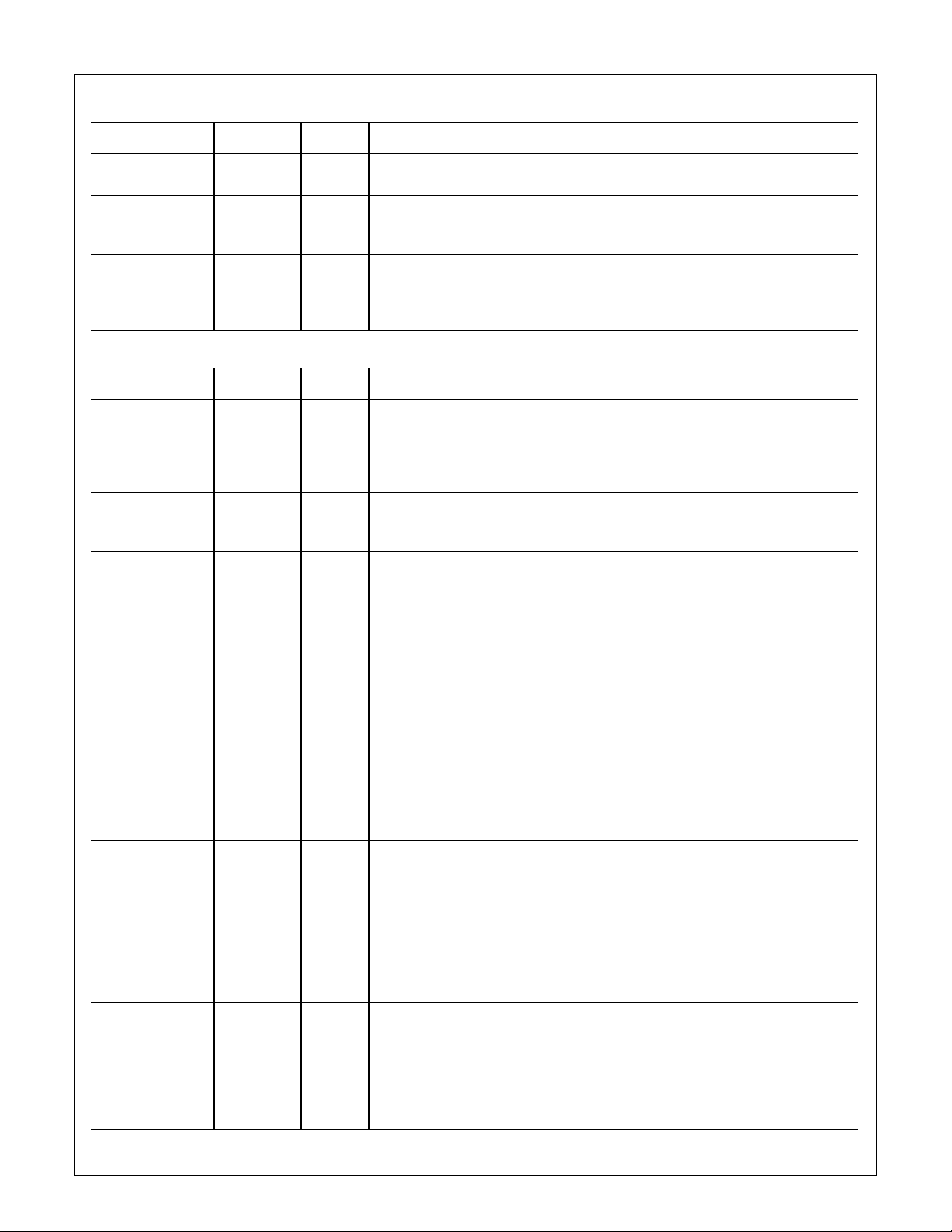

1.0 System Diagram

Features

■ Fully IEEE 802.3 Ethernet Repeater compliant

■ Eight IEEE 802.3 10BASE-T compliant ports with

on-chip transmit filters

■ One IEEE 802.3 compatible AUI port

■ Direct drive status LED outputs

■ Network traffic level monitor with direct drive LED

outputs

■ Automatic internal power-on reset function. External

TTL compatible reset pin provided for device testing if

required

■ Inter-LERIC™ bus for cascading up to 3 devices on a

single board

■ Register/LED status interface compatible with

DP83955/6 LERIC™ products

■ Single 20 MHz crystal or external 20 MHz oscillator

module operation

■ Single 5V supply

■ 160 pin PQFP package

Status LEDs (Optional)

Per 10BASE-T Port Link & Partition

AUI Port Partition

Global Activity, Global Collision

Network Traffic Bargraph

Alert (High Traffic or Long Partition)

DP83959 LERIC8

8-Port Lite Ethernet Repeater Interface Controller

Transformer

10BASE-T

Port 1

TRI-STATE® is a registered trademark of National Semiconductor Corporation.

™

and Inter-LERIC™ are trademarks of National Semiconductor Corporation.

LERIC

Transformer Transformer

10BASE-T

Port 2

10BASE-T

Port 3

10BASE-T

Port 4

TransformerTransformer TransformerTransformerTransformer

10BASE-T

Port 5

Transformer

10BASE-T

Port 6

20MHz

Oscillator

or Crystal

10BASE-T

Port 7

Inter Repeater Bus

(Optional)

10BASE-T

Port 8

AUI

Port

©1997 National Semiconductor Corporation

www.national.com

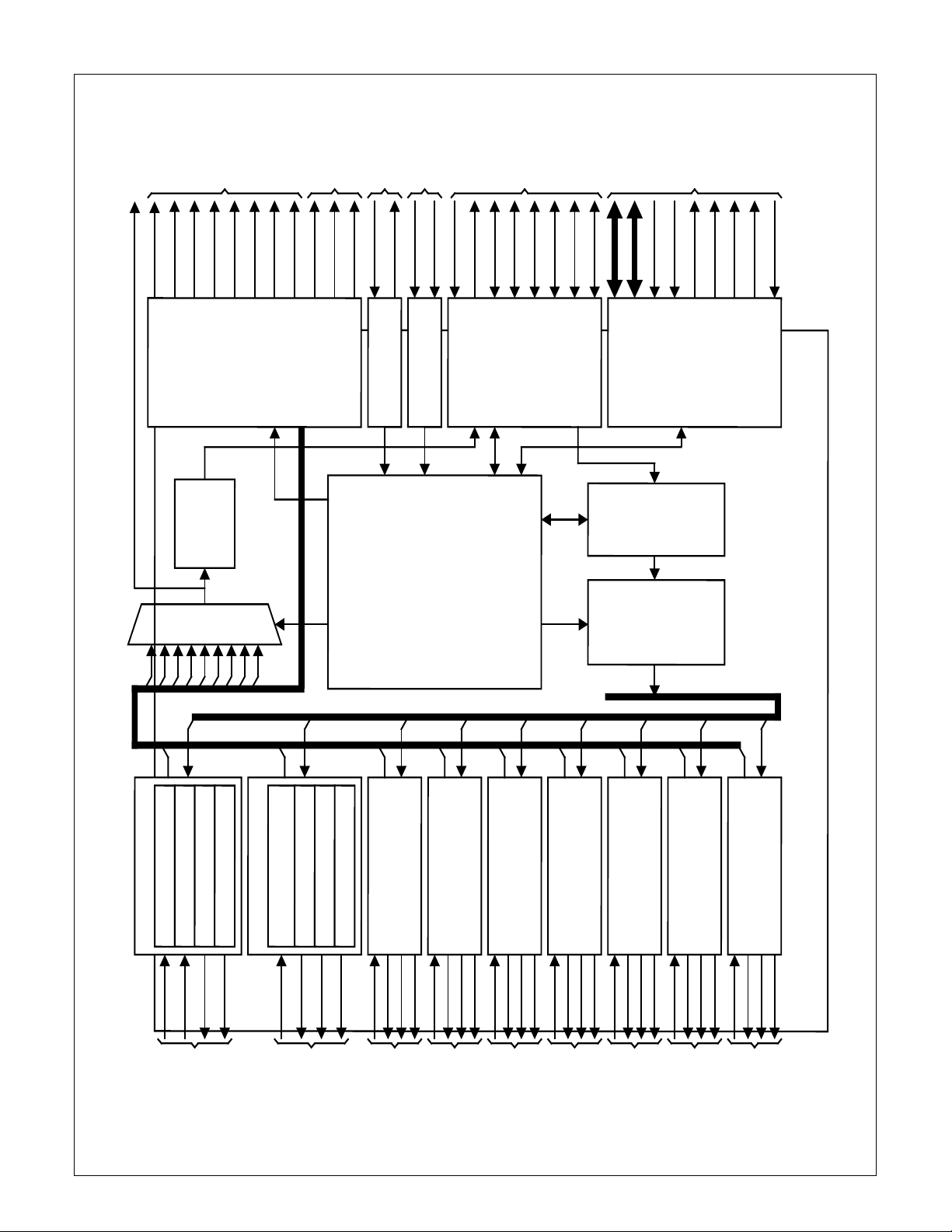

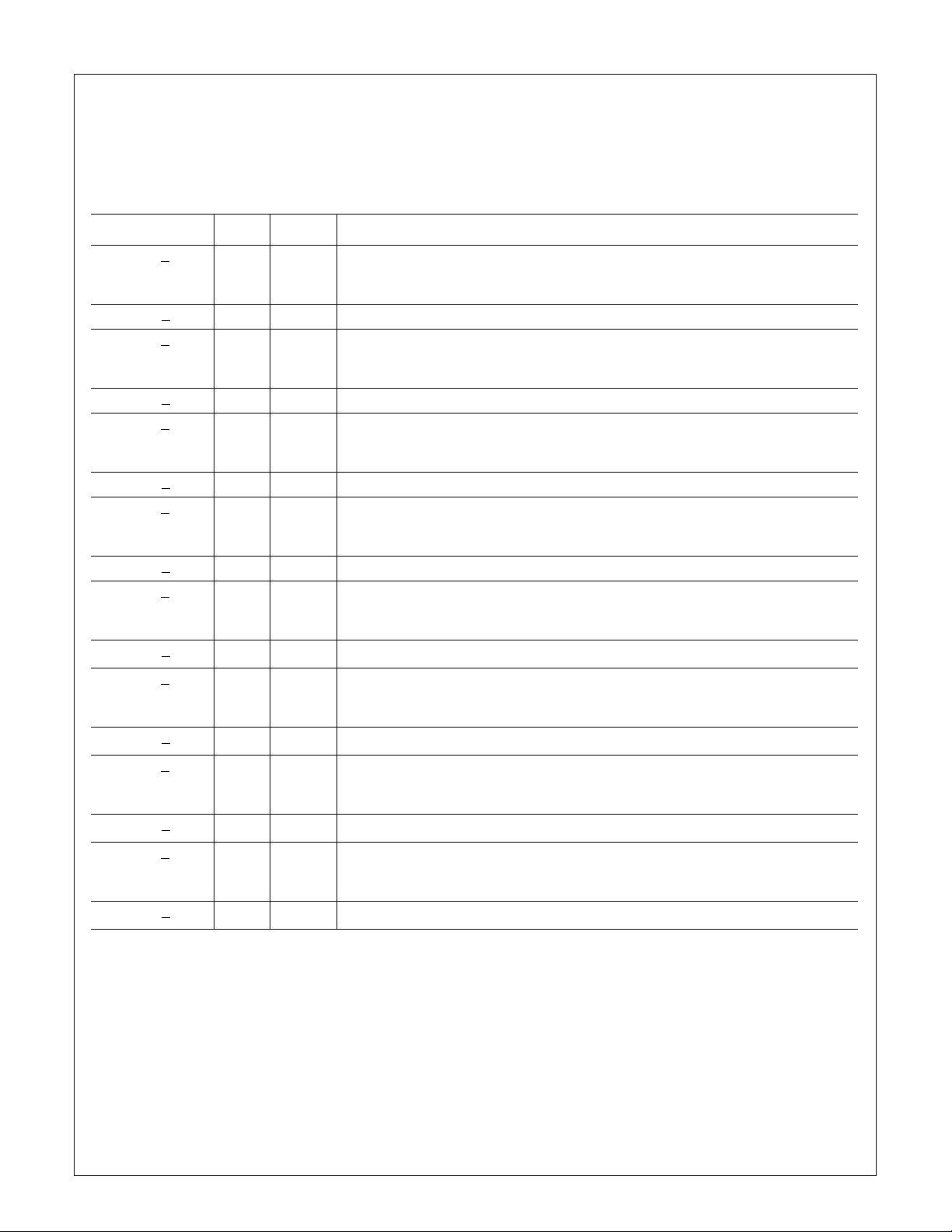

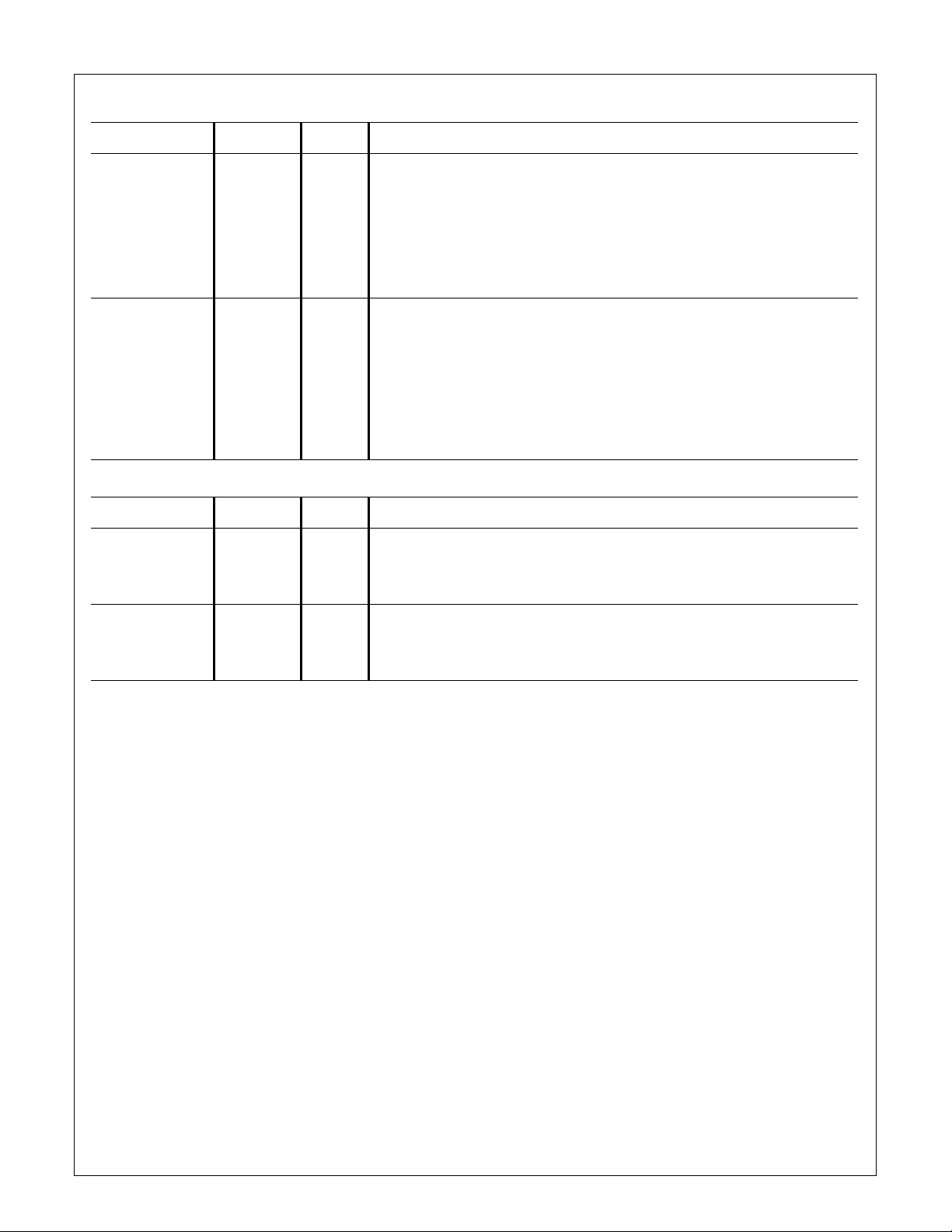

2.0 Block Diagram

LEDs

Traffic

Bargraph

RXM

/TRAF2

/TRAF4

/TRAF1

/TRAF3

/TRAF5

/TRAF6

/TRAF7

/TRAF8

/ALERT

LEDs

Global

/GCOL

/GACT

X_IN

Clock

X_OUT

Reset

/ACKI

/MLOAD

RST_INT/EXT

/ACKO

IRD

Inter-

/IRE

Bus

LERIC

IRC

/COLN

/ACTN

RA[4:0]

/ANYXN

D[3:0]

/RD

/WR

Status

Config/

READY

Bus

/STR

DFS

BUFEN

DEF/OPT

Traffic

Monitor

Decoder

Manchester

RX

Mux

LED

Interface

Crystal

Oscillator

Reset

Generator

Bus

Interface

Inter-LERIC

and Timers

Repeater Main State Machine

Compatible

& DP83955/6

Configuration

Buffer

Elasticity

and

Encoder

TX De-Mux

Manchester

Interface

& Register

Status/LED

DP83959 LERIC8

AUI Port 0

AUI Interface

RX0+/-

Port State Machine

Port Partition Logic

Port Status Register/LED Driver

TX0+/-

CD0+/-

/PART0

AUI

Port 0

10BASE-T Port 1

with Waveshaping

Port State Machine

Twisted Pair Transceiver

RX1+/-

Port Partition Logic

TX1+/-

P/L_1A

Port 1

10BASE-T

10BASE-T Port 2

Port Status Register/LED Driver

P/L_1B

TX2+/-

RX2+/-

10BASE-T

P/L_2B

P/L_2A

Port 2

TX3+/-

RX3+/-

2

10BASE-T Port 3

TX4+/-

RX4+/-

P/L_3B

P/L_3A

Port 3

10BASE-T

10BASE-T Port 4

TX5+/-

RX5+/-

P/L_4B

P/L_4A

Port 4

10BASE-T

10BASE-T Port 5

TX6+/-

RX6+/-

P/L_5B

P/L_5A

Port 5

10BASE-T

10BASE-T Port 6

TX7+/-

RX7+/-

P/L_6B

P/L_6A

Port 6

10BASE-T

10BASE-T Port 7

TX8+/-

RX8+/-

P/L_7B

P/L_7A

Port 7

10BASE-T

10BASE-T Port 8

P/L_8B

P/L_8A

Port 8

10BASE-T

www.national.com

Table of Contents

1.0 System Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1

2.0 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2

3.0 Pin Connection Diagram . . . . . . . . . . . . . . . . . . . . . . . . .4

4.0 Pin Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5

4.1 AUI Port (Port 0) . . . . . . . . . . . . . . . . . . . . . . . . . . .5

4.2 Twisted Pair Ports (Ports 1 - 8) . . . . . . . . . . . . . . . . 5

4.3 Status LED Interface . . . . . . . . . . . . . . . . . . . . . . . .7

4.4 Inter-LERIC Bus Interface . . . . . . . . . . . . . . . . . . . .9

4.5 Clock Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . .10

4.6 Register/Configuration Interface . . . . . . . . . . . . . .11

4.7 Miscellaneous Pins . . . . . . . . . . . . . . . . . . . . . . . .12

4.8 Power and Ground Pins . . . . . . . . . . . . . . . . . . . . .13

5.0 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . 14

5.1 Repeater Main State Machine & Timers . . . . . . . .14

5.2 Port State Machines . . . . . . . . . . . . . . . . . . . . . . . .14

5.3 Receive Multiplexer . . . . . . . . . . . . . . . . . . . . . . . .14

5.4 Manchester Decoder 1 . . . . . . . . . . . . . . . . . . . . . . .4

5.5 Elasticity Buffer . . . . . . . . . . . . . . . . . . . . . . . . . . .14

5.6 Transmit DE-Multiplexer & Manchester Encoder . . 15

5.7 Inter-LERIC Bus Interface . . . . . . . . . . . . . . . . . . .15

5.8 Clock Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . .15

5.9 Reset Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . .15

5.10 Traffic Monitor LED Interface . . . . . . . . . . . . . . . . .16

5.11 Port Status LEDs . . . . . . . . . . . . . . . . . . . . . . . . . .18

5.12 Configuration/Register Interface . . . . . . . . . . . . . .18

5.13 Min/Max Mode LED Interface . . . . . . . . . . . . . . . .19

5.14 AUI Port 0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .19

5.15 10BASE-T Ports 1-8 . . . . . . . . . . . . . . . . . . . . . . .19

6.0 LERIC8 Registers 22

6.1 Register Address Map . . . . . . . . . . . . . . . . . . . . . 22

6.2 LERIC8 Status Register . . . . . . . . . . . . . . . . . . . . 23

6.3 Port 0 (AUI) Status/Configuration Register . . . . . . 24

6.4 Ports 1-8 (10BASE-T) Status/Configuration

Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

7.0 System Considerations . . . . . . . . . . . . . . . . . . . . . . . . 26

7.1 Cascading . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

7.2 IEEE Conformance . . . . . . . . . . . . . . . . . . . . . . . . 26

8.0 DC Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

9.0 Switching Characteristics . . . . . . . . . . . . . . . . . . . . . . 28

9.1 Port Arbitration . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

9.2 Receive - AUI Port . . . . . . . . . . . . . . . . . . . . . . . . 28

9.3 Receive - 10BASE-T Ports . . . . . . . . . . . . . . . . . . 29

9.4 Transmit - AUI Port . . . . . . . . . . . . . . . . . . . . . . . . 29

9.5 Transmit - 10BASE-T Ports . . . . . . . . . . . . . . . . . 30

9.6 Collision - AUI Port . . . . . . . . . . . . . . . . . . . . . . . . 30

9.7 Collision - 10BASE-T Ports . . . . . . . . . . . . . . . . . 31

9.8 Collision - All Ports - Inter-LERIC Bus . . . . . . . . . 32

9.9 Collision - All Ports - One Port Left . . . . . . . . . . . . 32

9.10 Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

9.11 LED Strobe . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

9.12 Register Read . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

9.13 Register Write . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

9.14 Inter-LERIC Bus (Packet Output) . . . . . . . . . . . . . 36

9.15 Inter-LERIC Bus (Packet Input) . . . . . . . . . . . . . . 36

10.0 AC Timing Test Conditions . . . . . . . . . . . . . . . . . . . . . 37

10.1 General Test Conditions . . . . . . . . . . . . . . . . . . . . 37

10.2 Capacitance. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

11.0 Physical Dimensions . . . . . . . . . . . . . . . . . . . . . . . . . . 38

3

www.national.com

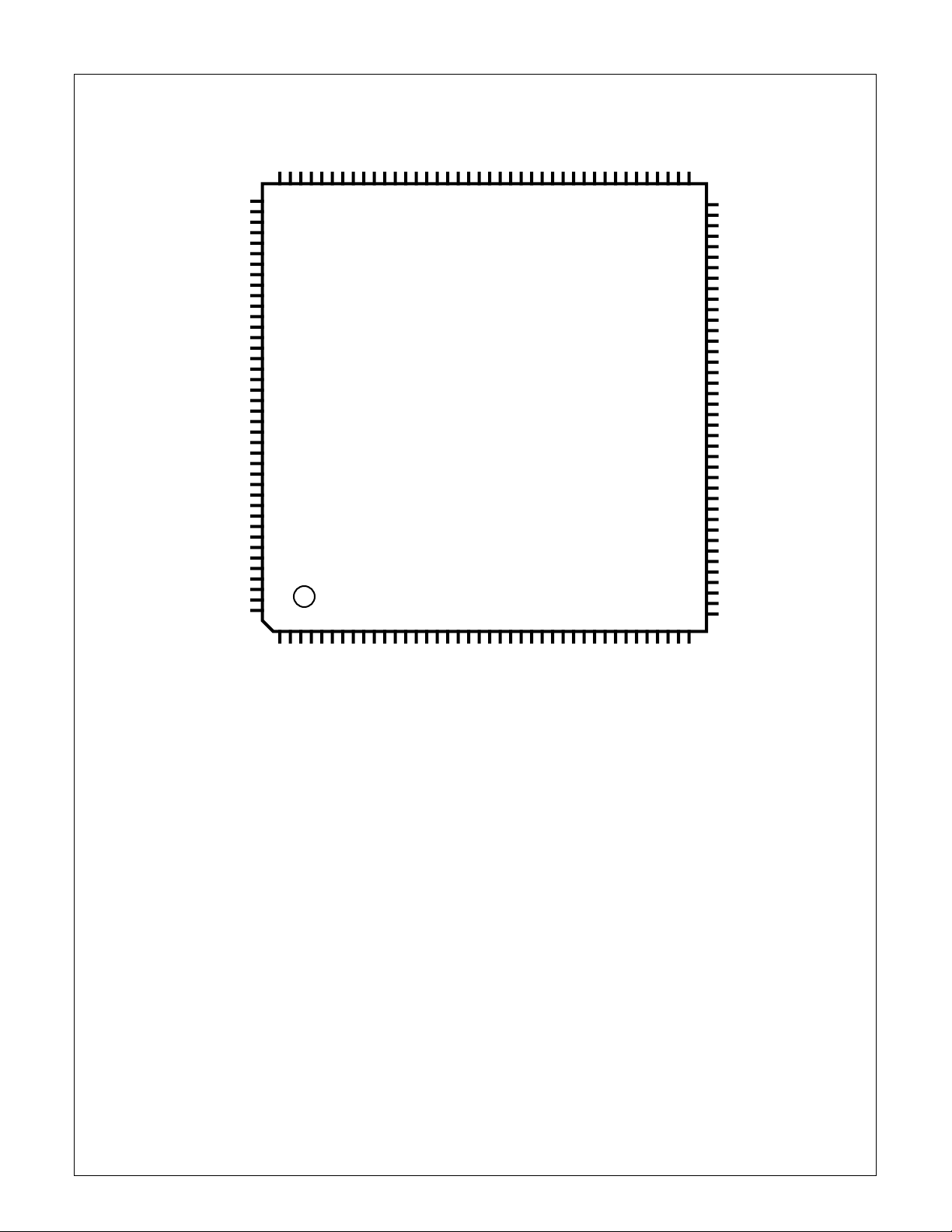

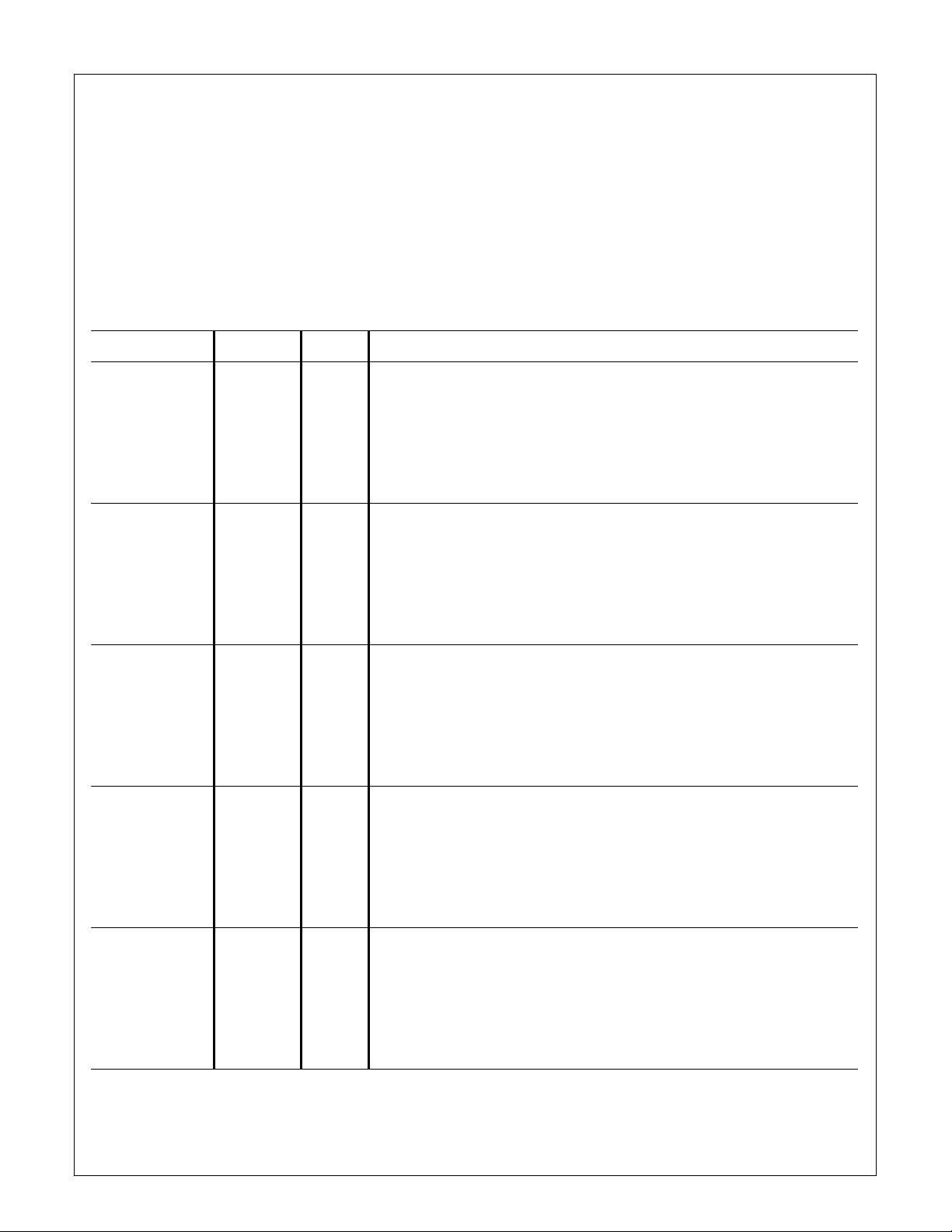

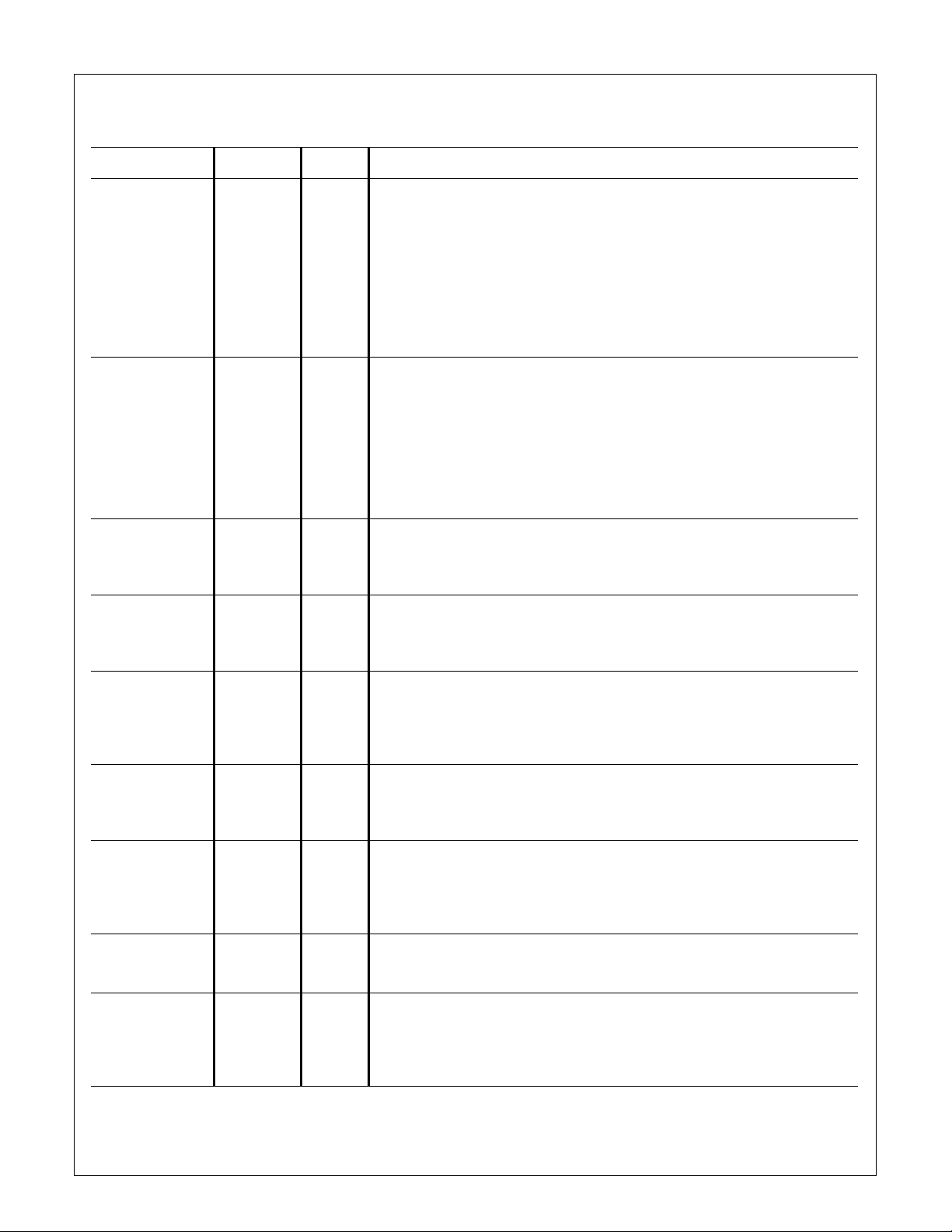

3.0 Pin Connection Diagram

NC

TX3+

TX3GND_P3

VCC_P3

RX3+

RX3-

RX2+

RX2VCC_P2

GND_P2

TX2+

TX2-

TX1+

TX1GND_P1

VCC_P1

RX1+

RX1-

GND_OSC

VCC_OSC

/MLOAD_

RST_INT/EXT

X_IN

X_OUT

VCC

GND

GND_LED

/ALERT

/TRAF1

/TRAF2

/TRAF3

GND_LED

/TRAF4

/TRAF5

/TRAF6

GND_LED

/TRAF7

/TRAF8

NC

121

122

123

124

125

126

127

128

129

130

131

132

133

134

135

136

137

138

139

140

141

142

143

144

145

146

147

148

149

150

151

152

153

154

155

156

157

158

159

160

NC

120

1

119

2

NC

TX4-

118

3

TX4+

117

4

116

5

VCC_P4

RX4-

GND_P4

115

114

7

6

RX4+

TEST_EN

113

112

8

9

TEST_4

RTX

GND_ANLG

VCC

VCC_ANLG

GND

REQ

TEST_3

109

105

108

107

106

104

111

110

DP83959VUL

LERIC8

160 pin PQFP

11

15

12

16

13

10

17

14

TEST_2

TEST_5

FIL_TTL

RX5-

101

100

103

102

Top View

19

20

21

18

RX5+

VCC_P5

98

99

22

23

TX5+

GND_P5

TX5-

97

96

95

26

24

25

TX6-

94

27

TX6+

GND_P6

93

92

28

29

VCC_P6

RX6-

RX6+

90

89

91

30

31

32

RX7-

88

33

RX7+

VCC_P7

86

87

34

35

TX7+

GND_P7

TX7-

85

84

83

38

36

37

NC

NC

82

81

80

NC

TX8-

79

78

TX8+

77

GND_P8

VCC_P8

76

RX8-

75

74

RX8+

73

RX0RX0+

72

CD0-

71

70

CD0+

69

TX0TX0+

68

VCC_AUI

67

66

GND_AUI

65

GND_PLL

VCC_PLL

64

RA4

63

62

RA3

61

RA2

RA1

60

RA0

59

58

VCC

57

GND

D3

56

D2

55

54

D1

53

D0

BUFEN

52

READY

51

50

/COLN

49

/ANYXN

/ACTN

48

GND

47

46

VCC

45

IRD

/IRE

44

IRC

43

42

NC

41

NC

39

40

NC

NC

GND

/GACT

/GCOL

P/L_1A

VCC_LED

P/L_1B

P/L_2A

P/L_2B

GND_LED

P/L_3A

P/L_4A

VCC_LED

GND_LED

P/L_5A

P/L_5B

P/L_6A

P/L_7A

VCC_LED

P/L_6B

P/L_4B

P/L_3B

Order Number DP83959VUL

See NS Package Number VUL160A

P/L_7B

P/L_8A

GND_LED

P/L_8B

TEST_1

/RD

/WR

DEF/OPT

/ACKI

/ACKO

VCC

GND

/STR

DFS

RXM

NC

/PART0

4

www.national.com

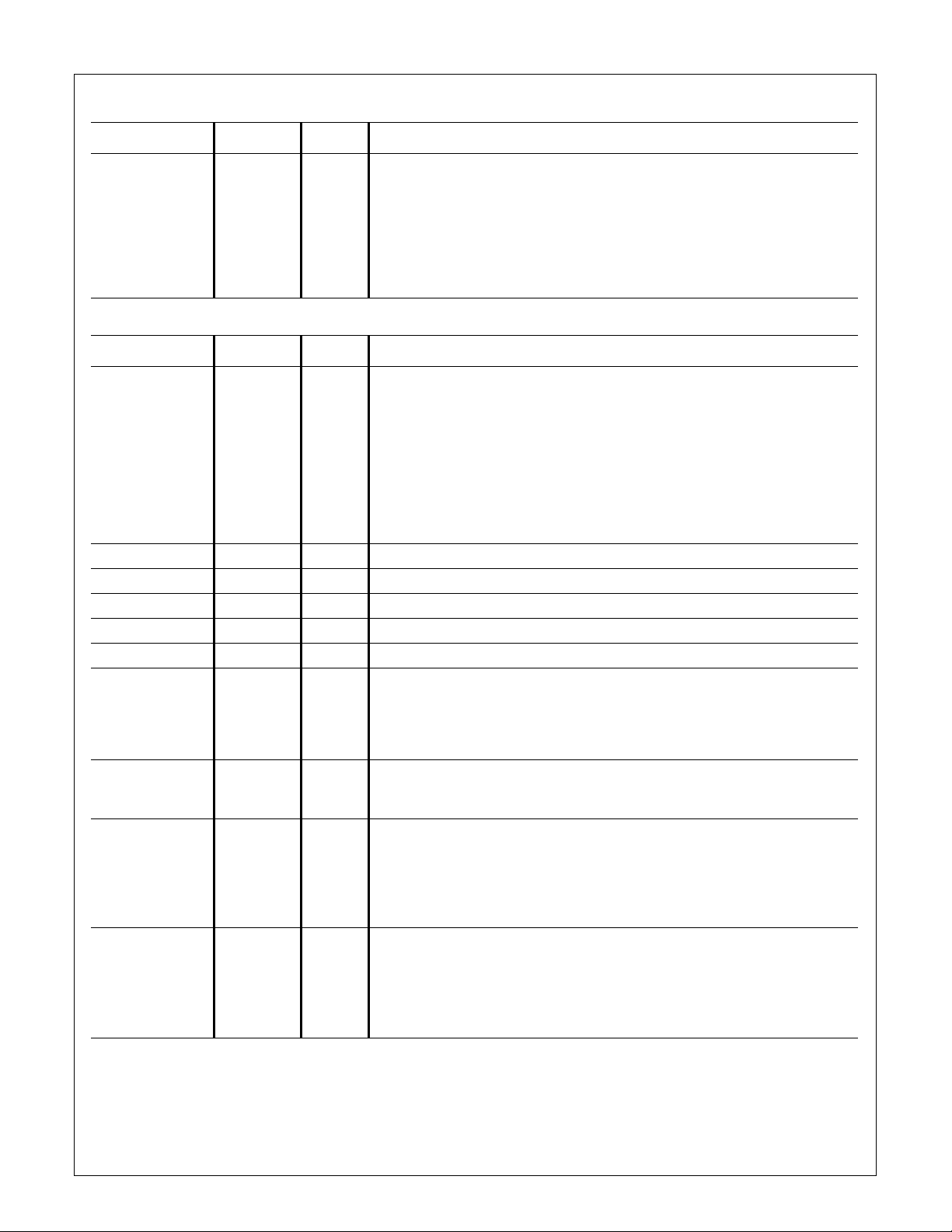

4.0 Pin Descriptions

Key to Pin Type:

O = TTL Compatible Output I/O = TTL Compatible Input/Output

O (ECL) = ECL Compatible Output I/O (O.D.) = TTL Compatible Input/Open Drain Output

I = TTL Compatible Input TPO = Twisted Pair Interface Compatable Output

I (ECL) = ECL Compatible Input TPI = Twisted Pair Interface Compatable Input

OZ = TTL Compatible TRI-STATE

O (O.D.) = Open Drain Output

4.1 AUI PORT (PORT 0)

Signal Name Type Pin # Description

®

Output AI = Analog Input

TX0+ O

(ECL)

TX0- O

(ECL)

RX0+ I

(ECL)

RX0- I

(ECL)

CD0+ I

(ECL)

CD0- I

(ECL)

68 AUI Transmit +: The AUI transmit path includes National Semiconductor's

patented low power dissipation differential drivers that do not need external load

resistors. This output should be connected directly to the AUI isolation tr ansformer.

69 AUI T ransmit -: The AUI transmit path includes National Semiconductor's patented

low power dissipation differential drivers that do not need external load resistors.

This output should be connected directly to the AUI isolation transformer.

72 AUI Receive +: This input should be terminated with 39Ω to GND via a series DC

blocking capacitor (shared with RX0-). Refer to Figure8.

73 AUI Receive -: This input should be terminated with 39Ω to GND via a ser ies DC

blocking capacitor (shared with RX0+). Refer to Figure8.

70 AUI Collision Detect +: This input should be terminated with 39Ω to GND via a

series DC blocking capacitor (shared with CD0-). Refer to Figure 8.

71 AUI Collision Detect -: This input should be terminated with 39Ω to GND via a

series DC blocking capacitor (shared with CD0+). Refer to Figure 8.

4.2 TWISTED PAIR PORTS (PORTS 1 - 8)

Signal Name Type Pin # Description

REQ AI 108 Equalization Resistor: A resistor connected between this pin and GND or V

adjusts the equalization step amplitude on the 10BASE-T Manchester encoded

transmit data for all eight 10BASE-T ports. No resistor is required for operation with

cable length of up to 100 meters.

RTX AI 107 Extended Cable Resistor:A resistor connected between this pin and GND or V

adjusts the amplitude of the differential transmit outputs for all eight 10BASE-T

ports. No resistor is required for operation with cable length of up to 100 meters.

CC

CC

5

www.national.com

4.0 Pin Descriptions (Continued)

The values of the resistor/capacitor parallel source impedance matching networks connected to each of the

10BASE-T transmit outputs will depend upon PCB layout

factors (such as track length, width, route etc.) and will hav e

to be determined for each design. Preliminary laboratory

Signal Name Type Pin # Description

TX1

+ TPO 134, 135 Port 1 Transmit: 10BASE-T transmitter output - requires a series source

impedance matching network consisting of a resistor and capacitor in parallel. The

values of these components will be application specific.

RX1

+ TPI 138, 139 Port 1 Receive: 10BASE-T receiver input - requires a 50Ω receive termination.

+ TPO 132, 133 Port 2 Transmit: 10BASE-T transmitter output - requires a series source

TX2

impedance matching network consisting of a resistor and capacitor in parallel. The

values of these components will be application specific.

RX2

+ TPI 128, 129 Port 2 Receive: 10BASE-T receiver input - requires a 50Ω receive termination.

+ TPO 122, 123 Port 3 Transmit: 10BASE-T transmitter output - requires a series source

TX3

impedance matching network consisting of a resistor and capacitor in parallel. The

values of these components will be application specific.

RX3

+ TPI 126, 127 Port 3 Receive: 10BASE-T receiver input - requires a 50Ω receive termination.

+ TPO 117, 118 Port 4 Transmit: 10BASE-T transmitter output - requires a series source

TX4

impedance matching network consisting of a resistor and capacitor in parallel. The

values of these components will be application specific.

RX4

+ TPI 113, 114 Port 4 Receive: 10BASE-T receiver input - requires a 50Ω receive termination.

+ TPO 95, 96

TX5

Port 5 Transmit: 10BASE-T transmitter output - requires a series source impedance matching network consisting of a resistor and capacitor in parallel. The values

of these components will be application specific.

work suggests that values of 13.5Ω and 820 pF are appropriate in order to meet IEEE 802.3 specifications and EMI

requirements - these values should be taken as a starting

point for investigation. Refer to Figure 9.

RX5

+ TPI 99, 100

TX6+ TPO 93, 94

RX6

+ TPI 89, 90

TX7+ TPO 83, 84

RX7

+ TPI 87, 88

TX8+ TPO 78, 79

RX8

+ TPI 74, 75

Port 5 Receive: 10BASE-T receiver input - requires a 50Ω receive termination.

Port 6 Transmit: 10BASE-T transmitter output - requires a series source imped-

ance matching network consisting of a resistor and capacitor in parallel. The values

of these components will be application specific.

Port 6 Receive: 10BASE-T receiver input - requires a 50Ω receive termination.

Port 7 Transmit: 10BASE-T transmitter output - requires a series source imped-

ance matching network consisting of a resistor and capacitor in parallel. The values

of these components will be application specific.

Port 7 Receive: 10BASE-T receiver input - requires a 50Ω receive termination.

Port 8 Transmit: 10BASE-T transmitter output - requires a series source imped-

ance matching network consisting of a resistor and capacitor in parallel. The values

of these components will be application specific.

Port 8 Receive: 10BASE-T receiver input - requires a 50Ω receive termination.

6

www.national.com

4.0 Pin Descriptions (Continued)

4.3 STATUS LED INTERFACE

All the DP83959's direct drive LED outputs can drive up to

14mA maximum. The LED outputs are intended to drive an

external LED with a series current limiting resistor. The P artition/Link OK LED outputs can sink or source current and

are thus suitable for driving single or bi-color LEDs directly.

Bi-color LEDs can be connected between the A and B outputs (with series current limiting resistors) (see section

5.11).

The direct drive LED outputs are asserted during pow-

er-on/reset (either internal or external reset) and remain as-

Signal Name Type Pin # Description

P/L_1A

P/L_1B

P/L_2A

P/L_2B

O (14mA

max.)

O (14mA

max.)

6

9

10

11

Partition/Link OK LED 1 - A and B: LED outputs (for use with single or

bi-color LEDs) with the following function:

Link Status

/OK

/OK

OK

OK

Partition/Link OK LED 2 - A and B: LED outputs (for use with single or

bi-color LEDs) with the following function:

Link Status

/OK

/OK

OK

OK

serted for 1 second (nominal) following the trailing edge of

the internal/external reset signal. During the LED test at

power-on/reset, the Partition/Link OK 'A' outputs will all be

logic '1' and the 'B' outputs logic '0'.

DP83955/6 compatible LED drive outputs are only asserted

for the duration of the 1 second LED test following the trailing edge of the internal/external reset (they are not asserted

during reset). The DP83955/6 compatible status LED

scheme is described in the functional description

(Section 5.13) as it requires external circuitry to latch the

status and drive the LEDs.

Partition Status

/PART

PART

/PART

PART

Partition Status

/PART

PART

/PART

PART

A Output

1

1

0

1

A Output

1

1

0

1

B Output

1

1

1

0

B Output

1

1

1

0

P/L_3A

P/L_3B

P/L_4A

P/L_4B

P/L_5A

P/L_5B

O (14mA

max.)

O (14mA

max.)

O (14mA

max.)

12

13

14

17

18

19

Partition/Link OK LED 3 - A and B: LED outputs (for use with single or

bi-color LEDs) with the following function:

Link Status

/OK

/OK

OK

OK

Partition/Link OK LED 4 - A and B: LED outputs (for use with single or

bi-color LEDs) with the following function:

Link Status

/OK

/OK

OK

OK

Partition/Link OK LED 5 - A and B: LED outputs (for use with single or

bi-color LEDs) with the following function:

Link Status

/OK

/OK

OK

OK

Partition Status

/PART

PART

/PART

PART

Partition Status

/PART

PART

/PART

PART

Partition Status

/PART

PART

/PART

PART

A Output

1

1

0

1

A Output

1

1

0

1

A Output

1

1

0

1

B Output

1

1

1

0

B Output

1

1

1

0

B Output

1

1

1

0

7

www.national.com

4.0 Pin Descriptions (Continued)

Signal Name Type Pin # Description

P/L_6A

P/L_6B

P/L_7A

P/L_7B

P/L_8A

P/L_8B

/TRAF1 O (14mA

/TRAF2 O (14mA

/TRAF3 O (14mA

/TRAF4 O (14mA

/TRAF5 O (14mA

/TRAF6 O (14mA

/TRAF7 O (14mA

/TRAF8 O (14mA

/ALERT O (14mA

O (14mA

max.)

O (14mA

max.)

O (14mA

max.)

max.)

max.)

max.)

max.)

max.)

max.)

max.)

max.)

max.)

20

21

22

25

26

27

150 Traffic Monitor LED 1 (1%):

151 Traffic Monitor LED 2 (2%):

152 Traffic Monitor LED 3 (3%):

154 Traffic Monitor LED 4 (6%):

155 Traffic Monitor LED 5 (12%):

156 Traffic Monitor LED 6 (25%):

158 Traffic Monitor LED 7 (50%):

159 Traffic Monitor LED 8 (>80%):

149 Alert LED: This LED output indicates that greater than 80% traffic level for

Partition/Link OK LED 6 - A and B: LED outputs (for use with single or

bi-color LEDs) with the following function:

Link Status

/OK

/OK

OK

OK

Partition/Link OK LED 7 - A and B: LED outputs (for use with single or

bi-color LEDs) with the following function:

Link Status

/OK

/OK

OK

OK

Partition/Link OK LED 8 - A and B: LED outputs (for use with single or

bi-color LEDs) with the following function:

Link Status

/OK

/OK

OK

OK

0 = 1% Traffic Level reached or exceeded

1 = Traffic Level less than 1%

0 = 2% Traffic Level reached or exceeded

1 = Traffic Level less than 2%

0 = 3% Traffic Level reached or exceeded

1 = Traffic Level less than 3%

0 = 6% Traffic Level reached or exceeded

1 = Traffic Level less than 6%

0 = 12% Traffic Level reached or exceeded

1 = Traffic Level less than 12%

0 = 25% Traffic Level reached or exceeded

1 = Traffic Level less than 25%

0 = 50% Traffic Level reached or exceeded

1 = Traffic Level less than 50%

0 = >80% Traffic Level reached or exceeded

1 = Traffic Level less than 80%

one second or more has occurred, or a 10BASE-T port partition has occurred.

The output remains active until the current event condition ceases or, if the

event condition is shorter than 30ms, for a minimum of 30ms (nominal value).

Active low.

Partition Status

/PART

PART

/PART

PART

Partition Status

/PART

PART

/PART

PART

Partition Status

/PART

PART

/PART

PART

A Output

1

1

0

1

A Output

1

1

0

1

A Output

1

1

0

1

B Output

1

1

1

0

B Output

1

1

1

0

B Output

1

1

1

0

8

www.national.com

4.0 Pin Descriptions (Continued)

Signal Name Type Pin # Description

/PART0 O (14mA

39 Partition LED 0: Partition LED output for the AUI port. Active low.

max.)

/GCOL O (14mA

max.)

4 Global Collision LED: Global collision status LED output. Indicates collision

activity on any port. Active low. This output will be asserted low until the start

of the next network event or for a maximum of 30ms (nominal value).

/GACT O (14mA

max.)

5 Global Activity LED: Global Activity LED output. Indicates receive activity

(carrier sense active) on any port. Active low. This output will be asserted low

until the start of the next network event or for a maximum of 30ms (nominal

value).

4.4 INTER-LERIC BUS INTERFACE

Signal Name Type Pin # Description

/ACKI I 32 Acknowledge Input: to the network ports' arbitration chain. If the Inter-LERIC

bus is not being used or if this LERIC8 is at the top of the /ACKI - /A CKO chain

or is the only repeater chip in the system, this pin should be connected to V

either directly or via a pull-up resistor (≈ 4.7 kΩ). Otherwise, this input should

be driven from the previous LERIC8's /ACKO output.

/ACKO O 33 Acknowledge Output: from the network ports' arbitration chain, connected to

the /ACKI of the next repeater chip in the /ACKI - /ACKO chain. If this LERIC8

is not chained to any other repeater chips, this pin should be left unconnected.

IRD I/O 45 Inter-LERIC Data: When asser ted as an output this signal provides a serial

data stream in NRZ format. The signal is asserted by a LERIC8 when it is

receiving data from one of its network segments. The default condition of this

signal is to be an input. In this state it may be driven by other devices on the

Inter-LERIC bus. If the Inter-LERIC bus is not being used, this pin should be

left unconnected (it has an internal pull-up resistor of 14 kΩ) or pulled up to

V

via an external resistor.

CC

/IRE I/O 44 Inter-LERIC Enable: When asserted as an output this signal provides an

activity framing enable for the serial data stream. The signal is asserted by a

LERIC8 when it is receiving data from one of its network segments. The

default condition of this signal is to be an input. In this state it may be driven b y

other devices on the Inter-LERIC bus. If the Inter-LERIC bus is not being

used, this pin should be left unconnected (it has an internal pull-up resistor of

14 kΩ) or pulled up to V

be used, this signal should have an external 680Ω pull-up resistor to ensure

fast de-assertion.

IRC I/O 43 Inter-LERIC Clock: When asserted as an output this signal provides a clock

signal for the serial data stream. Data (IRD) is changed on the falling edge of

the clock. The signal is asserted by a LERIC8 when it is receiving data from

one of its network segments. The default condition of this signal is to be an

input. When an input, IRD is sampled on the rising edge of the clock. In this

state it may be driven by other devices on the Inter-LERIC bus. If the

Inter-LERIC bus is not being used, this pin should be left unconnected (it has

an internal pull-up resistor of 14 kΩ) or pulled up to V

resistor.

/COLN I/O 50 Collision on Port N: This denotes that a collision is occurring on the port

receiving the data packet (Port N). The default condition of this signal is to be

an input. In this state it may be driven by other devices on the Inter-LERIC

bus. If the Inter-LERIC bus is not being used, this pin should be left

unconnected (it has an internal pull-up resistor of 3.5 kΩ) or pulled up to V

via an external resistor. If the Inter-LERIC bus is to be used, this signal should

have an external 680Ω pull-up resistor to ensure fast de-assertion.

via an external resistor. If the Inter-LERIC b us is to

CC

via an external

CC

CC

CC

9

www.national.com

4.0 Pin Descriptions (Continued)

Signal Name Type Pin # Description

/ACTN I/O (O.D.) 48 Activity on Port N: The LERIC8 asser ts this signal when data or collision

information is received from one of its network segments. The LERIC8 senses

this signal when this or another LERIC8 in a multi-LERIC system is receiving

data or collision information. If the Inter-LERIC bus is not being used, this pin

should be left unconnected (it has an internal pull-up resistor of 3.5 kΩ) or

pulled up to V

this signal should have an external 680Ω pull-up resistor to ensure fast

de-assertion.

/ANYXN I/O (O.D.) 49 Activity on Any Port Except Port N: The LERIC8 asserts this signal when a

transmit collision is experienced or multiple ports have active collisions on

their network segments. The LERIC8 senses this signal when this or another

LERIC8 in a multi-LERIC system is experiencing transmit collisions or multiple

ports have active collisions on their network segments. If the Inter-LERIC bus

is not being used, this pin should be left unconnected (it has an internal

pull-up resistor of 14 kΩ) or pulled up to V

Inter-LERIC bus is to be used, this signal should have an external 680Ω

pull-up resistor to ensure fast de-assertion.

4.5 CLOCK INTERFACE

Signal Name Type Pin # Description

X_IN I 144 20 MHz Crystal Oscillator Input: This pin can be used to connect an

external 20MHz crystal (between X_IN and X_OUT) as shown in Figure 2, or

as an external TTL compatible 20MHz oscillator module input as shown in

Figure 3.

X_OUT O 145 20 MHz Crystal Oscillator Output: This pin is used to connect to an external

20 MHz crystal (between X_IN and X_OUT) as shown in Figure 2. When

using an external 20 MHz crystal oscillator module connected to the X_IN

input, this pin should be left unconnected as shown in Figure 3.

via an external resistor. If the Inter-LERIC bus is to be used,

CC

via an external resistor. If the

CC

10

www.national.com

4.0 Pin Descriptions (Continued)

4.6 REGISTER/CONFIGURATION INTERFACE

Signal Name Type Pin # Description

RA4

RA3

RA2

RA1

RA0

D3

D2

D1

D0

/RD I 31 Read Strobe: When strobed low, this input schedules a register read access

/WR I 30 Write Strobe: When strobed low, this input schedules a register write access

/READY O 51 Ready Handshake: The falling edge of this active low signal during a read

/STR O 36 Display Update Str obe:When using the DP83955/6 compatible status LEDs,

DFS O 37 Display Frozen Strobe: Asserted high when the display data for each pac k et

BUFEN O 52 Buffer Enable: Used to control an external buffer (if required) for the data

/MLOAD I 142 Mode Load/Reset: TTL level reset input (not Schmitt) for external reset or

I/O 63

62

61

60

59

I/O 56

55

54

53

Register Address [4:0]: Address input value for the current register access.

These pins also provide DP83955/6 compatible LED status: during display

update cycles these pins become outputs that provide port address and data

for LED display purposes. Pins RA[1:4] cycle values from 0h to 9h while RA0

provides Bad Polarity status for the 10BASE-T ports. See Section 5.13 for

more details. If the DP83955/6 compatible LEDs and register interface are not

being used, these pins should be left unconnected.

In Option mode (see DEF/OPT), the logic levels present on RA[4:0] at reset

(set by pull-up or pull-down resistors) are latched into the configuration

registers. See section 5.12 for more information.

Data [3:0]: Bi-directional register data. /RD and /WR control the data

direction. With /RD low and /WR high, D[3:0] are outputs and with /RD high

and /WR low, D[3:0] are inputs. These pins also provide the DP83955/6

compatible status outputs for latching to LEDs. See Section 5.13 for more

details. If the DP83955/6 compatible LEDs and register interface are not being

used, these pins should be left unconnected.

In Option mode (see DEF/OPT), the logic levels present on D[3:0] at reset (set

by pull-up or pull-down resistors) are latched into the configuration registers.

See Section 5.12 for more information.

to the register addressed by the RA[4:0] pins. If the register interface is not

being used, this pin should be connected to V

resistor (≈4.7 kΩ).

to the register addressed by the RA[4:0] pins. If the register interface is not

being used, this pin should be connected to V

resistor (≈4.7 kΩ).

cycle indicates that data is stable and valid for sampling. In write cycles, the

falling edge of /READY denotes that the write data has been latched by the

LeRIC8. Therefore, data must have been available and stable for this

operation to be successful.

this active low signal controls the latching of display data f or network ports into

the external display latches. If not required, this pin should be left

unconnected.

is frozen at the end of the repeater transmission of the packet until the start of

the next network event or for a maximum of 30ms (nominal value). This

ensures DP83955/6 compatible status LEDs are visible even for single

network events.

bus, D[3:0]. Extermal buffer will be necessary in systems having a register

interface.

test purposes. If not required, this pin should be connected to V

directly or via a pull-up resistor (≈4.7 kΩ). On the rising (trailing) edge of

/MLOAD, the logic levels present on the D[3:0] and RA[4:0] inputs (set by

pull-up or pull-down resistors) are latched into the configuration registers.

either directly or via a pull-up

CC

either directly or via a pull-up

CC

CC

either

11

www.national.com

4.0 Pin Descriptions (Continued)

Signal Name Type Pin # Description

RST_INT/EXT I 143 RESET Internal or External: This pin is used to select either internal

(automatic) or external reset mode. External reset pulses should be applied to

the /MLOAD pin. If not used, this pin should be connected to V

directly or via a pull-up resistor (≈4.7 kΩ).

0 = External reset selected

1 = Internal reset selected

The rising edge of the external (/MLOAD) or internal reset signal starts the 1

second display test operation.

4.7 MISCELLANEOUS PINS

Signal Name Type Pin # Description

DEF/OPT I 29 Default/Optional Configuration Mode: This input is used to select the

LERIC8 configuration mode:

1 = Default Mode - The default LERIC8 configuration is used. To select this

mode the DEF/OPT pin should be pulled up to V

resistor. See Section 5.12 for a description of the default parameters.

0 = Optional Mode - The LERIC8's configuration is loaded into the device at

the trailing edge of reset from values set on the D[3:0] and RA[4:0] pins.

These values are set using 10 kΩ pull-up or pull-down resistors. For

normal default mode, no resistors are required.

TEST_1 I 28 Test 1: This pin should be connected to V

TEST_2 I 103 Test 2: This pin should be connected to GND for normal operation.

TEST_3 O 104 Test 3: This pin should be left unconnected for normal operation.

TEST_4 I 111 Test 4: This pin should be connected to GND for normal operation.

TEST_5 I 102 Test 5: This pin should be connected to GND for normal operation.

TEST_EN I 112 Test Enable: This pin selects between normal and factory test operation

modes:

0 = Normal operation - tie the TEST_EN pin to GND for normal operation.

1 = LERIC8 factory test mode - do not use.

RXM O 38 Receive Manchester Data: This pin should be left unconnected for normal

operation. It is the receive Manchester data output and is supplied for

evaluation and testing purposes.

FIL_TTL I 101 Filter /TTL Transmit Data: This pin selects between pre-filter TTL transmit

data and normal filtered analog transmit data. Connect this pin to GND for

normal operation.

0 = Normal Analog Transmit Data - Transmit outputs are normal 10BASE-T.

1 = Pre-Filter TTL Transmit Data - Transmit outputs become TTL level.

NC - 1, 2, 40,

41, 42,

80, 81,

82, 119,

120,

121, 160

No Connect: These pins are not connected internally to the DP83959. They

should be connected directly to the PCB ground plane. This will help decrease

the thermal resistance between the device and its environment.

for normal operation.

CC

CC

CC

with a 4.7 kΩ

either

12

www.national.com

Loading...

Loading...