PRELIMINARY

DP83953 (RIC2A)

Repeater Interface Controller with Security Features,

Internal Drivers and Integrated Filters

DP83953 (RIC2A) Repeater Interface Controller with Security Features, Internal Drivers and Integrated Filters

March 1998

General Description

The DP83953 Repeater Interface Controller with Security

Features and Integrated Transmit Filters (RIC2A) is an enhanced v ersi on of t he DP83952 Repeat er Inter f ace Control ler with Security Features (RIC II). The RIC2A integrates

driver and f il ter circuitry into the RIC II design.

The functionality of the RIC2A is essentially similar to the

RIC II, but the pin definitions have been modified to reflect

the added integrated drivers and filters. Additionally, the

power and ground pin locations have been rearranged.

Therefore, the RIC2A is not a drop in replacement for the

RIC ll.

The RIC2A is National Semiconductor’s managed repeater

solution designed to comply with IEEE 802.3 Repeater

Specifica tions. Segment partiti on and jabber loc kup protection state machines are implemented in accordance with

this standard. The RIC2A has thirteen network interface

ports available, including an AUI compatible port. The AUI

port incorporates driv ers to connect an ext ernal MAU using

maximum length cable. Similarly, the other twelve interface

ports integrat e 10BASE- T t ransc eiv ers with supporting dri ver and transmit filter circuitry. (continued)

Features

Fully compliant with the IEEE 802.3 Repeater Specification

12 IEEE 802.3 10BASE-T compatible ports with built-in

drivers and analog transmit filters; additional external

isolation transformers are required to implement hubs

1 IEEE 802.3 compatible AUI port

Cascadable for la rger hub applications

On chip Elasticity Buffer, Manchester encoder and decoder

Separate Partition state machines for each port

Compatible with 802.3k Hub Management requirements

LED displays to provide port status information, including receive, collision, partition, jabber and link status,

Power-up configuration options

Repeater and Partition Specifications, Status Display,

Processor Operati ons

Simple processor interface for repeater management

and port disable.

On-chip Event Counte rs and Event Flag Arrays

Serial Management Bus Interface to combine packet

and repeater status information

Single 5V supply

The Security Features

Prevents unauthorized eavesdropping and/or intrusion

on a per port basis

58 On Chip CAMs (Content Addressable Memory) allow storage of acceptable addresses

Learn mode automatically records addresses of attached node

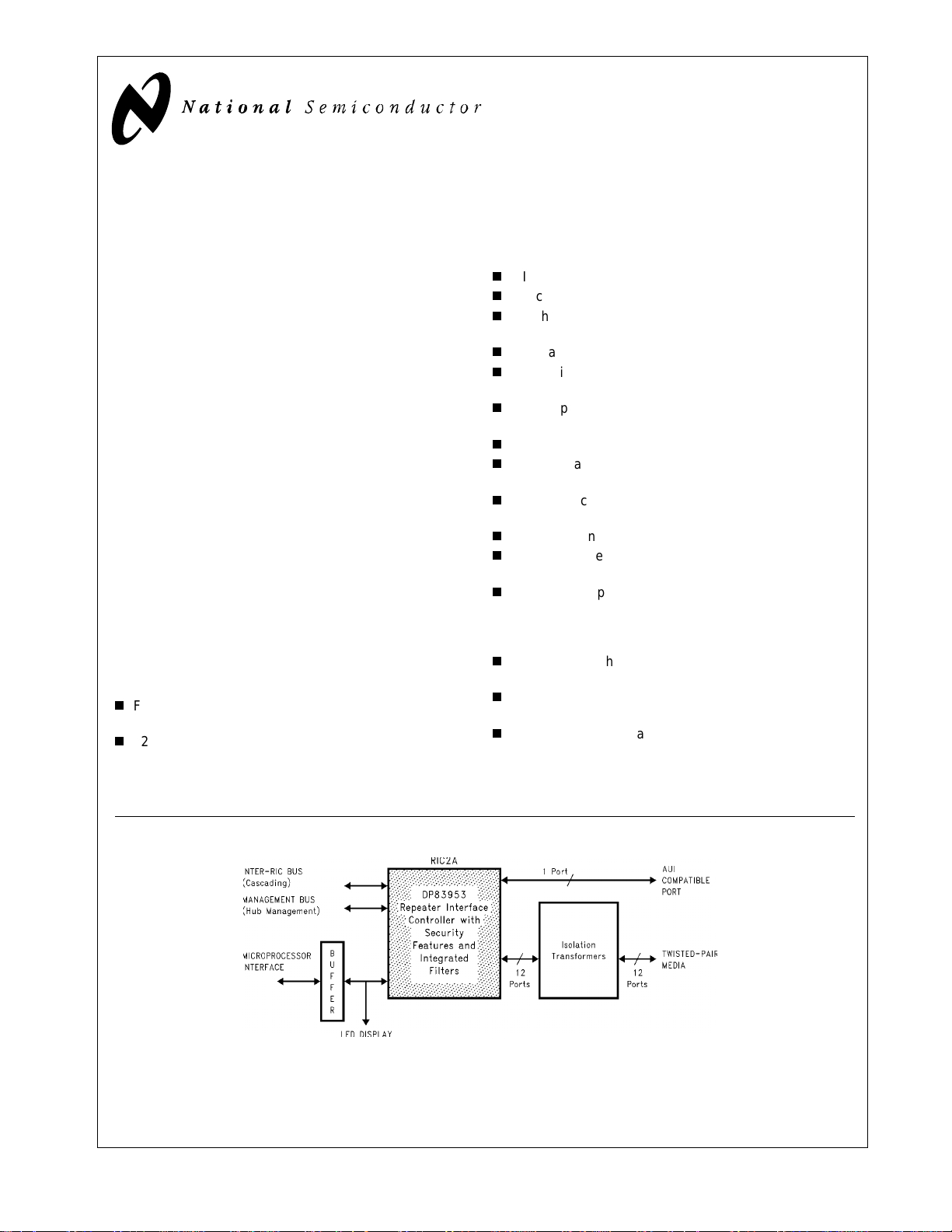

System Diagram

FAST® and TRI-STATE® are registered trademarks of National Semiconductor Corporation.

™

is a trademark of National Semiconductor Corporation

100RIC

™

SONIC

is a trademark of National Semiconductor Corporation

Ethernet is a trademark of Xerox Corporation

is a registered trademark of Lattice Semiconductor

GAL

®

PAL

is a registered trademark of and license from Advanced Micro Devices, Inc.

®

© 1998 National Semiconduct or Corporation

www.national.com

General Description

(continued)

The RIC2A repeater consists of two major functional

blocks: The segment specific block and the shared functional b locks. The segment specific b lock incorporates relevant IEEE specifications on a per port basis. The shared

functional bl ocks incorporate core logic for the entire IEEE

repeater unit. The core logic blocks consist of a repeater

receive multiple xor, a phase locked loop (PLL), a Manches ter decoder, an elasticity buffer, a transmit encoder and a

demultip lexor.

A larger repeater system may be constructed by cascading

several RIC2A devices via the Inter-RIC bus. This method

Table of Contents

1.0 Connection Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

2.0 Pin Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

3.0 Block Diagrams . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

4.0 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . 12

4.1 Summary of DP83953 RIC2A Feature

Enhancements from DP83952 RIC II . . . . . . . . . 12

4.2 Overview Of RIC2A Functions . . . . . . . . . . . . . . . 12

4.3 Description Of Repeater Operations . . . . . . . . . . 14

4.4 Examples Of Packet Repetition

Scenarios . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

4.5 Description Of Hardware Connection For Inter-ric

Bus . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

4.6 Processor and Display Interface . . . . . . . . . . . . . 28

4.7 Description Of Hardware Connection For Processor

And Display Interface . . . . . . . . . . . . . . . . . . . . . . 30

of cascading allows the RIC2A system to function as a single repeater unit without introducing additional repeater

hops.

The RIC2A is configurable for specific applications. It provides port status information for LED array displays and a

simple interface for system processors. The RIC2A possesses multifunctional counters and status flag arrays to

facilitate network statistics gathering, as well as a serial

Hub Management Interf ace Bus for collect ing, e v ent dat a in

managed hub applications.

5.0 HUB Management Support . . . . . . . . . . . . . . . . . . . . . 35

5.1 Event Counting Function . . . . . . . . . . . . . . . . . . 35

5.2 Event Record Function . . . . . . . . . . . . . . . . . . . . 36

5.3 Management Interface Operation . . . . . . . . . . . . 37

5.4 Description of Hardware Connection for

Management Interface . . . . . . . . . . . . . . . . . . . . 43

6.0 Port Block Functions . . . . . . . . . . . . . . . . . . . . . . . . . 44

6.1 Transceiver Functions . . . . . . . . . . . . . . . . . . . . 44

6.2 Segment Partition . . . . . . . . . . . . . . . . . . . . . . . . 47

6.3 Port Status Register Functions . . . . . . . . . . . . . . 47

6.4 Local Ports and Expected Activity . . . . . . . . . . . 49

7.0 RIC2A Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

8.0 Board Layout Recommendations . . . . . . . . . . . . . . . 75

9.0 DC and AC Specification . . . . . . . . . . . . . . . . . . . . . . 77

10.0 Physical Dimensions . . . . . . . . . . . . . . . . . . . . . . . . . 90

2 www.national.com

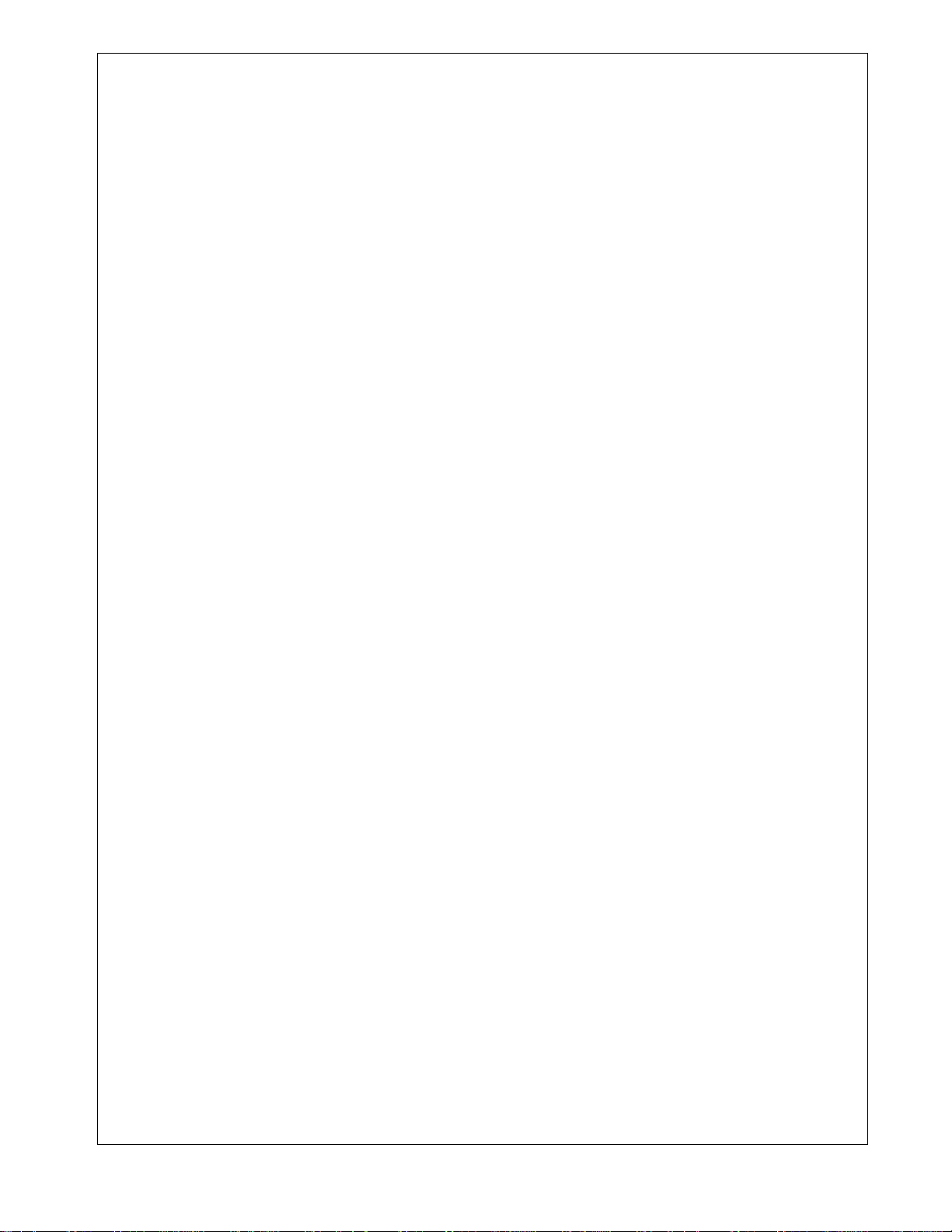

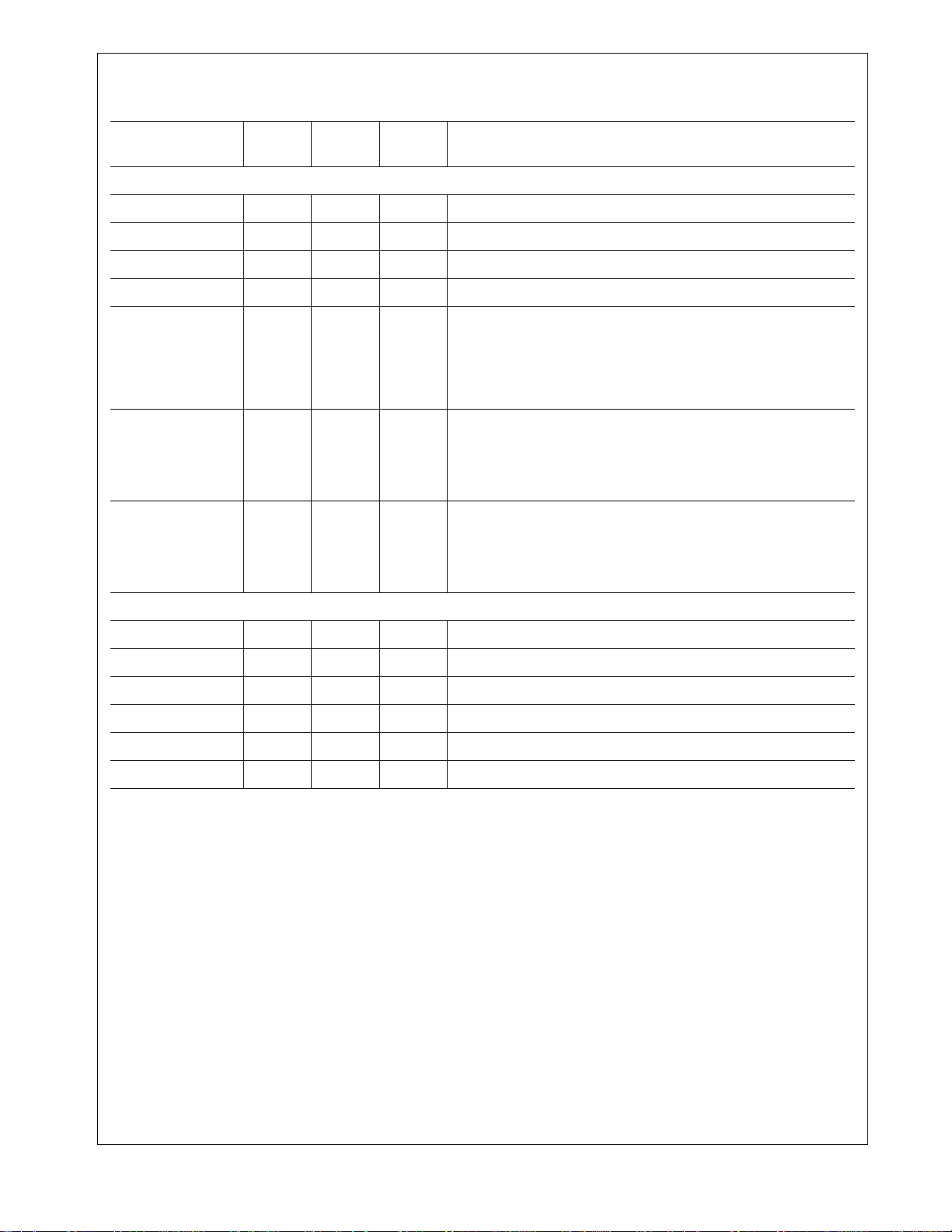

1.0 Connection Diagram

Order Number DP83953VUL

NS Package Number VUL160A

3 www.national.com

1.0 Connection Diagram

(Continued)

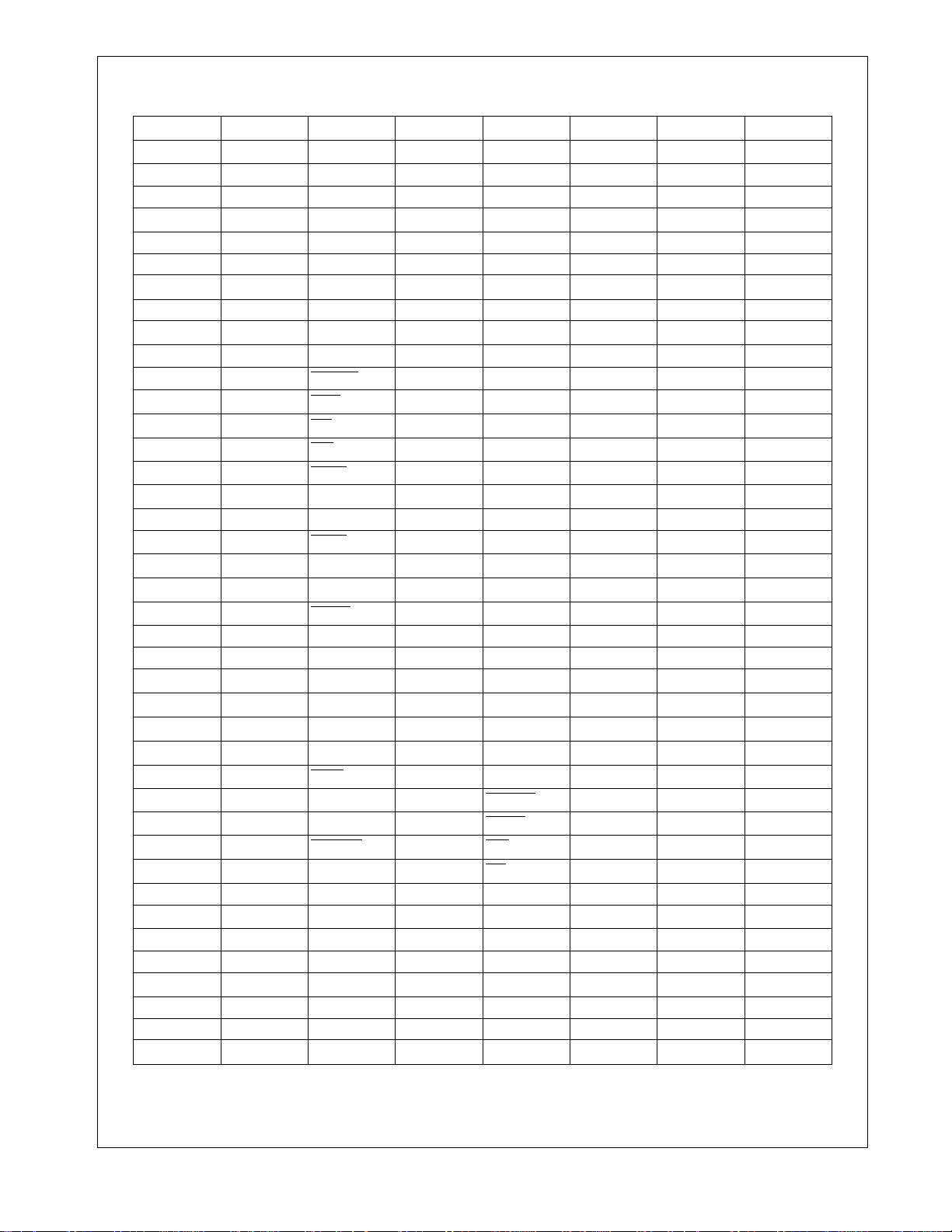

12 T.P. Ports + 1 AUI

PIN NAME PIN NO. PIN NAME PIN NO. PIN NAME PIN NO. PIN NAME PIN NO.

GNDP13 40 V

DD

TXO13- 39 GND 79 TXO2+ 119 TEST_11 159

TXO13+ 38 IRC 78 GNDP2 118 TES T_10 158

TXO12- 37 IRE 77 V

TXO12+ 36 IRD 76 RXI2- 116 TEST_8 156

GNDP12 35 COLN 75 RXI2+ 115 TEST_7 155

P12 34 V

V

DD

DD

RXI12- 33 GND 73 RX1+ 113 FIL TTL 153

RXI12+ 32 PKEN 72 CD1- 112 V

RXI11- 31 RXMPLL 71 CD1+ 111 GNDWS 151

RXI11+ 30

V

P11 29

DD

GNDP11 28

TXO11- 27

TXO11+ 26

TXO10- 25 V

BUFEN

RDY

ELI

RTI

STR0

DD

TXO10+ 24 GND 64 NC 104 TXO6- 144

GNDP10 23

P10 22 ACTND 62 V

V

DD

STR0

RXI10- 21 ANYXND 61 GND 101 V

RXI10+ 20

ACKO

RXI9- 19 MRXC 59 RA4 99 RXI6+ 139

RXI9+ 18 MEN 58 RA3 98 RXI5- 138

P9 17 MRXD 57 RA2 97 RXI5+ 137

V

DD

GNDP9 16 MCRS 56 RA1 96 V

TXO9- 15 V

DD

TXO9+ 14 GND 54 V

TXO8- 13

ACKI

TXO8+ 12 ACTNS 52

GNDP8 11 ANYXNS 51

P8 10

V

DD

PCOMP

RXI8- 9 NC 49

RXI8+ 8 TEST_6 48 D7 88 RXI4- 128

V

A 7 TEST_5 47 D6 87 RXI4+ 127

DD

GNDA 6 TEST_4 46 D5 86 RXI3- 126

RTX 5 TEST_3 45 D4 85 RXI3+ 125

REQ 4 TEST_2 44 D3 84 V

NC 3 RXI13- 43 D2 83 GNDP3 123

TEST_1 2 RXI13+ 42 D1 82 TXO3- 122

V

DD

Note 1: NC = No Connect

Note 2: Port

Note 3: The path to each port

V

1V

and GND are denoted as

DD

V

and GND must have a very low impedance.

DD

P13 41 D0 81 TXO3+ 121

DD

V

Px and GNDPx, where x=2-13 for all twisted pair ports.

DD

80 TXO2- 120 GND 160

P2 117 TEST_9 157

DD

74 RX1- 114 NC 154

WS 152

DD

70 TX1- 110 RXI7- 150

69 TX1+ 109 RXI7+ 149

68 VDD AUI 108 VDDP7 148

67 GND AUI 107 GNDP7 147

66 NC 106 TXO7- 146

65 NC 105 TXO7+ 145

63 NC 103 TXO6+ 143

DD

102 GNDP6 142

P6 141

DD

60 CLKIN 100 RXI6- 140

P5 136

DD

55 RA0 95 GNDP5 135

PLL 94 TXO5- 134

DD

53 GNDPLL 93 TXO5+ 133

92 TXO4- 132

91 TXO4+ 131

90 GNDP4 130

89 VDDP4 129

P3 124

DD

50

MLOAD

CDEC

WR

RD

4 www.national.com

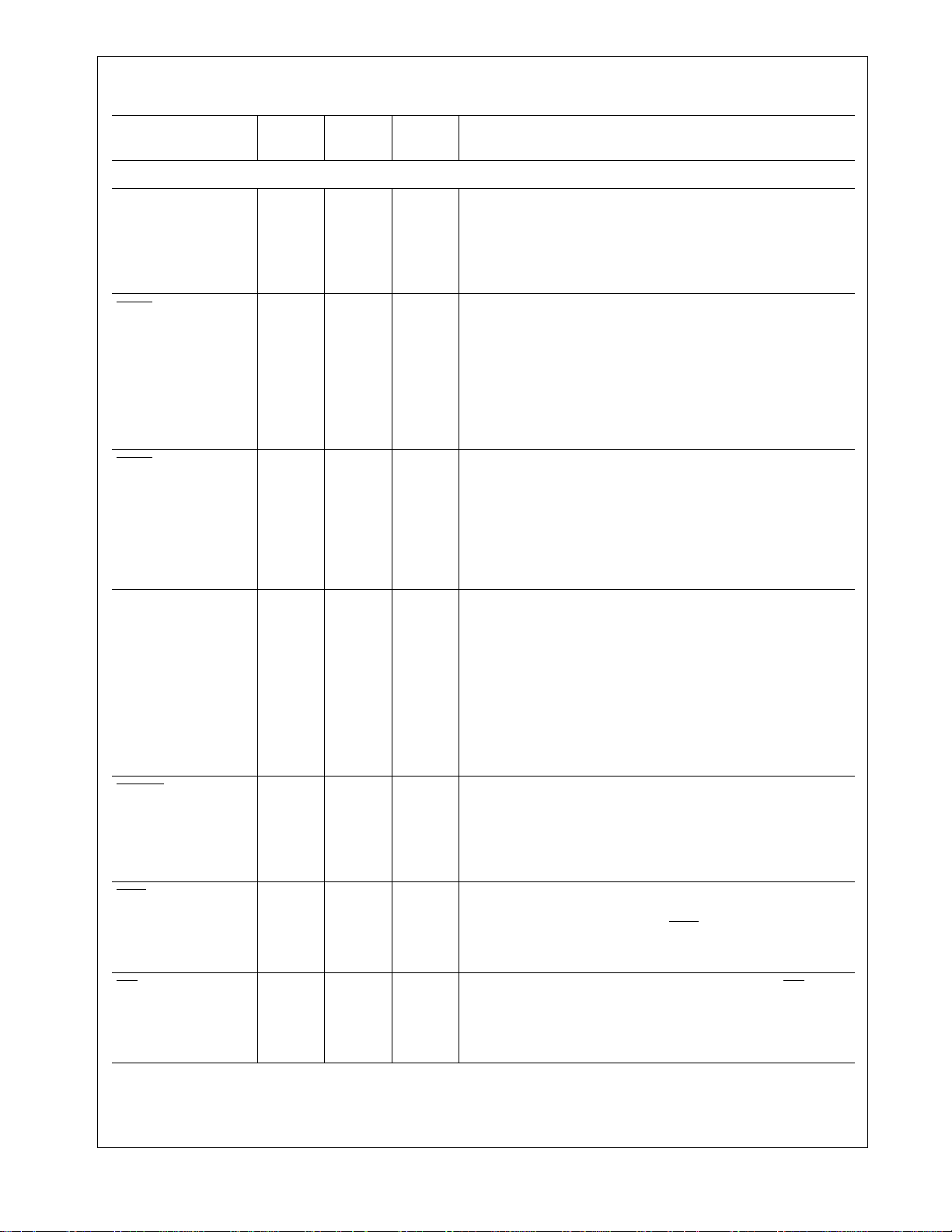

2.0 Pin Descriptions

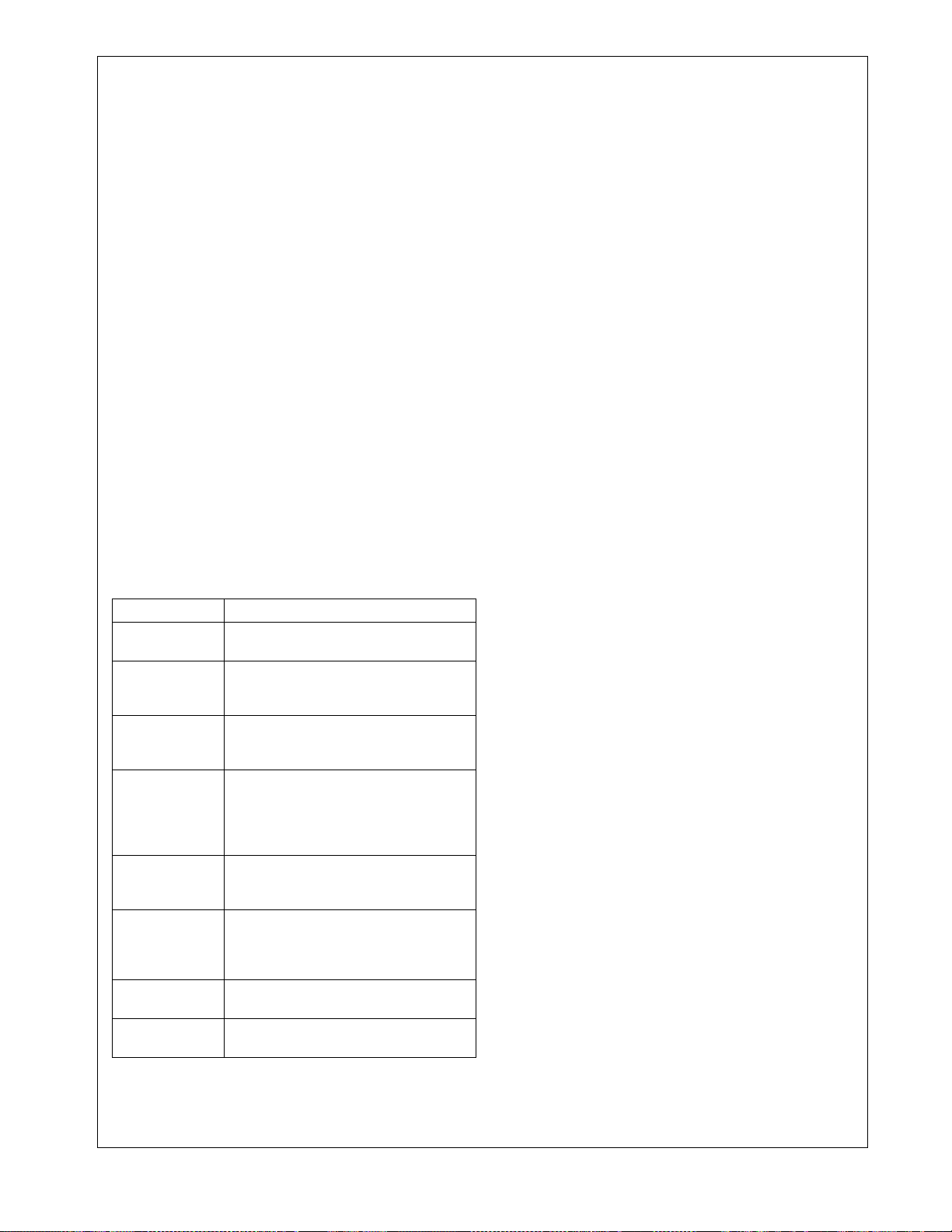

Pin Name Pin No.

Driver

Type

I/O Description

Network Interface Pins

RXI2- to RXI13- TP I Twisted Pair Receive Input Negative

RXI2+ to RXI13+ TP I Twisted Pair Receive Input Posi tive

TXO2- to TXO13- TP O Twisted Pair Transmit Output Negative

TXO2+ to TXO13+ TP O Twisted Pair Transmit Output Positive

FIL

TTL

ter/

FILTTL 153 TT I

: This pin can be utilized for the PCB diagnostic pur-

poses.

0:

Normal repeater operation

1:

Differential transmit signals change to TTL l evel +TX and de-

layed +TX.

REQ 4 Analog I Equalization Resistor: A re sisto r connect ed bet ween this pin and

GND or

V

adjusts the equalization step amplitude on the

DD

Manchester encoded t ransmit data. Care m ust be taken to ensure

system timing integrity when using cable lengt hs greater than

100m. The value here is depende nt upon board layout.

RTX 5 Analog I Extended Cable Resist or: A resistor connected between this pin

and GND or

V

adjusts th e am plitude of the differential transmit

DD

outputs. Care must be taken to ensure system timing integrity

when using cable lengt hs greater than 100m. The value here is

dependent upon boar d layout.

AUI Port

CD1+ 111 AL I AUI Collision Detect Input Positive

CD1- 112 AL I AUI Collision Detect Input Negative

RX1+ 113 AL I AUI Receive Input Positive

RX1- 114 AL I AUI Receive Input Negative

TX1+ 109 AD O AUI Transmit Output Positive

TX1- 110 AD O AUI Transmit Output Negati ve

TP

= Twisted Pair interface compatibl e, TT = TTL compatible, I = Input, O = Output, Analog = current dependent eff ect,

AL

= AUI Level, AD = AUI Drive

5 www.national.com

2.0 Pin Descriptions

(Continued)

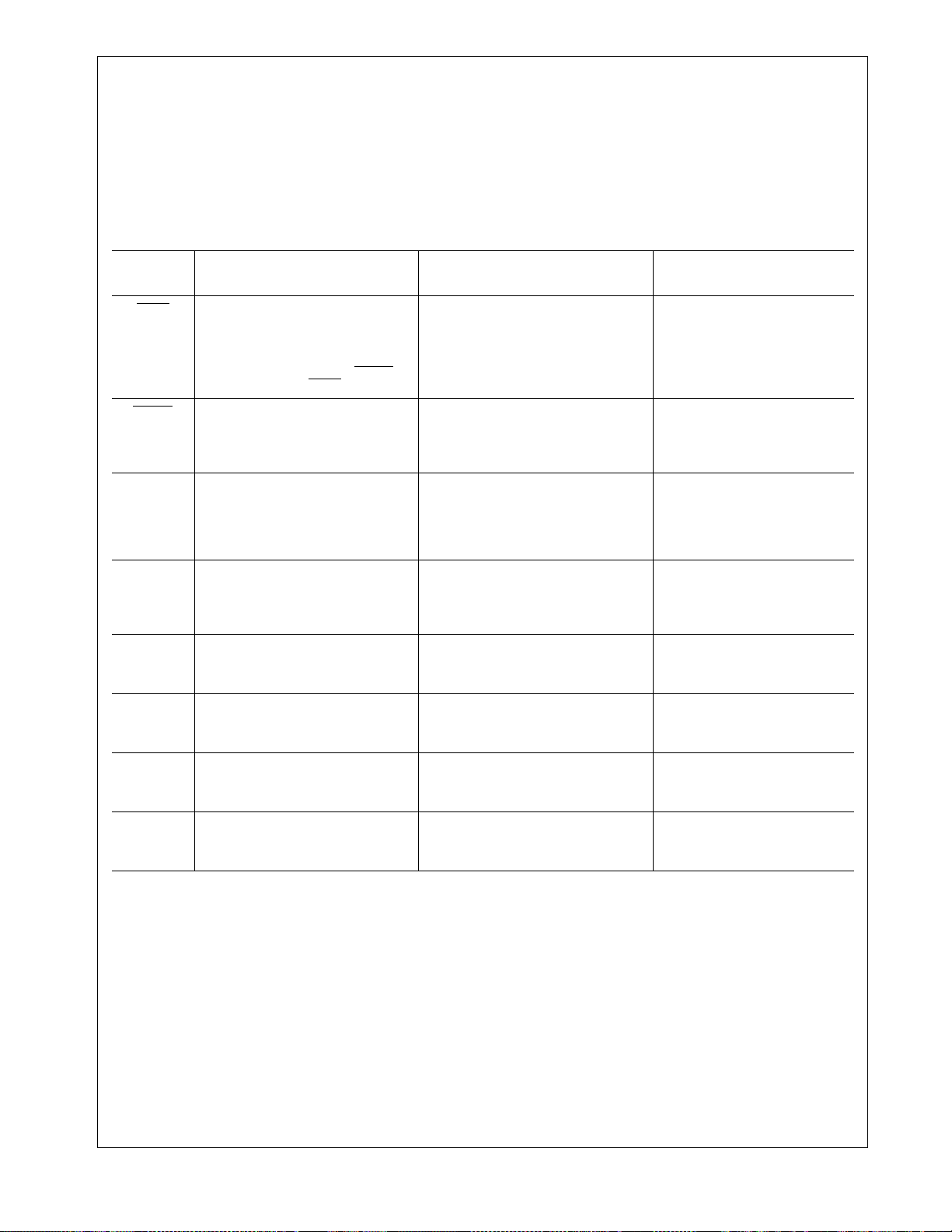

Pin Name Pin No.

Driver

Type

I/O Description

Processor Bus Pins

R

RA0 - RA4 TT I

EGISTER ADDRESS INPUTS: These five pins are used to

select a register to be read or wri tten. The st ate of these i nputs

is ignored when the read, write and Mode Load input strobes

are high. (Even under these conditions these inputs must n ot be

allowed to float at an undefined logic state). See text and table

for proper Mode Load Operat ion strapping.

STR0 63 C O DISPLAY UPDATE

Maximum Display Mode:

display data for network ports 1 to 7 into the off chip display

latches.

Minimum Display Mode:

display data for the RIC2 A into the off chip display latch.

During processor access cycles (read or write is asserted) thi s

signal is inactive (high).

STR1 66 C O DISPLAY UPDATE

Maximum Display Mode:

display data for network ports 8 to 13 into the off chip display

latches.

Minimum Display Mode:

During processor access cycles (read or write is asserted) thi s

signal is inactive (high).

STR

OBE 0

This signal controls the latching of

This signal control s the latching of

STR

OBE 1

This signal controls the latching of

No operation

D

D0 - D7 TT B, Z

ata Bus

Display Update Cycles:

These pins becom e outputs providing

display data and por t addr ess information.

Processor Access Cycles:

Data input or output is performed

via these pins. The r ead, write an d mode load input s control t he

direction o f the signal s.See text and tabl e for prope r Mode Loa d

Operation strap ping.

Note: The data pins remain in their display update function, i.e., asserted as outputs unless either the read or write strobe is asserted.

BUFEN 70 C O

BUF

FER ENABLE: This output contr ols th e TRI-STATE

®

operation of the bus transcei ver which provides the int erface between the RIC2A's data pins and the processor's data bus.

Note: The buffer enable output indicates the function of the data pins. When it is

high they are performing display update cycles, when it is low a processor access

or mode load cycle is occurring.

RDY 69 C O DATA READY STROBE: The falling edge of this si gnal during

a read cycle indicates th at data is stable and val id for sampling.

In write cycles the falling edge of RDY

denotes that the write

data has been latch ed by the RIC2A. The refore data mu st have

been available and stable for this operatio n to be successful.

E

ELI 68 C O

VENT LOGGING INTERRUPT: A low level on the ELI

output

indicates the RIC2A's hub managem ent logic requires CPU attention. The interrupt i s cleared b y accessing the Port Even t Recording regi ster or Event Counter that produced it. Al l i nterrupt

sources may be masked.

6 www.national.com

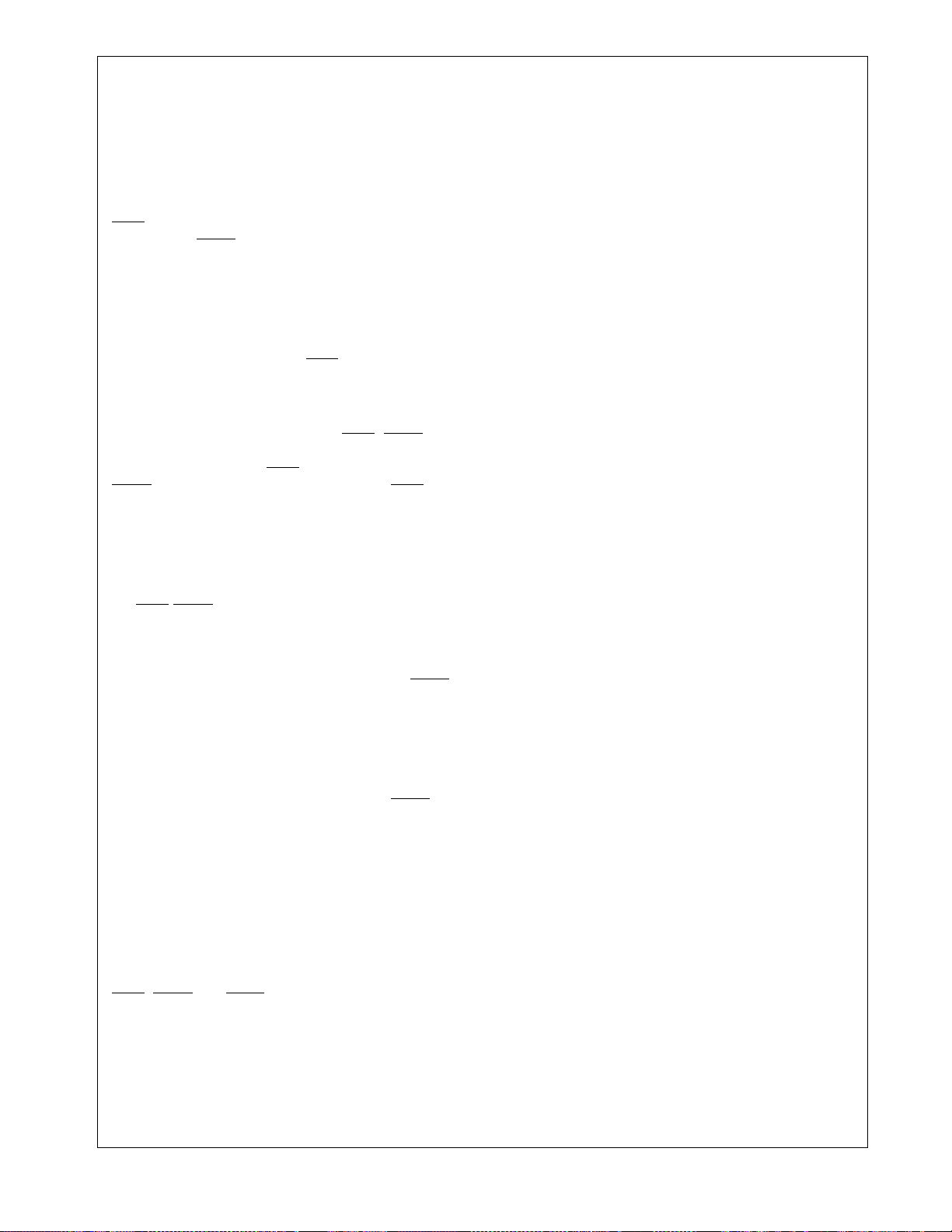

2.0 Pin Descriptions

RTI 67 C O

(Continued)

R

EAL TIME INTERRUPT: A low level on the RTI

cates the RIC2A's real t ime (packet specific) i nterrupt logic requires CPU attention. The interrupt is cleared by reading the

Real Time Interrupt St atus register. Al l interrupt sources m ay be

masked.

output indi-

C

CDEC 91 TT I

WR 90 TT I

RD 89 TT I

MLOAD 92 TT I DEVICE RESET AND MODE

TT

= TTL compatible, B = Bi-directional, C = CMOS compatible, OD = Open Drain, I = Input, O = Output,

Z

= high impedance

OUNTER

strobe decrements all of the RIC2A's Port Event Counters by

one. This input is int ernally synchronized and if necessary the

operation of the signal is delayed if there is a simultaneous internally generated counting operation.

WR

ITE STROBE: Strobe from the CPU use d to write an internal

register defined by the RA0 - RA4 inputs.

READ

register defined by the RA0 - RA4 inputs.

back up from low to high, all of the RIC2A's state machines,

counters and network ports are reset and hel d inactive. On the

rising edge of MLOAD

and RA0 - RA4 inputs are lat ched into the RIC2A's conf iguration

registers. The ri sing edge of MLOAD

of the display test oper ation. The clock signal must be present

on the CLKIN pin during MLOAD

DEC

REMENT: A rising edge on the CDEC

STROBE: Strobe from the CPU used to rea d an internal

LOAD:

the logic levels present on the D0 - 7 pins

When this input cycles

also signal s the beginning

assertion and de-ass ertion.

input

7 www.national.com

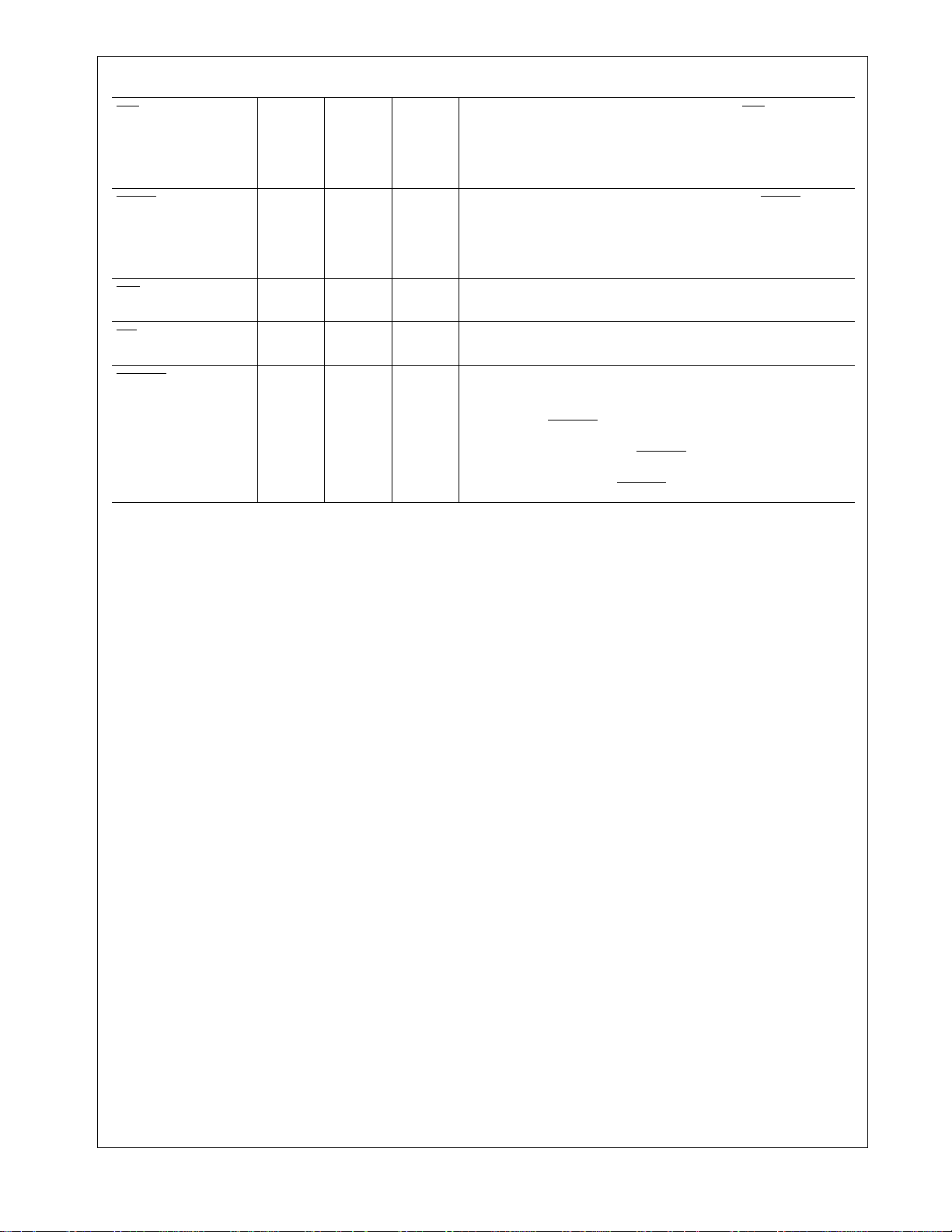

2.0 Pin Descriptions

(Continued)

Pin Name Pin No.

Inter-RIC Bus Pins

ACKI 53 TT I

ACKO 60 TT O

IRD 76 TT B,Z

IRE 77 TT B,Z

IRC 78 TT B,Z

Driver

Type

I/O Description

ACK

NOWLEDGE INPUT: Input to the network ports' arbitration

chain.

ACK

NOWLEDGE OUTPUT: Output from the networ k ports' arbi-

tration chain.

I

vides a serial data st ream in NRZ format . The signal is ass erted by

a RIC2A when it is receiving data fr om one of its network segments. The default condition of this signal i s to be an input. In this

state it may be driven by other devices on the Inter-RIC bus.

I

vides an activ ity f raming en able fo r the se rial dat a strea m. The sig nal is asserted by a RIC2A wh en it is rec eivi ng data f rom one of i ts

network segments. The default condition of this signal is to be an

input. In this state it may be driven by other devices on the InterRIC bus.

I

vides a clock signal for the serial data stream. Data (IRD) is

changed on the fal ling ed ge of the clock. The s ignal i s asser ted by

a RIC2A when it is receiving data fr om one of its network segments. The default condition of this signal is to be an input. When

an input, IRD is sampled on the rising edge of the clock. In this

state it may be driven by other devices on the Inter-RIC bus.

NTER-

NTER-

NTER-

RIC D

ATA: When asserted as an output this signal pro-

RIC E

NABLE: When asser ted as an output this signal pro-

RIC C

LOCK: When asserted as an output this signal pro-

COL

COLN 75 TT B,Z

PKEN 72 C O

CLKIN 100 TT I 40 MHz CLOCK INPUT: This input is used t o generate the

ACTND 62 OD O

ACTNS 52 TT I

ANYXND 61 OD O

ANYXNS 51 TT I

TT

= TTL compatible, B = Bi-directional, C = CMOS compatible, OD = Open Drain, I = Input, O = Output,

Z

= high impedance,

LISION ON PORT N: This denotes that a c ollision is occ urring

on the port r eceiving the dat a packet. The defaul t condition of this

signal is to be an input. In this state it may be driven by other devices on the Inter-RIC bus.

PACK

ET ENABLE: This output acts as an active high enable for

an external bus transceiver (if require d) fo r the IRE, IRC IRD and

COLN signals. When high the bus transceiver should be transmitting on to the bus, i.e. t his RIC2A is dr iving the IRD, IRE, I RC, and

COLN bus lines. When low the bus transceiver should receive from

the bus.

RIC2A's timing refer ence for the state machines, and phase lock

loop decoder.

ACT

IVITY ON PORT

RIC2A is recei ving data or c ollision infor m ati on from one o f its network segments.

ACT

IVITY ON PORT

other RIC2A in a multi-RIC2A system is receivin g data or collis ion

information.

A

CTIVITY ON ANY PORT EXCLUDING PORT

output is active when a RIC2A is experiencing a transmit collision

or multiple ports have active collisions on their network segmen ts.

A

CTIVITY ON ANY PORT EXCLUDING PORT

put senses when this RIC2A or ot her RIC2As in a multi-RI C2A system are experiencing transmit collisions or multiple ports have

active collisions on their network segments.

N D

RIVE: This output is active when the

N S

ENSE: This input s enses when this or an-

N D

RIVE: This

N S

ENSE: This in-

8 www.national.com

2.0 Pin Descriptions

(Continued)

Pin Name Pin No.

Driver

Type

I/O Description

Management Bus Pins

M

MRXC 59 TT O,Z

ANAGEMENT RECEIVE CLOCK: When asserted this signal provides a clock si gnal for the MRXD serial data stream . The MR XD

signal is chan ged on the falling edge of this clock. The signal is asserted when a RIC2A is receiving data from one of its network segments. Other w ise the signal is inactive.

M

MCRS 56 TT B,Z

ANAGEMENT CARRIER SENSE: When asserted this signal provides an activ ity framing enable for the serial data stream. The signal is asserted when a RIC2A is receiving data from one of its

network segments. Otherwise the signal is an input.

M

MRXD 57 TT O,Z

ANAGEMENT RECEIVE DATA: When asserted this signal provides a seri al data stream i n NRZ format. The data stream is made

up of the data packet and RIC2A status information. The signal is

asserted when a RIC2A is receiving data from one of its network

segments. Otherwise the signal is inactive.

M

MEN 58 C O

ANAGEMENT BUS OUTPUT ENABLE: This output act s as an active high enable for an external bus transcei ver (if required) for the

MRXC, MCRS

and MRXD signals. When high the bus transceiver

should be transmi tting on to the bus.

PCOMP 50 TT I

P

ACKET

packet compress l ogi c. A low level on this si gnal when MCRS

tive will cause that packet to be compressed. If PCOMP

all packets are compressed, if PCO M P

COMP

RESS: This input is used to activ ate the RIC2A's

is tied high packet co mpres -

is ac-

is tied low

sion is inhibit ed.

External Decoder Pins

R

RXMPLL 71 TT O

ECEVE DATA MANCHESTER FORMAT: This output makes the

data, in Manc hester format , recei ved by po rt N avai labl e for test purposes. If not use d for testing this pin should be le ft open.

Test Pins

TEST_(12:7) 154-159 TT I Factory test control pins - this pin should be connected to GND for

proper operat ion of the repeater.

TEST_(6:2) 44-48 TT I Factory test control pins - this pin should be connected to GND for

proper operat ion of the repeater.

TEST_1 2 TT O Factory test control pins - this pin should be le ft unconnected for

proper operat ion of the repeater.

Po we r and Ground Pins

V

DD

GND 54, 64, 73, 79, 101,

1, 55, 65, 74, 80, 102 Positive Supply

Nega tive S u pp ly

160

V

A 7 Positive Supply for Analog circuitr y

DD

GNDA 6 Negative Supply for Analog circuitry

V

PLL 94 Positive Supply for Phase Lock Loop

DD

GNDPLL 93 Negative Supply for Phase Lock Loop

V

WS 152 Positive Supply for Wave Shape circuitry

DD

GNDWS 151 Negative Supply for Wave Shape circuitry

VDD P

n

10, 17, 22, 29, 34, 41,

117, 124, 129, 136,

Positiv e su pp l y fo r p or t N . C o nne c t for all por ts .

141, 148

GND P

n

11, 16, 23, 28, 35, 40,

Negative supply for port N. Connect for all ports.

118, 123, 130, 135,

142, 147

VDD AUI 108 Positive sup ply for AUI port.

GND AUI 107 Negative supply for AUI port.

TT

= TTL compatible, B = Bi-directional, C = CMOS compatible, OD = Open Drain, I = Input, O = Output,

Z

= high impedance

9 www.national.com

3.0 Block Diagrams

Figure 1. Shared Repeater and Segment Functional Blocks

10 www.national.com

3.0 Block Diagrams

(Continued)

Figure 2. RIC2A Port Architecture Security Block Diagram

Note: The block di agram for the RIC2A , when use d in the non-secur e mode , is identi cal to the “sha red” repea ter funct ional blo ck diag ram.(

in secure mode, additional security logic is used when operating the device (

Figure 2

)

Figure 1

). But,

11 www.national.com

4.0 Functional Description

The IEEE 802.3 repeater specification delineates the functional criteria that all compliant repeater systems must

adhere to. An implementation of these requirements

strongly suggest a multiport modular design style. In such

a design, functionality is split between those tasks common

to all data channels and those exclusive to each individual

channel. The RIC2A follows this approach. Certain functional blocks are replicated for each network attachment,

(also known as a repeater port), and others are shared.

The following subsections provide an overview of the

RIC2A architecture. First, RIC2A feature enhancements

from the RIC II is discussed. Then, the RIC2A functional

blocks are described.

4.1 Summary of DP83953 RIC2A Feature Enhancements from DP83952 RIC II

1. The DP83953 RIC2A integrat es transmit filter s and drivers on a per port basis. These additional features allow

a system dev eloper to add l itt le more tha n exter nal is olation tran sformer s in o rder t o bu ild f ully secure d/man aged

hub products.

2. The functionality of the DP83953 is essentia lly similar to

DP83952, but some of the pin definitions have been

modified to reflect the new integrated drivers and transmit filter s. Therefore, the RIC2A is

ment for the RICII

locations have been rearranged to accommodate additional pins.

3. Integrated network port drivers provide controlled rise

and fall time output signals. These port drivers will facil itate EMI compliance without procuring additional components.

4. Compared to DP83952, the DP83 953 requires additiona l

current dr ive. The additional current is required to im plement the new integrated drivers and transmit filters.

. Additionally, power and ground pin

not a drop in replace-

4.2 Overview Of RIC2A Functions

Segment Specific Bloc k: Network Port

As shown in the block diagram, the segment specific b locks

consist of

A logic sectio n and a physical layer interface section.

The logic bloc k is required for perform ing repeater operations upon that particular segment. It is known as the

“port” lo gic since it is the access “port” the segm ent has

to the rest of the network.

This function is repeated 13 times in the RIC2A (one for

each port) and is shown on the right side of the block diagram, Figure 1.

The physical layer interface depends upon the port. Port 1

has an AUI compliant interface for use with AUI compatible

transceiver boxes and cable. Ports 2 to 13 are twisted pair

ports.

The four dist inct functions insi de the port logic block are:

1. The Port State Machine "PSM" performs data and collision repetition as described by the IEEE repeater specification. For exampl e, i t may det ermi ne if this p ort sho uld

be receiving from or transmitting to a particular network

segment.

2. The Port Partition Logic implements the segment partitioning algorithm. This algorithm is defined by the IEEE

specificatio n and is used t o protect t he network f rom malfunctioning segments.

3. The Port Status Register r eflects the cur rent stat us of the

port. The system processor may access this register to

obtain port status information or to configure certain po rt

options, such as port disable.

4. The Port security configuration logic determines if the

transmitted or received packet will cont ain intact or pseudo random data. This logic consists of two dedicated

CAM locations p er por t f or lea rning, storing, and compa ring port source addresses.

Shared Functional Blocks: Repeater Core Logic

The shared functional blocks consists of the repeater Main

State Machine (MSM), Timers, a 32 bit Elasticity Buffer,

PLL Decoder, Receive and Transmit Multiplexors, and

Security Logic with 32 shareable CAM locations. These

blocks perform the majority of the operations needed to fulfill the requirements of the IEEE repeater specification.

When a packet is received by a port it is then sent via the

Receive Multiplexor to the PLL Decoder. Notification of the

data and collision status is sent to the MSM through the

receive multiplexor and collis ion activity stat us signals. T his

enables the MSM to determine th e source and type of data

to be transmitted and eventually repeated to all ports. This

information may be valid data or the jam pattern.

According to the IEEE repeater specifications, after a collision has been determined, the transmit data will be

replaced with a jam pattern consisting of a alternating ones

and zeros. (e.g. 1010...) for at least 96 bit times. If a collision occurs during the preamb le, the addr ess field, the type

field, or the data field the RIC2A will immediately switch to

the jam pattern to be transmit ted to all ports.

If the RIC2A is configured for the "non-secure" mode, the

valid received data is transmitted to all of the other ports,

except the port which is rec eiving the pack et.

If the RIC2A is configured for the "secure" mode, the

source and destination addresses within each packet are

first chec ked against the addresses of the local and shared

CAMs assigned to the port. Based on this comparison , and

the port configuration will be either:

1. A pseudo random bit pattern may be generated in the

data field of the designated “secure” packet and then

transmitted to their respective port(s). Or,

2. The received data may be transmitted intact.

The data always remains intact on the Inter-RIC bus (IRB

to be described later) to allow any cascaded repeaters to

compare all destination addresses with their l ocal CAMs. In

12 www.national.com

4.0 Functional Description

the case of a source address mismatch, the RIC2A will

immediately switch to a random bit pattern on both the

local transmit t ing po rts and th e IRB.

The main state machine operates in conjunction with a

series of counter timers. These timers will ensure that all

associated IEEE specification times (referred to as the

TW1 to TW6 times) are met.

An IEEE repeater system must meet the same signal jitter

performance as any other receiving n ode attached to a network segment. Consequently, a phase locked loop

Manchester decoder is required so that the packet may be

decoded, and the jitter accumulated over the receiving segment recovered. The decode logic outputs data in non

return to zero (NRZ) format with an associated clock and

enable. This format allows the packet to be conveniently

transferred to o ther attached devices, such as network controllers and other repeaters through the Inter-RIC bus

(IRB). The data may then be re-encoded into Manchester

data and transmitted.

During reception and/or transmission through the physical

layer transceivers a loss of bits in the preamble field of a

packet may occur. This loss must be replaced according to

the IEEE repeater specification. To accomplish this, an

elasticity buffer is employed to restore a full length preamble upon transmission.

(Continued)

The Sequence of Operation

Soon after the network segment receiving a packet has

been identified, the RIC2A will transmit the preamble pattern (1010...) to all other network segments. While the preamble is being transmitted, the elasticity buffer will monitor

the decoded received clock and data signals via the InterRIC bus (IRB). When the start of frame delimiter (SFD) is

detected, the received dat a stream will be written into the

elasticity buffer. The removal of stored data from the elasticity buffer for re-transmission is not allowed until a valid

length preamble pattern has been transmitted.

Internal CAMs

To implement the security features, the RIC2A uses two

sets of Content Addressable Memory (CAMs) for address

comparison: port CAMs, and shared CAMs.

Port CAMs

The RIC2A provides two CAM locations (48 bits wide) per

port for comparison. The tw o CAM locati ons contai n sour ce

address(es) for incoming packets on their respective ports.

The addresses can be stored (CPU access) or learned

(Learn Mode). While in learning mode, LME=1, external

processor access is not advised or allowed, since the contents of the two CAM registers may not be valid. Once the

addresses are learned, they are used to make comparisons between the source and destination addresses. An

address can only be learned when a packet has been

received with a valid CRC. External processor/logic access

to these registers is fine while learning is not in progress,

LME=0 in the port security configuration register.

Shared CAMs

The RIC2A provides thirty-two shareable CAM locations

(48 bits wide) to store Ethernet addresses associated with

the ports. The Ethernet addresses are stored by writing to

these CAM locati ons where the addresses could be shared

among the thirteen ports. By using shared CAMs, multiple

Ethernet addresses can be associated with a single port,

or multiple ports can be allocated to a single Ethernet

address. After the destination address of the received

packet is completely buffered, the RIC2A will compare this

address with the stored addresses in the CAM locations.

The source address is compared in a similar fashion.

These shared CAM locations are user defined onl y, and wil l

not be filled in learning mode.

A CAM entry could be shared among the thirteen local

ports. This is done through a 16-bit CAM Location Mask

Register (CLMR). For each CAM entry there is only one

CLMR, therefore there are 32 registers for the 32 CAM

entries.

Since register access is performed on a byte basis, six

write cycles must be completed to program the Ethernet

address into the CAM. The upper three bits of the CAM

Location Mask Register (CLMR) act as a pointer indicating

which byte of the 6-byte address will be accessed next.

This pointer will increment every time a read or write cycle

is completed to the CAM entry. The pointer starts at 1, indicating the least significant byte of the address.

Four additional registers are provided to validate the 32

shared CAM entries and are referred to as the Shared

CAM Validation Registers 1-4 (SCVR 1-4, Page 9H,

Address 16-19H). Each bit of the SCVR is mapped to one

CAM loc ati on. An ad dress in the CA M loc ation will o nly be

valid when a corres ponding bit Address Valid (ADV bit) has

been set in this register. The RIC2A will include only valid

CAM locations f or address comparison.

The contents of all CAM locations are unknown at power

up. This is not a problem since corresponding Address

Valid (ADV) bits are not set for each CAM. Therefore, comparisons will not take pl ace with the CAM contents.

Inter-RIC Bus (IRB) Interface

A RIC2A based repeater system may be constructed to

support many more network attachments than those available through a single chip. The split functions described

earlier, allow data packets and collision status to be transferred between multiple RIC2As while allowing the system

to function as a single logical repeater. Since all RIC2As in

a multiple RIC2A system are identical and capable of performing all repetition functions, the fail ure of one RIC2A will

not cause a failure of the entire system. This is an important issue, especially with respect to large multi-port

repeaters.

In a multi-RIC2A system, the RIC2As can communicate

through a specialized interface known as the Inter-RIC

bus(IRB). This bus allows the data packet to be transferred

from the receiving RIC2A to other RIC2As in the system.

Each RIC2A then transmits the datastream to its segments.

13 www.national.com

4.0 Functional Description

The notification of collisions occurring across the network

is just as important as data transfers. The Inter-RIC bus

has a set of status lines capable of conveying collision

information between RIC2As in order to ensure that their

main state machines operate in the appropri ate manner.

(Continued)

LED Interface and Hub Management Function

Repeater systems usually possess optical displays indicating network activity and the status of specific repeater

operations. The display update block of the RIC2A c an provide the system designer with a wide variety of indicators.

The updates are completely autonomous and merely

require SSI logic to drive the display devices, usually made

up of light emitting diodes (LEDs). The status display is

very fle xib le and allo ws the user to choose appropri ate indicators for the specification of his equipment.

The RIC2A was designed for those interested in implementing large repe aters with hub managem ent capabi lit ies .

Hub management uses the unique position of repeaters in

a network to gather statistics about the network segments

they are attached to. Important events are gathered by the

management block from logic blocks throughout the chip.

These e vents are then stored in on-chip latches, or counted

in on-chip counters according to the developer’s supplied

latching and counting masks.

The fundamental task of a hub management system implementation is to associate the current packet and any management status information with the network segment. An

example could be keeping track of packets received on a

repeater’s ports. An ideal system would place the combined data packet and status field in system memory for

future examination by hub management software. The

main function of the RIC2A's hub management support

logic is to provide this function.

To accomplish this task, the RIC2A util izes a dedicate d hub

management interface. This is similar to the Inter-RIC bus

since it allows the data packet to be recovered from the

receiving RIC2A. Unlike the Inter-RIC bus, the intended

recipient is not another RIC2A, but typical National Semiconductor's DP83932 ("SONIC

allows a management status field to be appended at the

end of each packet without affecting the operation of the

entire repeater system.

In addition to the cou nter s provided on the RIC DP83950B,

the RIC2A implements thirteen more (8 bit wide) counters.

These counters will count events specified in the Event

Count and Interrupt Mask Register2 (ECIMR2). These

include items such as Frame Check Sequences, Frame

Alignment Errors, Partitions, and Out of Window Collisions.

This register also includes "Reset On Read" and "Freeze

When Full" contr ol bits.

It should be noted that Counter Decrement (CDEC) will not

be used with the ECMR2. Also, real time or event logging

interrupts (RTI or ELI) will not be generated for this register.

Processor Interface

The RIC2A's processor interface uses an octal bi-directional data bus in order to interface to a system processor.

The RIC2A has on-chip registers to indicate the status of

™

"). This dedicated bus

the hub management functions, chip configuration, and

port status. These registers are accessed by pl acing the

respective address at the Register Address (RA4 - RA0)

input pins.

Display update cycles and processor accesses occur utilizing the same data bus. An on-chip arbiter in the processor/display block schedules and controls the accesses and

ensures the correct information is written into the display

latches. During the display update cycles the RIC2A

behaves as a master of its data bus. This is the default

state of the data bus. Consequently, a TRI-STATE buffer

must be placed between the RIC2A and the system processor's data bus. This ensures that bus contention problems are avoided during simultaneous display update

cycles and processor accesses of other devices on the

system bus. When the processor accesses a RIC2A register, the RIC2A enables the data buffer and selects the

operation, eit her input or output, of the data pins.

For faster regi ster accesses, the RIC2A provides the added

feature of disabling display update cycles. Setting the Disable LED Update bit, DLU in the Lower Event Information

register (Page 1H, Address 1FH) stops the RIC LED

update cycles. This disables the shared mode of the data

bus, leaving the RI C2A in slave access mode. In this mode,

the maximum read/write cycle time is reduced to approximately 400 ns.

4.3 Description Of Repeater Operations

In order to implement a multi-chip repeater system that

behav es as a singl e logical rep eat er , special conside rati ons

must be taken into account with respect to the data path

used for packet repetition. For example, we must consider

where in the data path specific operations such as

Manchester decoding and elasticity buffering are performed. Additionally, the system state machines, which utilize available network activity signals, must accommodate

various packet repetition and collision scenarios according

to the IEEE repeater specification.

The RIC2A contains two types of interacting state

machines. They are:

1. Port State Machines (PSMs) Every network attachment

has its own PSM.

2. Main State Machine (MSM) This state machine controls

the shared functional blocks as shown in the block diagram Figure 1.

14 www.national.com

4.0 Functional Description

(Continued)

Repeater Port and Main State Machines

The Port and Main State Machines are described with terminology used in the IEEE Repeater specification. For a

detailed explanation of terms, please refer to that specification. References made to repeater states or terms

described in the IEEE specification will be shown in italics.

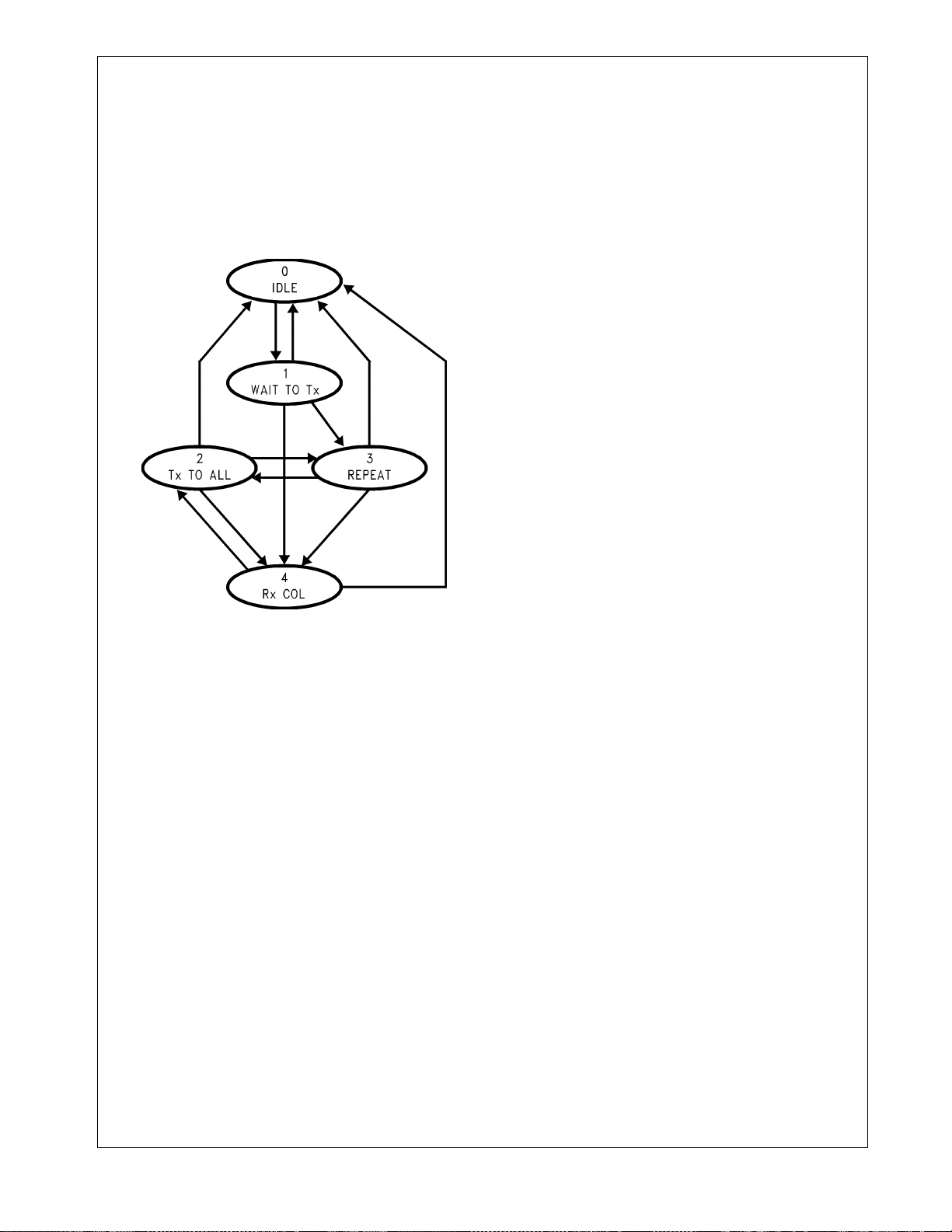

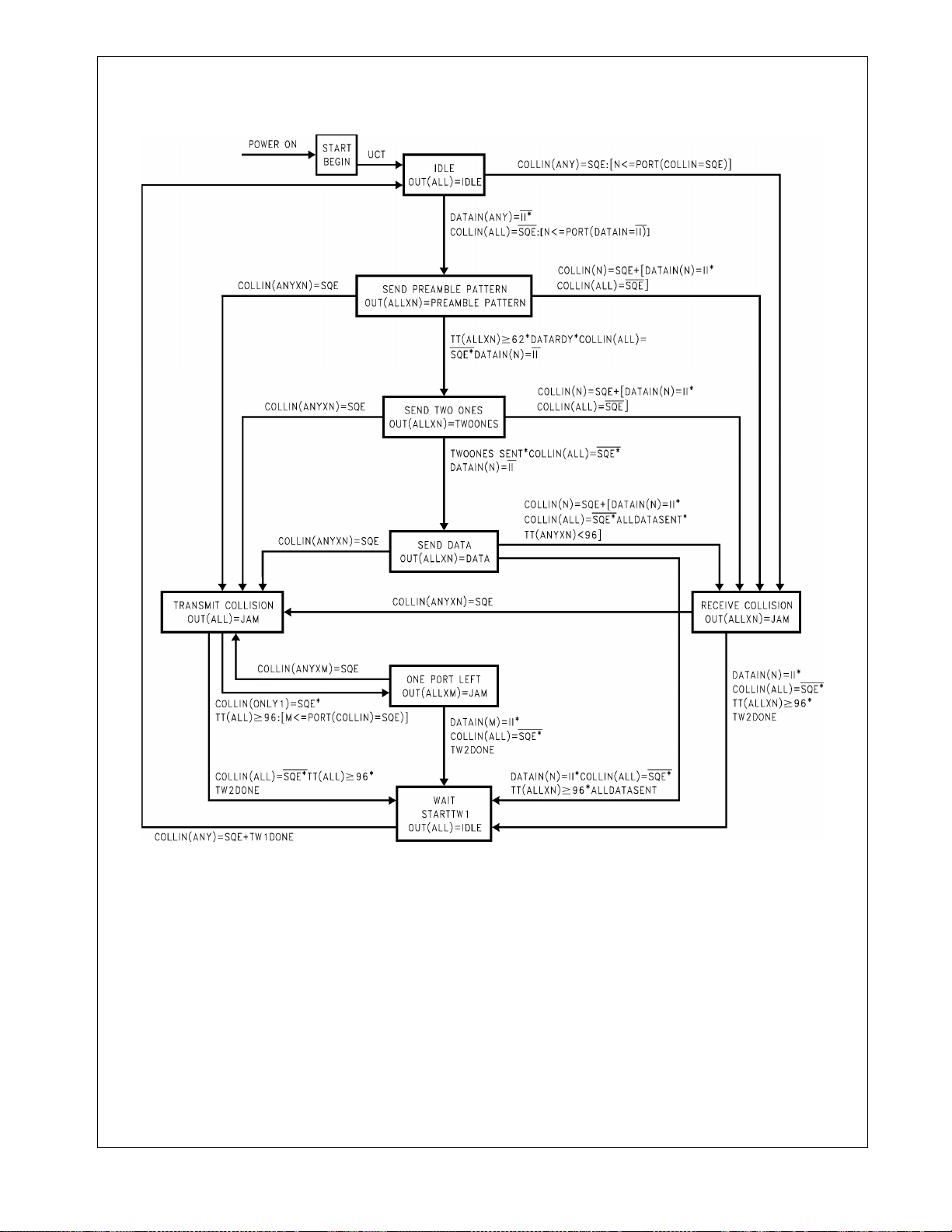

Figure 3 shows the Inter-RIC Bus State Diagram and Figure 4 shows the IEEE State Diagram.

Figure 3. Inter-RIC bus State Diag ram

15 www.national.com

4.0 Functional Description

(Continued)

Figure 4. IEEE Repeater Main State Diagram

16 www.national.com

4.0 Functional Description

(Continued)

The Port State Machine (PSM)

The two primary functions of t he PSM are to:

1. Control the transmission of repeated data, pseudo random data, and jam signal s over the attached segments .

2. Determine if a port will be the source of data or collision

informati on to be repe ated over t he network. This repeater port i s known as

quired to enable the repeater to transition from an

state to the

COLLISION

to locate the port that will be

packet.The dat a recei ved f ro m

PLL decoder and transmitted over the Inter-RIC bus. If a

collision occurs, the repeater enters the

COLLISION

tion is performed in order to determine which port is

PORT M. PORT M

other ports if the repeater enters the

state. In this state

ment. At that time, all other ports are still required to

transmit to t heir segments.

PORT N

SEND PREAMBLE PATTERN

states. (See Figure 4) This process is used

state. Then a subsequent arbitration opera-

is differentiated from the repeater’s

PORT M

. An arbit rati on proc ess is r e-

IDLE

or

RECEIVE

PORT N

for that particular

PORT N

is direct ed t o t he

TRANSMIT

ONE PORT LEFT

does not transmit to its seg-

The Main State Machine (MSM)

The MSM controls the operation of the shared f unct ional

blocks in each RIC2A as shown in the block diagram,

Figure 1, and performs the majority of the data and collision operations as defined by the IEEE specification.

Inter-RIC Bus (IRB) Operation

Overview

The IRB consists of eight signals. These signals implem ent

a protocol that may be used to connect multiple RIC2As

together. In this configuration, the logical function of a single repeater is maintained. The resulting multi- RIC2A

repeater syst em is compliant with the IEEE 802.3 Repeater

Specification and may even encompass several hundred

network segments. Figure 5 shows an example of a multiport RIC2A system.

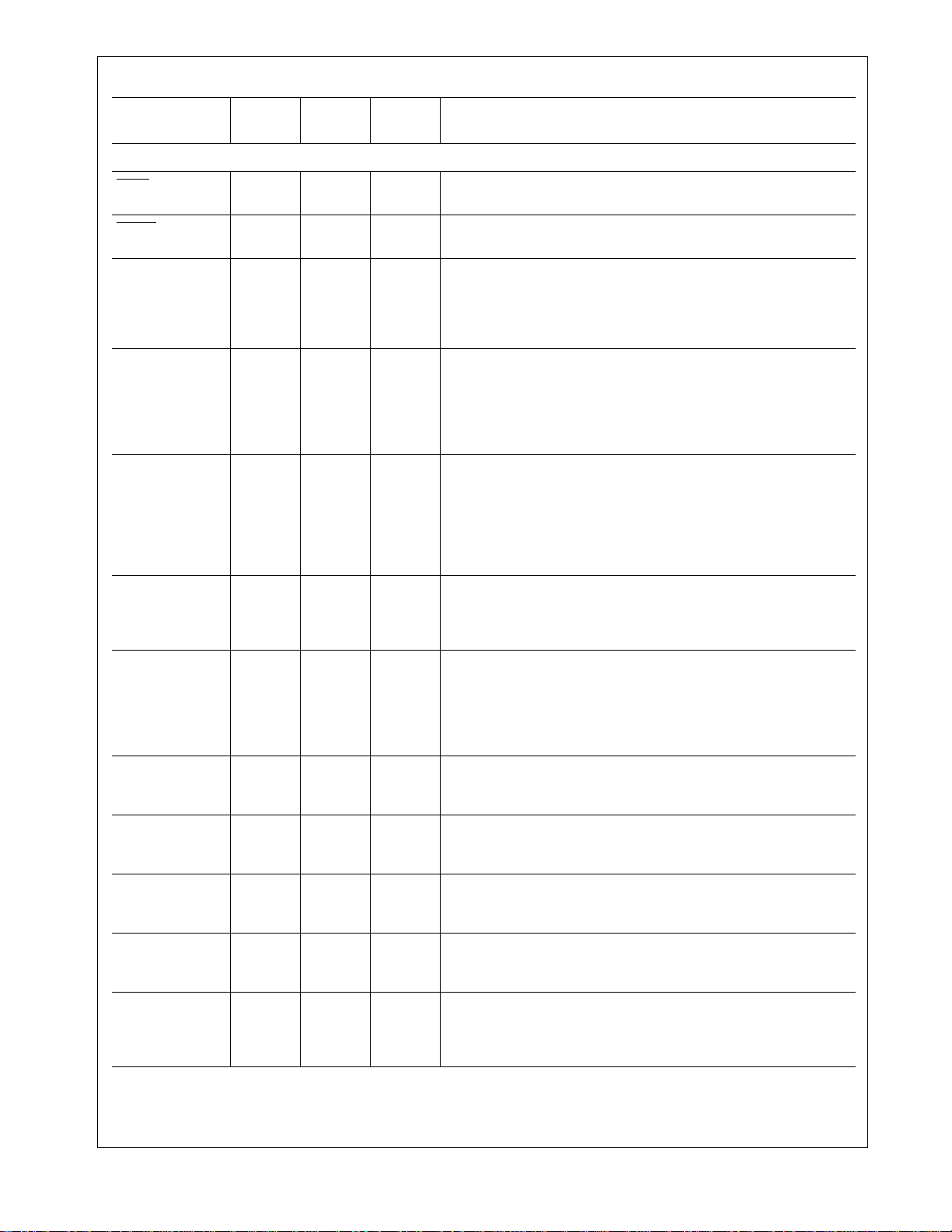

Function Action

Preamble

Regeneration

Fragment

Extension

Elasticity Buffer

Control

Jam / Preamble

Pattern Generation

Transmit

Collision

Enforcement

Data Encoding

Control

Tw1

Enforcement

Tw2

Enforcement

Restore the length of the preamble pattern to the defined size.

Extend received dat a or col lision fragments to meet the minimum fragment

length of 96 bits.

A portion of the received pac ket may require storage in an Elasticity Buffer to

accommodate preamble regeneration.

In cases of receive or transmit collisions, a RIC2A is req uired t o t ransmit a

jam pattern (1010...).

Note: This pattern is the same as that used for preamble regeneration.

The

TRANSMIT COLLISION

quires a repeater to r emai n in this sta te

for at least 96 bit ti m es.

NRZ formatted data in the ela sticity

buffer must be encoded i nto Manchester formatted data pri or to re-transmission.

Enforce the Transmi t Recovery Time

specification.

Enforce Carrier Recovery Time specification on all ports with active collisi ons.

state re-

The interaction of the main and port state machines is visible, i n part, through the Inter-RIC bus.

17 www.national.com

4.0 Functional Description

(Continued)

The IRB connects multiple RIC2As to realize the following

operations:

Port N

Identification (which port the repeater receives

data from)

Port M

Identification (which port last experienced a colli-

sion)

Data Transfer

RECEIVE COLLISION

identification

TRANSMIT COLLISION

DISABLE OUTPUT

identification

(jabber protection)

The following table briefly describes the operation of the

Inter-RIC bus signals, the conditions required for a RIC2A

to assert a signal, and which RIC2As (in a multi-RIC2A

system) would monitor the signal.

Inter-RIC

Bus Signal

Function

ACKI Input signal to Th e PSM arbit rati on

chain. This chain is employed to

identify

Note: A RIC2A whic h contains

PORT M

nal being low when its

PORT N

may be identified by its

and

ACKI

PORT M

input is high.

PORT N

ACKO

ACKO Output signal from the PSM arbi-

tration chain.

ACTN This sig nal denotes there i s activity

on

PORT N

or

PORT M.

ANYXN This signal denotes that a repeater

port that is not

PORT N

or

PORT M

is experiencing a collision.

COLN Denotes

PORT N

or

PORT M

periencing a collision.

IRE This signal ac ts as an act ivi ty fra m-

ing signal for the IRC and IRD signals.

Conditions Required for a RIC2A

to Drive this Signal

RIC2A Receiving the Signal

Not applicable This is depende nt upon the

method used to casca de

.

or

sig-

If this RIC2A contains port N, then

the device will assert this signal.

RIC2As , desc r ib ed in a follo w ing section.

This is dependent upon the

method used to casca de

RIC2As , desc r ib ed in a follo w ing section.

A RIC2A must contain

PORT M.

Note: Although this signal n ormally has only

one source asserting the signal active it is used

in a wired-or configuration.

Any RIC2A which satisfies the a bove

condition.

Note: This bus line is used in a wired-or configuration.

is ex-

A RIC2A must contain

PORT M.

PORT N

PORT N

or

The signal is monitored by all

RIC2As in the re peater syst em.

The signal is monitored by all

RIC2As in the re peater syst em.

or

The signal is monitored by all

other RIC2As in the repeater

system.

A RIC2A must contain

PORT N.

The signal is monitored by all

other RIC2As in the repeater

system.

IRD Decoded ser ial data, in NRZ for-

mat, received from the net work

segment attached to

PORT N.

IRC Clock signal associated with IRD

and IRE.

A RIC2A must contain

A RIC2A must contain

18 www.national.com

PORT N.

PORT N.

The signal is monitored by all

other RIC2As in the repeater

system.

The signal is monitored by all

other RIC2As in the repeater

system.

4.0 Functional Description

Methods of RIC2A Cascading

In order to build multi-RIC2A repeaters,

PORT M

RIC2As in the system. Inside each RIC2A, the PSMs are

arranged in a logical arbitration chain where port 1 is the

highest and port 13 the lowest. The top of the chain, the

input to port 1 is accessible to the user via the RIC2A's

ACKI

becomes the ACKO

PORT N

chain with receive or collision activity.

is performed when the repeater is in the

M

when the repeater leaves the

state. In order for the arbitration chain to function, all that

needs to be done is to tie the ACKI

state. In multi-RIC2A systems there are two methods to

propagate the arbitration chain between RIC2As:

The first and most straight forward is to extend the arbitration chain by daisy chaining the ACKI

between RIC2As. In this approach one RIC2A is placed at

the top of the chain (its ACKI

ACKO

the next RIC2A and so on. This arrangement is simple to

implement but it places some topological restrictions upon

the repeater system. In particular, if the repeater is constructed using a backplane with removable pr inted circuit

boards. (These boards contain the RIC2As and their associated components.) If one of the boards is removed then

the ACKI

not operate cor rectly.

The second method of

this problem. This second technique relies on an external

parallel arbiter which monitors all o f the RIC2As' ACKO

nals and responds to the RIC2A with the highest priority. In

this scheme each RIC2A is assigned with a priority level.

One method of doing this is to assign a priority number

which reflects the position of a RIC2A board on the

repeater backplane, i.e., its slot number. When a RIC2A

experiences receive activity and the repeater system is in

the

nal arbitration logic drives the identifi cation number onto an

arbitration bus and the RIC2A containing

identified. An identical proced ure is used in the

COLLISION

not subject to the problems caused by missing boards, i.e.,

empty slots in the backplane. The logic associated with

asserting this arbi tration v ector in the v ario us packet repetition scenarios could be implemented in PAL® or GAL®

type devices.

Both of the above methods employ the same signals:

ACKI

tion.

The Inter-RIC bus allows mul ti -RIC2A operations to be performed in exactly the same manner as if there is only a single RIC2A in the system. The simplest way to describe the

operation of Inter-RIC bus is to see how it is used in a number of common packet repetition scenarios.

identification must be performed across all the

input pin. The output from the bottom of the chain

output pin. In a single RIC2A system

is defined as the highest port in the arbitration

is defined as the highest port in the chain with a collision

input is tied high), then the

signal from this RIC2A is sent to the ACKI input of

ACK O chain will be br oken and th e repeater will

PORT N or M

IDLE

state, the RIC2A board will assert ACKO. Exter-

state to identify

, ACKO and ACTN to perform

PORT M.

(Continued)

Por t N

IDLE

PORT N

identification

state.

and

PORT

TRANSMIT COLLISION

signal to a logic high

ACKO signals

identification avoids

sig-

PORT N

will be

TRANSMIT

Parallel arbitration is

PORT N

or M arbitra-

4.4 Examples Of Packet Repetition Scenarios

The operation of RIC2A is described b y the f oll owi ng e xamples of packet repetition scena rios.

Data Repetition Overview

When a packet is received at one port, the RIC2A checks

the source, and destination addresses of the packet. The

port configuration causes either a pseudo random bit

sequence, or the received packet to be transmi tt ed to diff erent ports.

If there is a destination address mismatch (secure mode),

then the RIC2A will generate a random pattern from the

first bit of the data field to that port. The data remains intact

on the Inter-RIC bus so other cascaded repeaters could

compare the destinat ion address with their local CAMs.

On a valid source address mismatch (secure mode),

RIC2A shall switch to random pattern both on the local

transmitt ing ports and the Inter-RIC bus.

Collision Scenari os Overview

The RIC 2A will adhere to all c ollision scenarios. When a

collisi on occ urs, RIC2A w ill switch to a jam patte r n to com ply with IEEE repeater specifications.

FIFO Condition Overview

Elasticity buffer error (ELBER) or FIFO overflow burst is

another condition that could take place anytime during the

packet transmission. The sequence of events for FIFO

burst is the same as those for collisi on.

Data Repetition Process

The first task to be performed is

This is an arbitration process performed by the Port State

Machines in the system. In situations where two or more

ports simultaneously receive packets, the Inter-RIC bus

operates by choosing one of the active ports, and forcing

the others to transmit data (real data or pseudo random

data). This is done in accordance with the IEEE specification's allowed exit paths from the

SEND PREAMBLE PATTERN

states.

The packet begins with a preamble pattern derived from

the RIC2A's on chip jam/preamble generator. The data

received at

plexor to the PLL decoder. Once phase lock has been

achieved, the decoded data (in NRZ f ormat) with its associated clock and enable signals, is asserted onto the IRD,

IRC, and IRE of the Inter-RIC bus. This serial data stream

is received from the bus by all RIC2As in the repeater and

directed to their elasticity buffers. Logic circuits monitor the

data stream and look for the Start of Frame Delimiter

(SFD). When it has been detected, data is loaded into the

elasticity buffer for later transmission. This will occur when

sufficient preamble has been transmitted and certain internal state machine oper ations have been fulfilled.

PORT N

is directed t hrough the receive multi-

PORT N

IDLE

or

RECEIVE COLLISION

identification.

state, i.e., to the

19 www.national.com

4.0 Functional Description

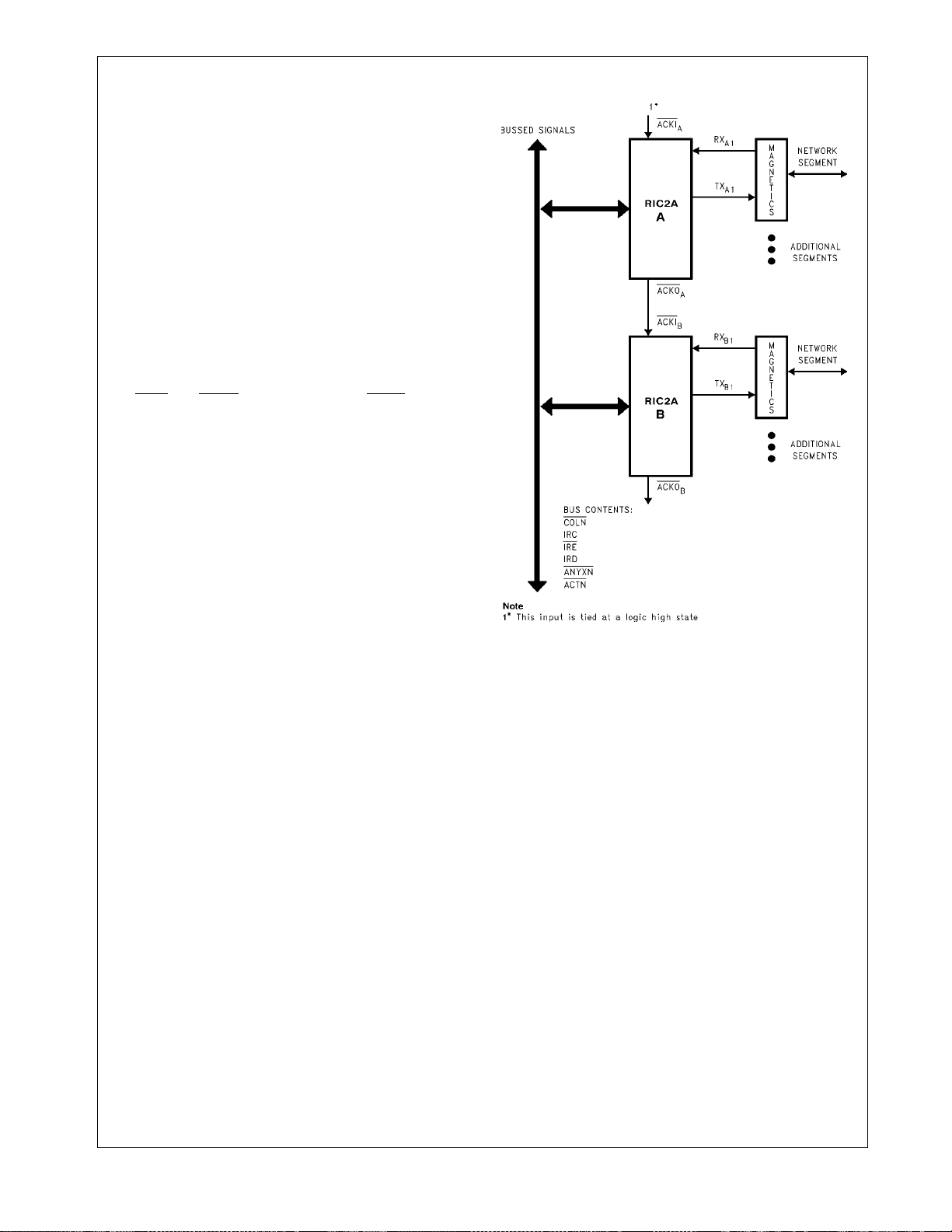

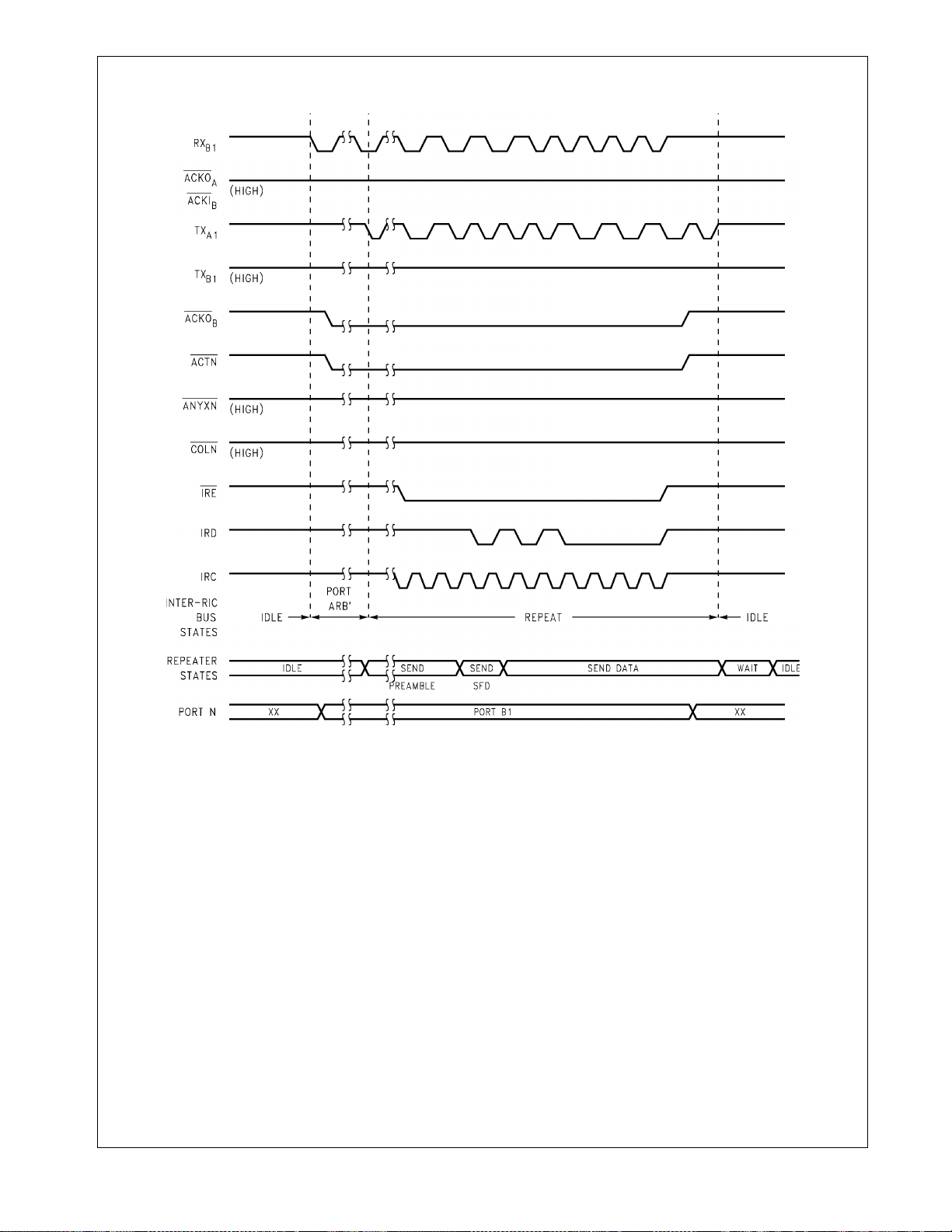

Figure 5 shows two RIC2As A and B, daisy chained

together with RIC2A-A positioned at the top of the chain. If

a packet is received at port B1 of RIC2A-B, and then

repeated to the other ports in the system (non-secure

mode). Figure 6 shows the functional timing diagram for

the packet repetition si gnals. In this example only two ports

in the system are shown. In non-secure mode, the other

ports also repeat the packet. It also indicates the operation

of the RIC2As' st ate machines in so far as can be seen by

observing the Inter-RIC bus. For reference, the repeater's

state transitions are shown in terms of the states defined

by the IEEE specification. The location of

shown. The following section describes the repeater and

Inter-RIC bus transitions sho wn in Fi gure 6.

The repeater activity is stimulated by the data signal

received by port B1. The RIC2As in the system are alerted

to forthcoming repeater operation by the falling edges on

the ACKI

Following a defined start up delay the repeater moves to

the

the start up delay to perform port arbitration. When packet

transmission begins, the RIC2A system enters the

REPEAT state. The expected, for normal packet repetition,

sequence of repeater states,

SFD

the Inter-RIC bus. They are then merged into a single

REPEAT state. Similarly, the

as a combin ed Inte r-RI C bus I D L E stat e.

Once a REPEAT operation has begun (e.g. the repeater

leaves the

bits of data or jam/preamble onto its network segments. If

the duration of the received signal from

than 96 bits, the r epeater transitions to the

LISION

fragment extension.

After the packet data has been repeated, including the

emptying of the RIC2As' elasticity buffers, the RIC2A performs the

formed during the

diagram.

and ACKO daisy chain and the ACTN bus signal.

SEND PREAMBLE

and

SEND DATA

state. The RIC2A system utilizes

are followed, but are not visible at

WAIT

IDLE

state), it is required to transmit at least 96

state (described later). This behavior is known as

Tw 1

transmit recovery operation. This is per-

WAIT

state shown in the repeater state

(Continued)

PORT N

is also

SEND PREAMBLE, SEND

and

IDLE

states appear

PORT N

is shorter

RECE IVE COL -

Figure 5. RIC2A System Topology

20 www.national.com

4.0 Functional Description

(Continued)

Note:

The activity shown on RX A1 represents the transmitted signal on TX A1 after being looped back by the attached transceiver.

1*

Figure 6. Data Repetition

21 www.national.com

4.0 Functional Description

(Continued)

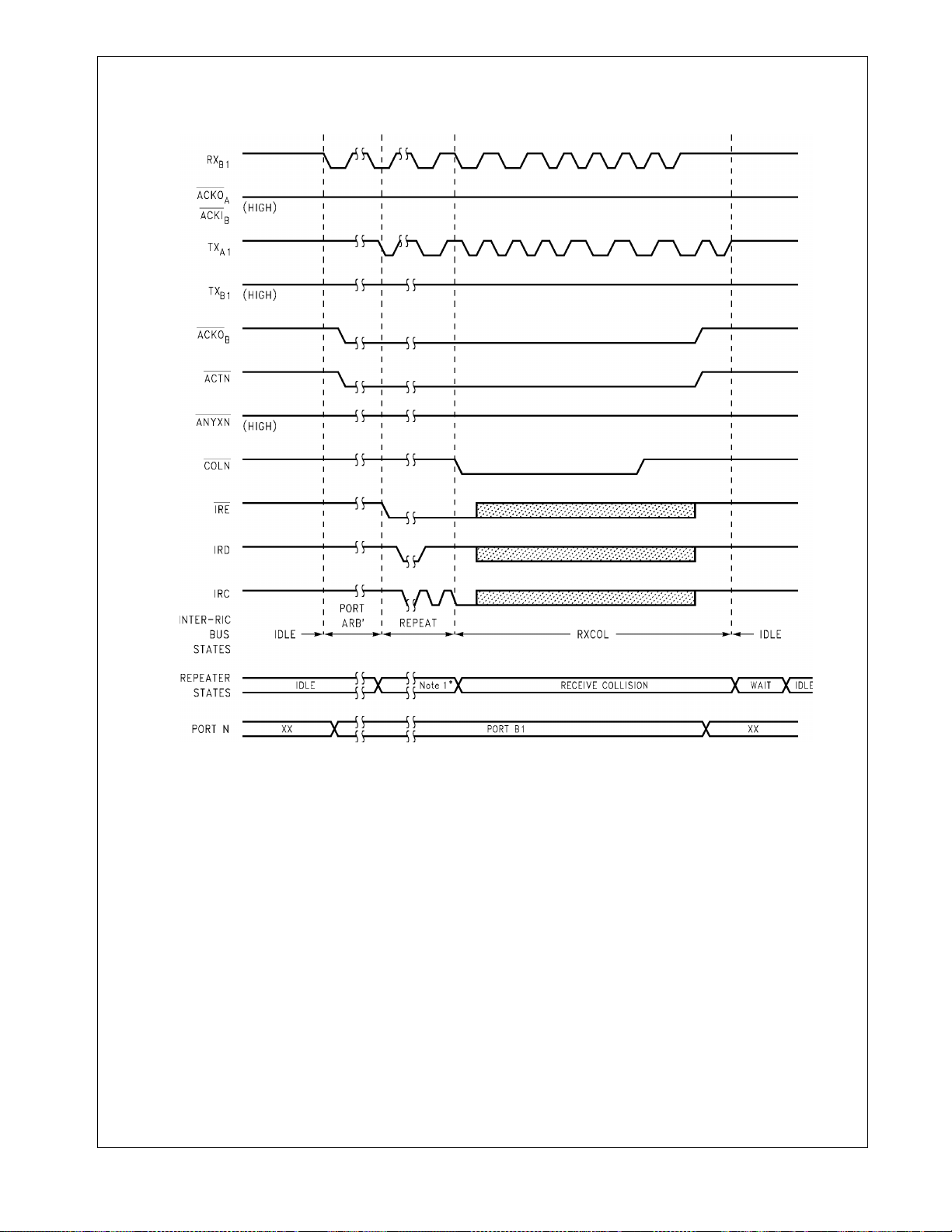

Note: 1 SEND PREAMBLE, SEND SFD, SEND DATA

AUI port shown.

Figure 7. Receive Collision

22 www.national.com

4.0 Functional Description

(Continued)

Receive Collisions (AUI Port only)

A receive collision is a collision which occurs on the network segment attached to the AUI port.

"receiv ed" in a similar manner as a data packet is received,

and then repeated to the other network segments. Not surprisingly, the receive collision propagation follows a similar

sequence of operations as data repetit ion.

An arbitration process is performed to find

preamble/jam pattern is transmitted by the repeater's other

ports. When the AUI port as

its segment the COLN

This forces all the RIC2As in the system to transmit a preamble/jam pattern to their segments. This is important

since they may be a lr eady transmitt ing data from their elasticity buffers. The repeater moves to the

SION

state and begins to transmit the jam pattern. The

repeater remains in this state until both the following conditions have been fulfill ed:

1. at least 96 bits have been transmitted onto the network,

2. the activity has ended.

Under close exami natio n, the repeate r specif ication reveals

that the actual end of activity has its own permutations of

conditions:

1. collision and receive data signals may end simulta-

neously,

2. receive data may appear t o end before co lli sion si gnals,

3. receive data may continue for some time after the end o f

the collision signal.

Network segments using coaxial media may experience

spurious gaps in segment activity when the collision signal

goes inactive. This arises from the inter-action between the

receive and collision signal squelch circuits, implemented

in coaxial transceivers, and the properties of the coaxial

cable itself. The repeater specification avoids propagation

of these activity gaps by extending collision activity by the

Tw2

wait time. Jam pattern transmission must be sustai ned

throughout this period. After this, the repeater will move to

the

WAIT

state unless there is a data signal being r eceived

by the AUI port as

The functional timing diagram, Figure 7, shows the opera-

tion of a repeater system during a receive collision. The

system configuration is the same as earlier described and

is shown in Figur e6.

The RIC2As perform the same

data repetition operations described previously. The system is noti fied of the receive collision on the AUI port by the

COLN

bus signal going active. This signal informs the main

state machines to send out the jam pattern rather than

valid data stored in the elasticity buffers. Once a collision

has occurred, the IRC, IRD and IRE

become undefined. When the collision has ended and the

Tw2

operation perfor med, the repeater moves to the

state.

PORT N.

PORT N

Inter-RIC bus signal is asserted.

PORT N

The collision is

PORT N

detects a collision on

and a

RECEIVE COLLI-

arbitration and

bus signals may

WAIT

Transmit Collisions

A transmit collision is a collision that is detected upon a

segment to whi ch the repeater system is transmitting. The

port state machine monitoring the colliding segment

asserts the ANYXN

causes

to the

had been

encoded 1 on to its network segment. While i n the

PORT M

TRANSMIT COLLISION

PORT N

MIT COLLISION

mit the 1010... jam pattern, and

performed. Ea ch RIC2A is obligated, by the IEEE spec if ication, to ensure all of its ports transmit for at least 96 bits

once the

This tra n s mit activ ity is e nfor c ed by th e A N Y XN

While ANYXN

To ensure this situation lasts for at least 96 bits, the MSM

inside the RIC2As assert the ANYXN

period. After this period has elapsed, ANYXN

asserted if there are multiple ports with active collisions on

their network segments.

There are two possible ways for a repeater to leave the

TRANSMIT COLLISION

TRANSMIT COLLISION

when network activity, i.e., collisions and their

sions, end before the 96 bit enforced period expires. Under

these conditions the repeater system may move directly to

the

WAIT

state when 96 bits have been transmitted to all

ports. If the MSM enforced period ends and there is still

one port experiencing a collision, the

state is entered. This may be seen on the Inter-RIC bus

when ANYXN

ting to its network segment. In this circumstance the InterRIC bus transitions to the RECEIVE COLLISION state.

The repeater will remain in this state while

sion,

Tw2

collision extension and any receive signals are

present. When these conditions ar e not true, packet repetition finishes and the repeater enters the

Figure 8 shows a multi-RIC2A system operating under

transmit collision conditions. There are many different scenarios which may occur during a transmit collision, this figure illustrates one of these. The diagram begins with

packet reception by port A1. Port B1 experiences a collision, since it is not

the main state machines in the system to switch from data

to jam pattern transmission.

Port A1 is also monitoring the ANYXN

tion forces A1 to relinquish its

mitting, stop asserting ACTN

PSM arbitration signals (ACKO

it transmits will be a Manchester encoded "1" in the jam

pattern. Since port B1 is the only port with a collision, it

attains

does however assert ACTN

the PSM arbitratio n chain (forces ACKO

ensure that ANYXN

ports, including

After some time port A1 e xperiences a collision. This ari ses

from the presence of the packet being received from port

A1's segment and the jam signal the repeater is now transmitting onto this segment. Simultaneous receive and transmit activity on one segment results in a collision. Port A1

fulfills the same criteria as B1, i.e., it has an active collision

PORT M

bus signal. The assertion of ANYXN

arbitration to begin. The repeater moves

state when the port which

starts to transmit a Manchester

TRANS-

state, all ports of the repeater must trans-

PORT M

state has been entered.

is active, all R IC2A port s will transmit ja m.

signal through out this

state. The most straight forward is

arbitration is

bus signal.

will on ly be

Tw2

exten-

ONE PORT LEFT

is de-asserted and

PORT N

status and stops asserting ANYXN. It

stays active and thus force all of the

PORT M,

to transmit to their segm ents.

PORT M

it asserts ANYXN. This alerts

PORT N

and release its hold on the

A and ACKI B). The first bit

, and exer t its presence upon

stops transmit-

PORT M's

WAIT

state.

bus line. Its a sser-

status, start trans-

B low). The MSMs

colli-

23 www.national.com

4.0 Functional Description

(Continued)

on its segment, but in addition it is higher in the arbitration

chain. This priority yields no benefits for port A1 since the

ANYXN

driving ANYXN

signal is still active. There are now two sources

, the MSMs and the collision on port B1.

Eventually the collision on port B1 ends and the ANYXN

extension by the MSMs expires. There is only one collision

on the network ( this may be deduced since ANYXN

tive) so the repeater will move to the

ONE PORT LEFT

is inac-

state. The RIC2A system treats this state in a similar manner to a receive collision with

PORT M

fulfillin g the role of

the receiving port. The difference from a true receive collision is that the switch from packet data to the jam pattern

has already been made (controlled by ANYXN

state of COLN

common with the operation of the

has no effect upon repeater operations. In

RECEIVE COLLISION

). Thus the

state, the repeater remains in this condition until the collision and receive activity on

repetition operation complete s when the

in the

WAIT

state has been perf ormed.

Note: In transmit collision conditions

which contained

during the

PORT N

TRANSMIT COLLISION

at the start of pac ket rep etition c ontai ns

PORT M

subside. The packet

Tw1

will only go active if the RIC2A

COLN

and

ONE PORT LEF T

recover y time

PORT M

states.

Jabber Protection

A repeater is required to disable transmit activity if the

length of its current transmission reaches the jabber protect limit. This is defined by the specification's

The repeater disables output for a time period defined by

the

Tw4

specification, after this period normal operation

may resum e.

Figure 9 shows the effect of a jabber length packet upon a

RIC2A based repeater system. The

state is entered from the

SEND DATA

JABBER PROTECT

state. While the

period is observed the Inter-RIC bus displays the IDLE

state. Thi s is misl eading si nce new pa ck et activi ty or co ntinuous activity (as shown in the diagram) does not result in

packet repetition. This may only occur when the

quirement has been sati sfied.

Tw3

Tw4

time.

Tw4

re-

24 www.national.com

4.0 Functional Description

(Continued)

Note: The Inter-RIC bus is configured to use active low signals. AUI port shown

Figure 8. Transmit Colli sion

25 www.national.com

4.0 Functional Description

(Continued)

Note:1* The IEEE Specificati on does not have a jabber protect s tate defined in i ts main state diagr am, this

behavior is defined in an additional MAU Jabber Lockup Protection state diagram.

Note: The Inter-RIC bus is configured to use active low signals. AUI port shown

Figure 9. Jabber Protect

26 www.national.com

4.0 Functional Description

Note: DE = Bus Drive Enable active high, /RE = Bus Receive Enable active low

Note: The Inter-RIC bus is configured to use active low signals.

Figure 10. External Bus Trans ceiver Connection Diagram

(Continued)

Figure 11. Mode Load Operation

4.5 Description Of Hardware Connection For Inter-ric Bus

When considering the hardware interface, the Inter-RIC

bus may be viewed as consisting of three gr oups of signals:

1. Port Arbitration chain, namely: ACKI

2. Simultaneous drive and sense signals, i.e., ACTN

ANYXN

tiple devices).

3. Drive or sense signals, i.e., IRE

(Only one device ass erts these si gnals at any inst ance in

time).

The first set of signals are either used as point to point

links, or with external arbitration logic. In both cases the

load on these signals will not be large, so the on-chip drivers are adequate. This may not be true for signal classes

(2) and (3 ) .

The Inter-RIC bus has been designed to connect RIC2As

together di rectly, or via external bus transceiver s. The latter

is advantageous in large repeaters. In the second application the backplane is often heavily loaded and is beyond

. (Potenti ally these signals may be dr iven by mul-

and ACKO.

and

, IRD, IRC and COLN.

the drive capabilities of the on-chip bus drivers. The need

for simultaneous sense and drive capabilities on the ACTN

and ANYXN signals, and the desire to allow operation with

external bus transceivers, makes it necessary for the se bus

signals to each have a pair of pins on the RIC2A. One

drives the bus, the other senses the bus signal. When

external bus transceivers are used, they must be open collector / open drain to allow wire-ORing of the signals. Additionally, the drive and sense enables of the bus transceiver

should be tied in the acti ve state.

The uni-directional nature of information transfer on the

IRE

, IRD, IRC and COLN signals, means a RIC2A is either

driving these signals or receiving them from the bus, but

not both at the same time. Thus a single bi-directional

input / output pin is adequate for each of these signals. If

an external bus transceiver is used with these signals the

Packet Enable "PKEN" RIC2A output pin performs the

function of a drive enable and sense disable.

Figure 10 shows the RIC2A con nected to the Inter-RIC bus

via external bus transceivers, such as National's DS3893A

bus transceiv ers.

27 www.national.com

Loading...

Loading...